# A Partitioning-Centric Approach for the Modeling and the Methodical Design of Automotive Embedded Systems Architectures

## Dissertation

A thesis submitted to the

## Faculty of Electrical Engineering and Computer Sciences

of the

## **Technical University of Berlin**

in partial fulfillment of the requirements for the academical degree of  $$\rm Dr.-Ing.$$

by

## **Augustin Kebemou**

Berlin 2008 D 83

# A Partitioning-Centric Approach for the Modeling and the Methodical Design of Automotive Embedded Systems Architectures

vorgelegt von Dipl.-Ing. Augustin Kebemou Berlin

Von der Fakultät IV - Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

> Doktor der Ingenieurwissenschaften - Dr.-Ing. -

> > genehmigte Dissertation

Promotionsausschuss:

- Prof. Dr.Sabine Glesner (Vorsitzender)

- Prof. Dr.-Ing. Ina Schieferdecker (Gutachter)

- Prof. Dr. Jakob Rehof (Gutachter)

Tag der wissenschaftlichen Aussprache: 06.05.2008

Berlin 2008 D 83

## Acknowledgments

"Acquiring knowledge is useless unless it makes us better servants of humanity".

The achievement of this thesis would not have been possible without the intervention and the support of many people. I am very grateful to all those who supported me during the work that led to this thesis.

In particular, I would like to thank the supervisor of this work, Prof. Dr.-Ing. Ina Schieferdecker (holder of the chair for Design and Testing of Telecommunication Systems at the TU Berlin and concurrently leader of the research group MOTION at the Fraunhofer Institute FOKUS) for her advices, for her reviews and her suggestions that improved both the technical and the scientific quality of this thesis. I also thank Ina for the friendly working atmosphere that gave me additional self-confidence to go ahead.

I am also deeply grateful to Prof. Dr. Jakob Rehof, the director of the Fraunhofer Institute for Software and Systems Engineering (ISST) and concurrently holder of the chair for Software Engineering at the university of Dortmund, who accepted spontaneously to support me, invested his time to examine my work and undertook the co-supervision activities that considerably contributed to the achievement of this thesis.

Taking this opportunity, I would further like to thank Rainer Mackenthun, the head of the Department of Dependable Technical Systems at the Fraunhofer Institute for Software and Systems Engineering (ISST) in Berlin, Prof. Dr. Herbert Weber, Dr. Alexander Borusan and Dr. Volker Zurwehn, also from the ISST institute in Berlin, for their psychological support. I did appreciate your fairness and the way you judged my work during my hard days.

I would also like to address my special thanks to Angelika Becker, who played a central role in the accomplishment of this thesis. Thank you very much, Geli, for the nights and the weekends you spent to review this thesis and to correct my textual formulations. Thank you for your advices. Thank you for the time you invested in intensive discussions with me. Thank you once more for your emotional support.

I finally wish to express my gratefulness to my family and all of my friends for their patience during the years of this thesis as well as to my colleagues at the Fraunhofer Institute for Software and Systems Engineering (ISST) who participated in the fruitful discussions that made this thesis possible.

Thank u all.

Once more, remember: "Acquiring knowledge is useless unless it makes you a better servant of humanity".

A. Kebemou

## Abstract

Because of the increasing demand for more comfort, security and environmental compatibility, the development of E/E-systems (Electric/Electronic) has become a central task for automobile manufacturers. In the actual context that is characterized by the rapid increase of software- and electronic-based components in modern vehicles and the related hard competition in the automobile market, it is necessary to design optimal architectures for automobiles' E/E-systems in a relatively short time. An optimal architecture of an E/E-system must minimize the usage of the hardware (i.e. processing units, memory elements, communication cables, etc.) as well as the operating costs (energy and fuel consumption, maintenance, waste disposal, etc.) and concurrently optimize the functioning and the quality (i.e. performance, reliability, safety, security, etc.) of the system. In this thesis we suggest to solve this problem by means of CAD-supported tools. This requires drastic changes within both the established development methods and the design processes. We propose a system-oriented design process and an automatic partitioning method with appropriate modeling techniques to support the model-based definition of the architectures of automobiles' E/E-systems.

## Abstrakt (Deutsch)

Vor dem Hintergrund der steigenden Nachfrage nach mehr Komfort, Sicherheit und Umweltfreundlichkeit ist die Entwicklung von E/E-Systemen (elektrik/elektronik) zu einer zentralen Aufgabe für die Automobilhersteller geworden. In der gegenwärtigen Situation, die durch die rapide Zunahme von software- und elektronikbasierten Bestandteilen in modernen Fahrzeugen und den damit verbundenen harten Konkurrenzkampf auf dem Automobilmarkt gekennzeichnet ist, ist es notwendig, optimale Architekturen für automobile E/E-Systeme in relativ kurzer Zeit zu entwickeln. Die optimale Architektur eines E/E-Systems muss die Hardwarenutzung (d. h. Prozessoren, Datenspeicher, Kommunikationskabel, I/O Module, etc.) und die Betriebskosten (Energie- und Treibstoffverbrauch, Wartung, Verschrottung, etc.) verringern und gleichzeitig die Funktionstüchtigkeit und die Qualität (Leistung, Zuverlässigkeit, Sicherheit, etc.) des Systems verbessern. In dieser Arbeit schlagen wir vor, dieses Problem durch computergestützte Werkzeuge zu lösen. Dies macht einschneidende Veränderungen sowohl in den Entwicklungsmethoden als auch in den Designprozessen erforderlich. Wir schlagen einen systemorientierten Entwicklungsprozess vor, der die modellbasierte Definition der Architekturen von automobilen E/E-Systemen unterstützen kann. Diese Arbeit definiert die passenden Modellierungstechniken und die Algorithmen, die eine automatische Partitionierung von System-level-E/E-Modellen ermöglichen.

# Contents

| 1 | Gen | eral introduction 1                                  |  |  |  |  |  |  |  |

|---|-----|------------------------------------------------------|--|--|--|--|--|--|--|

|   | 1.1 | Motivation                                           |  |  |  |  |  |  |  |

|   | 1.2 | Problem definition                                   |  |  |  |  |  |  |  |

|   | 1.3 | Procedural method to solve the problem               |  |  |  |  |  |  |  |

|   | 1.4 | Contributions                                        |  |  |  |  |  |  |  |

|   | 1.5 | Publications                                         |  |  |  |  |  |  |  |

|   | 1.6 | Scheduling of the thesis                             |  |  |  |  |  |  |  |

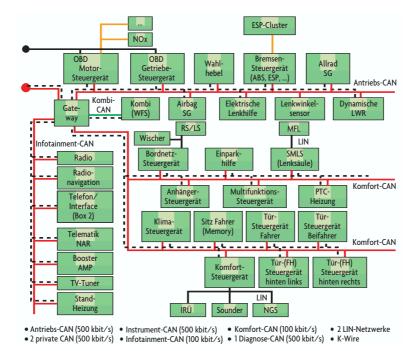

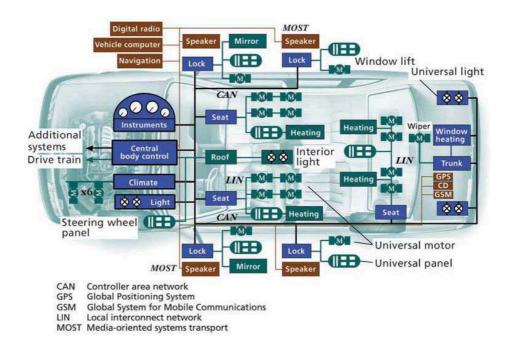

| 2 | Aut | Automotive Embedded Systems                          |  |  |  |  |  |  |  |

|   | 2.1 | Automotive electronics                               |  |  |  |  |  |  |  |

|   |     | 2.1.1 Embedded systems                               |  |  |  |  |  |  |  |

|   |     | 2.1.2 Automotive and embedded systems                |  |  |  |  |  |  |  |

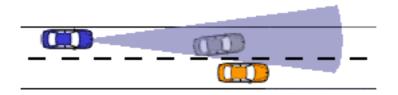

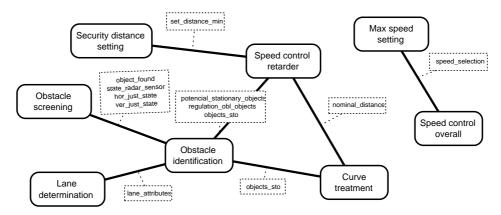

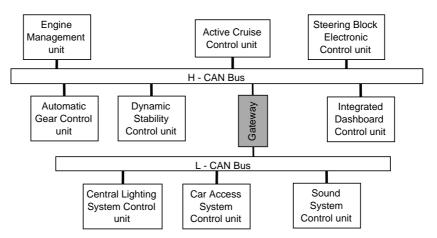

|   |     | 2.1.3   Example: The Active Cruise Control   17      |  |  |  |  |  |  |  |

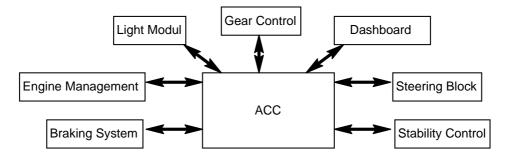

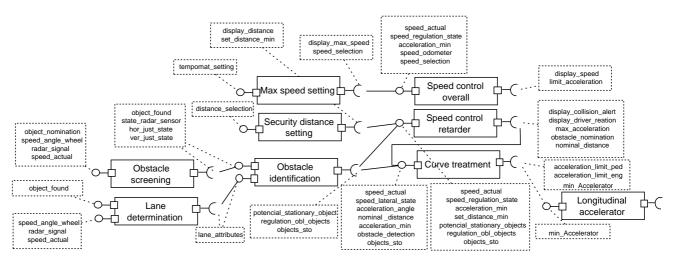

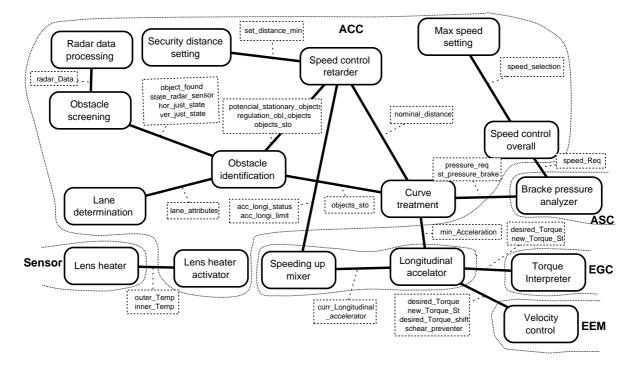

|   |     | 2.1.4 The ACC functional connectivity                |  |  |  |  |  |  |  |

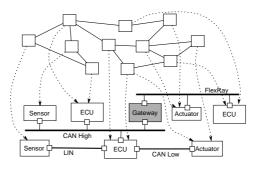

|   | 2.2 | Automotive connectivity                              |  |  |  |  |  |  |  |

|   | 2.2 | 2.2.1 Automotive communication protocols             |  |  |  |  |  |  |  |

|   |     | 2.2.2 All-rounder automotive communication protocols |  |  |  |  |  |  |  |

|   |     | 2.2.3 High-speed and real-time protocols             |  |  |  |  |  |  |  |

|   |     | 2.2.4       General-purpose protocols       23       |  |  |  |  |  |  |  |

|   |     | 2.2.5 Other in-vehicle and smart network protocols   |  |  |  |  |  |  |  |

|   | 2.3 | Conclusion                                           |  |  |  |  |  |  |  |

|   |     |                                                      |  |  |  |  |  |  |  |

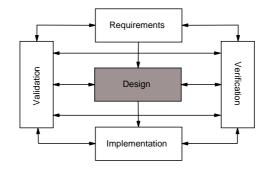

| 3 | Emt | pedded systems design 27                             |  |  |  |  |  |  |  |

|   | 3.1 | Embedded systems design methods                      |  |  |  |  |  |  |  |

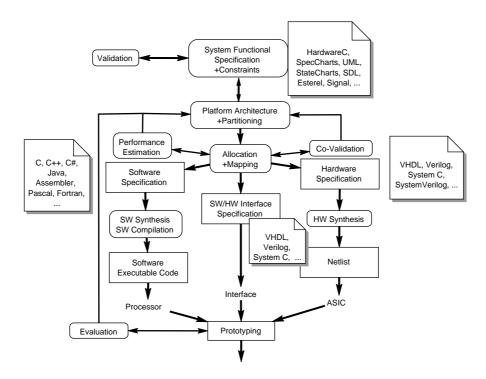

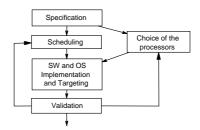

|   |     | 3.1.1 The sequential design process                  |  |  |  |  |  |  |  |

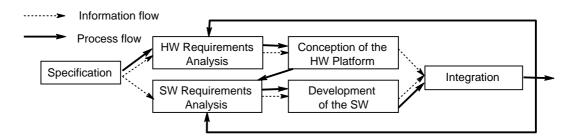

|   |     | 3.1.2 The concurrent design method                   |  |  |  |  |  |  |  |

|   | 3.2 | Design activities                                    |  |  |  |  |  |  |  |

|   |     | 3.2.1 The specification                              |  |  |  |  |  |  |  |

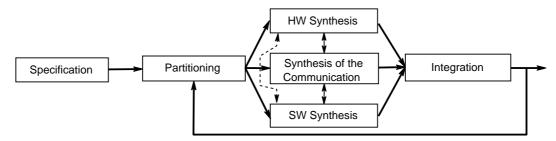

|   |     | 3.2.2 The partitioning                               |  |  |  |  |  |  |  |

|   | 3.3 | The implementation                                   |  |  |  |  |  |  |  |

|   |     | 3.3.1 The software synthesis                         |  |  |  |  |  |  |  |

|   |     | 3.3.2 The hardware synthesis                         |  |  |  |  |  |  |  |

|   |     | 3.3.3 The synthesis of the interfaces                |  |  |  |  |  |  |  |

|   | 3.4 | Conclusion                                           |  |  |  |  |  |  |  |

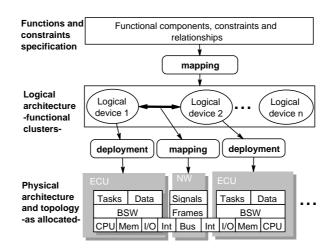

| 4 | Aut | omotive systems design 35                            |  |  |  |  |  |  |  |

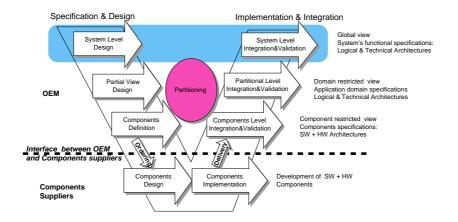

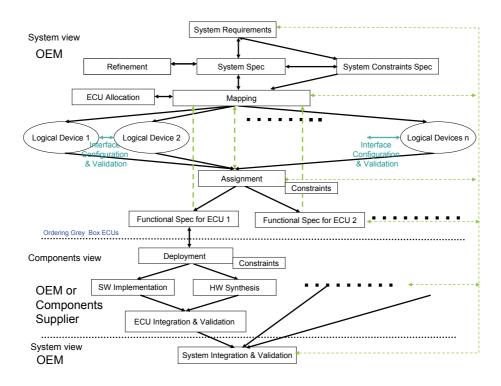

| • | 4.1 | Design of AES                                        |  |  |  |  |  |  |  |

|   |     | 4.1.1 Top-down and bottom-up                         |  |  |  |  |  |  |  |

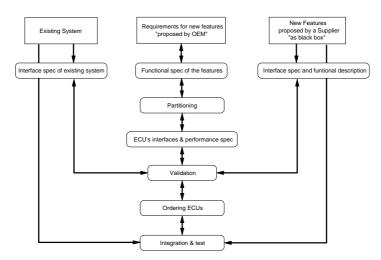

|   |     | 4.1.2 Current OEM design practice                    |  |  |  |  |  |  |  |

|   |     | 4.1.3 Limitations of the current OEM design practice |  |  |  |  |  |  |  |

|   | 4.2 | Proposed design approach                             |  |  |  |  |  |  |  |

|   |     | 4.2.1 Factors of the problem resolution              |  |  |  |  |  |  |  |

|   |     |                                                      |  |  |  |  |  |  |  |

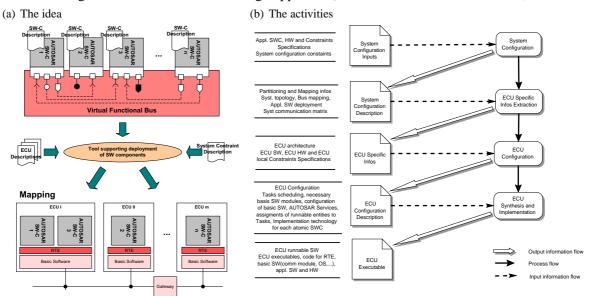

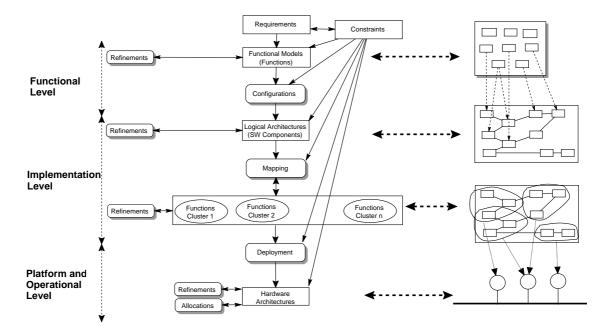

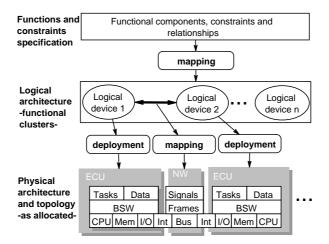

|   |       | 4.2.2 The system-oriented design approach                               |

|---|-------|-------------------------------------------------------------------------|

|   |       | 4.2.3 Analysis                                                          |

|   | 4.3   | Conclusion                                                              |

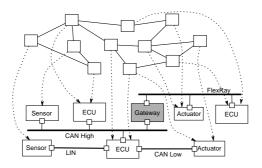

| 5 | Мос   | leling AES: State-of-the-art 41                                         |

|   | 5.1   | Modeling AES                                                            |

|   |       | 5.1.1 Model-driven system development in the automotive engineering 41  |

|   |       | 5.1.2 AES are heterogeneous and complex systems                         |

|   | 5.2   | AES modeling needs                                                      |

|   | 0.2   | 5.2.1 AES modeling prerequisites                                        |

|   |       | 5.2.2 Features expected from an AES model-based design solution         |

|   | БЭ    |                                                                         |

|   | 5.3   | 0 1                                                                     |

|   |       | 5.3.1 Abstraction levels in the AES design                              |

|   |       | 5.3.2 AES architectural modeling concepts                               |

|   |       | 5.3.3 AES behavioral modeling concepts                                  |

|   | 5.4   | Conclusion                                                              |

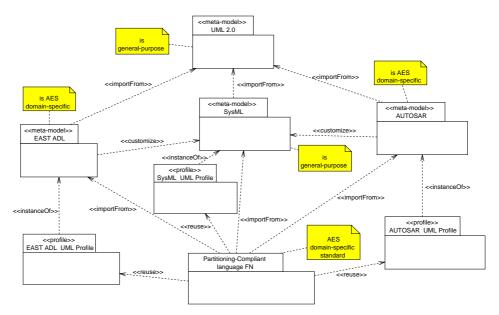

| 6 | The   | value of AES modeling languages 49                                      |

|   | 6.1   | The evaluation framework                                                |

|   | • • • | 6.1.1 AES modeling requirements for the partitioning                    |

|   |       | 6.1.2 Related work                                                      |

|   |       | 6.1.3 Classification criteria                                           |

|   |       |                                                                         |

|   | 6.0   | 0 11                                                                    |

|   | 6.2   | AES modeling languages                                                  |

|   |       | 6.2.1 General-purpose languages                                         |

|   |       | 6.2.2 Automotive domain-specific modeling languages                     |

|   | 6.3   | Evaluation and classification of AES modeling languages                 |

|   | 6.4   | Conclusion                                                              |

| 7 | Inpu  | ts for the partitioning 67                                              |

|   | 7.1   | Required inputs for the partitioning                                    |

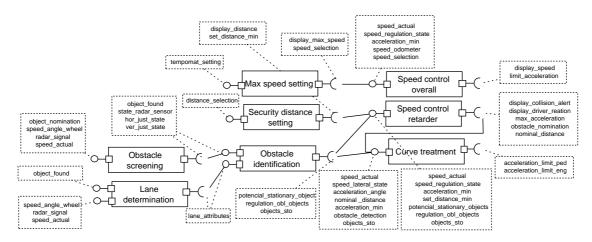

|   | 7.2   | Specifying the system's functionalities                                 |

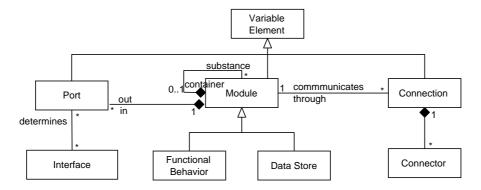

|   |       | 7.2.1 Relevant modeling concepts                                        |

|   |       | 7.2.2 The FN: The modeling solution for the functional specification 69 |

|   | 7.3   | Specifying the hardware platform                                        |

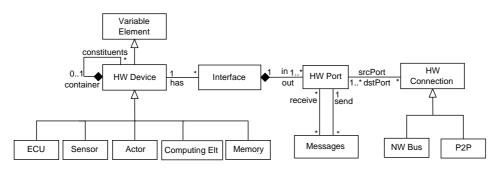

|   |       | 7.3.1 Relevant modeling concepts                                        |

|   |       | 7.3.2   The HN: The hardware platform   7.5.1   7.5.2                   |

|   | 7.4   | The partitioning                                                        |

|   | 1.4   |                                                                         |

|   |       | 1 01                                                                    |

|   |       | 7.4.2 Relevant attributes for the elements of the input models          |

|   | 7.5   | Conclusion                                                              |

| 8 | The   | synthesis Model 81                                                      |

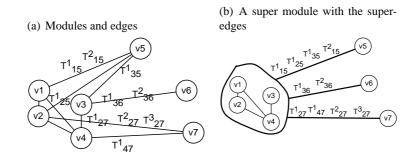

|   | 8.1   | Definition of the synthesis model                                       |

|   |       | 8.1.1 Requirements for the synthesis model                              |

|   |       | 8.1.2 The synthesis model                                               |

|   | 8.2   | Annotations for the synthesis model                                     |

|   | 5.2   | 8.2.1 Concurrency, sequencing                                           |

|   |       | 8.2.2 Annotations for the nodes                                         |

|   |       |                                                                         |

|   |       | 0                                                                       |

|   |       | 8.2.4 Annotations for the tokens                                        |

|   |       |                                                                         |

|   | 8.3   | 8.2.5 Formal definition of the synthesis model                          |

| 8.3.2       Model transformation       89         8.4       Conclusion       89         9       The partitioning: State-of-the-art       91         9.1.1       Frames of the problem       91         9.1.2       Fraumes of the problem       91         9.1.2       Requirements for the partitioning algorithm       92         9.2       Partitioning methods       93         9.2.1       Exact and heuristic methods       93         9.2.2       Constructive partitioning techniques       95         9.2.3       Iterative improvement techniques       97         9.3       Conclusion       101         10       The partitioning strategy       103         10.1       The rescretp process       103         10.1       Partere-clustering       105         10.2       The pre-clustering algorithm       1065         10.2.1       Definitions of terms       1067         10.3       The clustering       107         10.3.1       Conclusion       107         10.3.2       The clostering algorithm       111         10.3.3       The Clostering algorithm       116         11.1       The Coseness function       107                                                                                                                                                                                                                                                                   |    |      | 8.3.1 T   | The weight of an edge in a <i>CDFM</i> model            |     |     |     |   |     |   | . 88  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|------|-----------|---------------------------------------------------------|-----|-----|-----|---|-----|---|-------|

| 9 The partitioning: State-of-the-art         91           9.1 The partitioning problem         91           9.1.1 Frames of the problem         91           9.1.2 Requirements for the partitioning algorithm         92           9.2 Partitioning methods         93           9.2.1 Exact and heuristic methods         93           9.2.2 Constructive partitioning techniques         95           9.2.3 Iterative improvement techniques         97           9.3 Conclusion         103           10.1 The partitioning strategy         103           10.1.1 A three-step process         103           10.1.2 Definitions of terms         105           10.2 The pre-clustering         105           10.2 The pre-clustering algorithm         106           10.3 The clustering         107           10.3 The clustering algorithm         106           10.3 The clustering algorithm         106           10.3 The clustering algorithm         107           10.3.2 The closeness function         111           10.3 Closeness metrics         107           10.3.3 The QT clustering algorithm         111           10.3 Conclusion         113           11.1 The CAN: A frame-oriented communication protocol         115           11.1.1                                                                                                                                             |    |      | 8.3.2 N   | Aodel transformation                                    |     |     |     |   |     |   | . 89  |

| 9.1       The partitioning problem       91         9.1.1       Frames of the problem       91         9.1.2       Requirements for the partitioning algorithm       92         9.2       Partitioning methods       93         9.2.1       Exact and heuristic methods       93         9.2.2       Constructive partitioning techniques       93         9.2.3       Iterative improvement techniques       97         9.3       Conclusion       101         10       The partitioning strategy       103         10.1       The merition of terms       104         10.1.2       Definition of terms       104         10.1.3       The main procedure       105         10.2.1       Definition       105         10.2.2       The pre-clustering algorithm       106         10.3       The closeness metrics       107         10.3.4       Conclusion       111         11.5       11.1.1       Orgeness function       110         10.3.3       The QL clustering algorithm       111         10.3.4       Conclusion       115         11.1       The CAN: A frame-oriented communication protocol       115         11.1.1       Organization of a                                                                                                                                                                                                                                                 |    | 8.4  | Conclusio | on                                                      |     |     |     |   |     |   | . 89  |

| 9.1       The partitioning problem       91         9.1.1       Frames of the problem       91         9.1.2       Requirements for the partitioning algorithm       92         9.2       Partitioning methods       93         9.2.1       Exact and heuristic methods       93         9.2.2       Constructive partitioning techniques       93         9.2.1       Exact and heuristic methods       93         9.2.2       Constructive partitioning techniques       97         9.3       Conclusion       101         10       The partitioning strategy       103         10.1       The merocess       103         10.1.2       Definition of terms       104         10.1.3       The main procedure       105         10.2.1       Definition       105         10.2.2       The pre-clustering algorithm       107         10.3.3       The closeness metrics       107         10.3.3       The QT clustering algorithm       111         10.3.4       Conclusion       115         11.1       The CAN: A frame-oriented communication protocol       115         11.1.1       Oralization of a CAN network       115         11.1.1       Oralization of                                                                                                                                                                                                                                        | _  |      |           |                                                         |     |     |     |   |     |   |       |

| 9.1.1       Frames of the problem       91         9.1.2       Requirements for the partitioning algorithm       92         9.2       Partitioning methods       93         9.2.1       Exact and heuristic methods       93         9.2.2       Constructive partitioning techniques       95         9.2.3       Iterative improvement techniques       97         9.3       Conclusion       101 <b>10 The partitioning algorithms</b> 103         10.1       The partitioning strategy       103         10.1.2       Definitions of terms       104         10.1.3       The main procedure       105         10.2.1       Definition       105         10.2.2       The pre-clustering       105         10.3.1       Closeness function       107         10.3.2       The closeness function       107         10.3.1       Closeness function       110         10.3.2       The clostening algorithm       111         10.3.4       Conclusion       115         11.1       The CAN: A frame-oriented communication protocol       115         11.1       The CAN: A frame-oriented communication protocol       115         11.1.1       Organization of a                                                                                                                                                                                                                                         | 9  |      | -         | -                                                       |     |     |     |   |     |   | -     |

| 9.1.2       Requirements for the partitioning algorithm       92         9.2       Partitioning methods       93         9.2.1       Exact and heuristic methods       93         9.2.2       Constructive partitioning techniques       95         9.2.3       Iterative improvement techniques       97         9.3       Conclusion       101         10 The partitioning algorithms       103         10.1.1       A three-step process       103         10.1.2       Definition of terms       104         10.1.3       The main procedure       105         10.2.1       Definition       105         10.2.1       Definition       105         10.2.2       The pre-clustering algorithm       106         10.3       The closeness function       107         10.3.1       Closeness function       107         10.3.2       The clostering algorithm       111         10.3.4       Conclusion       113         11       Organization of a CAN network       115         11.1.1       Organization of a standard CAN data frame       116         11.3.4       Formes       124         11.4       Frames multiplexing       119                                                                                                                                                                                                                                                                   |    | 9.1  | •         |                                                         |     |     |     |   |     |   |       |

| 9.2       Partitioning methods       93         9.2.1       Exact and heuristic methods       93         9.2.2       Constructive partitioning techniques       95         9.3.3       Iterative improvement techniques       97         9.3.       Conclusion       101         10       The partitioning algorithms       103         10.1.1       A three-step process       103         10.1.2       Definitions of terms       104         10.3.3       The pre-clustering       105         10.2.1       Definition       105         10.2.2       The pre-clustering algorithm       106         10.3       The develoption algorithm       106         10.3.1       Choseness function       107         10.3.2       The clustering algorithm       101         10.3.3       The QT clustering algorithm       111         10.3.4       Conclusion       113         11       Organization of a CAN network       115         11.1.1       Organization of a Atandard CAN data frame       116         11.1.3       Format of a standard CAN data frame       116         11.1.4       Frames multiplexing       119         11.1.5       Relations with the                                                                                                                                                                                                                                         |    |      |           | •                                                       |     |     |     |   |     |   | -     |

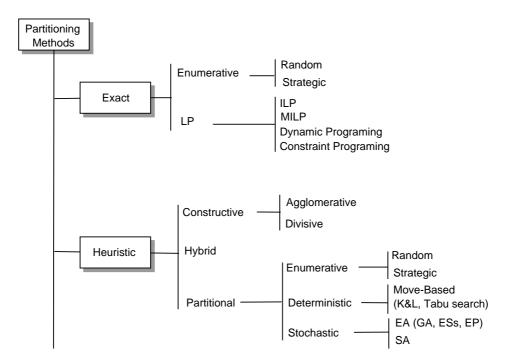

| 9.2.1       Exact and heuristic methods       93         9.2.2       Constructive partitioning techniques       95         9.2.3       Iterative improvement techniques       97         9.3       Conclusion       101         10 The partitioning algorithms       103         10.1.1       A three-step process       103         10.1.2       Definitions of terms       104         10.1.3       The main procedure       105         10.2.1       Definition       105         10.2.2       The pre-clustering algorithm       106         10.3       The clustering       107         10.3.1       Closeness metrics       107         10.3.2       The closeness function       110         10.3.3       The QT clustering algorithm       111         10.3.4       Conclusion       113         11       Evaluating and improving a partition       115         11.1.1       Organization of a CAN network       115         11.2       CAN reames       116         11.3       Format of a standard CAN data frame       116         11.4.4       Frames multiplexing       117         11.5       Relations with the partitioning       119                                                                                                                                                                                                                                                        |    |      |           |                                                         |     |     |     |   |     |   |       |

| 9.2.2       Constructive partitioning techniques       95         9.3       Iterative improvement techniques       97         9.3       Conclusion       101         10 The partitioning algorithms       103         10.1       The partitioning strategy       103         10.1.1       A three-step process       103         10.1.2       Definitions of terms       104         10.1.3       The main procedure       105         10.2.1       Definition       105         10.2.2       The pre-clustering       105         10.2.2       The pre-clustering algorithm       106         10.3       The closeness metrics       107         10.3.1       Closeness metrics       107         10.3.2       The closeness function       110         10.3.3       The QT clustering algorithm       111         10.3.4       Conclusion       113         11.1       Organization of a CAN network       115         11.1.2       CAN frame-oriented communication protocol       115         11.1.3       Format of a standard CAN data frame       116         11.1.4       Frames multiplexing       119         11.2       CAN frames       121                                                                                                                                                                                                                                                       |    | 9.2  |           | •                                                       |     |     |     |   |     |   |       |

| 9.2.3       Iterative improvement techniques       97         9.3       Conclusion       101         10       The partitioning algorithms       103         10.1       The partitioning strategy       103         10.1.1       A three-step process       103         10.1.2       Definitions of terms       104         10.1.3       The main procedure       105         10.2.1       Definition       105         10.2.2       The pre-clustering algorithm       106         10.3       The clustering       107         10.3.1       Closeness metrics       107         10.3.2       The clostering algorithm       111         10.3.3       The QC clustering algorithm       111         10.3.4       Conclusion       113         11       10.3.4       Conclusion       113         11       10.3.4       Conclusion       115         11.1.1       Organization of a CAN network       115         11.1.2       CAN frames       116         11.1.3       Format of a standard CAN data frame       116         11.1.4       Frames multiplexing       119         11.1.6       Practical considerations for the frames multiplexing <td></td>                                                                                                                                               |    |      |           |                                                         |     |     |     |   |     |   |       |

| 9.3       Conclusion       101         10       The partitioning algorithms       103         10.1       The partitioning strategy       103         10.1.1       A three-step process       103         10.1.2       Definitions of terms       104         10.1.3       The main procedure       105         10.2.1       Definition       105         10.2.2       The pre-clustering       105         10.2.2       The pre-clustering algorithm       106         10.3       The closeness metrics       107         10.3.1       Closeness function       110         10.3.2       The closeness function       110         10.3.3       The QT clustering algorithm       111         10.3.4       Conclusion       113         11       The CAN: A frame-oriented communication protocol       115         11.1.1       Organization of a CAN network       115         11.1.2       CAN frames       116         11.1.4       Frames multiplexing       117         11.1.5       Relations with the partitioning       119         11.2.4       Frames multiplexing       117         11.2.1       The cost function       121 <t< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                                                                                                                    |    |      |           |                                                         |     |     |     |   |     |   |       |

| 10 The partitioning algorithms       103         10.1 The partitioning strategy       103         10.1.1 A three-step process       103         10.1.2 Definitions of terms       104         10.1.3 The main procedure       105         10.2.1 Definition       105         10.2.2 The pre-clustering       105         10.2.1 Definition       105         10.2.2 The pre-clustering algorithm       106         10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11       10.3.4 Conclusion       113         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.1.2 CAN frames       116         11.1.3 Format of a standard CAN data frame       116         11.1.4 Frames multiplexing       119         11.1.5 Relations with the partitioning       119         11.2 CAN frames       121         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques                                                                                                                                                                                                          |    |      |           |                                                         |     |     |     |   |     |   |       |

| 10.1 The partitioning strategy       103         10.1.1 A three-step process       103         10.1.2 Definitions of terms       104         10.1.3 The main procedure       105         10.2 The pre-clustering       105         10.2.1 Definition       105         10.2.2 The pre-clustering algorithm       106         10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.1.2 CAN frames       116         11.1.3 Format of a standard CAN data frame       116         11.1.4 Frames multiplexing       119         11.1.5 Relations with the partitioning       119         11.2 The value of a partition       121         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123 <th></th> <th>9.3</th> <th>Conclusio</th> <th>on</th> <th>• •</th> <th>• •</th> <th>• •</th> <th>·</th> <th>• •</th> <th>•</th> <th>. 101</th>                            |    | 9.3  | Conclusio | on                                                      | • • | • • | • • | · | • • | • | . 101 |

| 10.1 The partitioning strategy       103         10.1.1 A three-step process       103         10.1.2 Definitions of terms       104         10.1.3 The main procedure       105         10.2.1 Definition       105         10.2.1 Definition       105         10.2.2 The pre-clustering algorithm       106         10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.1.2 CAN frames       116         11.1.3 Format of a standard CAN data frame       116         11.1.4 Frames multiplexing       119         11.1.5 Relations with the partitioning       119         11.2 The value of a partition       121         11.2.1 The cost function       121         12.2 The cost as a bin packing problem       122         13.3 In Pa Next Fit, the First Fit and the Best Fit strategies       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies                                                                                                                                                          | 10 | Tho  | nartition | ing algorithms                                          |     |     |     |   |     |   | 103   |

| 10.1.1 A three-step process       103         10.1.2 Definitions of terms       104         10.1.3 The main procedure       105         10.2 The pre-clustering       105         10.2.1 Definition       105         10.2.2 The pre-clustering algorithm       106         10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.2 CAN frames       116         11.3 Format of a standard CAN data frame       116         11.4 Frames multiplexing       117         11.5 Relations with the partitioning       119         11.2 The value of a partition       121         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124                                                                                                                                                                               | 10 |      | •         | 5 6                                                     |     |     |     |   |     |   |       |

| 10.1.2 Definitions of terms       104         10.1.3 The main procedure       105         10.2 The pre-clustering       105         10.2.1 Definition       105         10.2.2 The pre-clustering algorithm       106         10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.2 CAN frames       116         11.1.3 Format of a standard CAN data frame       116         11.1.4 Frames multiplexing       119         11.1.5 Relations with the partitioning       119         11.2 CAN frames       116         11.1.4 Frames multiplexing       119         11.2 The value of a partition       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124 <t< td=""><td></td><td>10.1</td><td>•</td><td><b>o o</b>,</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></t<>                                                |    | 10.1 | •         | <b>o o</b> ,                                            |     |     |     |   |     |   |       |

| 10.1.3 The main procedure       105         10.2 The pre-clustering       105         10.2.1 Definition       105         10.2.2 The pre-clustering algorithm       106         10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.2 CAN frames       116         11.3.5 Relations with the partitioning       117         11.5 Relations with the partitioning       119         11.6 Practical considerations for the frames multiplexing       119         11.2 The value of a partition       121         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.4.1 The FFD str                                                                                                                                                    |    |      |           |                                                         |     |     |     |   |     |   |       |

| 10.2 The pre-clustering       105         10.2.1 Definition       105         10.2.2 The pre-clustering algorithm       106         10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.1.2 CAN frames       116         11.1.4 Frames multiplexing       117         11.1.5 Relations with the partitioning       119         11.2.6 The cost as a bin packing problem       121         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.4.2 The frames packing algorithm for the cost investigation       125         11.5.1 The Kernighan & Lin strategy       127                                                                                                                                                             |    |      |           |                                                         |     |     |     |   |     |   |       |

| 10.2.1 Definition       105         10.2.2 The pre-clustering algorithm       106         10.3 The clustering       107         10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113 <b>11 Evaluating and improving a partition 115</b> 11.1 The CAN: A frame-oriented communication protocol       115         11.1.2 CAN frames       116         11.1.3 Format of a Standard CAN data frame       116         11.1.4 Frames multiplexing       117         11.1.5 Relations with the partitioning       119         11.2 CAN frames       117         11.1.5 Relations with the partitioning       119         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.3.2 Off-line packing algorithm for the cost investigation       125         11.4.1 The FFD str                                                                                                                                                                       |    | 10.2 |           | •                                                       |     |     |     |   |     |   |       |

| 10.2.2 The pre-clustering algorithm       106         10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.1.2 CAN frames       116         11.1.3 Format of a standard CAN data frame       116         11.1.4 Frames multiplexing       117         11.5 Relations with the partitioning       119         11.6 Practical considerations for the frames multiplexing       119         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.3.2 Off-line packing strategies       125         11.4.2 The frames packing algorithm for the cost investigation       126         11.5.1 The Kernighan & Lin strategy <td></td> <td>10.2</td> <td></td> <td>-</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> |    | 10.2 |           | -                                                       |     |     |     |   |     |   |       |

| 10.3 The clustering       107         10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.1.2 CAN frames       116         11.1.3 Format of a standard CAN data frame       116         11.1.4 Frames multiplexing       117         11.5 Relations with the partitioning       119         11.2 The value of a partition       121         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.4.1 The FFD strategy for the cost investigation       125         11.4.2 The frames packing algorithm for the cost investigation       126         11.4.1 The Kernighan & Lin strategy       127         11.5.1 The Kernighan & Lin strategy <td< td=""><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td></td></td<>           |    |      |           |                                                         |     |     |     |   |     |   |       |

| 10.3.1 Closeness metrics       107         10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.2 CAN frames       116         11.3 Format of a standard CAN data frame       116         11.4 Frames multiplexing       117         11.5 Relations with the partitioning       119         11.6 Practical considerations for the frames multiplexing       119         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.4.1 The FFD strategy for the cost estimation       125         11.4.2 The frames packing algorithm for the cost investigation       126         11.5.1 The Kernighan & Lin strategy       127         11.5.2 The impro                                                                                                                 |    | 10.3 |           |                                                         |     |     |     |   |     |   |       |

| 10.3.2 The closeness function       110         10.3.3 The QT clustering algorithm       111         10.3.4 Conclusion       113         11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.2 CAN frames       116         11.1.3 Format of a standard CAN data frame       116         11.1.4 Frames multiplexing       117         11.1.5 Relations with the partitioning       119         11.1.6 Practical considerations for the frames multiplexing       119         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.4.1 The FFD strategy for the cost estimation       125         11.4.2 The frames packing algorithm for the cost investigation       126         11.5.1 The Kernighan & Lin strategy       127         11.5.2 The improvement technique       128         11.5.3 The improvement procedure       130                                                                                                                            |    | 10.5 |           | •                                                       |     |     |     |   |     |   |       |

| 10.3.3 The QT clustering algorithm11110.3.4 Conclusion113 <b>11 Evaluating and improving a partition115</b> 11.1 The CAN: A frame-oriented communication protocol11511.1.1 Organization of a CAN network11511.2 CAN frames11611.1.3 Format of a standard CAN data frame11611.1.4 Frames multiplexing11711.1.5 Relations with the partitioning11911.1.6 Practical considerations for the frames multiplexing11911.2.1 The cost function12111.2.2 The cost as a bin packing problem12211.3 Bin packing techniques12311.3.1 The Next Fit, the First Fit and the Best Fit strategies12311.3.2 Off-line packing strategies12411.4 Investigating the cost of a partition12511.4.1 The FFD strategy for the cost estimation12511.4.2 The frames packing algorithm for the cost investigation12611.5.1 The Kernighan & Lin strategy12711.5.2 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |      |           |                                                         |     |     |     |   |     |   |       |

| 10.3.4 Conclusion113 <b>11 Evaluating and improving a partition115</b> 11.1 The CAN: A frame-oriented communication protocol11511.1.1 Organization of a CAN network11511.1.2 CAN frames11611.1.3 Format of a standard CAN data frame11611.1.4 Frames multiplexing11711.1.5 Relations with the partitioning11911.1.6 Practical considerations for the frames multiplexing11911.2.1 The value of a partition12111.2.2 The cost function12111.2.2 The cost as a bin packing problem12211.3 Bin packing techniques12311.3.1 The Next Fit, the First Fit and the Best Fit strategies12311.3.2 Off-line packing strategies12411.4 Investigating the cost of a partition12511.4.1 The FFD strategy for the cost estimation12511.4.2 The frames packing algorithm for the cost investigation12611.5 Improving the partition12711.5.1 The Kernighan & Lin strategy12711.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |    |      |           |                                                         |     |     |     |   |     |   |       |

| 11 Evaluating and improving a partition       115         11.1 The CAN: A frame-oriented communication protocol       115         11.1.1 Organization of a CAN network       115         11.1.2 CAN frames       116         11.1.3 Format of a standard CAN data frame       116         11.1.4 Frames multiplexing       117         11.5 Relations with the partitioning       119         11.6 Practical considerations for the frames multiplexing       119         11.2.1 The cost function       121         11.2.2 The cost as a bin packing problem       122         11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.4.1 The FFD strategy for the cost estimation       125         11.4.2 The frames packing algorithm for the cost investigation       126         11.5 Improving the partition       127         11.5.1 The Kernighan & Lin strategy       127         11.5.2 The improvement procedure       130                                                                                                                                                                                                                                                                           |    |      |           |                                                         |     |     |     |   |     |   |       |

| 11.1The CAN: A frame-oriented communication protocol11511.1.1Organization of a CAN network11511.1.2CAN frames11611.1.3Format of a standard CAN data frame11611.1.4Frames multiplexing11711.1.5Relations with the partitioning11911.1.6Practical considerations for the frames multiplexing11911.2The value of a partition12111.2.1The cost function12111.2.2The cost as a bin packing problem12211.3Bin packing techniques12311.3.1The Next Fit, the First Fit and the Best Fit strategies12311.3.2Off-line packing strategies12411.4Investigating the cost of a partition12511.4.1The FFD strategy for the cost estimation12611.5Improving the partition12711.5.1The Kernighan & Lin strategy12711.5.2The improvement technique12811.5.3The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |      | 10.5.1 C  |                                                         | • • | • • | • • | • | ••• | • | . 115 |

| 11.1.1 Organization of a CAN network11511.1.2 CAN frames11611.1.3 Format of a standard CAN data frame11611.1.4 Frames multiplexing11711.1.5 Relations with the partitioning11911.1.6 Practical considerations for the frames multiplexing11911.2 The value of a partition12111.2.1 The cost function12111.2.2 The cost as a bin packing problem12211.3 Bin packing techniques12311.3.1 The Next Fit, the First Fit and the Best Fit strategies12311.4.1 The FD strategy for the cost estimation12511.4.2 The frames packing algorithm for the cost investigation12611.5 Improving the partition12711.5.2 The improvement technique12811.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 11 | Eval | uating ar | nd improving a partition                                |     |     |     |   |     |   | 115   |

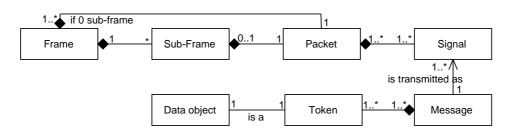

| 11.1.2 CAN frames11611.1.3 Format of a standard CAN data frame11611.1.4 Frames multiplexing11711.1.5 Relations with the partitioning11911.1.6 Practical considerations for the frames multiplexing11911.2 The value of a partition12111.2.1 The cost function12111.2.2 The cost as a bin packing problem12211.3 Bin packing techniques12311.3.1 The Next Fit, the First Fit and the Best Fit strategies12311.4.1 The FD strategy for the cost estimation12511.4.2 The frames packing algorithm for the cost investigation12611.5 Improving the partition12711.5.2 The improvement technique12811.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 11.1 | The CAN   | N: A frame-oriented communication protocol              |     |     |     |   |     |   | . 115 |

| 11.1.3Format of a standard CAN data frame11611.1.4Frames multiplexing11711.1.5Relations with the partitioning11911.1.6Practical considerations for the frames multiplexing11911.2The value of a partition12111.2.1The cost function12111.2.2The cost as a bin packing problem12211.3Bin packing techniques12311.3.1The Next Fit, the First Fit and the Best Fit strategies12311.3.2Off-line packing strategies12411.4Investigating the cost of a partition12511.4.1The FFD strategy for the cost estimation12511.4.2The frames packing algorithm for the cost investigation12611.5Improving the partition12711.5.1The Kernighan & Lin strategy12711.5.3The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |      | 11.1.1 C  | Organization of a CAN network                           |     |     |     |   |     |   | . 115 |

| 11.1.4Frames multiplexing11711.1.5Relations with the partitioning11911.1.6Practical considerations for the frames multiplexing11911.2The value of a partition12111.2.1The cost function12111.2.2The cost as a bin packing problem12211.3Bin packing techniques12311.3.1The Next Fit, the First Fit and the Best Fit strategies12311.3.2Off-line packing strategies12411.4Investigating the cost of a partition12511.4.1The FFD strategy for the cost estimation12511.4.2The frames packing algorithm for the cost investigation12611.5Improving the partition12711.5.1The Kernighan & Lin strategy12711.5.2The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |      | 11.1.2 (  | CAN frames                                              |     |     |     |   |     |   | . 116 |

| 11.1.5 Relations with the partitioning11911.1.6 Practical considerations for the frames multiplexing11911.2 The value of a partition12111.2.1 The cost function12111.2.2 The cost as a bin packing problem12211.3 Bin packing techniques12311.3.1 The Next Fit, the First Fit and the Best Fit strategies12311.3.2 Off-line packing strategies12411.4 Investigating the cost of a partition12511.4.1 The FFD strategy for the cost estimation12611.5 Improving the partition12711.5.1 The Kernighan & Lin strategy12711.5.2 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |      | 11.1.3 F  | Format of a standard CAN data frame                     |     |     |     |   |     |   | . 116 |

| 11.1.6 Practical considerations for the frames multiplexing11911.2 The value of a partition12111.2.1 The cost function12111.2.2 The cost as a bin packing problem12211.3 Bin packing techniques12311.3.1 The Next Fit, the First Fit and the Best Fit strategies12311.3.2 Off-line packing strategies12411.4 Investigating the cost of a partition12511.4.1 The FFD strategy for the cost estimation12611.5 Improving the partition12711.5.1 The Kernighan & Lin strategy12711.5.2 The improvement procedure12811.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |      | 11.1.4 F  | rames multiplexing                                      |     |     |     |   |     |   | . 117 |

| 11.2 The value of a partition12111.2.1 The cost function12111.2.2 The cost as a bin packing problem12211.3 Bin packing techniques12311.3.1 The Next Fit, the First Fit and the Best Fit strategies12311.3.2 Off-line packing strategies12411.4 Investigating the cost of a partition12511.4.1 The FFD strategy for the cost estimation12611.5 Improving the partition12711.5.1 The Kernighan & Lin strategy12711.5.2 The improvement technique12811.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |      | 11.1.5 F  | Relations with the partitioning                         |     |     |     |   |     |   | . 119 |

| 11.2.1 The cost function12111.2.2 The cost as a bin packing problem12211.3 Bin packing techniques12311.3.1 The Next Fit, the First Fit and the Best Fit strategies12311.3.2 Off-line packing strategies12411.4 Investigating the cost of a partition12511.4.1 The FFD strategy for the cost estimation12511.4.2 The frames packing algorithm for the cost investigation12611.5 Improving the partition12711.5.1 The Kernighan & Lin strategy12711.5.2 The improvement technique12811.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |      | 11.1.6 F  | Practical considerations for the frames multiplexing    |     |     |     |   |     |   | . 119 |

| 11.2.2 The cost as a bin packing problem12211.3 Bin packing techniques12311.3.1 The Next Fit, the First Fit and the Best Fit strategies12311.3.2 Off-line packing strategies12411.4 Investigating the cost of a partition12511.4.1 The FFD strategy for the cost estimation12511.4.2 The frames packing algorithm for the cost investigation12611.5 Improving the partition12711.5.1 The Kernighan & Lin strategy12711.5.2 The improvement technique12811.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    | 11.2 | The valu  | e of a partition                                        |     |     |     |   |     |   | . 121 |

| 11.3 Bin packing techniques       123         11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.4.1 The FFD strategy for the cost estimation       125         11.4.2 The frames packing algorithm for the cost investigation       126         11.5 Improving the partition       127         11.5.1 The Kernighan & Lin strategy       127         11.5.2 The improvement technique       128         11.5.3 The improvement procedure       130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |      | 11.2.1 T  | The cost function                                       |     |     |     |   |     |   | . 121 |

| 11.3.1 The Next Fit, the First Fit and the Best Fit strategies       123         11.3.2 Off-line packing strategies       124         11.4 Investigating the cost of a partition       125         11.4.1 The FFD strategy for the cost estimation       125         11.4.2 The frames packing algorithm for the cost investigation       126         11.5 Improving the partition       127         11.5.1 The Kernighan & Lin strategy       127         11.5.2 The improvement technique       128         11.5.3 The improvement procedure       130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |      | 11.2.2 T  | The cost as a bin packing problem                       |     |     |     |   |     |   | . 122 |

| 11.3.2 Off-line packing strategies12411.4 Investigating the cost of a partition12511.4.1 The FFD strategy for the cost estimation12511.4.2 The frames packing algorithm for the cost investigation12611.5 Improving the partition12711.5.1 The Kernighan & Lin strategy12711.5.2 The improvement technique12811.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 11.3 | Bin pack  | ing techniques                                          |     |     |     |   |     |   | . 123 |

| 11.4 Investigating the cost of a partition       125         11.4.1 The FFD strategy for the cost estimation       125         11.4.2 The frames packing algorithm for the cost investigation       126         11.5 Improving the partition       127         11.5.1 The Kernighan & Lin strategy       127         11.5.2 The improvement technique       128         11.5.3 The improvement procedure       130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |      | 11.3.1 T  | The Next Fit, the First Fit and the Best Fit strategies |     |     |     |   |     |   | . 123 |

| 11.4.1 The FFD strategy for the cost estimation12511.4.2 The frames packing algorithm for the cost investigation12611.5 Improving the partition12711.5.1 The Kernighan & Lin strategy12711.5.2 The improvement technique12811.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |      | 11.3.2 C  | Off-line packing strategies                             |     |     |     |   |     |   | . 124 |

| 11.4.2 The frames packing algorithm for the cost investigation12611.5 Improving the partition12711.5.1 The Kernighan & Lin strategy12711.5.2 The improvement technique12811.5.3 The improvement procedure130                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    | 11.4 | Investiga | ting the cost of a partition                            |     |     |     |   |     |   | . 125 |