### Design, Control and Analysis of a Novel Multilevel Converter with a Reduced Switch Count

vorgelegt von M. Sc. Margarita A. Norambuena Valdivia geb. in Viña del Mar

von der Fakultät IV - Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

> Doktor der Ingenieurwissenschaften -Dr.-Ing-

> > genehmigte Dissertation

Promotionsausschuss: Vorsitzender: Prof. Dr. Marcelo Pérez (UTFSM) Gutachterin: Prof. Dr.-Ing. Sibylle Dieckerhoff (TU Berlin) Gutachter: Prof. Dr.-Ing. José Rodríguez Pérez (UNAB) Prof. Dr.-Ing. Ralph Kennel (TU München) Dr. Samir Kouro Raener (UTFSM)

Tag der wissenschaftlichen Aussprache: 20. October 2017

Berlin, 2018.

U. Técnica Federico Santa María - Technische Universität Berlin Departamento de Ingeniería Electrónica - Faculty IV - Elektrotechnik und Informatik Valparaíso, Chile - Berlin, Deutschland

## Design, Control and Analysis of a Novel Multilevel Converter with a Reduced Switch Count

Margarita A. Norambuena Valdivia

2018

### Acknowledgments

This PhD project has been done under the guidance of the Chair of Industrial Electronics of the Electronic Department at the Universidad Técnica Federico Santa María (UTFSM), Valparaíso, Chile and the Chair of the Research group of Power Electronics at Faculty IV - Electrical Engineering and Computer Science at Technische Universität Berlin (TUB), Berlin, Germany. The four years I have spent on this PhD have been very interesting and educational. I would never have been able to finish my PhD dissertation without the guidance of my supervisors.

Firstly, I would like to express my deepest gratitude to my supervisor Prof. Dr.-Ing. José Rodríguez for his constant guidance, helpful comments, advice, interest, and support. Prof. Rodríguez has always given me the confidence and security to think with freedom and to implement my new ideas. I am profoundly happy to have him as my supervisor; he is a very interesting person, he always gave me some of his time when I needed it, and was always available to talk, not only about my PhD work, but also about new tendencies in the world, good music and the best places to go visit.

My deepest gratitude goes also to my supervisor Prof. Dr.-Ing. Sibylle Dieckerhoff for accepting me, for her interest, helpful comments, advice, and support. Prof. Dieckerhoff gave me the space, the opportunity and the trust to convert my ideas into reality. I cannot imagine being able to finish my PhD dissertation without her assistance and support. She is very meticulous, organized, clear in her goals and in the steps that must be followed and I admire her for that.

I would like to thank Prof. Dr. Samir Kouro for being the co-supervisor of my PhD dissertation from the UTFSM. His comment about a new back-to-back two-level converter was the cornerstone that made this PhD dissertation possible.

Besides my supervisors, I would like to thank Prof. Dr.-Ing. Ralph Kennel for being the fourth examiner for this dissertation.

My sincere thanks go to my colleagues at TUB and UTFSM; I would especially like to express my gratitude to Tino Kahl for his help and friendship during my stay in Berlin and thereafter. Tino has a wide knowledge and experience with building PCBs, and without his help and comments my work would have taken more time and I would probably still be stuck making beginner mistakes.

I would like to thank the administrative and technical staff members from TUB who have been kind enough to advise and help in their respective roles. I thank Mrs. Gudrun Pourshirazi for her help, cooperation and time.

I would like to thank my parents and siblings for supporting me spiritually as I wrote this dissertation and throughout my life in general, even when geographical distance has

#### separated us.

I am grateful for the support of the Chilean Research Council(CONICYT) under grant "Doctorado Nacional 2014" (21140574), FONDECYT under grant 1170167 and also the support of German Academic Exchange Service (DAAD) under the grant "Bi-nationally Supervised Doctoral Degrees" (57129430) for funding my PhD project period.

Y por último, agradezco a la persona más trascendental de mi vida, porque sin ella jamás hubiera podido llegar hasta donde estoy, mi Padre Dios es lo más importante que podría llegar a tener. Todo por él y nada sin él.

# **Table of Contents**

| Tabl | e of Conte                                                                                                             | ents I                                                                                                                                                                                                                                   |

|------|------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figu | res Index                                                                                                              | ш                                                                                                                                                                                                                                        |

| Tabl | es Index                                                                                                               | v                                                                                                                                                                                                                                        |

| Abst | tract                                                                                                                  | 1                                                                                                                                                                                                                                        |

| Resi | umen                                                                                                                   | 2                                                                                                                                                                                                                                        |

| Kurz | fassung                                                                                                                | 3                                                                                                                                                                                                                                        |

| 1.   | Introduc                                                                                                               | tion 4                                                                                                                                                                                                                                   |

| 2.   | <ul> <li>2.1. Neu<br/>2.1.1.</li> <li>2.1.2.</li> <li>2.1.3.</li> <li>2.1.4.</li> <li>2.2. Activ<br/>2.2.1.</li> </ul> | I Converters7tral Point Clamped (NPC) Converter7The power circuit7Vectors generated by the inverter8The classical modulation11Summary12ve Neutral Point Clamped (ANPC) Converter13The power circuit13Vectors generated by the inverter14 |

|      | 2.2.3.<br>2.2.4.<br>2.3. Flyir<br>2.3.1.<br>2.3.2.                                                                     | The classical modulation16Summary17ng Capacitor Converter (FCC)18The power circuit18Vectors generated by the inverter18The classical modulation20                                                                                        |

|      | 2.3.4.<br>2.4. Stac<br>2.4.1.<br>2.4.2.<br>2.4.3.                                                                      | Summary21cked Multicell Converter (SMC)23The power circuit23Vectors generated by the inverter23The classical modulation25Summary26                                                                                                       |

| 3.  | Reduced Multilevel Converter                                   | 28   |

|-----|----------------------------------------------------------------|------|

|     | 3.1. Basic properties                                          | . 29 |

|     | 3.2. Operation principle                                       | . 33 |

|     | 3.2.1. Analysis of constraints                                 | . 38 |

|     | 3.2.2. Implementation in Medium Voltage                        | . 39 |

|     | 3.2.3. Remark about the number of output levels                |      |

|     | 3.3. Mathematical model                                        |      |

|     | 3.4. The Classic Modulation                                    | . 42 |

| 4.  | Control Strategy: Model Predictive Control                     | 46   |

|     | 4.1. Classification of MPC                                     | . 46 |

|     | 4.1.1. Explicit Model Predictive Control (EMPC)                | . 47 |

|     | 4.1.2. Finite Control Set - Model Predictive Control (FCS-MPC) |      |

|     | 4.2. Summary                                                   |      |

|     | 4.3. MPC implementation strategy                               |      |

|     | 4.4. FCS-MPC applied to a Reduced Multilevel Converter         |      |

|     |                                                                |      |

| 5.  | RMC: Analysis and Performance                                  | 55   |

|     | 5.1. System Response                                           |      |

|     | 5.1.1. 3-Level Topologies                                      |      |

|     | 5.1.1.a. Cost Function Definition                              |      |

|     | 5.1.1.b. Simulation Results                                    |      |

|     | 5.1.2. 5-Level Topologies                                      |      |

|     |                                                                |      |

|     | 5.1.2.b. Simulation Results                                    |      |

|     | 5.2. Characteristics of the Structure                          |      |

|     | 5.2.1. Blocking voltage                                        |      |

|     | 5.2.2. Switching frequency                                     |      |

|     | 5.2.3. Switching and conduction losses                         |      |

|     | 5.2.4. Energy storage and size of the inner capacitors         |      |

|     | 5.3. Comments                                                  |      |

|     | 5.4. Back-to-Back RMC                                          | . 76 |

| 6.  | Experimental Validation                                        | 82   |

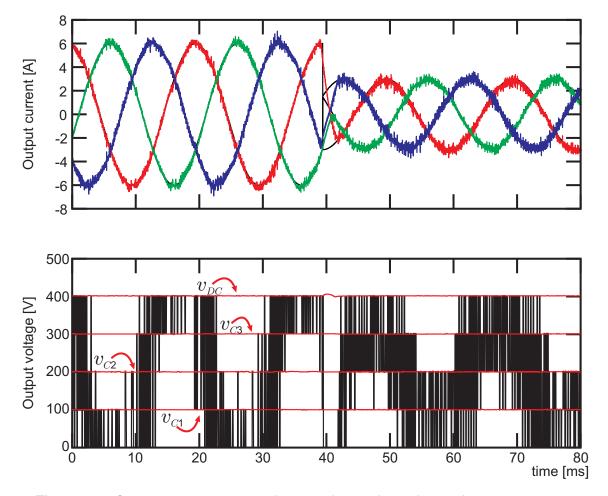

|     | 6.1. Steady State Behavior                                     | . 82 |

|     | 6.2. Dynamic Response                                          | . 88 |

| 7.  | Conclusions and Future Outlook                                 | 90   |

| Ар  | pendix                                                         | 92   |

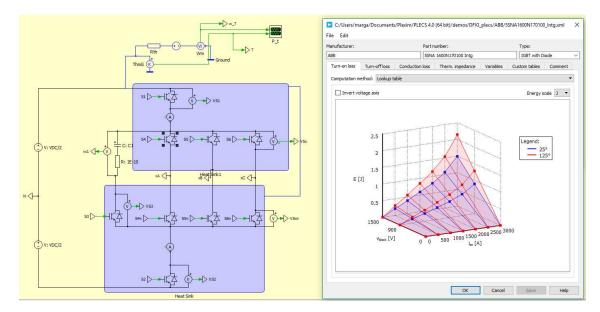

| Α.  | Calculation of losses                                          | 92   |

|     |                                                                |      |

| Ар  | pendix                                                         | 94   |

| В.  | Test Bench                                                     | 94   |

| Bib | liography                                                      | 96   |

# **Figures Index**

| 2.1.  | Three Phase Inverter 3-level NPC.                                        | 8   |

|-------|--------------------------------------------------------------------------|-----|

| 2.2.  | NPC inverter output                                                      | 9   |

| 2.3.  | Space vectors of NPC.                                                    | 10  |

| 2.4.  | Switching state for $\mathbf{V}_0$ . $S = \{+, +, +\}$ .                 | 11  |

| 2.5.  | Switching state for $V_1$ . $S = \{+, 0, 0\}$ .                          | 11  |

| 2.6.  | Block diagram of Level Shifted-PWM modulation.                           | 11  |

| 2.7.  | Classic Level Shifted-PWM modulation.                                    | 12  |

| 2.8.  | 1-Phase 5-level ANPC Inverter.                                           | 13  |

| 2.9.  | Possible switching states of an 5L-ANPC                                  | 14  |

| 2.10. | Space vectors of 5L-ANPC.                                                | 15  |

| 2.11. | Block diagram of PS-PWM modulation for a 5L-ANPC.                        | 16  |

| 2.12. | Classic PWM modulation for a 5L-ANPC.                                    | 17  |

| 2.13. | 1-Phase Inverter 5-level FCC.                                            | 18  |

| 2.14. |                                                                          | 20  |

| 2.15. |                                                                          | 21  |

| 2.16. | Classic Phase Shifted-PWM modulation.                                    | 21  |

| 2.17. | Topology of one phase of a Stacked Multicell Converter 2x2.              | 23  |

| 2.18. | Switching states not allowed in a SMC 2x2                                | 24  |

| 2.19. | •                                                                        | 25  |

| 2.20. | Block diagram of the classical modulation for an SMC 2x2.                | 26  |

| 2.21. | Classical modulation of a SMC 2x2.                                       |     |

|       |                                                                          |     |

| 3.1.  | Five Level Reduced Multilevel Converter (5L-RMC), with 3 DC-cell and     | ~~  |

|       | a 2L-VSI output inverter.                                                | 28  |

| 3.2.  |                                                                          | 29  |

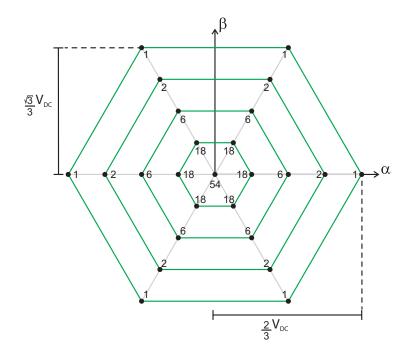

| 3.3.  | Total possible output voltage vector in 5L-RMC.                          | 31  |

| 3.4.  | Output voltage space vectors generated by the RMC, including their       | ~ 4 |

|       | numbers of redundancies.                                                 | 34  |

| 3.5.  | Different DC-cell switching states (only non-redundant states are shown) | ~ - |

| • •   | and their respective output potentials for a 5L-RMC.                     | 35  |

| 3.6.  | Possible DC-DC voltage combinations in 1DC-cell RMC.                     | 36  |

| 3.7.  | Output voltage of the 3L-RMC for different cases                         | 37  |

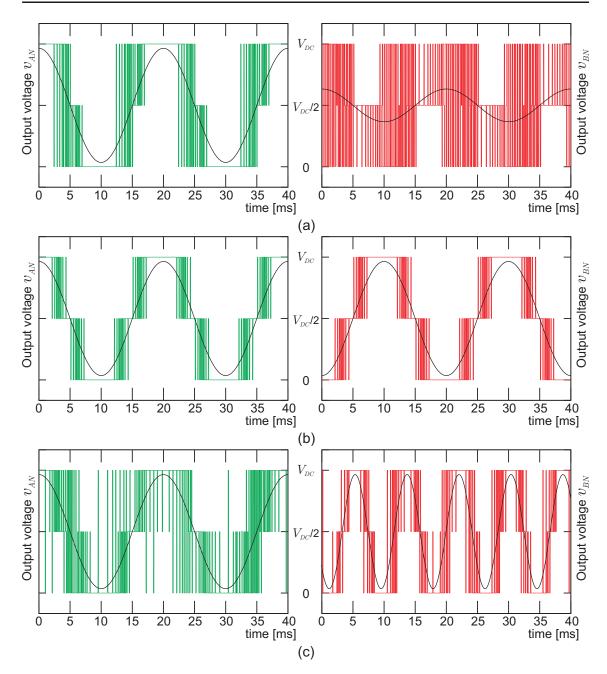

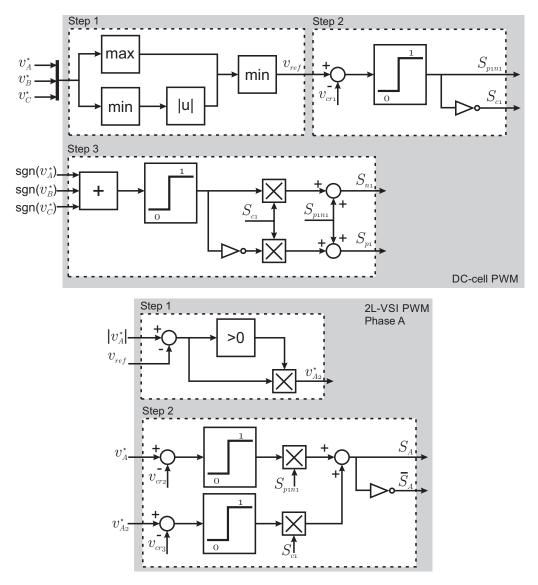

| 3.8.  | Block diagram of PWM modulation for a 3L-RMC.                            | 43  |

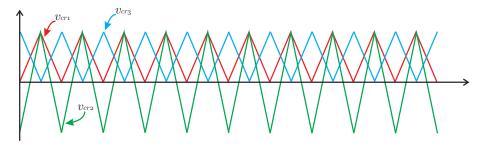

| 3.9.  | Carrier signals in the PWM modulation for a 3L-RMC.                      | 44  |

| 3.10. | RMC 3-phase RMC modulation                                               | 45  |

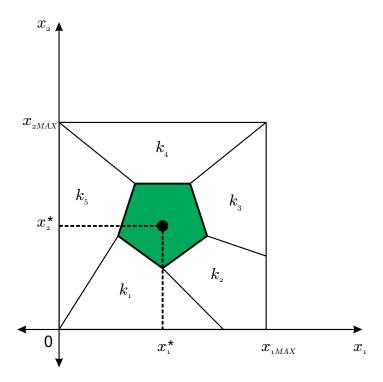

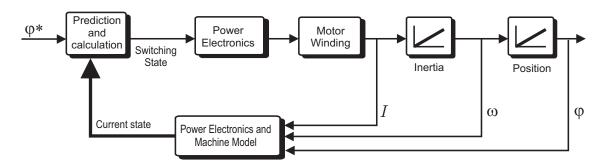

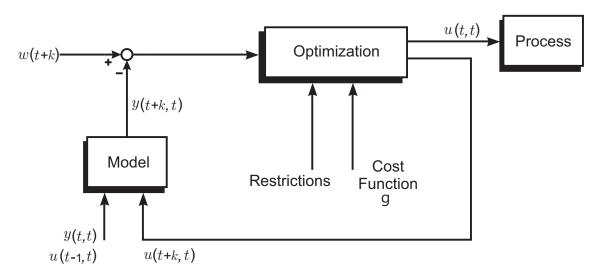

| 4.1.  | Structure of an explicit predictive control.                             | 48  |

| 4.2.  | Structure of a direct predictive control.                                | 49  |

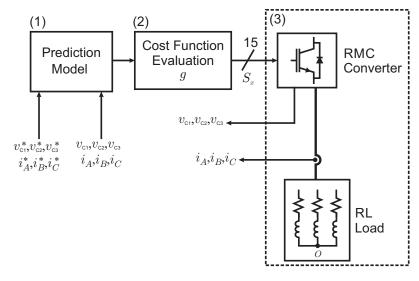

| 4.3.  | Predictive Control Strategy.                                             |     |

| 4.4.         | Control scheme for FCS-MPC.                                                            | 54 |

|--------------|----------------------------------------------------------------------------------------|----|

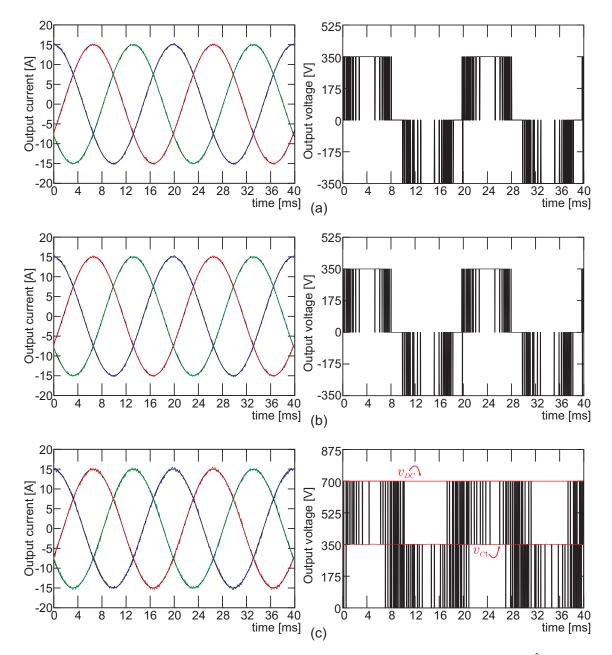

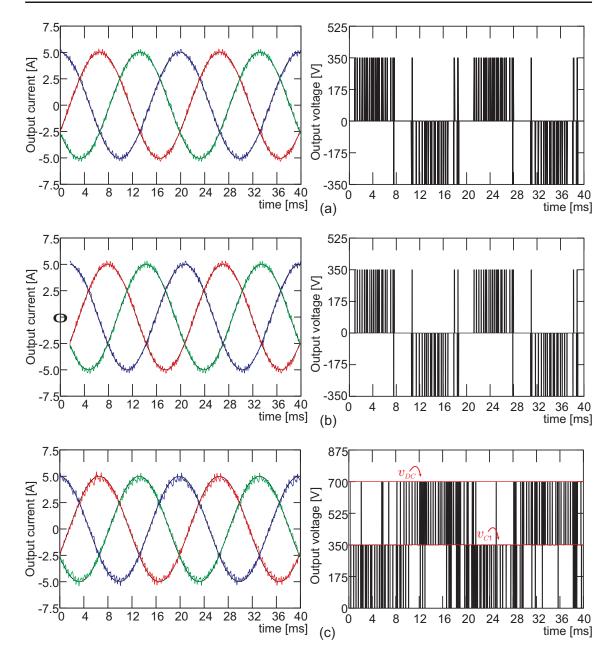

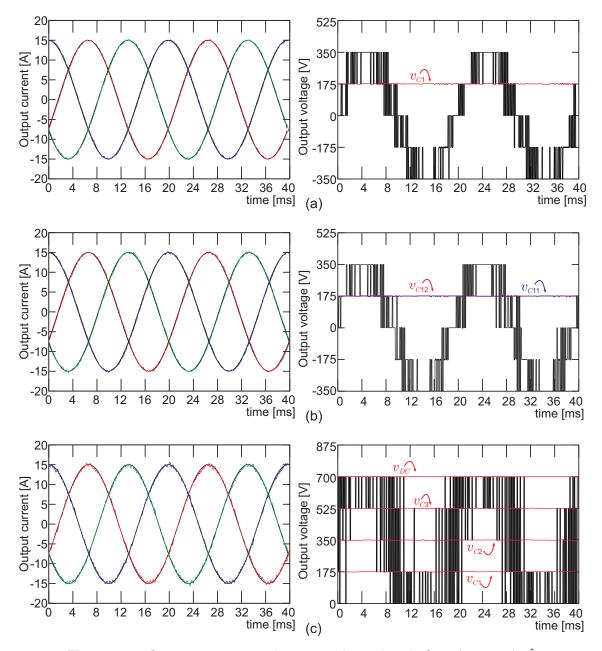

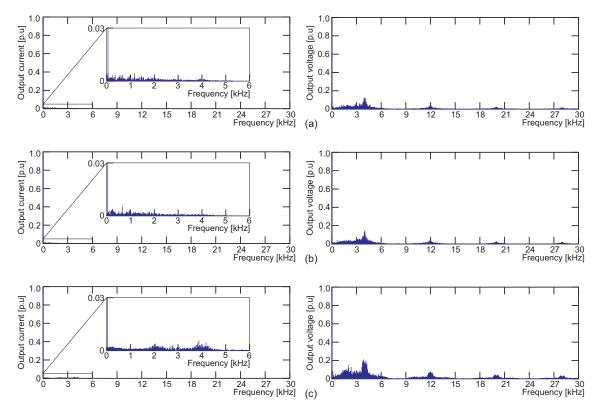

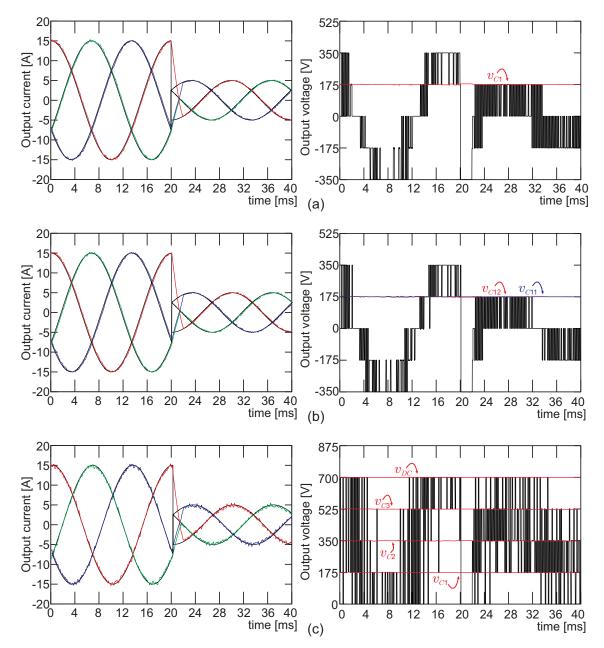

| 5.1.<br>5.2. | Output currents and output voltage 3-level 15A                                         |    |

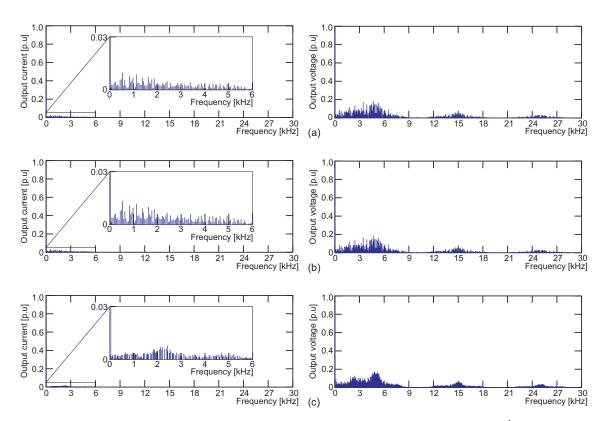

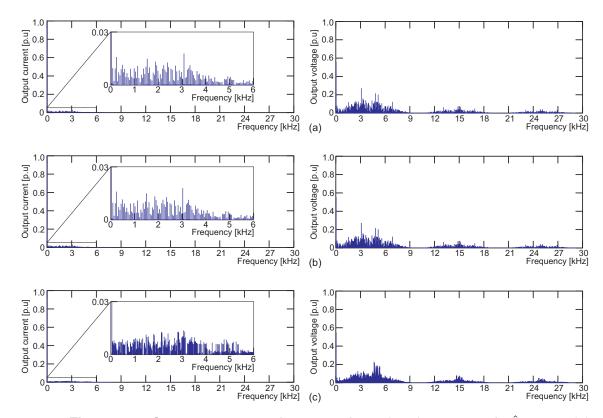

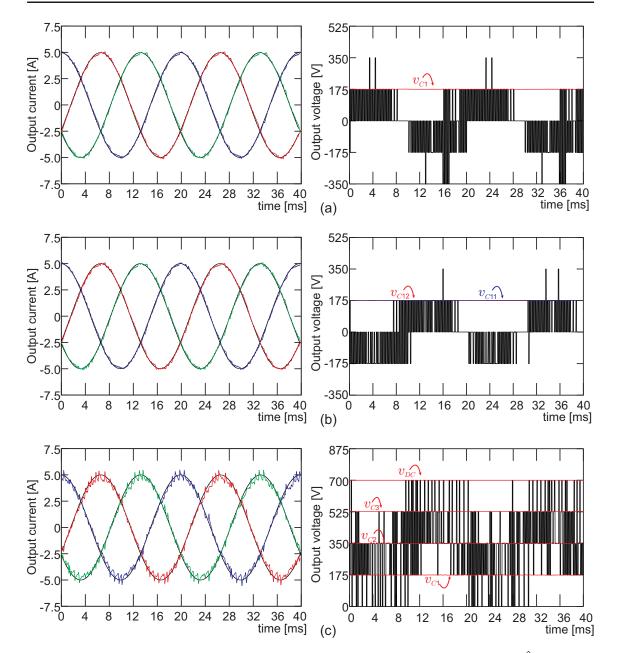

| 5.3.         | Output current and output voltage spectrum 3-level 15A                                 |    |

| 5.4.         | Output current and output voltage spectrum 3-level 5A                                  |    |

| 5.5.         | Output currents and output voltage 3-level                                             | 61 |

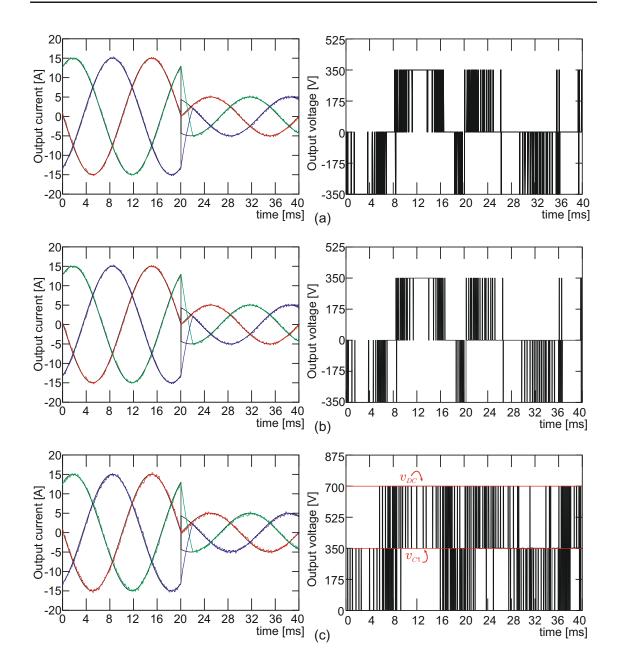

| 5.6.         | Output currents and output voltage 5-level 15A                                         | 63 |

| 5.7.         | Output currents and output voltage 5-level 5A                                          | 64 |

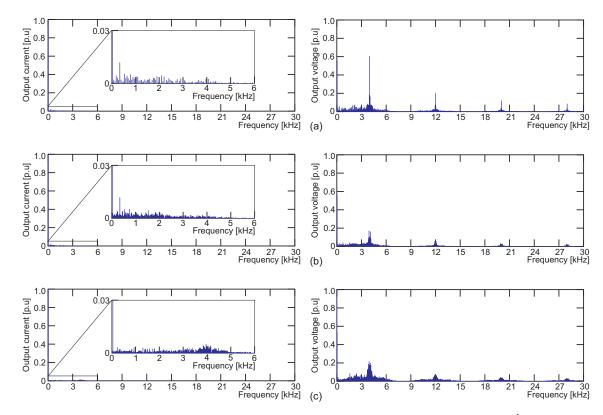

| 5.8.         | Output current and output voltage spectrum 5-level 15A                                 | 65 |

| 5.9.         | Output current and output voltage spectrum 5-level 5A                                  | 66 |

| 5.10.        | Output currents and output voltage 5-level                                             | 67 |

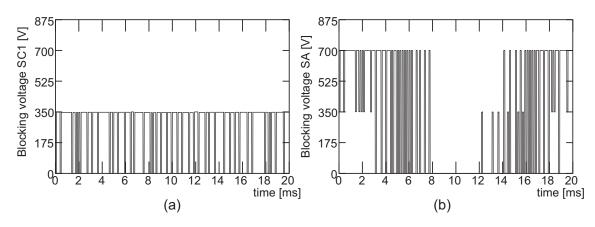

| 5.11.        | Blocking voltage in 3-level RMC                                                        | 69 |

| 5.12.        | Blocking voltage in 5-level RMC                                                        | 69 |

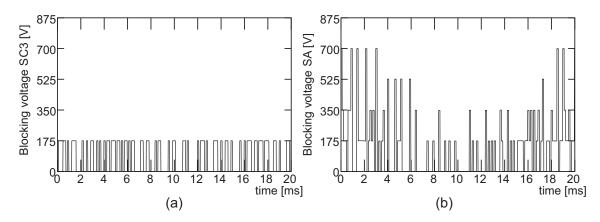

| 5.13.        | Switching and conduction power losses for: (a) 3-level topologies, (b)                 | 72 |

| 5.14.        | 5-level topologies                                                                     | 74 |

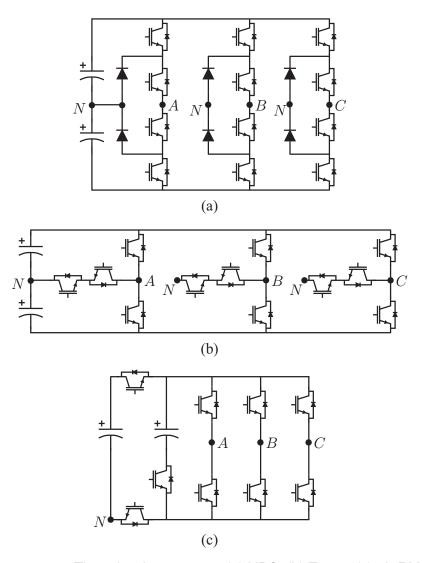

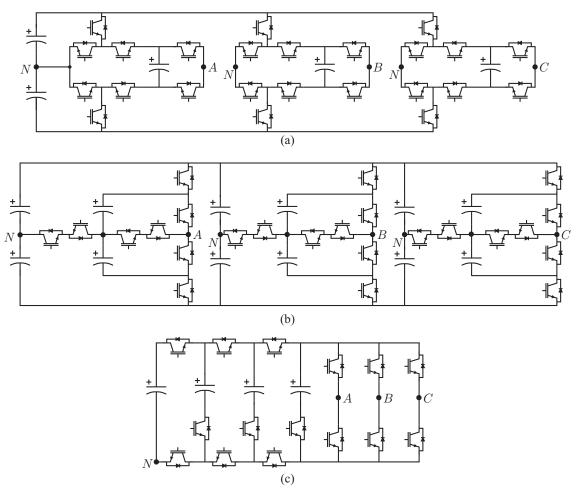

| 5.15.        | Five-level converters: (a) ANPC; (b) SMC; (c) 5L-RMC.                                  | 75 |

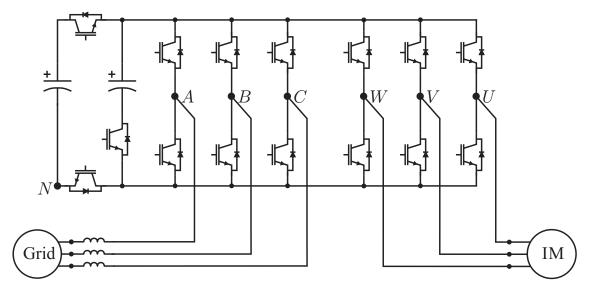

| 5.16.        | 3L-RMC back-to-back connection.                                                        | 76 |

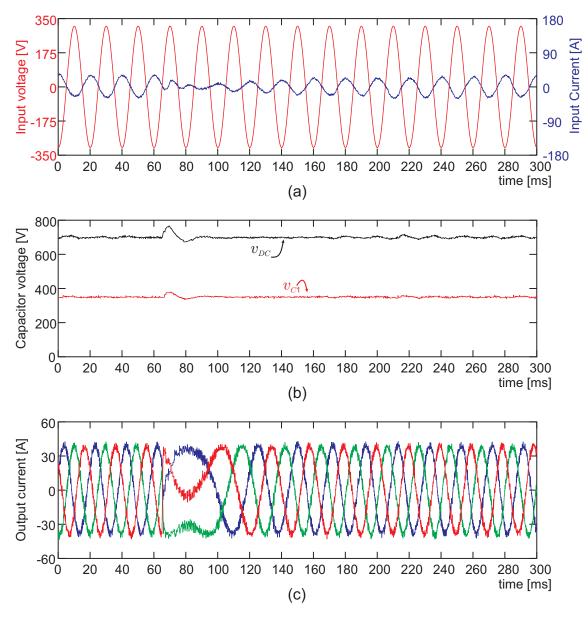

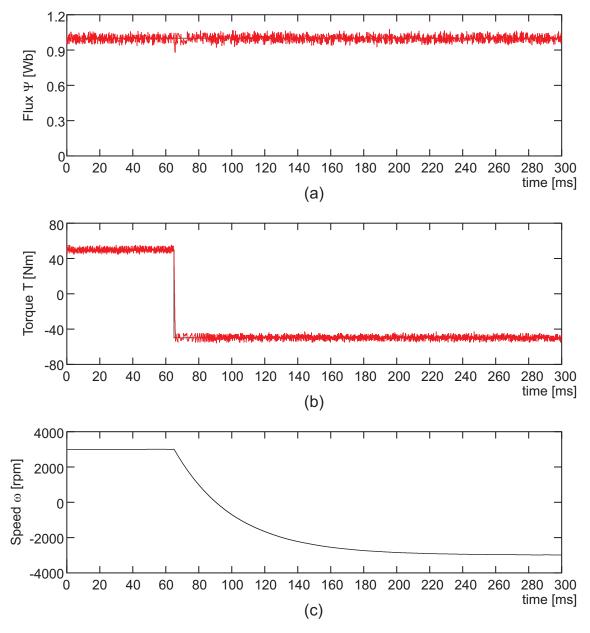

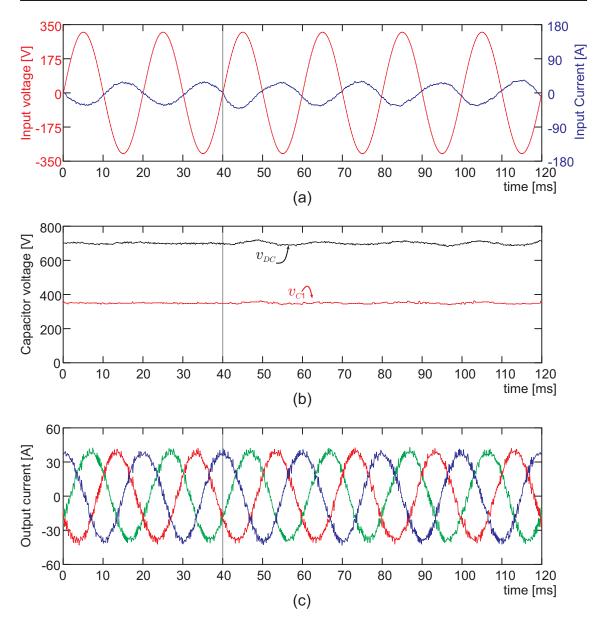

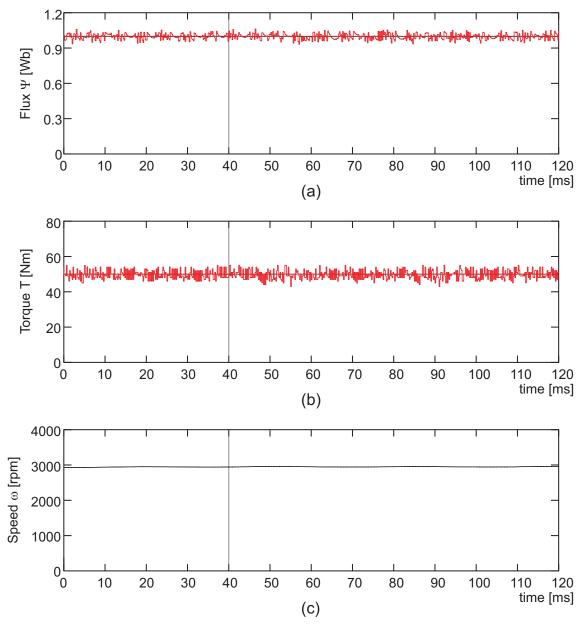

| 5.17.        | RMC back-to-back: electric variables Torque step                                       | 78 |

| 5.18.        | RMC back-to-back: mechanic variables Torque step                                       | 79 |

| 5.19.        | RMC back-to-back: electric variables power step                                        | 80 |

| 5.20.        | RMC back-to-back: mechanic variables power step                                        | 81 |

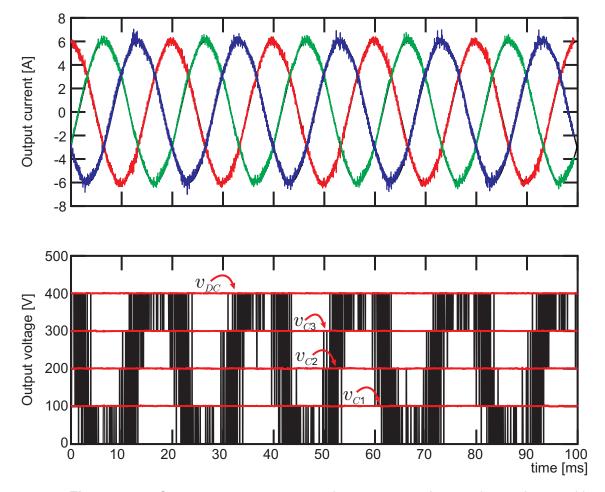

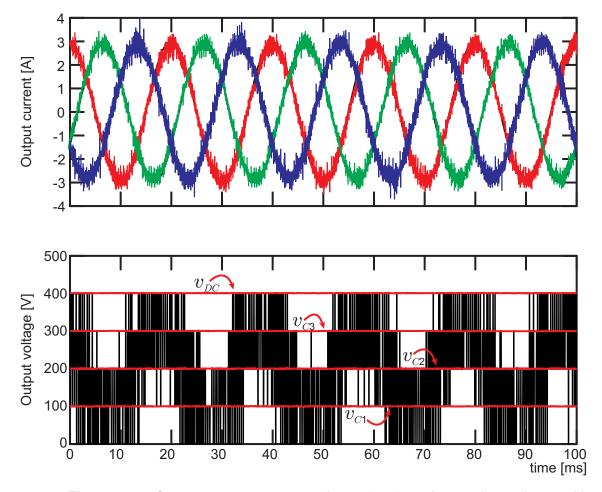

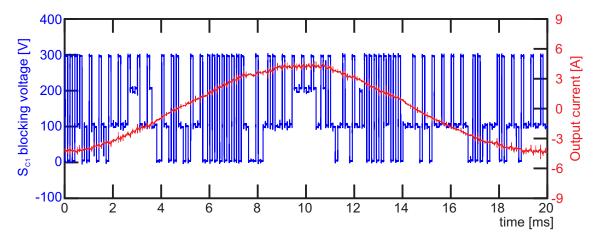

| 6.1.         | Output current, output voltage, $v_{AN}$ , and capacitor voltage 6A                    | 83 |

| 6.2.         | Output current, output voltage $(v_{AN})$ and capacitor voltage 3A                     | 84 |

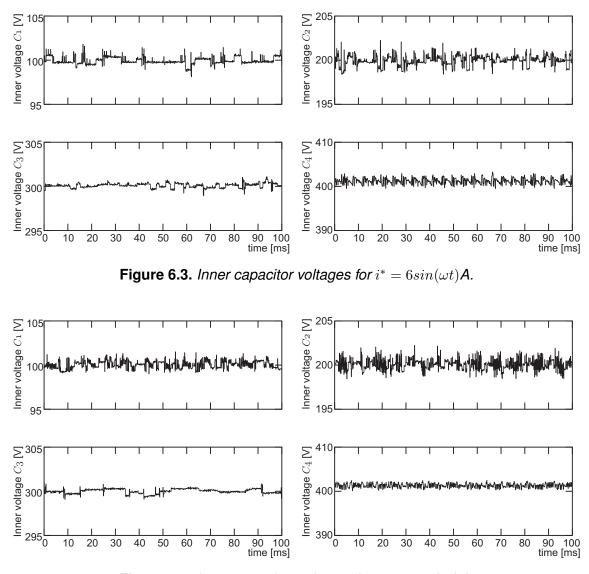

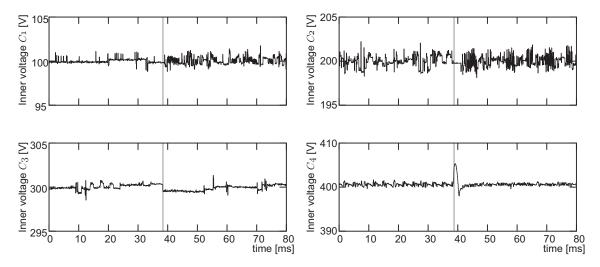

| 6.3.         | Inner capacitor voltages for $i^* = 6sin(\omega t)A$ .                                 |    |

| 6.4.         | Inner capacitor voltages for $i^* = 3sin(\omega t)A$ .                                 | 85 |

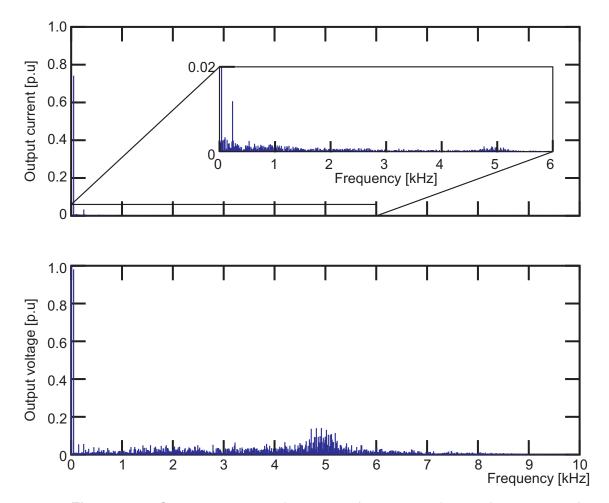

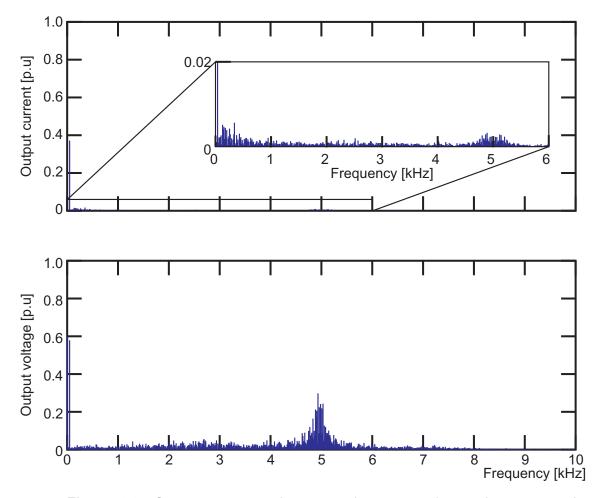

| 6.5.         | Output current and output voltage, $v_{AN}$ , harmonic spectrum 6A                     | 86 |

| 6.6.         | Output current and output voltage, $v_{AN}$ , harmonic spectrum 3A                     |    |

| 6.7.         | Output current and blocking voltage in power switch $S_{C1}$ .                         | 87 |

| 6.8.         | Inner capacitor voltages.                                                              | 88 |

| 6.9.         | Output current, output voltage and capacitor voltage after a current step.             | 89 |

| A.1.         | $PLECS^{\mathbb{R}}$ simulation to calculate the converter's total losses              | 92 |

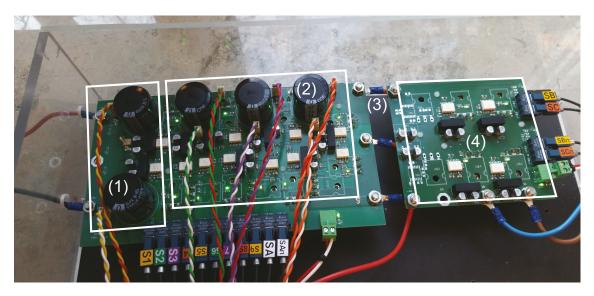

| B.1.         | RMC prototype: (1) dc-link capacitors; (2) DC-cells; (3) Variable dc-link; (4) 2L-VSI. | 94 |

# **Tables Index**

| 2.1.<br>2.2.<br>2.3.<br>2.4.                                                                   | Switching states Neutral Point ClampedSwitching states Active Neutral Point ClampedSwitching states Flying Capacitor ConverterSwitching states Stacked Multicell Converter                                                                                                                            | 15<br>19                               |

|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| <ol> <li>3.1.</li> <li>3.2.</li> <li>3.3.</li> <li>3.4.</li> <li>3.5.</li> <li>3.6.</li> </ol> | DC-cell RMC: Possible switching states                                                                                                                                                                                                                                                                | 31<br>32<br>33<br>38                   |

| 4.1.                                                                                           | Operating characteristics of EMPC and FCS-MPC                                                                                                                                                                                                                                                         | 50                                     |

| 5.1.<br>5.2.<br>5.3.<br>5.4.<br>5.5.<br>5.6.<br>5.7.<br>5.8.<br>5.9.                           | Simulation parameters<br>THD for 3-level topologies<br>THD for 5-level topologies<br>Blocking voltage for multilevel topologies<br>Average switching frequency<br>Switching frequency in 5-level RMC<br>Capacitance size<br>Capacitance size<br>Simulation parameters for the back-to-back connection | 59<br>66<br>68<br>70<br>71<br>73<br>73 |

| 6.1.                                                                                           | Test bench parameters.                                                                                                                                                                                                                                                                                | 82                                     |

| A.1.                                                                                           | Devices selected                                                                                                                                                                                                                                                                                      | 93                                     |

## Abstract

Multilevel converters are used in a wide range of applications, such as drives, energy conversion and distributed generation. This Thesis proposes a new multilevel converter topology that allows increasing the number of output voltage levels with a fewer required power semiconductors than in standard multilevel topologies such as Active Neutral Point Clamped (ANPC), Flying Capacitor Converter (FCC) and Stacked Multicell Converter (SMC).

The proposed topology consists of a cascaded connection of basic units called *main cells*, which are composed of three power switches, one flying capacitor and two output switches for each output phase.

In this Thesis, the comparisons are made between the proposed topology and conventional topologies such as ANPC and SMC. Points of comparison include the required number of power switches, voltage stress across the switches, power distribution, capacitors' size and energy storage.

To verify the performance of the proposed multilevel topology, extensive simulations and experimental studies were carried out on a 3-phase 5-level converter.

### Resumen

Los convertidores de potencia multinivel son empleados en una amplia gama de aplicaciones, incluyendo: máquinas y accionamientos, conversión de energía y generación distribuida. Esta Tesis propone una nueva topología de convertidor multinivel que permite incrementar el número de niveles de tensiones a la salida del convertidor empleando un reducido número de semiconductores de potencia en comparación con topologías multinivel convencionales, tales como el convertidor Active Neutral Point Clamped (ANPC), el convertidor Flying Capacitor (FCC) y el convertidor Stacked Multicell (SMC).

Esta topología está conformada por la conexión en cascada de unidades básicas llamadas *celdas principales*, que se componen por un condensador flotante y tres semiconductores de potencia, y dos semiconductores de potencia para seleccionar la salida de tensión correspondiente a cada fase del sistema.

En este trabajo se discute el número de semiconductores de potencia requeridos, el estrés de tensión a los que son sometidos, la distribución de potencia a través de ellos y la energía almacenada en los condensadores flotantes en comparación con topologías estándares y comerciales como los son el ANPC y el SMC.

La validación de la topología multinivel propuesta es verificada a través de simulaciones y resultados experimentales en un prototipo trifásico de 5 niveles.

## Kurzfassung

Mehrstufige Wechselrichter finden ein breites Anwendungsspektrum. Sie werden beispielsweise als Antriebsumrichter, in der Energieversorgung oder für verteilte Erzeugungsanlagen genutzt. Verglichen mit etablierten Schaltungen wie dem Active Neutral Point Clamped (ANPC) Converter, dem Flying Capacitor Converter (FCC) oder dem Stacked Multicell Converter (SMC) erreicht die in dieser Arbeit vorgestellte, neuartige Umrichter-Topologie eine erhöhte Stufenzahl der Ausgangsspannung bei reduzierter Anzahl an benötigten Leistungsschaltern.

Die vorgeschlagene Topologie besteht aus einer kaskadierten Verbindung aus Basiszellen, den "Main Cells" und jeweils zwei Leistungsschaltern für jede Ausgangsphase. Die Basiszellen sind aus drei Leistungsschaltern und einem Flying Capacitor aufgebaut. Sie erzeugen eine variable Zwischenkreisspannung für die angeschlossenen Ausgangsphasen.

In dieser Arbeit wird ein Vergleich zwischen der vorgestellten Topologie und den etablierten Schaltungen ANPC, FCC und SMC durchgeführt. Die Vergleichskriterien beinhalten die Anzahl an benötigten Leistungshalbleitern, die Sperrspannung über den einzelnen Schaltern, die Verlustleistungsverteilung sowie die in den Kondensatoren gespeicherte Energie und deren Kapazität.

Die Verhaltensweisen der vorgeschlagenen Topologie werden in umfangreichen Simulationen und experimentellen Untersuchungen eines dreiphasigen 5-Level Wechselrichters analysiert.

# **Chapter 1**

### Introduction

Voltage Source Converters (VSC) today have a wide variety of applications [1–3], such as:

- Industry: Pumps, ventilators, conveyors, mills, etc.

- Transportation: Trains, trucks, cars, airplane.

- Transmission and distribution of energy: wind farms, HVDC, STATCOMs, active filters, etc.

- Drives: Load side and grid side converter.

VSCs can behave as a rectifier (VSR-*Voltage Source Rectifier*) or as an inverter (VSI-*Voltage Source Inverter*) depending on the direction of the power flow. Therefore, it is a fully bidirectional structure.

Because of its simple structure and mature technology, the two-level VSC has been the most attractive option for industries [4]. However, the two-level VSC provides a poor voltage quality. Large harmonic content of the output voltage of a two-level VSC hampers its application in supplying sensitive loads and also in grid-connected energy conversion systems where strict grid codes should be followed. Adding harmonic filters to the output of a two-level VSC to improve the power quality results in a complex, expensive and bulky system that is less attractive for industrial applications.

Multilevel VSCs provide several voltage steps by which a more sinusoidal voltage waveform can be constructed. Multilevel converters have emerged as an attractive solution for power electronics applications due to their numerous merits over classical two-level converters; these advantages include better output voltage waveform quality, lower harmonic distortion of the input and output currents, reduced filter size, lower common-mode voltages, reduced electromagnetic interference, reduced torque ripple in drive applications and the feasibility of fault tolerant operation [5].

Multilevel converters consist of an array of semiconductor devices and capacitive voltage sources, which can generate output voltage waveforms with multiple steps by appropriate switching. With the increase in the number of output voltage levels or steps, the staircase output waveform approaches a sinusoidal waveform. The 3-level Neutral Point Clamped (NPC) converter is one of the classical multilevel topologies [6]. The NPC has become popular due to its simple structure, but it has not been extended to higher-level operation due to excessive losses of clamping diodes, uneven distribution of losses in inner and outer devices and the need to balance the capacitor voltages [7].

The concept of multicell converters introduced 20 years ago, allowed an important advance in the domain of medium voltage (3kV, 4.5kV, 6.6kV) and high power (several MW) applications. The development of static converters dedicated to high power applications is currently expanding. By using a series of connected commutation cells, the converters' input voltage can easily be increased and the waveform improved while using smaller components with better properties. The Flying Capacitor Converter (FCC) is an example of these topologies [8,9].

The Stacked Multicell Converter (SMC) is a novel multilevel converter topology in the same line as the flying capacitor converter; it allows converters to reach output voltage, output power and performances still higher than the classical multicell FCC [10].

Like the FCC, the SMC uses flying capacitors and the voltage across these flying capacitors have to be balanced to allow for a correct operation of multicell topologies. When Pulse Width Modulation (PWM) techniques are used, it is necessary to study natural balancing properties of the SMC converter, and when Model Predictive Control (MPC) is used, it is possible to control these internal voltages directly. Some external circuits (such as the RLC filter) can be used to increase the effectiveness of the voltage balancing.

Multilevel converters are a good candidate for supplying sensitive loads and being used in the grid-tied system, due to their good power quality, higher efficiency and superior electromagnetic compatibility (EMC) [11,12]. Different structures of multilevel converters have been reported in the literature in recent years. This thesis proposes a new multilevel converter structure that reduces the necessary number of power switches and flying capacitors to generate the same number of output levels as in classical topologies such as FCC, SMC and NPC.

The new multilevel topology is called Reduced Multilevel Converter (RMC); it consists of a cascaded connection of basic units called main cells (MC) and a 3-phase output inverter stage. The RMC is a multilevel inverter with a single DC-bus configuration. Every MC is formed by three power switches and one capacitor. The MCs work as a DC-DC multilevel converter, generating a variable *dc-link* as their output. The output inverter stage can be any inverter with a single DC-bus configuration like the 2L-VSI, Neutral Point Clamped (NPC), ANPC, T-type [13], FCC or Stacked Multicell Converter. However, in this work, the basic 2L-VSI is used so as to identify RMC's real contributions.

The upcoming chapters of this dissertation are organized as follows:

Chapter 2 presents a brief description of the main multilevel converter with a single DC-bus configuration that will be used to compare the performance of the RMC. These topologies are the Neutral Point Clamped (NPC) converter, the 5-level Active Neutral Point Clamped (5L-ANPC) converter, the Flying Capacitor Converter (FCC) and the Stacked Multicell Converter (SMC).

Chapter 3 presents the description of the proposed topology in this dissertation, the Reduced Multilevel Converter, its basic properties, operation principles and mathematical

model.

Chapter 4 gives a brief summary of Model Predictive Control (MPC), the control strategy used to control the proposed topology. This chapter describes the principal advantages and disadvantages of the MPC strategy and its implementation scheme.

Chapter 5 presents a simulation analysis of the proposed topology compared with the multilevel converters described in chapter 2. The analysis is made considering the system's response, i.e. output currents, output voltages, capacitor voltage balance, harmonic spectrum, total harmonic distortion and dynamic characteristic, and the characteristics of the structure, i.e. blocking voltage, switching frequency, switching and conduction losses, storage energy and size of the inner capacitors.

Chapter 6 presents an experimental validation of the designed topology using a 5L-RMC prototype.

Finally, Chapter 7 provides a brief summary of the whole dissertation and discusses some extended research ideas that can be carried out in the future.

# **Chapter 2**

### **Multilevel Converters**

Nowadays, multilevel inverters are a well accepted and mature technology for power electronic applications. In this work, the following types of multilevel inverters will be considered:

- **Neutral Point Clamped (NPC) converter:** A three-level NPC converter will be considered as the startup point to understand multilevel converters.

- Active Neutral Point Clamped (ANPC) converter: A five-level ANPC converter will be considered as a comparison point for 5-level commercial topologies.

- Flying Capacitor Converter (FCC): An FCC will be considered as the classical flying capacitor topology.

- Stacked Multicell Converter (SMC): An SMC will be discussed as a flying capacitor commercial topology.

### 2.1. Neutral Point Clamped (NPC) Converter

The NPC converter was introduced in the early 1980s [6]. Today, the NPC topology has become very popular in industry and academic research all over the world. Some commercial examples are ACS1000 (ABB), MV Simovert (Siemens), TMdrive-70 (TMEIC-GE), Silcovert-TN (Ansaldo), MV7000 (Converteam) and IngeDrive MV500 (IngeTeam). NPC inverters can be found in industry using IGCT (Integrated Gate Commutated Thyristor), IEGT (Injection Enhanced Gate Transistor), and medium-voltage IGBT (Insolated Gate Bipolar Transistor).

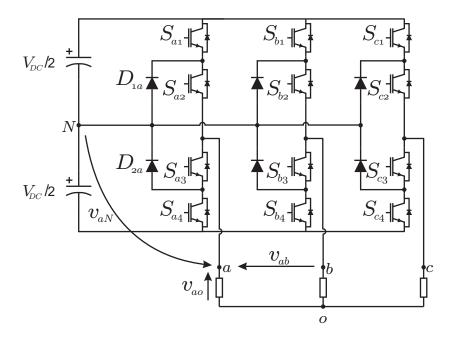

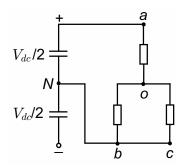

#### 2.1.1. The power circuit

Fig 2.1 presents the power circuit of this topology. Each phase of the inverter has four power switches that are composed of a power transistor with an antiparallel diode. In addition, two clamping diodes  $(D_{1x}, D_{2x}, x \in \{a, b, c\})$  are used to connect the output terminal to the medium point (N) of the *dc-link* capacitors. This configuration allows the

Figure 2.1. Three Phase Inverter 3-level NPC.

| ICHING STATES FOR ONE P            | HASE OF THE NPC INVE |

|------------------------------------|----------------------|

| Switching State                    | Output Voltage       |

| $(S_{x1}, S_{x2}, S_{x3}, S_{x4})$ | $v_{xN}$             |

| (1,1,0,0)                          | $V_{DC}/2$           |

| (0,1,1,0)                          | 0                    |

| (0,0,1,1)                          | $-V_{DC}/2$          |

Table 2.1

Switching states for one phase of the NPC inverter

power circuit to generate three voltage levels at the output terminal of phase x with respect to the neutral point N, considering the switching combinations given in Table 2.1. When  $S_{xi} = 0$ , the power switch  $S_{xi}$  is OFF, and when  $S_{xi} = 1$ , the power switch is ON, for all  $i \in \{1, 2, 3, 4\}$ .

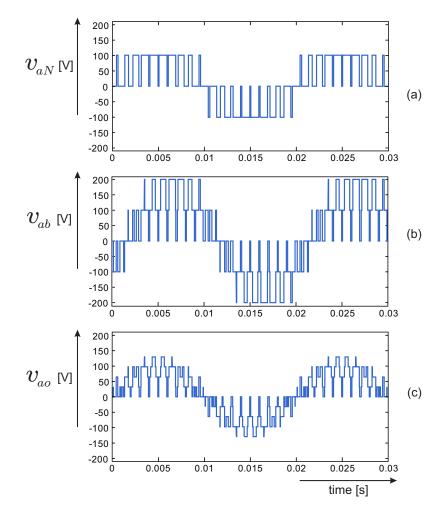

Fig. 2.2 shows the levels of voltages generated at the NPC inverter output. The main parameters for the simulation setup are  $V_{DC} = 200V$  and carrier PWM period  $T_c = 1ms$ . Since NPC has three levels between the output terminal and the neutral point of the inverter  $(v_{xN})$ , it will have k = 2m - 1 levels in the line-to-line voltages  $(v_{ab})$ , with m the number of levels at the output of inverter  $(v_{xN})$ . Therefore, the voltage  $v_{xo}$  will have 2k - 1 levels.

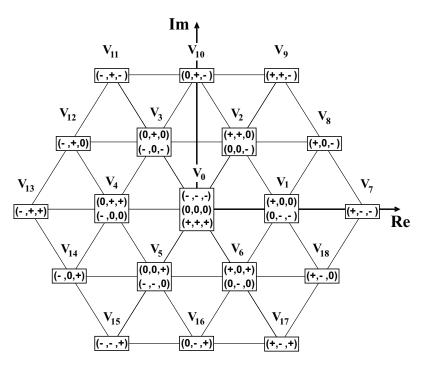

#### 2.1.2. Vectors generated by the inverter

For the three-phase inverter, 27 switching states are generated. Each switching state is represented by three possible values denoted by +, 0 and – that represent the switching combinations that generate  $V_{DC}/2$ , 0, and  $-V_{DC}/2$  respectively, at the output of the inverter phase.

Figure 2.2. NPC inverter output: (a) Voltage  $v_{aN}$ ; (b) Voltage  $v_{ab}$ ; (c) Voltage  $v_{ao}$ .

Considering that the space vector is defined for the output voltage:

$$\mathbf{v}_s = \frac{2}{3} [v_{aN}(t) + a v_{bN}(t) + a^2 v_{cN}(t)]$$

(2.1)

$$a = e^{j\frac{2\pi}{3}} = -\frac{1}{2} + j\frac{\sqrt{3}}{2}$$

(2.2)

$$a^{2} = e^{j\frac{4\pi}{3}} = -\frac{1}{2} - j\frac{\sqrt{3}}{2}$$

(2.3)

Figure 2.3. Space vectors of NPC.

and the definition of voltage states is described by:

$$S = (S_a, S_b, S_c) \tag{2.4}$$

$$S_{a,b,c} \in \{+,0,-\}$$

(2.5)

State +  $\rightarrow$   $S_{x1}, S_{x2}$  are on State 0  $\rightarrow$   $S_{x2}, S_{x3}$  are on State -  $\rightarrow$   $S_{x3}, S_{x4}$  are on for x = a, b, c

The 27 switching states produce 19 different voltage vectors, as shown in Fig. 2.3. Some switching states are redundant, generating the same voltage vector. For example, vector  $V_0$  can be generated by three different switching states: (+,+,+), (0,0,0), and (-,-,-).

$$\mathbf{V}_{0} = \frac{2}{3} \left[ \frac{V_{DC}}{2} + a \frac{V_{DC}}{2} + a^{2} \frac{V_{DC}}{2} \right]$$

(2.6)

$$\mathbf{V}_0 = \frac{2}{3} \left[ 0 + a0 + a^2 0 \right] \tag{2.7}$$

$$\mathbf{V}_0 = \frac{2}{3} \left[ \frac{-V_{DC}}{2} + a \frac{-V_{DC}}{2} + a^2 \frac{-V_{DC}}{2} \right]$$

(2.8)

Voltage vectors  $V_1$  to  $V_6$  can be generated by two different switching states, that is, they present redundant switching states.

**Figure 2.4.** *Switching state for*  $V_0$ *.*  $S = \{+, +, +\}$ *.*

**Figure 2.5.** Switching state for  $V_1$ .  $S = \{+, 0, 0\}$ .

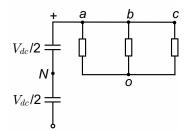

Fig. 2.4 shows the configuration of the load considering a passive load (resistors) for switching a state vector  $V_0$ , with  $S = \{+, +, +\}$ , and Fig. 2.5 shows the configuration for switching a state vector  $V_1$ , with  $S = \{+, 0, 0\}$ .

#### 2.1.3. The classical modulation

The classic PWM modulation is a special technique called: *Level Shifted PWM*. The LS-PWM used in this work consists of an Alternate Opposition Disposition [14].

Fig 2.6 shows the block diagram for connecting the signals to the power switches using a LS-PWM modulation, while Fig. 2.7 shows the waveforms for the classic LS-PWM modulation.

Figure 2.6. Block diagram of Level Shifted-PWM modulation.

Figure 2.7. Classic Level Shifted-PWM modulation.

#### 2.1.4. Summary

The main advantages and disadvantages of this topology can be summarized as follows.

#### Advantages :

- As a widely used topology, there is sufficient information in the literature about its applications [14–18]. This means that the NPC is a mature technology, which is a decisive factor in establishing a new technology in the industry.

- It only needs one source of DC voltage to power the entire inverter. The midpoints can be obtained using capacitors.

#### Disadvantages :

- There is an unequal distribution of losses between the inner and outer switching devices in each converter leg.

- An increasing number of clamping diodes is needed for higher number of levels.

- Depending on how the *dc-link* voltage, V<sub>DC</sub>, is obtained, imbalances may arise between the capacitors. This drawback can be mitigated by modifying the control strategy [19–21].

- At higher number of levels, it is problematic to maintain the proper balance of voltage in capacitors. Therefore, the control law becomes more complex [22–26].

### 2.2. Active Neutral Point Clamped (ANPC) Converter

The design of the multilevel converters allows for several output levels. However, such circuits often come at the price of far higher complexity. For example, to generate 5 output voltage levels in the NPC it is necessary to use additional clamping diodes, capacitors and the corresponding control and charging circuitry, which is a complex control strategy, and even so, a more complex control might not be sufficient to operate an NPC with more than 3 levels. An alternative approach is to connect converters in series. This again adds to the complexity of the *dc-link* supply circuit due to the need for galvanic separation of the supplies and thus costly transformers [27, 28].

This issue can be solved by the 5-level ANPC that incorporates an additional capacitor per output phase. ABB commercializes the 5L-ANPC with its ACS 2000 model.

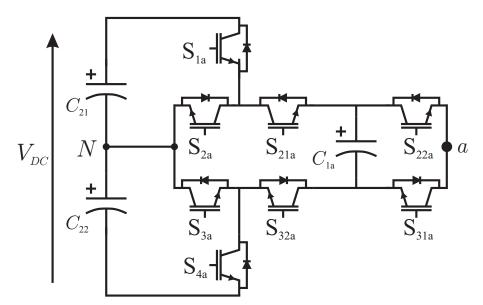

#### 2.2.1. The power circuit

Fig. 2.8 presents the power circuit of this topology. Each phase of the inverter has one capacitor and eight power switches, two of them are used to connect the medium point (N) of the *dc-link* capacitors.

Figure 2.8. 1-Phase 5-level ANPC Inverter.

The configuration of the ANPC enables the generation of five voltage levels at the output terminal of phase *a*, with respect to the neutral point *N*, considering the switching combinations given in Table 2.2. This topology needs a direct control over the inner voltage in the flying capacitor to ensure the correct performance, keeping the inner capacitor voltage to  $V_{DC}/4$ .

The power switches in 5L-ANPC do not have the same blocking voltage. The power switches  $S_{22a}$ ,  $S_{31a}$ ,  $S_{21a}$  and  $S_{32a}$  block  $V_{DC}/4$ , and the switches  $S_{1a}$ ,  $S_{2a}$ ,  $S_{3a}$ , and  $S_{4a}$  block  $V_{DC}/2$ .

#### 2.2.2. Vectors generated by the inverter

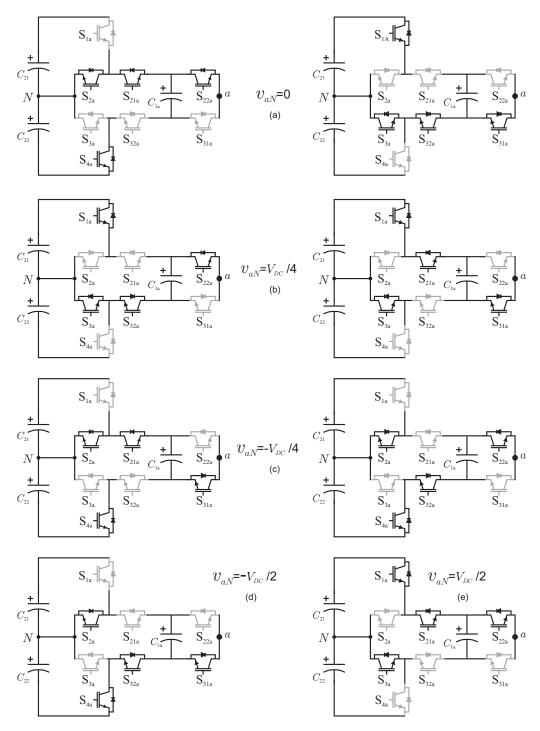

Fig. 2.9 shows the possible switching states for phase *a* of ANPC, where power switches shown in grey are OFF and power switches in black are ON.

**Figure 2.9.** Possible switching states of an 5L-ANPC: (a) Output voltage: 0; (b) Output voltage:  $V_{DC}/4$ ; (c) Output voltage:  $-V_{DC}/4$ ; (d) Output voltage:  $-V_{DC}/2$ ; (e) Output voltage:  $V_{DC}/2$ .

| Voltage | Switches states |          |          |          |           |           |           |           | Output voltage |

|---------|-----------------|----------|----------|----------|-----------|-----------|-----------|-----------|----------------|

|         | $S_{1a}$        | $S_{2a}$ | $S_{3a}$ | $S_{4a}$ | $S_{21a}$ | $S_{32a}$ | $S_{22a}$ | $S_{31a}$ |                |

| $V_1$   | 0               | 1        | 0        | 1        | 0         | 1         | 0         | 1         | $-V_{DC}/2$    |

| $V_2$   | 0               | 1        | 0        | 1        | 1         | 0         | 0         | 1         | $-V_{DC}/4$    |

| $V_3$   | 0               | 1        | 0        | 1        | 0         | 1         | 1         | 0         | $-V_{DC}/4$    |

| $V_4$   | 0               | 1        | 0        | 1        | 1         | 0         | 1         | 0         | 0              |

| $V_5$   | 1               | 0        | 1        | 0        | 0         | 1         | 0         | 1         | 0              |

| $V_6$   | 1               | 0        | 1        | 0        | 0         | 1         | 1         | 0         | $V_{DC}/4$     |

| $V_7$   | 1               | 0        | 1        | 0        | 1         | 0         | 0         | 1         | $V_{DC}/4$     |

| $V_8$   | 1               | 0        | 1        | 0        | 1         | 0         | 1         | 0         | $V_{DC}/2$     |

| Table 2.2                                           |    |

|-----------------------------------------------------|----|

| SWITCHING STATES FOR ONE PHASE OF THE ANPC INVERTER | ₹. |

Fig. 2.9-(a) shows the circuit for voltages  $V_4$  and  $V_5$  indicated in Table 2.2, Fig. 2.9-(b) shows the circuit for voltages  $V_6$  and  $V_7$ , Fig. 2.9-(c) shows the circuit for voltages  $V_2$  and  $V_3$ , Fig. 2.9-(d) shows the circuit for vector  $V_1$  and finally, Fig. 2.9-(e) shows the circuit for vector  $V_8$  indicated in Table 2.2.

It is possible see that vectors  $V_2$ ,  $V_3$ ,  $V_6$  and  $V_7$ , have an influence on the inner voltage, charging or discharging the inner capacitor as a function of the output current.

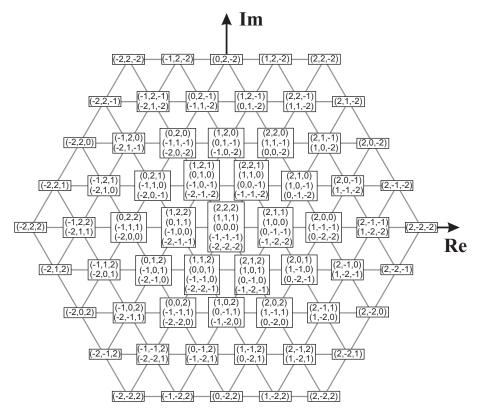

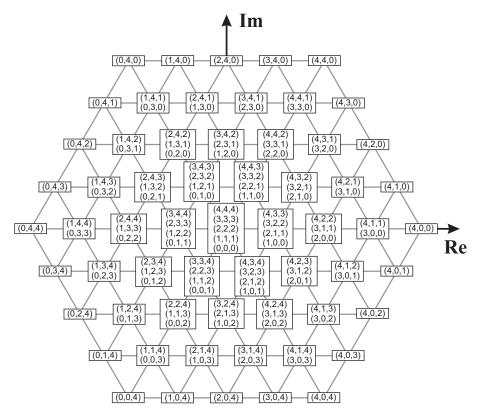

For the three-phase inverter,  $8^3 = 512$  switching states are generated. The 512 switching states produce 125 different voltage vectors, as shown in Fig. 2.10.

Figure 2.10. Space vectors of 5L-ANPC.

Some voltage vectors are redundant. For example, vector V = 0 can be generated by five different voltage states (*S*): (2,2,2), (1,1,1), (0,0,0), (-1,-1,-1), and (-2,-2,-2). Where:

$$S = (S_a, S_b, S_c)$$

(2.9)

$$S_{a,b,c} \in \{2, 1, 0, -1, -2\}$$

(2.10)

State 2  $\rightarrow v_{aN} = V_{DC}/2$

State 1  $\rightarrow v_{aN} = V_{DC}/4$

State 0  $\rightarrow v_{aN} = 0$

State -1  $\rightarrow v_{aN} = -V_{DC}/4$

State -2  $\rightarrow v_{aN} = -V_{DC}/2$

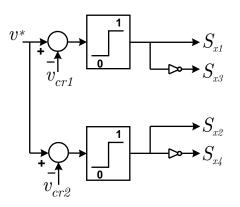

#### 2.2.3. The classical modulation

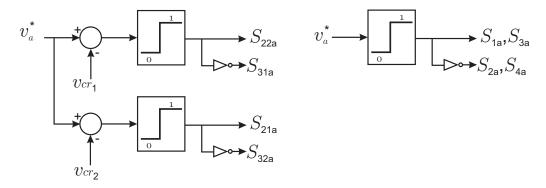

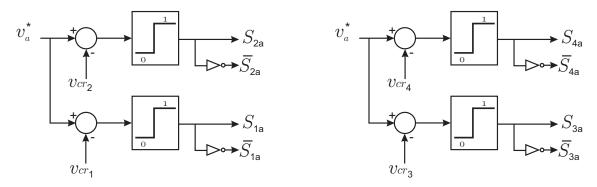

The classic modulation used in the 5L-ANPC is a Phase Shifted-PWM (PS-PWM) with  $\phi=180^{\circ}.$

From Table 2.2, it can be seen that pair of power switches  $(S_{22a}, S_{31a})$ ,  $(S_{21a}, S_{32a})$ ,  $(S_{1a}, S_{2a})$ , and  $(S_{3a}, S_{4a})$  are complementary switch pair and  $S_{1a}$  and  $S_{3a}$  require the same switching signal.

It can also be observed that  $S_{1a}$  and  $S_{3a}$  are turned OFF when the output voltage is negative and turned ON when the output voltage is positive. So, the switch pairs  $(S_{1a}, S_{2a})$ , and  $(S_{3a}, S_{4a})$  can be operated at fundamental frequency based on the polarity of the phase voltage.

A classic PS-PWM can be used to control the switch pairs  $(S_{22a}, S_{31a})$  and  $(S_{21a}, S_{32a})$ .

Fig 2.11 shows the block diagram for connecting the signals to the power switches using the PWM modulation, while Fig. 2.12 shows the waveforms for the classic modulation for a 5L-ANPC.

Figure 2.11. Block diagram of PS-PWM modulation for a 5L-ANPC.

Figure 2.12. Classic PWM modulation for a 5L-ANPC.

#### 2.2.4. Summary

The main advantages and disadvantages of this topology can be summarized as follows.

Advantages: It is more suitable for high-performance medium voltage motor drives [29–37].

- It can overcome the limitations of the NPC inverter by reducing the total number of capacitors necessary to generate five levels, which makes it easy to balance all voltages.

- It only needs one source of DC voltage to power the entire inverter. The midpoints can be obtained using capacitors.

**Disadvantages:** • Depending on how the voltage *dc-link*, *V*<sub>DC</sub>, is obtained, imbalances may arise between the capacitors. Modifying the control output switches can mitigate this drawback.

- Since it has a larger number of semiconductor devices, it has higher conduction losses.

- To go to medium voltage applications, it is necessary to duplicate power switches S<sub>1A</sub>, S<sub>2A</sub>, S<sub>3A</sub> and S<sub>4A</sub> in all phases to get the same blocking voltage in all semiconductors.

### 2.3. Flying Capacitor Converter (FCC)

The FCC topology was developed in the 1990s [8], and it uses several floating capacitors instead of clamping diodes to share the voltage stress among devices and to achieve different voltage levels in the output.

The FCC topology can be extended, achieving more levels in the output phase by the connection of more cells in tandem (see Fig. 2.13). Nowadays, the FCC has a reduced industrial presence, but some commercial products can be found such as the ALSPA VDM6000 converter by Alstom [38, 39].

#### 2.3.1. The power circuit

Figure 2.13. 1-Phase Inverter 5-level FCC.

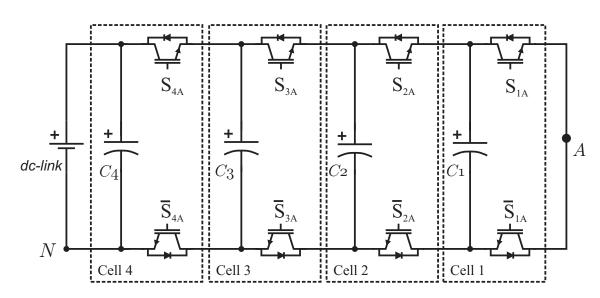

Fig. 2.13 shows the topology for a 5-level single-phase FCC, which is composed by the tandem connection of four basic units called *cells*.

Each cell requires a capacitor and two power switches, which must be operated complementarily. In most works, the capacitor voltages ratio is set as  $v_{C1} : v_{C2} : v_{C3} : v_{C4} =$ 1 : 2 : 3 : 4. When this condition is reached, the converter generates a 5-level voltage waveform between the output terminal A and the inverter neutral point N. Other voltage ratios have been proposed in literature [40–42]; however, the standard 1 : 2 : 3 : 4 ratio presents the advantage of evenly spreading the voltage stress across the power switches.

Additionally, this standard ratio can be naturally achieved with a simple Phase Shifted Pulse Width Modulation (PS-PWM) strategy, i.e., in an open-loop manner [43, 44].

#### 2.3.2. Vectors generated by the inverter

Every cell of FCC can generate two possible states. In the case of a 5-level FCC with four cells, the total possible states are:  $2^4 = 16$ . Table 2.3 shows the possible states of the multilevel converter and the influence of the inner voltage on the output value.

| Voltage  | Switches' states |          |          | es       | Output voltage                      | Output voltage |

|----------|------------------|----------|----------|----------|-------------------------------------|----------------|

|          | $S_{4a}$         | $S_{3a}$ | $S_{2a}$ | $S_{1a}$ |                                     | [V]            |

| $V_1$    | 0                | 0        | 0        | 0        | 0                                   | 0              |

| $V_2$    | 0                | 0        | 0        | 1        | $v_{C1}$                            |                |

| $V_3$    | 0                | 0        | 1        | 0        | $v_{C2} - v_{C1}$                   | $V_{DC}/4$     |

| $V_4$    | 0                | 1        | 0        | 0        | $v_{C3} - v_{C2}$                   |                |

| $V_5$    | 1                | 0        | 0        | 0        | $v_{C4} - v_{C3}$                   |                |

| $V_6$    | 0                | 0        | 1        | 1        | $v_{C2}$                            |                |

| $V_7$    | 0                | 1        | 1        | 0        | $v_{C3} - v_{C1}$                   |                |

| $V_8$    | 1                | 1        | 0        | 0        | $v_{C4} - v_{C2}$                   | $V_{DC}/2$     |

| $V_9$    | 0                | 1        | 0        | 1        | $v_{C3} - v_{C2} + v_{C1}$          |                |

| $V_{10}$ | 1                | 0        | 0        | 1        | $v_{C4} - v_{C3} + v_{C1}$          |                |

| $V_{11}$ | 1                | 0        | 1        | 0        | $v_{C4} - v_{C3} + v_{C2} - v_{C1}$ |                |

| $V_{12}$ | 0                | 1        | 1        | 1        | $v_{C3}$                            |                |

| $V_{13}$ | 1                | 1        | 1        | 0        | $v_{C4} - v_{C1}$                   | $3V_{DC}/4$    |

| $V_{14}$ | 1                | 1        | 0        | 1        | $v_{C4} - v_{C2} + v_{C1}$          |                |

| $V_{15}$ | 1                | 0        | 1        | 1        | $v_{C4} - v_{C3} + v_{C2}$          |                |

| $V_{16}$ | 1                | 1        | 1        | 1        | $v_{C4}$                            | $V_{DC}$       |

Table 2.3SWITCHING STATES FOR ONE PHASE OF THE FCC.

The redundancy in the voltage states  $V_2$ ,  $V_3$ ,  $V_4$  and  $V_5$  for output level  $V_{DC}/4$  and the redundancy in the voltage states  $V_6$ ,  $V_7$ ,  $V_8$ ,  $V_9$ ,  $V_{10}$  and  $V_{11}$  for output level  $V_{DC}/4$ and finally, the redundancy in the voltage states  $V_{12}$ ,  $V_{13}$ ,  $V_{14}$  and  $V_{15}$  for output level  $3V_{DC}/4$  achieve an appropriate combination of switching states that ensures the correct inner voltage and the desired output voltage, charging or discharging the inner capacitor as necessary.

For the 3-phase 5-level FCC there are  $16^3 = 4096$  possible switching states. These switching states produce 125 different voltage vectors, as shown in Fig. 2.14.

Some voltage vectors are redundant, the vector  $\mathbf{V} = 0$  can be generated by five different voltage states (*S*): (4,4,4), (3,3,3), (2,2,2), (1,1,1), and (0,0,0). Considering:

$$S = (S_a, S_b, S_c) \tag{2.11}$$

$S_{a,b,c} \in \{4,3,2,1,0\}$ (2.12)

$\begin{array}{l} \text{State 4} \rightarrow v_{aN} = V_{DC} \\ \text{State 3} \rightarrow v_{aN} = 3V_{DC}/4 \\ \text{State 2} \rightarrow v_{aN} = V_{DC}/2 \\ \text{State 1} \rightarrow v_{aN} = V_{DC}/4 \\ \text{State 0} \rightarrow v_{aN} = 0 \end{array}$

Figure 2.14. Space vectors of 5L-FFC.

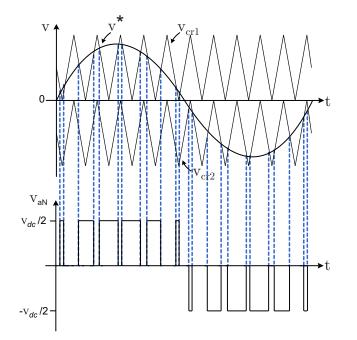

#### 2.3.3. The classical modulation

The classic PWM modulation of the FCC that allows the inner voltage to be balanced is a special technique called: *Phase Shifted PWM* (PS-PWM). The phase shifted between the carrier signal in an FCC is given by the expression:

$$\phi = \frac{360}{N_c} \tag{2.13}$$

where  $N_c$  is the number of cells in the topology. In the case of the 5-level FCC,  $\phi = 90^{\circ}$ .

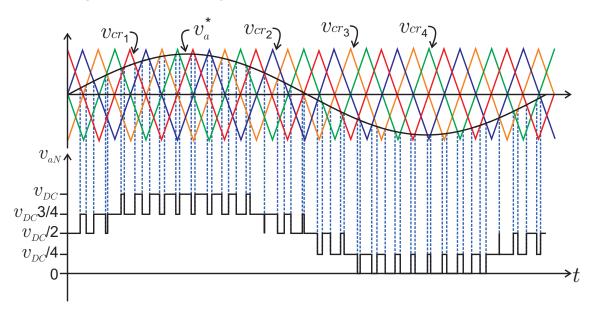

Fig 2.15 shows the block diagram that generates the signals to the power switches employing a PS-PWM modulation, where  $v_a^*$  is the reference signal for the output phase a and  $v_{cr_i}$  for all  $i \in \{1, 2, 3, 4\}$  are the carrier signals. Fig. 2.16 shows the classic PS-PWM waveform.

Figure 2.15. Block diagram of PS-PWM modulation for a 5-level FCC.

Figure 2.16. Classic Phase Shifted-PWM modulation.

#### 2.3.4. Summary

The main advantages and disadvantages of this topology can be summarized as follows.

- Advantages: The large number of capacitors provides a source of energy storage, which augments the system's ability to deal with momentary loss of power from the grid.

- In case of failure, removing cells does not decrease the maximum voltage applied; the only consequences are the reduction of levels obtained at the output, the increase of blocking voltage in the semiconductors and the voltage in the capacitors.

- FCC has a modular configuration, which makes it a *scalable* converter.

- **Disadvantages:** The number, size and voltage rating of capacitors increases with the number of levels; in addition to increasing the size of the inverter, these are some of the components that make the FCC of lesser life and higher cost.

- The main capacitor must be designed to withstand the maximum voltage. In the case of a very high voltage, it is necessary to resort to configurations of the arrangement of capacitors.

- The stray inductances from large commutation loops cause high voltages overshoots.

- Like the NPC configuration, in this inverter special considerations must be taken in the implementation of the control to ensure a correct balance of the voltages of the flying capacitors. [45, 46]

### 2.4. Stacked Multicell Converter (SMC)

Today, the 3-phase 5-level SMC topology has a commercial application in medium voltage with the MV6 series from GE Power Conversion.

#### 2.4.1. The power circuit

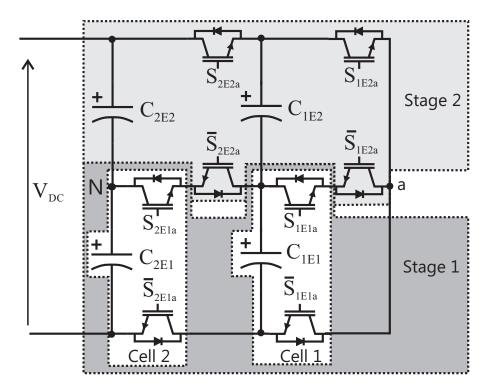

Figure 2.17. Topology of one phase of a Stacked Multicell Converter 2x2.

Fig. 2.17 presents the power circuit of the 5L-SMC converter for one phase; it is based on a hybrid association of elementary commutation cells. Each of these cells requires a capacitor and two power switches, which must be operated complementary.

Each stage (n cells stacked vertically) of the full converter can be viewed as a classical multicell converter (Flying Capacitor Converter) having p commutation cells in series.

Fig. 2.17 shows the particular case when p = 2 cells (horizontal) and n = 2 stages (vertical). For this converter, four flying capacitors  $C_{iEj}$  with  $i \in \{1,2\}$  and  $j \in \{1,2\}$  appear, where *i* indicates the number of the respective cell (cells put horizontally) while *j* indicates the number of the respective stages (cells put vertically). Each voltage across these capacitors is then equal to  $V_{C_{iEj}} = \frac{i \cdot E}{n \cdot p}$  with  $E = V_{DC}$  the input voltage of the converter.

#### 2.4.2. Vectors generated by the inverter

The SMC 2x2 shown in Fig. 2.17 has  $N_{states} = 9$  different states and  $N_{levels} = 5$  different levels in the output. These 9 configurations and their respective levels consi-

**Figure 2.18.** Switching states not allowed in a SMC 2x2: (a) Short circuit in cell 1; (b) Short circuit in cell 2; (c) Short circuit in both cells.

dering the particular case of the SMC 2x2,  $V_{C_{2E2a}} = V_{C_{2E1a}}$ ;  $V_{C_{1E2a}} = V_{C_{1E1a}}$ ;  $E = V_{DC}$ and  $V_{DC} : V_{C_{2E1a}} : V_{C_{1E1a}} = 4 : 2 : 1$ , are shown in Table 2.4 where  $S_{iEja} = 1$  when switch  $S_{iEja}$  is ON, and  $S_{iEja} = 0$  when switch  $S_{iEja}$  is OFF.

Each power switch can take only two possible states, so, if SMC has four switches (not considering the complementary pair) then it will have  $N_{states} = 4^2 = 16$  possible states. However, this argument is invalid, because there are seven switching states that are not allowed. The state when the switch of the upper stage is ON ( $S_{jE2a} = 1$ ) and the switch of the lower stage is OFF ( $S_{jE1a} = 0$ ) (see Fig. 2.18) generates a short circuit through both capacitors of the stage j. Consequently, the total states for each cell of both stages (ex. cell 1 of the stage 1 and cell 1 of the stage 2) is 3 instead of  $N_{states_{cell1}} = 2^2 = 4$ , so the total number of states of an SMC 2x2 will be  $N_{states} = 3^2 = 9$  because it has three states for each cells and has two cells.

Generalizing, the number of possible states of the circuit is then equal to:

$$N_{states} = (n+1)^p \tag{2.14}$$

The number of levels in an SMC for the output voltage is equal to:

| Voltage | State                                      | Output Voltage                               | Output Voltage |  |

|---------|--------------------------------------------|----------------------------------------------|----------------|--|

|         | $(S_{2E2a}, S_{2E1a}, S_{1E2a}, S_{1E1a})$ | $v_{aN}$                                     | $v_{aN}$ [V]   |  |

| $V_1$   | (0,0,0,0)                                  | $-V_{C_{2E1a}}$                              | $-V_{DC}/2$    |  |

| $V_2$   | (0,0,0,1)                                  | $V_{C_{1E1a}} - V_{C_{2E1a}}$                | $-V_{DC}/4$    |  |

| $V_3$   | (0,0,1,1)                                  | $V_{C_{1E2a}} + V_{C_{1E1a}} - V_{C_{2E1a}}$ | 0              |  |

| $V_4$   | (0,1,0,0)                                  | $-V_{C_{1E1a}}$                              | $-V_{DC}/4$    |  |

| $V_5$   | (0,1,0,1)                                  | 0                                            | 0              |  |

| $V_6$   | (0,1,1,1)                                  | $V_{C_{1E2a}}$                               | $V_{DC}/4$     |  |

| $V_7$   | (1,1,0,0)                                  | $V_{C_{2E2a}} - V_{C_{1E2a}} - V_{C_{1E1a}}$ | 0              |  |

| $V_8$   | (1,1,0,1)                                  | $V_{C_{2E2a}} - V_{C_{1E2a}}$                | $V_{DC}/4$     |  |

| $V_9$   | (1,1,1,1)                                  | $V_{C_{2E2a}}$                               | $V_{DC}/2$     |  |

Table 2.4

Switching states for one phase of the Stacked Multicell Converter 2x2

$$N_{levels} = (np) + 1 \tag{2.15}$$

The 3-phase 5L-FCC has  $9^3 = 729$  switching states, and these 729 switching states produce 125 different voltage vectors, the same as in 5L-ANPC, as shown in Fig. 2.10.

#### 2.4.3. The classical modulation

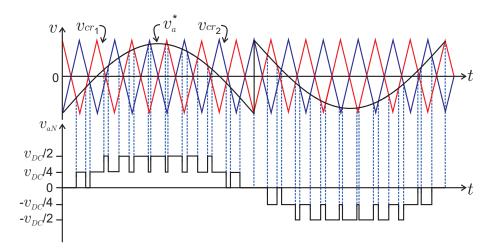

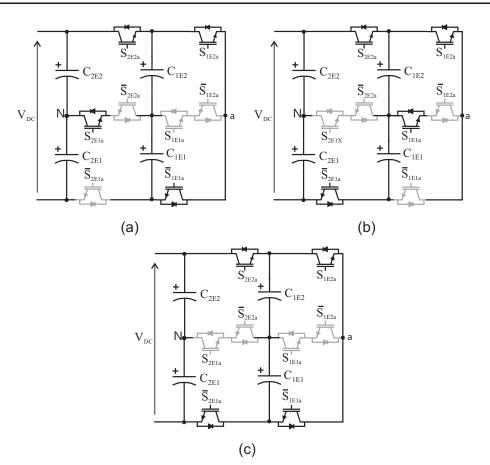

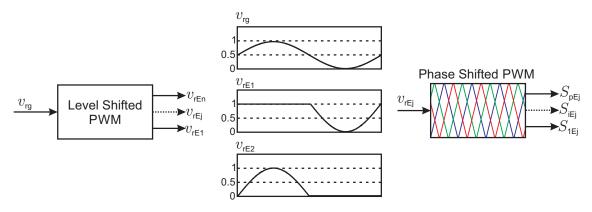

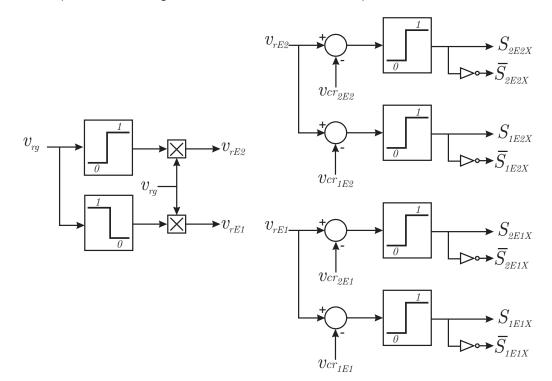

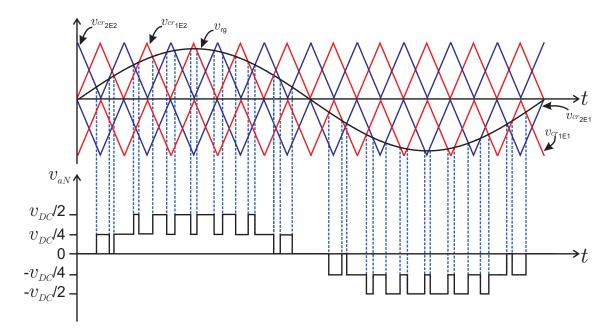

It is necessary to define the global referential signal called  $v_rg$ . This signal corresponds to the reference for the output voltage of the converter.

Based on this  $v_rg$  signal and on the number of stages (n = 2), n signals of internal references (called  $v_{rEj}$ ) can be generated. These signals  $v_{rEj}$  will be sent to each stage (n = 2) of the converter, and then each signal  $v_{rEj}$  is modulated with the PS-PWM strategy for each stage.

Figure 2.19. Steps in the classical modulation of the SMC.

Consequently, the classical modulation of the SMC requires two steps. The first step

modulates the  $v_rg$  signal for each stage of the SMC (in vertical) to determinate the internal reference signals (called  $v_{rEj}$ ), and the second step modulates the  $v_{rEj}$  signals for each cell of each stages (in horizontal). The resulting modulation is a Mixed Shifted-PWM, which is composed of a Phase Shifted-PWM (PS-PWM) determined for the numbers of cells that compose each stage (two horizontal cells in the case of the SMC 2x2), and a Level Shifted-PWM (LP-PWM) determined by the numbers of stages that compose the converter (two vertical stages in the case of the SMC 2x2).

Figure 2.20. Block diagram of the classical modulation for an SMC 2x2.

Fig. 2.19 shows the steps for the classical modulation of an SMC with *n* stages and *p* cells where the first step to determinate the voltage reference for each vertical stage  $(v_{rEj})$  is an LS-PWM.

Fig. 2.20 shows the block diagram of the classical modulation for an SMC with 2 stacks and 2 cells. Fig. 2.21 shows the classical modulation in the particular case of a 2x2 SMC.

#### 2.4.4. Summary

The main advantages and disadvantages of this topology can be summarized as follows.

Advantages: The capacitors are smaller than those used in FCC. In 5L-SMC, two capacitors blocking  $V_{DC}/4$  and two blocking  $V_{DC}/2$  are necessary, and 5L-FCC requires one capacitor blocking  $V_{DC}/4$ , one blocking  $V_{DC}/2$ , one blocking  $3V_{DC}/4$  and finally one for the *dc-link* ( $V_{DC}$ ).

Figure 2.21. Classical modulation of a SMC 2x2.

- It has a large number of levels to the output of converter with good current and power dynamics.

- The number of degrees of freedom increases in relation to the levels per cell.

- The converter has a modular configuration feature that makes it a scalable converter.

- **Disadvantages:** This topology has more power semiconductors per cell than in a classical multicell converter.

- There are a lot of flying capacitors that need to be balanced.

## **Chapter 3**

## **Reduced Multilevel Converter**

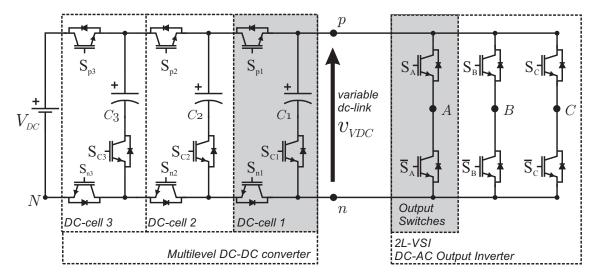

The Reduced Multilevel Converter (RMC) [47] structure concept is composed of a variable *dc-link* converter and a 3-phase output inverter stage, like the one shown in Fig. 3.1 for a 5-level configuration using a 2L-VSI. The variable *dc-link* structure is composed of a cascaded connection of basic units called *DC-cells* which is shown in Fig. 3.2.

Every DC-cell is formed by three power switches and one capacitor; when the power switch in series with the capacitor ( $S_{Ck}$ ) is ON, the upper and lower switches ( $S_{pk}$  and  $S_{nk}$ ) must to work in a complementary way to avoid a short circuit.

One way to understand how this topology works is to imagine it as two parts that work together. The first part (the DC-cells) works as a DC-DC multilevel converter, generating a variable *dc-link* between the points *p* and *n*, and the second part (output inverter) works as a DC-AC inverter connected to a variable *dc-link* and can be any inverter with a single DC-bus configuration like the 2L-VSI, NPC, 3L-ANPC, 5L-ANPC, T-type (SMC 1x2) [13], FCC, or SMC.

**Figure 3.1.** Five Level Reduced Multilevel Converter (5L-RMC), with 3 DC-cell and a 2L-VSI output inverter.

In this work, the basic 2L-VSI is used for simplicity. The 2L-VSI is connected to the

variable *dc-link* and can choose the output voltage between two options:  $v_{pN}$  or  $v_{nN}$  as shown in Fig. 3.1.

Figure 3.2. Generic DC-cell k of RMC.

## 3.1. Basic properties

The RMC is a modular multicell structure, much like the FCC and SMC; this means that it is possible to increase or decrease the number of levels by connecting or disconnecting DC-cell units following the multicell arrangement.

Every main cell, see Fig. 3.2, has three possible conduction states. These are shown in Table 3.1, where  $S_{pk} = 1$  means that the power switch pk is ON and  $S_{pk} = 0$  means that it is OFF, for all power switches  $S_{pk}$ ,  $S_{nk}$  and  $S_{Ck}$ .

| Switching State |          |          | Output Potential           |                            |  |

|-----------------|----------|----------|----------------------------|----------------------------|--|

| $S_{pk}$        | $S_{nk}$ | $S_{Ck}$ | $v_{o_{(k)}}^+$            | $v_{o_{(k)}}^-$            |  |

| 1               | 1        | 0        | $v_{o_{(k+1)}}^+$          | $v_{o_{(k+1)}}^-$          |  |

| 0               | 1        | 1        | $v_{o_{(k+1)}}^- + v_{ck}$ | $v_{o_{(k+1)}}^{-}$        |  |

| 1               | 0        | 1        | $v_{o_{(k+1)}}^+$          | $v_{o_{(k+1)}}^+ - v_{ck}$ |  |

Table 3.1

DC-CELL RMC: POSSIBLE SWITCHING STATES

Hence, each additional DC-cell incorporates three possible switching states for the DC-DC multilevel part of the converter and the total possible states can be expressed as an equation in function of the number of DC-cells ( $N_{DC-cell}$ ) as follows:

$$N_{states_{DC-DC}} = 3^{N_{DC-cell}} \tag{3.1}$$

In the case of the RMC shown in Fig. 3.1, there are 3 DC-cells, and the possible switching states for the DC-DC multilevel part are  $3^3 = 27$ .

A 2L-VSI is used for the DC-AC inverter part, and there are two power switches for each output phase. These two switches work in a complementary way; when  $S_x = 1$ , i.e. it is ON, the switch  $\bar{S}_x = 0$ , is OFF. This is necessary, because  $S_x = 1$  and  $\bar{S}_x = 1$  at the same time generates a short circuit in the variable dc-link, that is, in the dc-link or in one of the inner capacitors.

The possible switching states for each phase is 2. Therefore, the number of possible states in function of the number of output phases  $(N_{OP})$  can be described by:

$$N_{states_{DC-AC}} = 2^{N_{OP}} \tag{3.2}$$

In the case of the RMC shown in Fig. 3.1, there are 3 output phases, and the possible switching states for the DC-AC part is  $2^3 = 8$ .

The total number of possible states of the whole converter is given by the multiplication of the number of states in the DC-DC multilevel part and in the DC-AC part as in equation (3.3):

$$N_{states} = N_{states_{DC-DC}} * N_{states_{DC-AC}}$$

(3.3)

For the case of a 5-level, 3-phase RMC shown in Fig. 3.1, the total possible states are  $N_{states} = 27 * 8 = 216$ .

The number of output voltages  $(N_{OV})$  between the output phase (A, B or C) and the neutral point of the converter (N) is given by:

$$N_{OV} = N_{DC-cell} + 2 \tag{3.4}$$

As long as the inner voltage in the capacitors follows the relationship given by:

$$v_{Ck} = k \frac{V_{DC}}{N_{DC-cell} + 1} \tag{3.5}$$

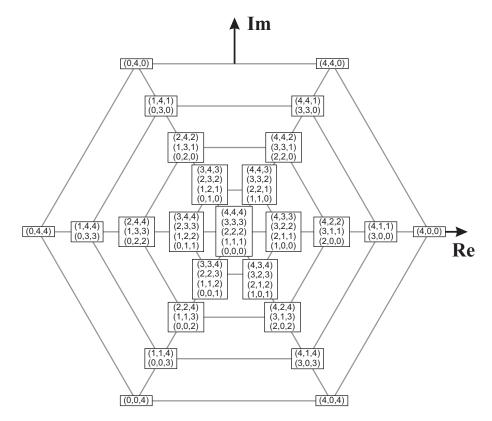

All possible combinations of these 216 possible switching states generate 65 output voltage vectors, which are shown in Fig. 3.3. The voltage vectors are described by the variable S as follow:

$$S = (S_A, S_B, S_C) \tag{3.6}$$

$$S_{a,b,c} \in \{4,3,2,1,0\}$$

(3.7)

State

$$4 \rightarrow v_{aN} = V_{DC}$$

State  $3 \rightarrow v_{aN} = 3V_{DC}/4$

State  $2 \rightarrow v_{aN} = V_{DC}/2$

State  $1 \rightarrow v_{aN} = V_{DC}/4$

State  $0 \rightarrow v_{aN} = 0$

Figure 3.3. Total possible output voltage vector in 5L-RMC.

There are 54 possible switching states for the voltage vector zero, 18 possible switching states for all possible voltage vectors in the first ring, six possible switching states for all voltage vectors in the second ring, two for the third ring and only one possible switching state for the vectors in the final ring, as is summarized in Table 3.2.

| Number of Possible Switching States | Output voltage Magnitude |

|-------------------------------------|--------------------------|

| 54                                  | 0 [V]                    |

| $18 \cdot 6 = 108$                  | $V_{DC}/6$ [V]           |

| $6 \cdot 6 = 36$                    | $V_{DC}/3$ [V]           |

| $2 \cdot 6 = 12$                    | $V_{DC}/2$ [V]           |

| $1 \cdot 6 = 6$                     | $2V_{DC}/3$ [V]          |

Table 3.2

REDUNDANT SWITCHING STATES FOR ALL POSSIBLE OUTPUT VOLTAGE LEVELS

Table 3.3 presents the 27 possible switching states of the 3DC-cell RMC with the 54 possible output voltages for one phase (choosing  $S_x = 1$  or  $S_x = 0$  for the 2L-VSI).

Switching states in voltage  $V_2 - V_5$  in Table 3.3 are redundant and generate the output voltage  $v_{pN} = V_{DC}$  and  $v_{nN} = 3V_{DC}/4$ . Voltages  $V_6 - V_7$  are redundant switching states that generate the output voltage  $v_{pN} = V_{DC}$  and  $v_{nN} = V_{DC}/2$ . Switching states in voltage  $V_8$  generate the output voltage  $v_{pN} = V_{DC}$  and  $v_{nN} = V_{DC}/4$ . Switching states in voltage  $V_9 - V_{13}$  generate the output voltage  $v_{pN} = 3V_{DC}/4$  and  $v_{nN} = V_{DC}/2$  with the voltages

| Voltage         | Switchings States |          |          |          |          |          | Output Voltage             |                                     |  |

|-----------------|-------------------|----------|----------|----------|----------|----------|----------------------------|-------------------------------------|--|

|                 | $S_{p3}$          | $S_{C3}$ | $S_{p2}$ | $S_{C2}$ | $S_{p1}$ | $S_{C1}$ | $S_x = 1 (v_{pN})$         | $S_x = 0 (v_{nN})$                  |  |

| $V_1$           | 1                 | 0        | 1        | 0        | 1        | 0        | $V_{DC}$                   | 0                                   |  |

| $V_2$           | 1                 | 0        | 1        | 0        | 1        | 1        | $V_{DC}$                   | $V_{DC} - v_{C1}$                   |  |

| $V_3$           | 1                 | 0        | 1        | 1        | 1        | 1        | $V_{DC}$                   | $V_{DC} - v_{C1}$                   |  |

| $V_4$           | 1                 | 1        | 1        | 0        | 1        | 1        | $V_{DC}$                   | $V_{DC} - v_{C1}$                   |  |

| $V_5$           | 1                 | 1        | 1        | 1        | 1        | 1        | $V_{DC}$                   | $V_{DC} - v_{C1}$                   |  |

| $V_6$           | 1                 | 1        | 1        | 1        | 1        | 0        | $V_{DC}$                   | $V_{DC} - v_{C2}$                   |  |

| $V_7$           | 1                 | 0        | 1        | 1        | 1        | 0        | $V_{DC}$                   | $V_{DC} - v_{C2}$                   |  |

| $V_8$           | 1                 | 1        | 1        | 0        | 1        | 0        | $V_{DC}$                   | $V_{DC} - v_{C3}$                   |  |

| $V_9$           | 1                 | 0        | 1        | 1        | 0        | 1        | $V_{DC} - v_{C2} + v_{C1}$ | $V_{DC} - v_{C2}$                   |  |

| $V_{10}$        | 1                 | 1        | 1        | 1        | 0        | 1        | $V_{DC} - v_{C2} + v_{C1}$ | $V_{DC} - v_{C2}$                   |  |

| V <sub>11</sub> | 1                 | 1        | 0        | 1        | 1        | 1        | $V_{DC} - v_{C3} + v_{C2}$ | $V_{DC} - v_{C3} + v_{C2} - v_{C1}$ |  |

| $V_{12}$        | 0                 | 1        | 1        | 0        | 1        | 1        | $v_{C3}$                   | $v_{C3} - v_{C1}$                   |  |

| $V_{13}$        | 0                 | 1        | 1        | 1        | 1        | 1        | $v_{C3}$                   | $v_{C3} - v_{C1}$                   |  |

| $V_{14}$        | 1                 | 1        | 0        | 1        | 1        | 0        | $V_{DC} - v_{C3} + v_{C2}$ | $V_{DC} - v_{C3}$                   |  |

| $V_{15}$        | 0                 | 1        | 1        | 1        | 1        | 0        | $v_{C3}$                   | $v_{C3} - v_{C2}$                   |  |

| $V_{16}$        | 0                 | 1        | 1        | 0        | 1        | 0        | $v_{C3}$                   | 0                                   |  |

| V <sub>17</sub> | 1                 | 1        | 1        | 0        | 0        | 1        | $V_{DC} - v_{C3} + v_{C1}$ | $V_{DC} - v_{C3}$                   |  |

| $V_{18}$        | 1                 | 1        | 0        | 1        | 0        | 1        | $V_{DC} - v_{C3} + v_{C1}$ | $V_{DC} - v_{C3}$                   |  |

| $V_{19}$        | 0                 | 1        | 1        | 1        | 0        | 1        | $v_{C3} - v_{C2} + v_{C1}$ | $v_{C3} - v_{C2}$                   |  |

| $V_{20}$        | 1                 | 0        | 0        | 1        | 1        | 1        | $v_{C2}$                   | $v_{C2} - v_{C1}$                   |  |

| $V_{21}$        | 0                 | 1        | 0        | 1        | 1        | 1        | $v_{C2}$                   | $v_{C2} - v_{C1}$                   |  |

| $V_{22}$        | 1                 | 0        | 0        | 1        | 1        | 0        | $v_{C2}$                   | 0                                   |  |

| $V_{23}$        | 0                 | 1        | 0        | 1        | 1        | 0        | $v_{C2}$                   | 0                                   |  |

| $V_{24}$        | 1                 | 0        | 1        | 0        | 0        | 1        | $v_{C1}$                   | 0                                   |  |

| $V_{25}$        | 1                 | 0        | 0        | 1        | 0        | 1        | $v_{C1}$                   | 0                                   |  |

| $V_{26}$        | 0                 | 1        | 1        | 0        | 0        | 1        | $v_{C1}$                   | 0                                   |  |

| $V_{27}$        | 0                 | 1        | 0        | 1        | 0        | 1        | $v_{C1}$                   | 0                                   |  |

Table 3.3

Switching states for 3-MCs 5-level Reduced Multilevel Converter.

pairs  $V_9 - V_{10}$  and  $V_{12} - V_{13}$  each being redundant.

Switching states in voltage  $V_{14} - V_{15}$  generate the output voltages  $v_{pN} = 3V_{DC}/4$  and  $v_{nN} = V_{DC}/4$ . Voltage  $V_{16}$  generates the output voltages  $v_{pN} = 3V_{DC}/4$  and  $v_{nN} = 0$ . Switching states in voltage  $V_{17} - V_{21}$  generate the output voltages  $v_{pN} = V_{DC}/2$  and  $v_{nN} = V_{DC}/4$  with voltages  $V_{17} - V_{18}$  and voltages  $V_{20} - V_{21}$  being redundant. Switching states in voltage  $V_{22} - V_{23}$  are redundant and generate the output voltages  $v_{pN} = V_{DC}/2$  and  $v_{nN} = 0$ . And finally, switching states in voltage  $V_{24} - V_{27}$  are redundant and generate the output voltage  $v_{pN} = V_{DC}/2$  and  $v_{nN} = 0$ .

This redundant switching states are summarized in Table 3.4.

| Switching States  | Output Voltage |             |  |

|-------------------|----------------|-------------|--|

|                   | $v_{pN}$       | $v_{nN}$    |  |

| $V_2 - V_5$       | $V_{DC}$       | $3V_{DC}/4$ |  |

| $V_{6} - V_{7}$   | $V_{DC}$       | $V_{DC}/2$  |  |

| $V_8$             | $V_{DC}$       | $V_{DC}/4$  |  |

| $V_1$             | $V_{DC}$       | 0           |  |

| $V_9 - V_{13}$    | $3V_{DC}/4$    | $V_{DC}/2$  |  |

| $V_{14} - V_{15}$ | $3V_{DC}/4$    | $V_{DC}/4$  |  |

| $V_{16}$          | $3V_{DC}/4$    | 0           |  |

| $V_{17} - V_{21}$ | $V_{DC}/2$     | $V_{DC}/4$  |  |

| $V_{22} - V_{23}$ | $V_{DC}/2$     | 0           |  |

| $V_{24} - V_{27}$ | $V_{DC}/4$     | 0           |  |

Table 3.4

REDUNDANT SWITCHING STATES FOR 3DC-CELL RMC

## 3.2. Operation principle

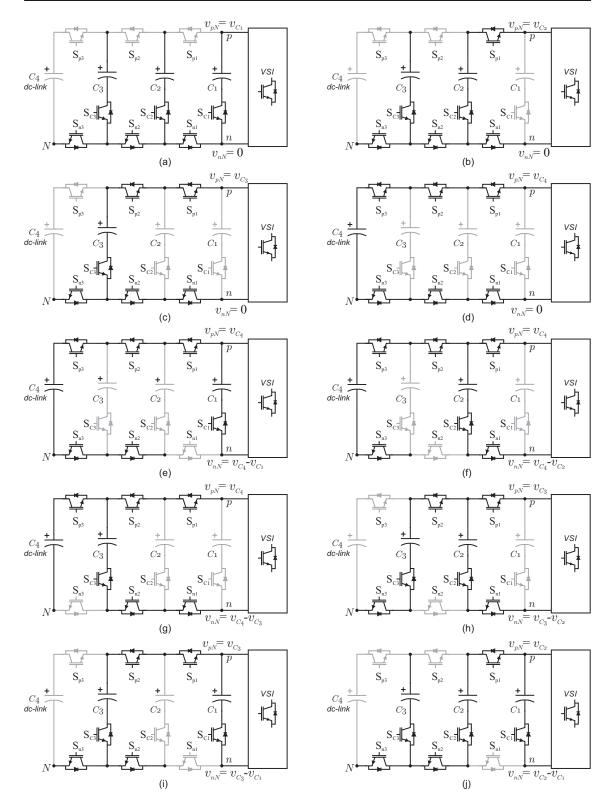

From the 27 allowed variable dc-link switching states, only 10 generate different voltage potentials in the output terminals (the 17 others generate redundant levels) for a three DC-cell RMC.

All combinations of these DC-DC multilevel voltages using a 2L-VSI in the DC-AC stage give a total of 216 possible output voltage space vectors. They are shown in Fig. 3.4, which includes the number of their redundancies.

Fig. 3.5 shows a selection of the 10 different dc-link level generation possibilities. Fig. 3.5-(a) to Fig. 3.5-(d) show the possible combinations for  $v_{nN} = 0$  and  $v_{pN} = V_{DC}/4$ ,  $v_{pN} = V_{DC}/2$ ,  $v_{pN} = 3V_{DC}/4$ , and  $v_{pN} = V_{DC}$ , respectively. Fig. 3.5-(e) to Fig. 3.5-(g) show possible combinations for  $v_{pN} = V_{DC}$ ,  $v_{nN} = 3V_{DC}/4$ ,  $v_{nN} = V_{DC}/2$ , and  $v_{nN} = V_{DC}/4$ , respectively. Fig. 3.5-(h) and Fig. 3.5-(i) show possible combinations of  $v_{pN} = 3V_{DC}/4$  and:  $v_{nN} = V_{DC}/4$ , and  $v_{nN} = V_{DC}/2$ , respectively. Fig. 3.5-(j) shows the combination of DC-DC voltage of  $v_{pN} = V_{DC}/2$  and  $v_{nN} = V_{DC}/4$ .

To generate five voltage levels with the same voltage step (dv/dt), the voltages in the inner capacitors must follow the following ratio:  $v_{C4} : v_{C3} : v_{C2} : v_{C1} = 4 : 3 : 2 : 1$ , with  $v_{C4} = V_{DC}$ .

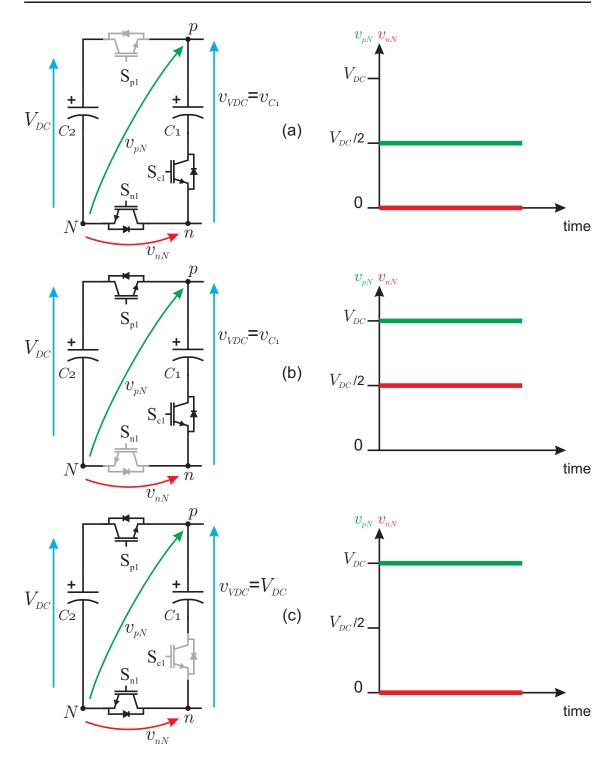

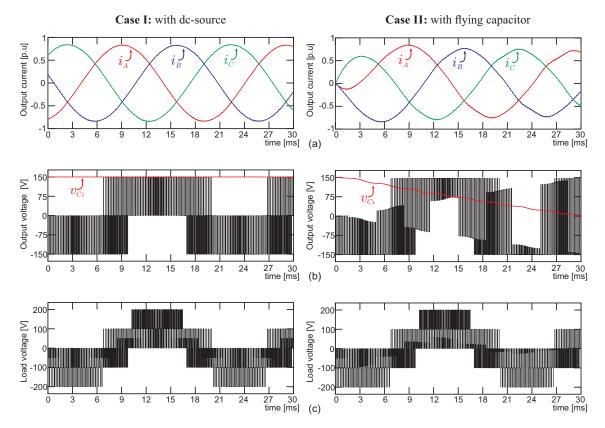

For simplicity and a better explanation, the operation principle of the 1DC-cell RMC, which is a 3-level topology, will be analyzed. The possible DC-DC voltage combinations in a 3-level RMC is shown in Fig. 3.6. In this case, the inner voltage on capacitor  $C_1$  is set to  $V_{DC}/2$ .

Fig. 3.6-(a) and Fig. 3.6-(b) generate the same voltage in the variable dc-link ( $v_{VDC} = v_{C1} = V_{DC}/2$ ). However, the possible output voltages are different; for  $v_{pN}$  the output voltage is  $V_{DC}/2$  or  $V_{DC}$ , and for  $v_{nN}$  the output voltage is 0 or  $V_{DC}/2$ . Finally, in Fig. 3.6-(c) the switching states generate a  $v_{VDC}$  equal to the main dc-link, i.e.  $v_{VDC} = V_{DC}$ , and

the output voltages can be  $v_{pN} = V_{DC}$  or  $v_{nN} = 0$ .