# Advanced Gateways in Automotive Applications

vorgelegt von Diplom-Ingenieur Tobias Lorenz aus Berlin

von der Fakultät Fakultät IV – Elektrotechnik und Informatik der Technische Universität Berlin zur Erlangung des akademischen Grades

> Doktor-Ingenieur - Dr.-Ing. -

genehmigte Dissertation

Promotionsausschuss:

Vorsitzender: Prof. Dr.-Ing. Georg Böck, TU-BerlinBerichter: Prof. Dr. rer. nat. Otto Manck, TU-BerlinBerichter: Prof. Dr.-Ing. Reinhold Orgelmeister, TU-Berlin

Tag der wissenschaftlichen Aussprache: 15.07.2008

Berlin 2008

D 83

## Acknowledgment

While I was working on my thesis over the last few years, I was fortunate enough to have had many fruitful and inspiring discussions in a congenial atmosphere with my colleagues both at the Technical University of Berlin as well as at Bosch, the business company I have been working for since 2004.

I am also deeply indebted to Prof. Otto Manck, my supervisor and mentor. During my time at his microelectronics division, he supported me with fruitful discussions and sound advice on research and technical issues, as well as on a personal level.

I would also like to thank Prof. Golze and Prof. Weinerth, which unfortunately were not able to attend the exam, Prof. Orgelmeister and Prof. Manck as the examiners and Prof. Böck as the chairman of the exam.

A special word of thanks goes also to the complete AE/EIP5 group at Bosch, which not only supported my work on the technical side, but more over we shared much of our recreational time. I also with to express my sincere thanks to Jan Taube for many discussions we had on the structure and implementation, Markus Ihle for the project management and Kay Hammer for helpful detailed information. The friendships that grew in the last years will last beyond my time in Reutlingen.

Furthermore, I would also like to thank my father, Jürgen Lorenz, and my uncle, Gert Lorenz, as neutral reviewers of my work and again Markus Ihle and Jan Taube regarding the scientific contents itself.

Without the steady support of my family during the complete time of education and studies, I never would have been able to do my dissertation in a relatively short time.

My special thanks also goes to all the other people, whom I have not directly named, but who also helped me both directly and indirectly during this period of my life.

# Declaration

I hereby declare that this submission is my own work and that, to the best of my knowledge and belief, it contains no material previously published or written by another person, nor material which to a substantial extent has been accepted for the award of any other degree or diploma of the university or other institute of higher learning, except where due acknowledgment has been made in the text.

(signature/name/date)

#### Abstract

Today's devices in automotive environments are linked by several independent networks, such as CAN, MOST and in the future FlexRay. The interconnection technologies between these networks is one of the fastest developing areas in automotive electronics. In recent years the improved capabilities enabled many new features, e.g. driver assistance systems.

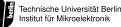

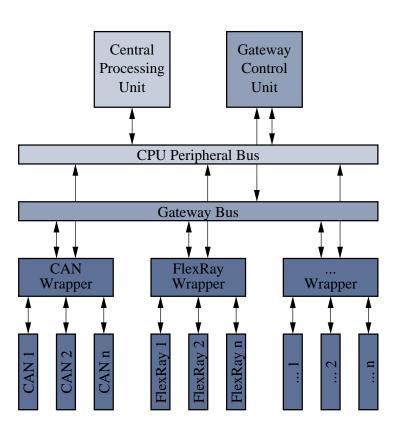

For the interconnection, complex gateway systems are necessary. Most of them are implemented as a System-On-Chip with high-speed CPUs and large buffer RAMs to provide just this functionality in software. With increasing throughput and number of interfaces on the gateway, this leads to high latency and jitter. Hardware based solutions can provide gateway functionality with hard real-time requirements and, additionally, circumvent the given problems.

The developed gateway concept is versatile, thus usable by different network types. It offers gateway functionality in hardware without the need to have a powerful CPU or large buffer RAM. CPU access to the underlying network interfaces is still possible to enable electronic control units (ECUs) to have further functionality.

For the gateway configuration, many non-standardized description formats are available. Unfortunately data exchange between different formats is inherently error-prone and time-consuming. A common description format is necessary and is found in the Field Bus Exchange Format (FIBEX).

On the other side gateway implementations have proprietary internal formats in which they store their configuration data. An optimal gateway toolchain should be based on the FIBEX configuration data of all connected networks and translate the routing information directly into the internal format of the target implementation.

The verification of complex gateway systems is problematic. Programming a remaining bus simulation is usually done manually, takes a long time and almost never covers the complete range of possible gateway mappings. Having an automated verification configuration generator was necessary. Such a regression test environment results in error logs containing patterns, which helps to find design or configuration bugs. Detailed statistics about latency and jitter of every mapping may be generated in parallel. Using FIBEX as common configuration format for the gateway and for the verification environment can eliminate inconsistencies.

#### Zusammenfassung

Heutige Steuergeräte in Kraftfahrzeugen sind über eine Reihe von unabhängigen Netzwerken, wie CAN, MOST und zukünftig FlexRay, miteinander verbunden. Die zunehmende Verknüpfung stellt derzeit eine der am stärksten wachsenden Bereiche in der Automobilelektronik dar. In den vergangenen Jahren sind durch die dadurch gestiegenen Möglichkeiten viele neue Funktionen entstanden, insbesondere im Bereich der Fahrerassistenzsysteme.

Für die Verbindung von Netzwerken sind komplexe Gateway-Systeme notwendig. Derzeit sind diese System-On-Chips mit schnellen CPUs und großen RAMs ausgestattet, speziell um die Gateway-Funktionen in Software zu realisieren. Mit der Zunahme von Datendurchsatz und Schnittstellenanzahl im Gateway, führt dies mittlerweile zu nicht mehr tragbarem Latenz- und Jitterverhalten. Hardwarebasierte Lösungen können die Gateway-Funktionen mit harten Echtzeitanforderungen erfüllen und die bekannten Probleme verhindern.

Das entwickelte Gateway-Konzept ist vielseitig und dadurch mit verschiedenen Netzwerktypen nutzbar. Es ermöglicht die Verlagerung der Gateway-Funktion in Hardware, ohne die Notwendigkeit einer schnellen CPU und eines großen Puffer-Speichers. Der CPU-Zugang zu den darunter liegenden Netzwerkschnittstellen ist weiterhin möglich, um weitere Funktionen im Steuergerät zu ermöglichen.

Für die Gateway-Konfiguration gibt es viele nicht-standardisierte Konfigurationsformate. Das macht den Austausch von Daten zwischen verschiedenen Formaten fehleranfällig und zeitaufwendig. Ein einheitliches Beschreibungsformat war notwendig und fand sich im Field Bus Exchange Format (FIBEX).

Auch intern weisen Gateways verschiedene proprietäre Konfigurationsformate auf. Die entwickelte Gateway-Toolchain ist daher in der Lage eine FIBEX-Konfiguration mit allen darin enthaltenen Konfigurationen zu laden und diese in das interne Format des Gateways zu übersetzen.

Die Verifikation eines solchen komplexen Gateway-Systems ist problematisch. Die Programmierung einer Restbussimulation wird üblicherweise manuell vorgenommen, was viel Zeit erfordert und fast nie den kompletten Bereich möglicher Gateway-Funktionen testet. Ein Tool zur automatisierten Erzeugung von Konfigurationen für die Verifikationsumgebung wurde entwickelt. Diese Regressionstestumgebung liefert Fehlermeldungen, deren Muster helfen können Fehler in Hard- und Software zu finden. Detaillierte Statistiken über Latenz und Jitter jeder Gateway-Funktion werden parallel erhoben. Die Benutzung von FIBEX als einheitliches Format für Gateway und Testumgebung hilft dabei Inkonsistenzen zu vermeiden.

# Contents

| 1        | Intr | oducti | ion                               | 10 |

|----------|------|--------|-----------------------------------|----|

| <b>2</b> | Con  | nmuni  | cation Networks                   | 12 |

|          | 2.1  | Basic  | Concepts                          | 12 |

|          |      | 2.1.1  | Physical Transmission             | 12 |

|          |      | 2.1.2  | Media Access Control              | 13 |

|          |      | 2.1.3  | Logical Link Control              | 14 |

|          |      | 2.1.4  | Upper Layers                      | 16 |

|          |      | 2.1.5  | Communication Controller          | 16 |

|          | 2.2  | Contro | oller Area Network                | 18 |

|          |      | 2.2.1  | Protocol Description              | 18 |

|          |      | 2.2.2  | Higher Layer Protocols            | 19 |

|          |      | 2.2.3  | Communication Controller          | 20 |

|          |      | 2.2.4  | Configuration Format              | 21 |

|          | 2.3  | Time-  | Triggered Controller Area Network | 21 |

|          |      | 2.3.1  | Protocol Description              | 22 |

|          |      | 2.3.2  | Communication Controller          | 23 |

|          | 2.4  | FlexR  | ay                                | 24 |

|          |      | 2.4.1  | Protocol Description              | 24 |

|          |      | 2.4.2  | Communication Controller          | 25 |

|          |      | 2.4.3  | Configuration Formats             | 27 |

|          | 2.5  | Media  | Oriented System Transport         | 27 |

|          |      | 2.5.1  | Protocol Description              | 28 |

|   |                   | 2.5.2                                                                                            | Communication Controllers           | 29                                                                                                                                             |

|---|-------------------|--------------------------------------------------------------------------------------------------|-------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

|   | 2.6               | Netwo                                                                                            | rk Architectures                    | 30                                                                                                                                             |

| 3 | Cur               | rent G                                                                                           | Fateways                            | 32                                                                                                                                             |

|   | 3.1               | Requi                                                                                            | rements                             | 32                                                                                                                                             |

|   | 3.2               | Tasks                                                                                            |                                     | 34                                                                                                                                             |

|   | 3.3               | Gatew                                                                                            | vay-Optimized Microcontroller       | 36                                                                                                                                             |

|   | 3.4               | Softwa                                                                                           | are Gateways                        | 38                                                                                                                                             |

|   |                   | 3.4.1                                                                                            | K2L Gateway                         | 39                                                                                                                                             |

|   |                   | 3.4.2                                                                                            | Automotive Open System Architecture | 39                                                                                                                                             |

|   |                   | 3.4.3                                                                                            | X2E Gateway                         | 41                                                                                                                                             |

|   | 3.5               | Config                                                                                           | guration Data Formats               | 41                                                                                                                                             |

|   |                   | 3.5.1                                                                                            | Field Bus Exchange Format           | 42                                                                                                                                             |

|   |                   | 3.5.2                                                                                            | AUTOSAR System Constraint Templates | 43                                                                                                                                             |

|   | 3.6               | Proble                                                                                           | ems and Issues                      | 43                                                                                                                                             |

|   |                   |                                                                                                  |                                     |                                                                                                                                                |

| 4 | Adv               | vanced                                                                                           | Gateway Architectures               | <b>45</b>                                                                                                                                      |

| 4 | <b>Adv</b><br>4.1 |                                                                                                  | Gateway Architectures               | <b>45</b><br>45                                                                                                                                |

| 4 |                   |                                                                                                  | ·                                   | _                                                                                                                                              |

| 4 |                   | Advan                                                                                            | aced Gateways                       | 45                                                                                                                                             |

| 4 |                   | Advan<br>4.1.1                                                                                   | aced Gateways                       | 45<br>45<br>46                                                                                                                                 |

| 4 |                   | Advan<br>4.1.1<br>4.1.2                                                                          | aced Gateways                       | 45<br>45<br>46                                                                                                                                 |

| 4 |                   | Advan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                        | aced Gateways                       | 45<br>45<br>46<br>52<br>59                                                                                                                     |

| 4 | 4.1               | Advan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4                                                        | aced Gateways                       | 45<br>45<br>46<br>52<br>59                                                                                                                     |

| 4 | 4.1               | Advan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Config                                              | aced Gateways                       | 45<br>45<br>46<br>52<br>59<br>61                                                                                                               |

| 4 | 4.1               | Advan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Config<br>4.2.1                                     | aced Gateways                       | <ol> <li>45</li> <li>45</li> <li>46</li> <li>52</li> <li>59</li> <li>61</li> <li>62</li> </ol>                                                 |

| 4 | 4.1               | Advan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Config<br>4.2.1<br>4.2.2                            | aced Gateways                       | <ol> <li>45</li> <li>45</li> <li>46</li> <li>52</li> <li>59</li> <li>61</li> <li>62</li> <li>63</li> </ol>                                     |

| 4 | 4.1               | Advan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Config<br>4.2.1<br>4.2.2<br>4.2.3                   | aced Gateways                       | <ol> <li>45</li> <li>45</li> <li>46</li> <li>52</li> <li>59</li> <li>61</li> <li>62</li> <li>63</li> <li>64</li> </ol>                         |

| 4 | 4.1               | Advan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Config<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4          | aced Gateways                       | <ul> <li>45</li> <li>45</li> <li>46</li> <li>52</li> <li>59</li> <li>61</li> <li>62</li> <li>63</li> <li>64</li> <li>64</li> </ul>             |

| 4 | 4.1               | Advan<br>4.1.1<br>4.1.2<br>4.1.3<br>4.1.4<br>Config<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>4.2.5 | acced Gateways                      | <ul> <li>45</li> <li>45</li> <li>46</li> <li>52</li> <li>59</li> <li>61</li> <li>62</li> <li>63</li> <li>64</li> <li>64</li> <li>65</li> </ul> |

|          |     | 4.3.1   | Gateway Executive Model                                                                                            |

|----------|-----|---------|--------------------------------------------------------------------------------------------------------------------|

|          |     | 4.3.2   | Automatic Test Generator                                                                                           |

| <b>5</b> | Imp | lemen   | tation and Results 75                                                                                              |

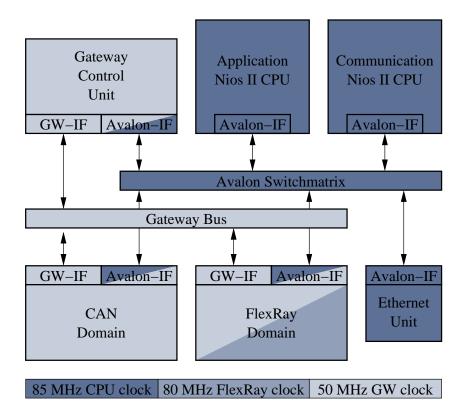

|          | 5.1 | Gatew   | ray Development Hardware                                                                                           |

|          |     | 5.1.1   | Development Board                                                                                                  |

|          |     | 5.1.2   | Physical Layer Board                                                                                               |

|          |     | 5.1.3   | Clock Frequencies                                                                                                  |

|          | 5.2 | CAN-0   | CAN Gateway Comparisons                                                                                            |

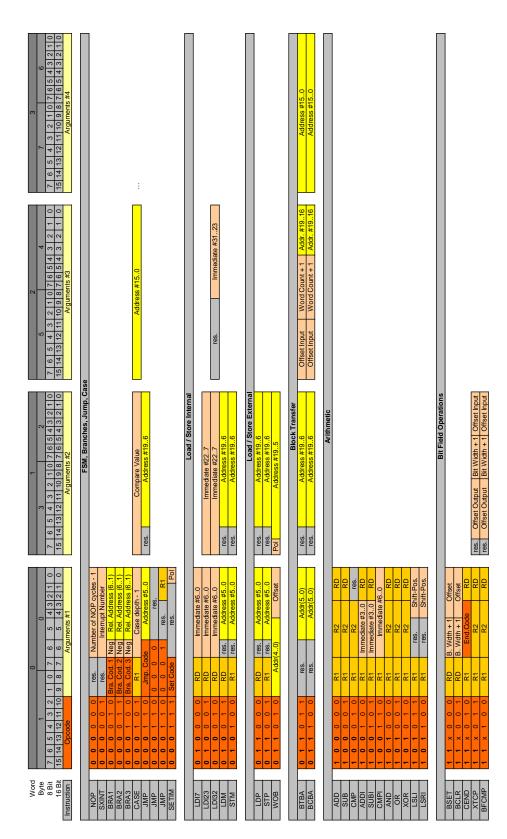

|          |     | 5.2.1   | Instruction Set                                                                                                    |

|          |     | 5.2.2   | Comparison of Implementations                                                                                      |

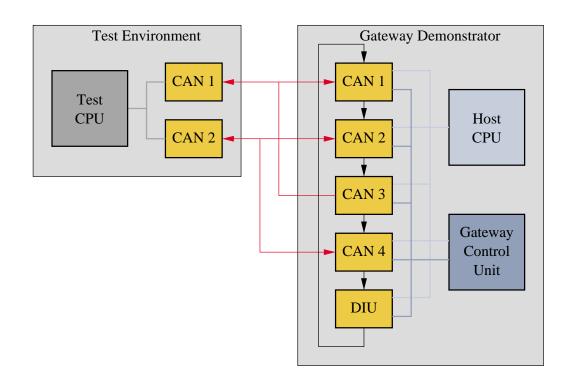

|          |     | 5.2.3   | Description of Test System                                                                                         |

|          |     | 5.2.4   | Implemented Tests $\ldots \ldots $ 82 |

|          |     | 5.2.5   | Results                                                                                                            |

|          | 5.3 | Multi-  | Protocol Gateway Implementation                                                                                    |

|          |     | 5.3.1   | RAM Configuration                                                                                                  |

|          |     | 5.3.2   | Instruction Set                                                                                                    |

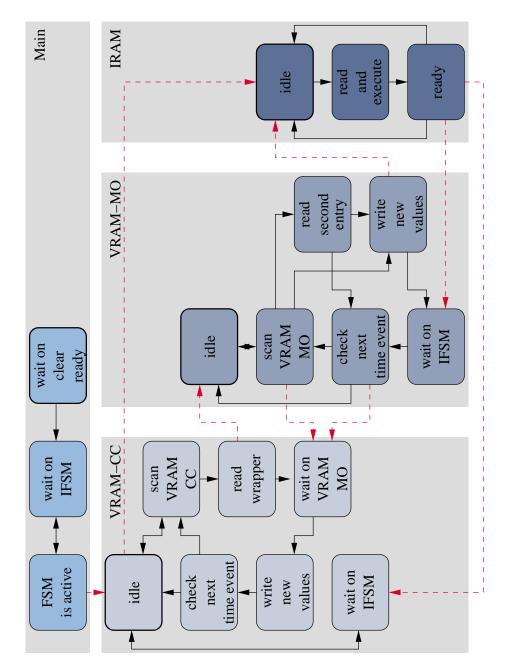

|          |     | 5.3.3   | Finite State Machines                                                                                              |

|          |     | 5.3.4   | Gate Count                                                                                                         |

|          | 5.4 | Toolch  | nain Optimization Results                                                                                          |

|          |     | 5.4.1   | Optimization Levels                                                                                                |

|          |     | 5.4.2   | Code Size and Execution Time                                                                                       |

|          | 5.5 | Verific | ation Environment Implementation                                                                                   |

|          |     | 5.5.1   | Test Description                                                                                                   |

|          |     | 5.5.2   | Test Scenarios                                                                                                     |

|          |     | 5.5.3   | Implementation Requirements                                                                                        |

|          |     | 5.5.4   | Results                                                                                                            |

|          |     | 5.5.5   | Future Improvements                                                                                                |

|          | 5.6 | Gatew   | vay Evaluation in OEM Environments                                                                                 |

|          |     | 5.6.1   | Vector RAM Usage Estimation                                                                                        |

|          |     | 5.6.2   | Instruction RAM Usage Estimation                                                                                   |

|                        | 5.6.3        | GCU Utilization Estimation                    | <br>. 105 |

|------------------------|--------------|-----------------------------------------------|-----------|

|                        | 5.6.4        | Routing Latency                               | <br>. 108 |

|                        | 5.6.5        | Worst Case Execution Time                     | <br>. 108 |

|                        | 5.6.6        | Evaluation of a High-Class Automotive Network | <br>. 108 |

|                        | 5.6.7        | Evaluation of a Mid-Class Automotive Network  | <br>. 109 |

|                        | 5.6.8        | Conclusion                                    | <br>. 111 |

| 6                      | Summary      | and Outlook                                   | 112       |

| G                      | lossary      |                                               | 115       |

| $\mathbf{L}\mathbf{i}$ | st of Figure | es                                            | 119       |

| $\mathbf{L}\mathbf{i}$ | st of Tables | 3                                             | 122       |

| В                      | ibliography  |                                               | 123       |

| $\mathbf{C}$           | urriculum V  | Vitae                                         | 134       |

## Chapter 1

## Introduction

The need for data transparency and information exchange within the overall in-car network has increased with the continuous improvement of electronic systems [1]. Just one of the numerous examples is the electronic stability program (ESP), monitoring the drive dynamics of the vehicle and taking control over engine management and brake systems when the vehicle is in danger of tipping over or skidding. A low latency gateway system is needed to connect the networks of both systems.

Nowadays most gateways are software gateways, based on standard communication controllers and a high performance CPU running appropriate software. This is a flexible concept, but on the other hand the performance is affected, since the hardware structure of a usual microcontroller is not optimized for gateway operations and the electronic control unit (ECU) often has to do other tasks as well. As the number of interfaces and the total bandwidth of a gateway increases continuously, software gateways will soon become bottlenecks, too slow to handle all incoming traffic in the required time. Currently these gateways are using CPUs with a clock frequency of about 150 MHz or even more [67], causing other problems, like high power consumption [75] and high electro-magnetic emission/radiation.

For the described network environment such a low-latency gateway system has been implemented in hardware. It currently allows processing of frame and signal mappings between multiple CAN and FlexRay networks.

The major part of the configuration of such a gateway system is defining the routing information for frames and signals between the channels. Before the emergence of standardized gateway description formats, the configuration data was necessarily specific for a gateway product and prohibited easy data exchange with other applications. Checking configurations was time-consuming and error-prone. A common description format was necessary and is found in the Field Bus Exchange Format (FIBEX). FIBEX is the upcoming XML-based data exchange standard with the capability to describe complete car networks, composed of different communication protocols. Currently full support for CAN, LIN and FlexRay networks is provided. The support of further protocols is recently under development. FIBEX also covers the configuration of gateway ECUs and defines operation tolerances in terms of relative or absolute timings.

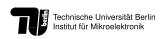

Based on these FIBEX files a gateway configuration toolchain was developed that interprets the network description and produces configuration images for both, the gateway and the communication controllers. An implemented abstraction layer allows the adaptation to different input formats in the future. The code can be generated optimized for execution time or memory size.

Safe operation of a gateway system is crucial. This has to be proven by an intensive test plan. The usual approach is to manually implement a test environment using a remaining bus simulation. Manual programming has several disadvantages. Checking the complete range of possible gateway mappings and test parameters is very expensive. Also manual programming can lead to errors not only in the implementation of the gateway function in hardware and software, but additionally in the test environment. This is especially true when changes to the gateway configuration also affect the test environment. Manual changes are always error-prone and often result in inconsistencies between gateway and test environment. These disadvantages can be eliminated by using tools to automate most of these tasks and by referring to a common source of information for the gateway and test configuration.

A verification environment was developed for black box testing of arbitrary gateways. It includes checks of the gateway mappings and therefore tests the gateways data consistency and timing behavior. A test generator has been implemented as an enhancement to the existing gateway configuration toolchain. This generator allows the usage of FIBEX files as a common source of information for both, the configuration of the gateway and the test environment. The test environment is implemented to test and compare different gateway implementations including the developed hardware gateway in realistic environments.

# Chapter 2

## **Communication Networks**

Gateways are based on communication networks. Some of the important protocols in automotive and industrial applications are explained in this chapter, along with their controllers, transport protocols and configuration formats [54] as available.

### 2.1 Basic Concepts

Each communication protocol can be explained by describing its specific function in the ISO/OSI reference model. Additionally the characteristics of their communication controllers (CC) can be described.

**ISO/OSI Reference Model** OSI stands for Open System Interconnection, an initiative that tries to standardize network communication. The OSI Reference Model is nowadays the most often model used to describe communication networks and protocols. Meanwhile this model is standardized in DIN and ISO/IEC 7498-1 [10]. The model is shown in table 2.1.

#### 2.1.1 Physical Transmission

The physical layer describes the media, signal and binary transmission characteristics. The connection to the upper layer is most often implemented in a separate physical layer transceiver chip (PHY).

**Media** The most common media types are physical coupling (copper or fiber optic), radio bands or infrared.

| Layer | Function             |

|-------|----------------------|

| 7     | application          |

| 6     | presentation         |

| 5     | session              |

| 4     | transport            |

| 3     | network              |

| 2.5   | logical link control |

| 2     | media access control |

| 1     | physical             |

Table 2.1: ISO/OSI Reference Model

**Signal Codings** Different signal codings are used to encode the signal on the wire, e.g. bit stuffing, NRZ, BiPhase or Manchester. They can reduce the frequency of the bit stream or enhance clock recovery from the signal.

**Mapping Mechanism** Mapping mechanisms can be used additionally to enhance clock recovery, transmission safety or providing DC freeness. This is done by adding additional bits to the data stream, but not by using calculations to generate these bits. Instead coding tables are used, such as 4B5B and 8B10B. In case of 4B5B a group of 4 source bits can be used to have a group of 5 target bits. As not every target combination is valid, this enhances the error detection or provide space for additional control characters for the Logical Link Control layer.

#### 2.1.2 Media Access Control

The data link layer can be divided into two sublayers named the Media Access Control (MAC) and the Logical Link Control (LLC) layers. This separation is defined in IEEE802 for Ethernet.

The MAC sublayer determines who is allowed to access the physical media at any given time.

**CSMA** The most often used media access protocol is Carrier Sense Multiple Access (CSMA). Carrier Sense describes the fact that a transmitter listens for a carrier wave to prevent sender interference. Multiple Access describes the fact that multiple nodes send and receive on the medium. Transmissions by one node are generally received by all other nodes using the medium.

In pure CSMA systems collisions can still occur, when two nodes start sending nearly at the same time. Receivers then only see frame errors and don't

acknowledge the transmissions, causing the transmitters to timeout and try again. One example using pure CSMA is the ALOHA network.

To solve this problem multiple additions have been developed.

**CSMA/CD** Carrier Sense Multiple Access With Collision Detection (CSMA/CD) is a method to reduce timeouts on collisions. This is not possible with all media and requires special PHYs. When a collision is detected the sender stops immediately and repeats the attempt after a random time. This is the technology used in every Local Area Network (LAN) using Ethernet without switches.

**CSMA/CA** Carrier Sense Multiple Access With Collision Avoidance (CSMA/CA) goes a step further as it tries to avoid collisions at all. Prior to sending, the network node informs the network of the following transmission. This is the technology used in every Wireless Local Area Network (WLAN). Still collisions can occur in the preceding information or transmission stage.

**CSMA/CD+CR** Carrier Sense Multiple Access With Collision Detection and Collision Resolution (CSMA/CD+CR) is collision free. This mechanism is often implemented by using priority based arbitration. When multiple nodes want to transmit, only the node with the highest priority is allowed to send, all other have to wait. This mechanism is used in the Controller Area Network (CAN).

#### 2.1.3 Logical Link Control

The Logical Link Control (LLC) as defined in IEEE 802.2, can modify data on transmit or receive, f.e. to add and remove additional source and target address information. Optionally flow control, detection and retransmission of dropped packets (data integrity) and acceptance filtering can be done. Most Ethernet bridges and switches work on the LLC.

**Data Integrity** Data integrity always means to put additional bits of redundant information to the data stream to detect or even correct erroneous data.

**Parity** The simplest form of error detection is using parity bits. Based on the number of high or low bits and depending on even or odd parity, an additional bit is added to the data stream. Of course the error detection only works with

an odd number of wrong bits. More wrong bits will make all results meaningless. This also means, that multiple wrong bits can have a correct parity and the errors are not detected at all.

**CRC** The Cyclic Redundancy Check (CRC) provides a larger number of bits to detect errors. It is a type of a hash function to generate a checksum using polynomial division. The relevant data bits and the number of CRC bits are flexible.

**Message- and Address-oriented Communication** A transmission is a broadcast on the network media. Depending on the filter mechanism on the receiver side, a communication can be message-oriented or address-oriented.

**Message-oriented Communication** means in this context, that a Message ID is transmitted with every frame and is used to filter the messages on the receiver side. The receiver selects, which broadcasts are relevant for this network node. Most of the time the Message ID is sufficient to describe the contents. Then transport protocols are not necessary. An example for message-oriented communication is CAN.

Address-oriented Communication means that every message is provided with a Sender or Receiver ID. The sender selects, which nodes should receive the message. As the message contents are not described by the IDs, further transport protocols are necessary. An example for message-oriented communication is Ethernet and IP as transport protocol.

**Message Filtering** In either case filtering can be done in hardware or software, mainly depending on the required functionality and the available communication controllers and CPUs.

**Message Trigger Mechanism** Depending on the message trigger mechanism, the protocol can be event-triggered or time-triggered.

**Event-Triggered Protocols** are protocols, where new messages are sent as soon as the wire is free. This allows low latency communication as long as the network utilization is kept to a minimum. Also event-triggered communication provides the maximum usage of bandwidth on collision free networks. An arbitration is done with each transmission to select which message will be the

next. Low priority messages can lose the arbitration, when the bus load is high. The sending delays for these messages are then not deterministic any more.

**Time-Triggered Protocols** are protocols, where messages are send in fixed time slots defined in a schedule table. This is called Time Division Multiple Access (TDMA). When the time slots can be flexible in duration, this is sometimes referred to as Flexible Time Division Multiple Access (FTDMA), e.g. FlexRay. Arbitration and prioritization are still possible in every slot, e.g. TTCAN. Latency times are usually longer, as the time between a message send request and the actual transmission depends on the message position in the schedule table. Time-Triggered Protocols are predestined for real-time applications, as the message transmission can be made deterministic.

#### 2.1.4 Upper Layers

Most often upper layers are implemented in software and are used in addressoriented networks.

**Network Layer** Path determination and logical addressing is provided by the network layer. In Ethernet the Internet Protocol (IP) is an example of such a network layer protocol.

**Session Layer** Mechanisms for host-to-host communication are provided by the session layer. One example is the Transmission Control Protocol (TCP/IP), which is based on the Internet Protocol.

**Presentation Layer** The presentation layer defined the representation of data. Encryption is a possible presentation provided in this layer. XML, the Extensible Markup Language, is another one.

**Application Layer** Network processes, which communicate using the network, are contained in the application layer.

#### 2.1.5 Communication Controller

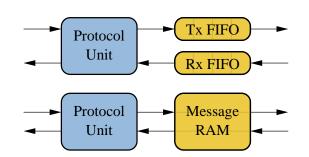

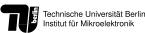

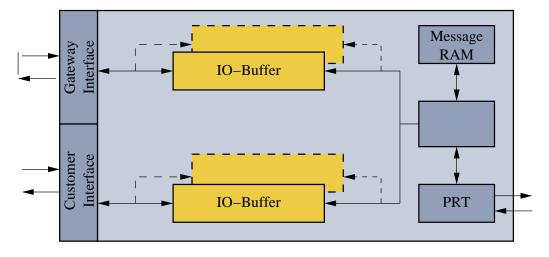

Communication controllers can be grouped into two main categories based on their mechanism of storing messages for receiving and transmitting as shown in figure 2.1.

Figure 2.1: FIFO- / MRAM-based Communication Controller

**Message RAM** Message RAM (MRAM)-based communication controllers have their own RAM in which they store all relevant messages and control information. Every message can be accessed whenever it is necessary and in no specific order. As the Message RAM needs to be accessible from the network side and from the host side for loading and storing messages, access protection must be implemented.

**Memory Mapped Access** In memory mapped implementations, where the Message RAM is mapped in the address space of the host CPU, mutual exclusion (Mutex) bits are necessary. As long as this locking bit for a specific message is set, the other side cannot access the message. This can lead to conflicts, especially when having time-triggered communication controllers, which need to have full access at any time.

**Message Handler Access** In this implementation direct access to the Message RAM is not possible. Instead a message handler is used to arbitrate between concurrent accesses to the Message RAM from the network and host side. At least one message buffer register is used to signal requests for load and store operations to the message handler from the host side.

**FIFO** Opposite to MRAM-based communication controllers, FIFO-based controllers store their messages in a FIFO buffer. A prioritization for message priority or message age is possible, but very uncommon. Therefore only the oldest message can be read or send at one time.

**Basic** A basic communication controller is a sub-type of a FIFO-based communication controller with only limited FIFO sizes, normally one or two messages per direction. These controllers are small in size, but require a high performance CPU in order not to lose any messages on receive and possible wait before transmitting new messages.

**DMA** All types can be enhanced by a DMA controller to transfer messages between the system memory and the internal storage. This reduces data transfers done by the CPU significantly.

### 2.2 Controller Area Network

The Controller Area Network (CAN) is a serial communications protocol developed by Robert Bosch GmbH, efficiently supporting distributed real time control with a very high level of security [30].

Its domain of applications ranges from high speed networks to low cost multiplex wiring. For example in automotive electronics engine control units, sensors, anti-skid-systems, e.g. are connected using CAN. At the same time it is cost effective to install CAN into vehicle body electronics, such as lamp clusters, to replace the wiring harness otherwise required.

**DeviceNet** DeviceNet [26] is a CAN based Layer 7 protocol, which was originally developed by Rockwell Automation, former Allen Bradley. Operation of the DeviceNet is based on an object-oriented communication model. DeviceNet is maintained by Open DeviceNet Vendor Association (ODVA). It is mainly used in industrial applications, especially in factory automation.

**Further Specifications** Further interesting specifications are ISO 11783 (ISOBUS) for agricultural engineering, ISO 11992 for trucks and trailers, NMEA 2000 [22] for maritime electronics, CANaerospace [19] for avionics and space technology and CanKingdom [6] for machine control.

#### 2.2.1 Protocol Description

CAN is best described using the ISO/OSI reference model.

**Physical Layer** The most common media type for CAN is twisted pair [31, 38]. Further derivatives also work over single wires [9], optical wires and radio bands [39]. The bit rates are normally between 5 kBit/s and 1 MBit/s.

**MAC Layer** On the MAC layer CAN uses NRZ encoding with bit stuffing. Multi master access to the media is provided by the CSMA/CD+CR protocol. Collision avoidance is done by bitwise arbitration, where the arbitration field is Technische Universität Berlin Institut für Mikroelektronik

used to define a static priority. The mechanism is therefore sometimes referred to as CSMA/BA for Bitwise Arbitration.

**LLC Layer** The controller automatically tries to retransmit corrupted messages or messages which lost arbitration, as soon as the bus is idle again. A distinction between temporary errors and permanent failures of nodes is made and defect nodes switched off autonomously.

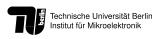

Figure 2.2: CAN Standard and Extended Frame Format

The CAN protocol version 2.0B defines message identifiers to have 11-Bit or 29-Bit depending on standard or extended frame format (see figures 2.2). Messages can have a payload of up to 8 bytes.

#### 2.2.2 Higher Layer Protocols

The CAN protocol is specified in ISO 11898. Several more standards from transport protocols to higher layer specifications are based on this and have been developed towards specific application areas.

**CANopen** The CANopen [2] profile family specifies standardized communication mechanisms and device functionalities. CANopen is maintained by CAN in Automation (CiA). Application areas are industry automation and embedded applications.

**SAE J1939** SAE J1939 [40] is a communication protocol based on CAN for real-time data exchange between electronic control units (ECUs) in the area of commercial vehicles.

### 2.2.3 Communication Controller

Most CAN controllers are either implemented as basicCAN controllers or as fullCAN controllers [3, 4]. BasicCAN controllers usually have one send buffer and one receive buffer, sometimes also with shadow buffers. The message filter mechanism and remote frame support is very limited. FullCAN controllers instead have multiple send and receive buffers and are often implemented using a Message RAM with full support for message filtering and remote frame support. Some variants already allow the connection to multiple CAN channels [18].

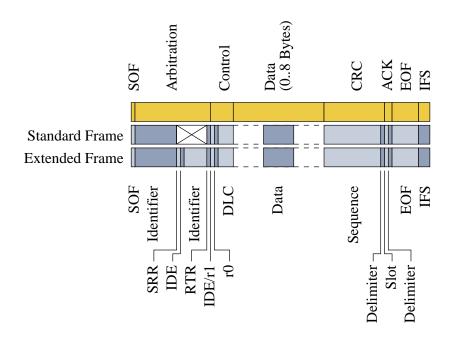

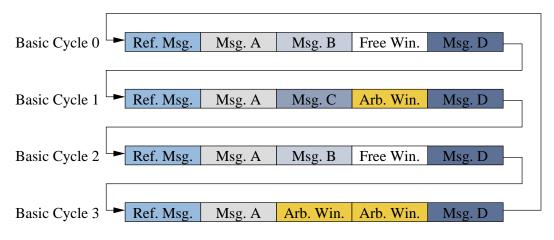

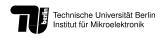

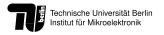

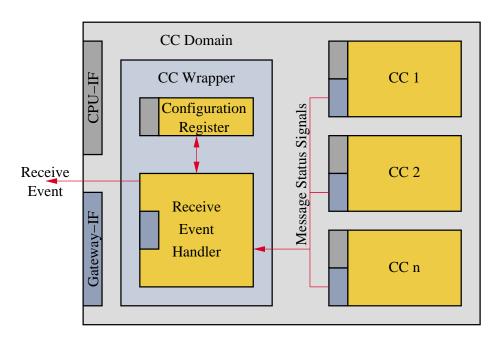

**Overview C\_CAN** The most common Message RAM based CAN controller is the Bosch C\_CAN shown in figure 2.3. The C\_CAN [32] is a single channel CAN module that can be integrated as stand-alone device or as part of an ASIC and is written in VHDL. It consists of the components CAN Core, Message RAM, Message Handler, Control Registers and a Module Interface. The Control Registers also include the CPU Interface Control Registers (CPU IFC Registers) for message transfers from and to the Message RAM.

Figure 2.3: C\_CAN Block Diagram

**CAN Core** The CAN Core implements the functionality required to perform the serial communication on the CAN bus according to the protocol specification.

**Message RAM** For the communication on a CAN network, individual message objects can be (pre-)configured. The message objects and related configuration data are stored in the Message RAM with 32 message objects. Successors of the C\_CAN module can be given different numbers of message objects at synthesis time, such as 16, 32, 64, 128.

**Message Handler** All functions concerning the handling of messages are implemented in the Message Handler. This includes the transfer of messages between the CPU Interface Control Registers, CAN Core and Message RAM, acceptance filtering and the handling of transmission requests and interrupts.

**Interface Registers** Two sets of CPU Interface Registers are used for the data transfer between the CPU's peripheral bus and the Message RAM. They consist of the complete data, header and control information used in the C\_CAN module. All host CPU accesses to messages in the Message RAM are made through the Interface Registers.

#### 2.2.4 Configuration Format

From all the CAN-supporting configuration formats, only one is widely used.

CANdb++ The most common configuration format for CAN is CANdb++ from Vector-Informatik [50, 51], also known as DBC files. CANdb is able to define messages, signals and signal groups. Each information and signal state can be given a name and a comment. Additional information can be defined for physical units and linear conversion formula. Unfortunately there was never a public specification of this format. Only a CANdbLib Class Library (DLL) for Microsoft Visual C++ [52, 53] is available.

### 2.3 Time-Triggered Controller Area Network

Time-Triggered CAN (TTCAN) is a higher level protocol having a Time Division Multiple Access (TDMA) mechanism on top of the event-triggered CAN protocol.

As TTCAN is based on CAN, only the additional protocol definitions and communication controllers are described in the following sections.

### 2.3.1 Protocol Description

For Time-Triggered networks a global time information must be available to all connected nodes.

**Reference Message** In TTCAN this global time is provided by a reference message send by one time master (and up to seven potential time masters). The slaves synchronize to this reference message.

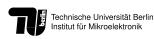

Figure 2.4: TTCAN Matrix Cycle

**Transmission Columns** Each reference message starts a basic cycle with a constant number of transmission columns. These transmission columns can be used for reference messages, time triggered windows, arbitration windows or can be free windows. The arbitration windows are available for event-triggered communication.

**Matrix Cycle** A frame can have a repeat factor higher then one, thus doesn't need to be sent in every basic cycle. Therefore up to 64 different basic cycles can be defined. All basic cycles together are called a matrix cycle.

**Specification** TTCAN is specified in ISO 11898-4 in addition to the CAN protocol itself.

#### 2.3.2 Communication Controller

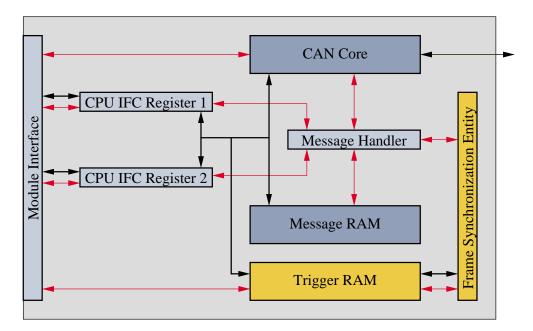

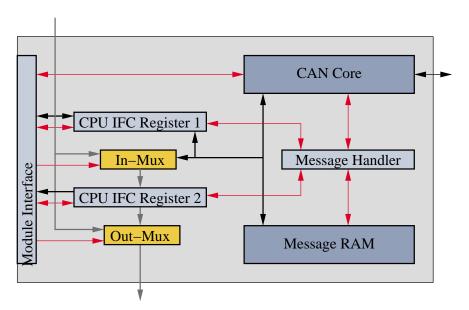

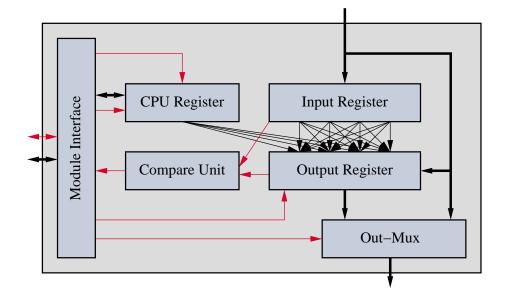

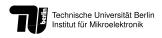

The TTCAN module (also provided by Bosch as VHDL code to be synthesized in FPGAs and ASICs) is based on the described C\_CAN module. Only two functional blocks, (see Figure 2.5) the Trigger Memory and the Frame Synchronization Entity, have been added.

Figure 2.5: TTCAN Block Diagram

**Trigger Memory** The Trigger Memory stores the time marks of the system matrix that are linked to the messages in the Message RAM. The data is provided to the Frame Synchronization Entity.

**Frame Synchronization Entity** The Frame Synchronization Entity is the state machine that controls the time triggered communication. It synchronizes itself to the reference message on the CAN bus, adjusts the cycle time and generates Time Triggers.

**Interface Register** The TTCAN module also uses two interface register sets to transfer the data between the Message RAM and the CPU. Both can be accessed independently from each other. The function of the registers is identical with the exception of the access from the second Interface Register to the Trigger Memory in the initialization process.

### 2.4 FlexRay

The FlexRay protocol aims to be fast and redundant. It was developed towards safety and fault-tolerant systems, e.g. for the use in X-by-Wire applications (Brake-, Drive- and Steer-by-Wire) [29, 7].

#### 2.4.1 Protocol Description

The FlexRay protocol is derived from several other protocol standards, especially ByteFlight [27] and TTP/C [49] and has therefore many similarities.

**Physical Layer** Two physical layer transceivers [28] connect the communication controller to two channels of twisted pair wires for redundancy. Three different bit rates are normally used: 2.5 MBit/s, 5 MBit/s or 10 MBit/s.

**Data Link Layer** FlexRay uses the NRZ in combination with 8B10B encoding for the data parts of the frame.

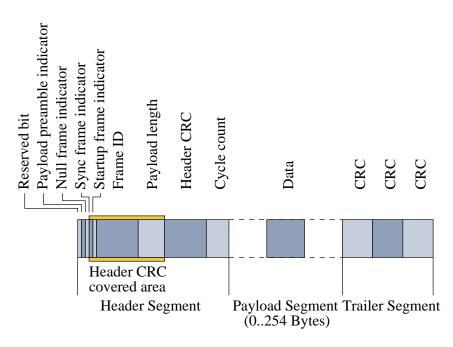

Figure 2.6: FlexRay Frame Format

**Communication Cycle** A FlexRay communication cycle consists of four parts: The static segment, the dynamic segment, the symbol window and the network idle time. A frame in the communication cycle is shown in figure 2.6.

**Macrotick/Microtick** All messages are sent at defined times measured in macroticks and microticks. This concept was derived from TTP/C [49].

**Static Segment** The static segment provides synchronous time-triggered communication using a TDMA protocol.

**Dynamic Segment** In the following asynchronous dynamic segment minislots allow event-triggered communication using prioritization based CSMA/CA similar to ByteFlight [27].

**Symbol Window** The symbol window provides basic communication with a bus guardian. A bus guardian terminates nodes which do not act conform to the protocol specification.

**Network Idle Time** The network idle time allows to calculate clock corrections and other cycle related tasks before the next communication cycle starts.

**Cycle Repetition** A frame doesn't need to be sent in every basic cycle, but can also be sent with another repeat factor. Therefore up to 64 different basic cycles can be defined. This is similar to TTCAN.

**Clock Synchronization** The multi-master distributed clock synchronization mechanisms, necessary for the timing of the communication cycle, differentiates the FlexRay cluster from other networks with independent clocks. In a cycle, up to 15 time masters can send their synchronization message. All nodes adjust their view of the global time using a voting mechanism during the network idle time. The synchronization algorithm in use is the Fault-Tolerant Midpoint Algorithm.

**Cold Startup / Integration Startup** To connect to the network every node has to run a startup, whereas the first two nodes are the cold start nodes and the following are integration nodes.

#### 2.4.2 Communication Controller

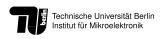

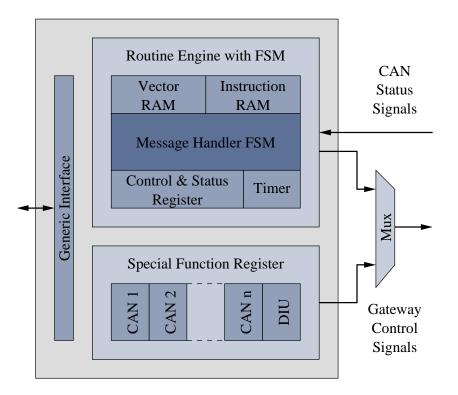

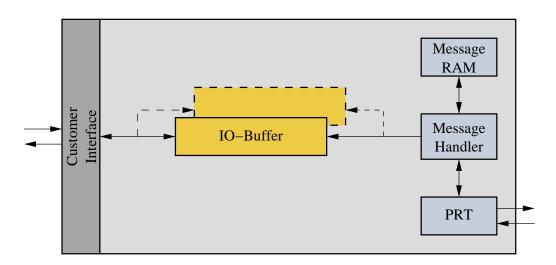

The Bosch E-Ray module is a FlexRay IP-module that can be integrated as stand-alone device or as part of an ASIC. The components of the module are shown in figure 2.7.

Figure 2.7: E-Ray Block Diagram

**Customer and Generic Interface** The Customer and Generic Interface (CIF, GIF) connects the E-Ray to the customer's specific CPU peripheral bus.

**Input and Output Buffers** The Input and Output Buffers (IBF, OBF) are used for the data transfer between the CPU and the Message RAM.

**Message RAM** The Message RAM is a single-ported RAM that stores up to 128 FlexRay message buffers together with related configuration data (header and data partition).

**Protocol Controller, Transient Buffer RAM** The FlexRay Channel Protocol Controller (PRT) consists of a shift register and FlexRay protocol FSM. They are connected to the Transient Buffer RAMs (TBF) for intermediate message storage and transfer to the Message RAM.

**Message Handler** The Message Handler (MHD) controls data transfers between the Input Buffers, Output Buffers and Transient Buffers and the Message RAM.

**Global Time Unit** The Global Time Unit (GTU) is used for the clock generation and synchronization and for the timing control of the static and dynamic segments.

**System Universal Control** The System Universal Control (SUC) controls the wakeup, startup and operation modes.

**Frame and Symbol Processing** The correctness of received frames is checked by the Frame and Symbol Processing (FSP) unit.

**Network Management** The network management vector contains a value which is OR'ed with each received network management frame. This is arithmetic is handled by the Network Management (NEM) unit.

**Interrupt Control Unit** The Interrupt Control unit(INT) handles the interrupt flags lines by assigning the flags to the status and error interrupt lines and setting and resetting the interrupt registers.

#### 2.4.3 Configuration Formats

The configuration of FlexRay is very complex as it does not only cover the frame configuration, but also the complex cluster and controller configurations.

**xCDEF** The XML Cluster Definition File (xCDEF) was defined by De-ComSys for their FlexRay tools. This file format is also used by other tool manufacturers as well. Detailed information of this format are not officially available from DeComSys.

**FIBEX** Nowadays FlexRay nodes are configured by the FIBEX format, described in section 3.5.1.

### 2.5 Media Oriented System Transport

The Media Oriented System Transport (MOST) [21, 20] is a networking standard intended for interconnecting multimedia components in automobiles and other vehicles. It differs from existing vehicle bus technologies in that it

connects via Plastic Optical Fiber (POC), thus providing a ring bus-based networking system at bit-rates higher than available on most previous vehicle-bus technologies.

### 2.5.1 Protocol Description

The MOST specification defines all seven layers of the ISO/OSI Reference Model for data communication.

**Cable** MOST networks normally work over optical fibers using an optical PHY (oPHY). Very new and still unused is the possibility to also use unshielded twisted pair wires (UTP) using an electrical PHY (ePHY).

**Physical** The MOST network often employs a ring topology, but star configurations and double rings for critical applications are possible and may include up to 64 devices or nodes. BiPhase is used for the signal coding.

**TDMA, CSMA/CA** In the ICM segment TDMA is used, CSMA/CA in the MCM and MDP segments.

**Timing Master** A Timing Master is one of the nodes, which continuously feeds data frames into the ring or acts as the gate for data. The preamble or packet header repeatedly synchronizes the rest of the nodes called Timing Slaves.

**Bandwidth** The total bandwidth (including streaming data and packed data) is approximately 24.8 MBit/s. Up to 16 stereo channels with a sample frequency of 44.1 kHz can be configured.

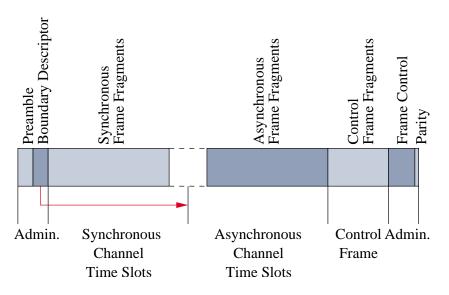

**Data Link Layer** Data is transferred in blocks of 16 frames. Beside administrative information and control data, a MOST frame contains time slots for synchronous and asynchronous transfer channels. Figure 2.8 shows the frame format of a MOST frame. The boundary between synchronous and asynchronous time slots can be selected using the boundary descriptor specified in quadlets (4 Bytes).

The control data and the asynchronous channel contain frames itself, which are transferred in fragments over the MOST frames in a block. A control frame is 32-Bit long and therefore contained in two MOST frames. An asynchronous frame is 58 byte long including source address, target address and CRC.

Figure 2.8: MOST Frame Format

#### 2.5.2 Communication Controllers

Currently MOST communication controllers are available only from SMSC, former Oasis and Xilinx.

**OS8104** The first Network Interface Control (NIC available for MOST was the OS8104 [45, 24, 23]. This controller connects on one side to the optical PHY and on the other to an interface that could either be used for connecting four  $I^2S$  and one  $I^2C$  connection or for connecting a packet combined mode (PCM) interface.

**API/SDK** When using the OS8104, most of the transport protocol functions have to be implemented in software. Therefore an Application Programming Interface (API) and a Software Development Kit (SDK) are available. The advantage of having the API running on the host CPU and the reason, why many OEMs still use the OS8104, is the upgrade possibility together with the rest of the ECU software.

The MOST Network contains the following simultaneous operating networks and frames:

- MOST Control Messages (MCM) are used to manage the network and communicate control data across the network.

- MOST Data Packet (MDP) are used to support nodes that communicate asynchronous data.

• INIC Control Messages (ICM) are used to support high-speed synchronous data with extremely low overhead, such as audio and video.

**OS81050** The OS81050 [46, 42] (also called INIC@25) comes with an improved host interface called the Media Local Bus (MLB [25]). It is called Intelligent Network Interface Controller (INIC), because of the fact, that most of the protocol stack previously running in software now runs as firmware on a specialized core in the NIC itself. This makes upgrading the ECU more complicated or even impossible, as not only the software needs to be handled, but also the INIC firmware.

**OS81082** The newest development is the OS81082 (also called INIC@50) [47]. The main advantage compared to the OS81050 is the possibility to connect an electrical PHY [43].

### 2.6 Network Architectures

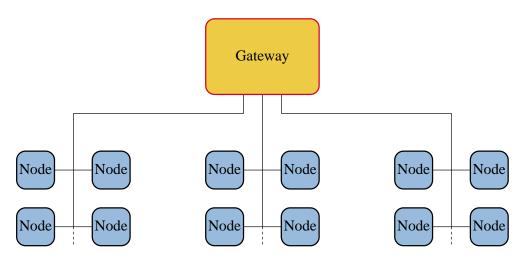

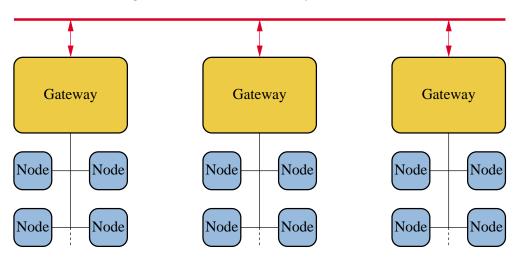

Todays automobiles consist of multiple communication networks of different type. Each network is implemented to handle a specific function domain, such as powertrain or infotainment. The interconnection between these networks is provided by gateways. When analyzing complete network architectures, two can be described as being most important: Central Gateway Architectures and Backbone Architectures.

These network architectures will be described in the following paragraphs. For simplicity the following figures present the physical topology only as a simple bus line, but in fact it depends on the type of communication network.

**Central Gateway Architecture** A central gateway architecture has only one gateway, that connects the communication networks. This creates high demands on the performance, but also provides a latency minimized communication over the networks. The demands for safety are very high, as the gateway is a single point of failure. An advantage lies in the possibility to provide one central diagnostic access to the automotive network.

**Backbone Architecture** In contrary, in a backbone architecture every communication network has its own gateway connected to a central high speed backbone network, such as FlexRay or IDB1394. This reduces the demands on performance and safety as every gateway has only two network connections. Backbone architectures will therefore become more established in future [68].

Figure 2.9: Central Gateway Architecture

Figure 2.10: Backbone Architecture

**Mixed Architecture** In fact many automotive networks have mixed architectures, somewhere between a central gateway and backbone architectures. The low-speed LIN bus for example is usually connected to a body controller ECU that itself is connected to a central gateway or backbone gateway.

**Impact on the Gateway** A gateway designed as central gateway with high performance and safety requirements can easily be used as a backbone gateway that has lower requirements. Therefore the difference has an impact mainly on the scalability of the gateway.

## Chapter 3

# **Current Gateways**

Automotive gateways are developed within their limitation of rough physical environment, required efficiency and high production quantities.

In recent years many new automotive features became available because of improved interconnection techniques between different car networks. Therefore new gateways were necessary with almost every car generation.

As hardware usually has longer product cycles, most gateways are implemented in software. Unfortunately most microcontrollers are developed towards different applications. Only few microcontrollers have specialized instruction sets dedicated to provide gateway functionality.

#### 3.1 Requirements

A gateway has to fulfill multiple requirements not only regarding technical, but also economical issues. These can also be used in comparing different implementations.

**Proven Communication Controllers** In automotive applications, the safety of passengers is directly influenced by failures of critical systems. Gateway systems are the most critical ones as they connect multiple ECUs and networks. Therefore it is very difficult to introduce completely new hardware components, such as communication controllers.

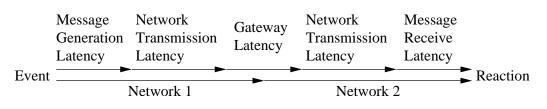

**Low Latency** Generally spoken latency is the period of time between one component generating and sending a message until another component is receiving and handling this message.

Figure 3.1: Latency between two networks

In a gateway environment the latency between two networks can be defined as a sum of

- generation latency to compute a new message after an event,

- transmission latency to transmit the message over the first network (dependent on schedule in time-triggered networks or message prioritization in event-triggered networks),

- gateway latency to process and transfer the content of the received message to a second message,

- transmission latency to transmit the message over the second network and

- receive latency to process and handle the received data.

The generation latency, transmission latencies and receive latency cannot be influenced by the application. These latencies depend on the used bus systems, the transmitting and receiving nodes and the synchronization of the time masters. The only latency that can be actively influenced is the gateway latency, which is in software terms identical to the task's Worst-Case-Execution-Time (WCET) [61]. It depends on the gateway concept, the number of interconnected networks, bus loads and the complexity of the gateway function as described below.

Low Jitter Jitter is the time in which the latency varies during normal message transmissions. Having a high jitter is more a problem of event-triggered communication systems, where high utilization of the communication link can lead to high delays and unpredictable latencies. For real-time applications a precise prediction of message delays and receive times is much more important then fast message transmits. Therefore gateways intended to be used in real-time applications are required to have low jitter.

Scalability, High Bandwidth and Throughput Gateway systems are often used in environments where high-speed networks need to be connected. FlexRay, MOST and Ethernet each have a bandwidth of more than 10 MBit/s. The throughput needs to be high enough to be able to process these data even under worst case conditions. Scalability can therefore be described as the impact of high network utilization and throughput on latency, jitter and frame loss.

Low Power Consumption, Temperature, Frequency and Electromagnetic Radiation On the other hand especially in automotive environments, low power consumption is a crucial factor, not only to be economical and efficient. High power consumption also means high temperatures that makes it difficult to fulfill the requirement for the large automotive temperature range from -40 C up to 125 C. It is often a result of complex hardware, where signal changes and state transitions happen with high clock frequencies. High frequencies are also causing high electromagnetic radiation which can affect other ECUs, sensors and actuators as well.

Low Cost and Gate Count In applications with high production quantities, the benefits can be increased dramatically by reducing the production cost of each part. The only way to do this in hardware is to reduce the gate count and RAM requirements by an innovative concept and an optimized implementation. Optimization is reflected in a reduced software code and hardware die size, which allows more dies per waver and therefore higher quantities at the same price. Also smaller die sizes often have a positive influence on the power consumption. On the other hand, a lower gate count allows to integrate more functionality without changing the die size.

### 3.2 Tasks

The movement of large amounts of complete messages between networks is only one task a gateway has to perform. Transfers can include operations on the signal level and usually need to be done with a specific time behavior.

**Frames and Signals** In many cases one frame consists of some few independent e.g. sensor and/or actuator signals of one or several bits. To minimize the used bandwidth of the connected buses, messages transmitted contain only signals necessary on the target bus. Therefore usually these transmitted messages are created from signals out of several received frames. However,

the bit position can vary in both messages so that many bit manipulating operations are necessary.

**Periodic Transmissions** To increase the safety of in-car systems, periodic transmissions can be used. Therefore the gateway has to buffer the message data and a timer is used to periodically transmit the message.

**Immediate Reaction** The gateway can react differently to the reception of a message. It is not only possible to immediately forward the frames and signals therein, but it is also possible to only send new messages, if specific parts of the received message have changed. The gateway has to compare the old and the new message and has to react accordingly. It is also possible to store just the received data for periodic transmission without immediate forwarding.

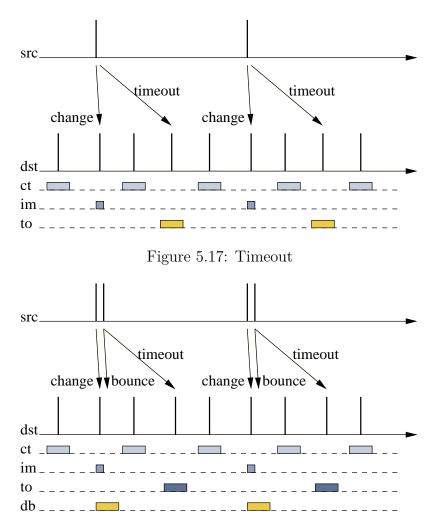

**Timeout Handling** The gateway can also react to messages, that are not received within a specified time. It is then possible to set timeout bits in certain messages, mark signals as obsolete, send additional timeout frames or change the interval duration of periodic transmissions.

**Debouncing** Some ECUs try to increase transmission safety by sending the same message multiple times in a short period. As this mainly wastes precious bandwidth, a gateway can be configured to react to these frames only once. Once a debounce time has passed, frame transmissions are allowed again.

**Transport Protocols** Some transport protocols require the gateway to not only forward frames, but to process them. This is especially true, when the gateway should transparently convert one transport protocol to another, which is always the case when different network types and therefore protocols are involved.

**Network Management** A gateway also needs to handle network management requests and responses on all connected networks. If these networks are of different type, a conversion is necessary.

**Further Control Applications** The previous tasks have shown the complexity of gateway implementations. Additionally microcontrollers performing the gateway function have to process several control applications, such as the evaluation of sensor data or the adjustment of actuators.

### 3.3 Gateway-Optimized Microcontroller

To support software gateways in fulfilling the requirements and manage their tasks, few microcontrollers have been developed especially for gateway applications. A characteristic of these controllers is that they already have many communication controllers integrated. The connection to the CPU is provided by high speed on-chip buses to reduce latency and increase throughput. In addition DMA controllers or network coprocessors can be integrated.

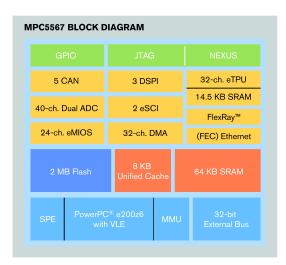

**Freescale MPC5567** The MPC5567 [66] is a microcontroller developed by Freescale, shown in figure 3.2.

Figure 3.2: Freescale MPC5567 Block Diagram

It has a high-performance 32-Bit PowerPC core with a clock frequency of up to 132 MHz and a MMU with 32-entry fully associative translation lookaside buffer. This processor core is enhanced by a signal processing extension (SPE), which brings additional capabilities for DSP, SIMD and floating point operations.

The enhanced Time Processor Unit (eTPU) is a programmable unit on which most timer handling functions of the gateway application can be offloaded. Additionally a 32-channel enhanced DMA controller can be programmed to automatically copy data from and to the communication controllers. This is one of the first device in which Freescale integrated their own FlexRay controller. It acts beside five CAN cores and an Ethernet core.

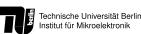

**Infineon TriCore TC1130** The Infineon TriCore TC1130 [69, 70, 71, 72], as shown in figure 3.3, provides four CAN controllers [11] and one Ethernet controller.

Figure 3.3: Infineon TriCore TC1130 Block Diagram

The 32-Bit TriCore architecture combines RISC, CISC and DSP functionality with a MMU and a FPU in a single chip. It can run with a core clock frequency of up to 150 MHz.

The DMA controller can be used to transfer data to and from the four CAN controllers and the Ethernet core. As the device supports hardware controlled context switches for tasks and interrupts, the gateway latency and jitter is reduced.

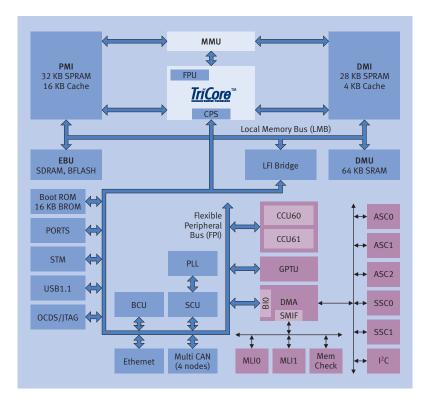

**NEC V850** The NEC V850 [76] family is especially well suited for highend chassis applications in the automotive area. One family member, the V850E/PH3 "Phoenix-FS", is shown in figure 3.4.

The V850E CPU is a 32-Bit RISC core with integrated FPU, a clock frequency of up to 128 MHz and a maximum performance of 166 MIPS.

The two CAN controllers and one FlexRay controller can transfer their data from and to the system RAM using an 8-channel DMA controller.

**Freescale HCS12X** The HCS12X [65] contains a 16-Bit HCS12 compatible CPU on which the main application software runs. The suffix X stands for an

Figure 3.4: NEC V850E/PH3 Phoenix-FS Block Diagram

additional XG ate [64] peripheral coprocessor module, that has been added to the system. This parallel processing module offloads the CPU by providing high speed data processing functions for transfers between peripheral modules, RAM and I/O ports.

The XGate offers a slight performance increase, but requires specialized software [63]. Standard gateway software, as described in the following section, is currently not available on the XGate and would not run fast enough on the HCS12. Therefore the HCS12X is currently only used without the XGate in gateway implementations. Although the XGate can be used to offload certain tasks (interrupt, timers) of the HCS12 software application.

### 3.4 Software Gateways

Technische Universität Berlin Institut für Mikroelektronik

For a long time the software structure of a gateway was not standardized. Therefore many different vendors had their own incompatible implementations of the same functionality, e.g. Vector Informatik, 3Soft or K2L.

**Operating System** The real-time operating system (RTOS) used by almost all automotive ECUs is OSEK/VDX as standardized in ISO 17356 [73]. It provides task management, different application modes, interrupt handling, event control mechanisms, resource management, alarms, messages, different hook routines for error handling, tracing and debugging.

**Driver** Every hardware module, such as the communication controllers, do need a software driver to adapt to this hardware module for low-level functions and network management functions. The CAN Driver for example provides services for initiating transmissions and callback functions for notifying receive events independently from the hardware.

**Network Management** provides functions for network wide shut down of the communication system, for determining the network configuration at startup, for monitoring the network configuration during operation and for providing information of the current network status.

**Communication Module** provides signal and frame routing functions between equal (e.g. CAN/CAN) or different (e.g. CAN/FlexRay) vehicle network systems. It is therefore also responsible for fragmentation and defragmentation of data.

**Transport Protocol Modules** provide segmentation of data in transmit direction, collection of data in receive direction, control of data flow and detection of errors (e.g. messages loss/doubling/sequence).

#### 3.4.1 K2L Gateway

K2L developed a software gateway with the described components. Their demonstration system is called MoCCa Vario II [74]. It is able to connect up to six CAN, two FlexRay, one MOST and multiple low speed bus systems. The software is portable to different Real-Time Operating Systems. The signal conversion and routing characteristics are defined in a table format, which contains operations for bit, byte, word and various complex conversion methods like scaling signal values or adding constants to messages. A configuration tool is provided for this proprietary tabular gateway format. The overall gateway application is embedded in a modular framework, suitable also to integrate other, non gateway applications.

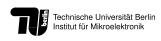

#### 3.4.2 Automotive Open System Architecture

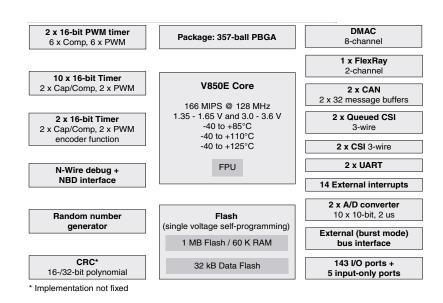

The Automotive Open System Architecture (AUTOSAR) Initiative tries to standardize complete software architectures [58, 59] to improve and fasten application developments [62]. Additionally, it does not only specify the current basic software, such as the OSEK/VDK operating system [79, 77, 78], but also

parts of the applications, the toolchain and the configuration formats. Several components are already available as shown in figure 3.5.

Figure 3.5: AUTOSAR Components

**Microcontroller Abstraction** Layer is the lowest software layer of the Basic Software. It contains drivers, software modules with direct access to the microcontrollers internal peripherals and memory mapped microcontroller external devices.

**ECU Abstraction** Layer interfaces the drivers of the Microcontroller Abstraction Layer. It also contains drivers for external devices. It offers an application programming interface (API) for access to peripherals and devices regardless of their location (microcontroller internal/external) and their connection to the microcontroller (port pins, type of interface).

**Services** Layer is the highest layer of the Basic Software and has the highest relevance for the application software. While access to I/O signals is covered by the ECU Abstraction Layer, the Services Layer offers operating system functionality, vehicle network communication and management services, memory services (NVRAM management), diagnostic services (including UDS communication and error memory) and ECU state management.

**Complex Device Drivers** implement complex sensor evaluation and actuator control with direct access to the microcontroller using specific interrupts and/or complex microcontroller peripherals, e.g injection control, electric valve control and incremental position detection.

**Runtime Environment** The RTE is a middleware layer providing communication services for the application software (AUTOSAR Software Components or AUTOSAR Sensor/Actuator components). The AUTOSAR Software Components communicate with other components (internal or external) or services via the RTE.

#### 3.4.3 X2E Gateway

X2E integrated and ported the K2L software gateway to an Altera FPGA using a NIOS II softcore processor. This combination makes it possible to easily implement various parts of the software in hardware.

The NIOS processor allows to integrate user-defined instructions for gateway specific tasks. With recent versions (since 6.0) of the Quartus synthesis software [90], it is also possible to use a technique called C2H [88]. C2H allows to select certain C functions and to synthesize them as function blocks in hardware, which improves the gateway performance even more.

## 3.5 Configuration Data Formats

Gateway configurations are based on non-standardized description formats. Data exchange between these formats is inherently error prone and time consuming.

Simple frame and signal relations between different CAN channels can already be described in CANdb (see section 2.2.4). When more complex functions are necessary, non-standardized user-defined attributes can be used. CANdb is limited to only one CAN network, however multiple files can be used.

A common description format usable for different networks types and gateway configurations was necessary. The Field Bus Exchange Format (FIBEX) provides these information.

The Automotive Open System Architecture adapted this format for their own System Constraint Templates.

#### 3.5.1 Field Bus Exchange Format

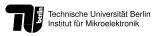

The Field Bus Exchange Format (FIBEX) is an XML-based file format, the upcoming standard for network configurations [60], which combines information about each aspect of a complete in-car network including controllers, channels, frames and signals [55, 56]. It is also the first standard to describe gateway configurations. The exchange format covers the functional network, the system topology and the communication level.

**Standardization** FIBEX is based on an initiative of BMW and was developed in cooperation with automobile manufacturers, suppliers and tool producers, proposed for data exchange between tools that deal with message-oriented bus communication systems. It is now being maintained at the Association for Standardisation of Automation- and Measuring Systems (ASAM e.V.).

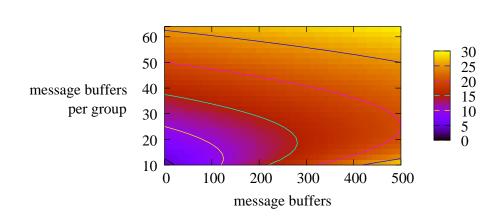

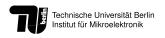

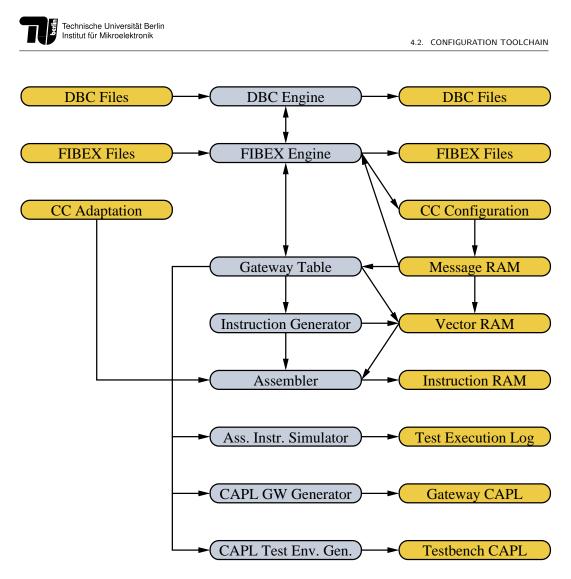

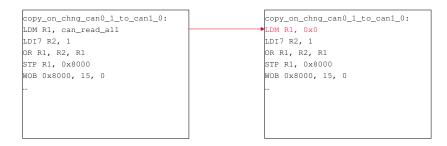

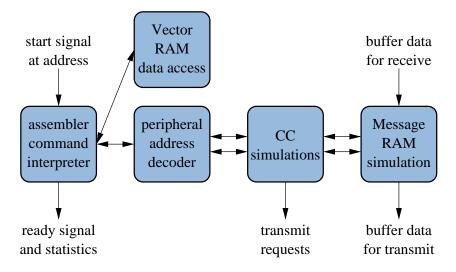

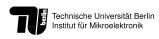

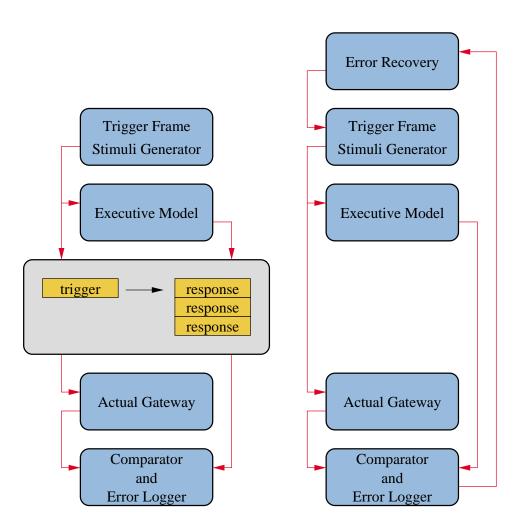

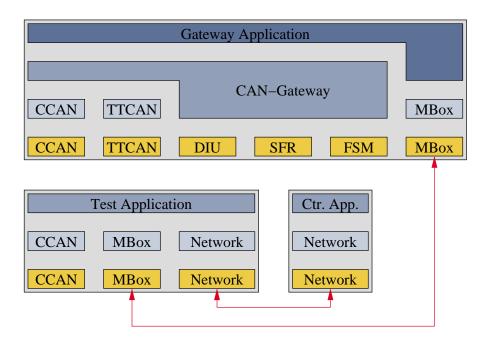

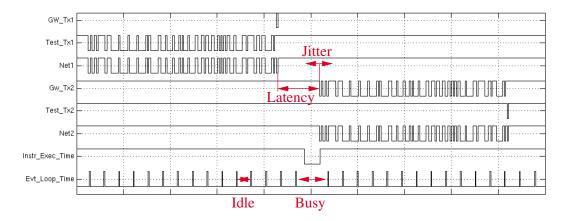

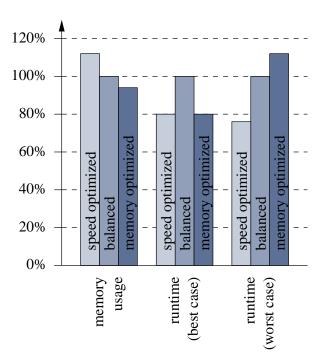

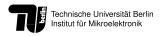

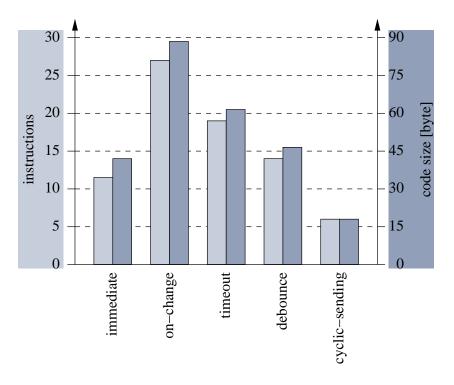

**Supported Networks** FIBEX tries to be widely independent from all communication controller implementations and protocols. In the version 1.2 it is usable for CAN, LIN and FlexRay networks. A MOST extension is available since version 2.0. A standardization for TTCAN is still pending.