Fakultät für Elektrotechnik und Informatik Institut für Softwaretechnik und Theoretische Informatik Lehrstuhl für Security in Telecommunications

# Why Cryptography Should Not Rely on Physical Attack Complexity

vorgelegt von

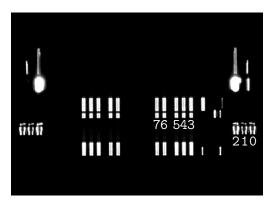

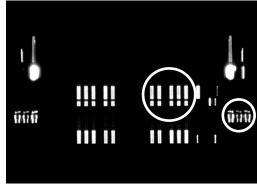

Juliane I. Krämer (Dipl. Math. oec.)

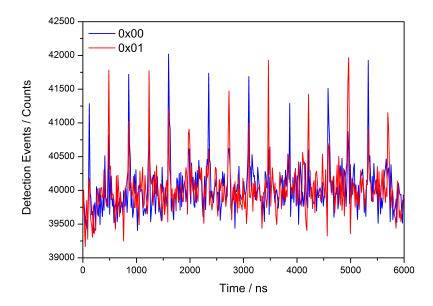

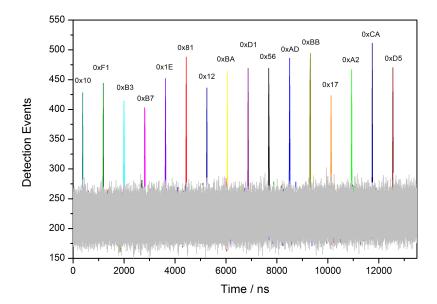

aus Detmold

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades Doktor der Naturwissenschaften (Dr. rer. nat.) genehmigte Dissertation

#### Promotionsausschuss:

Vorsitzende: Prof. Anja Feldmann, Ph.D., Technische Universität Berlin Gutachter: Prof. Dr. Jean-Pierre Seifert, Technische Universität Berlin Gutachter: Prof. Dr. Johannes Buchmann, Technische Universität Darmstadt Gutachterin: Prof. Dr. Tanja Lange, Technische Universiteit Eindhoven

Tag der wissenschaftlichen Aussprache: 23. März 2015

Berlin 2015 D83

| Ich versichere an Eides statt, dass ich diese Dissertation selbständig verfasst und nur die angegebenen Quellen und Hilfsmittel verwendet habe. |

|-------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                 |

| Datum                                                                                                                                           |

|                                                                                                                                                 |

|                                                                                                                                                 |

# Zusammenfassung

Seitdem Mitte der Neunziger Jahre die ersten Seitenkanal- und Fehlerangriffe auf kryptographische Technologien vorgestellt wurden, werden kontinuierlich neue Möglichkeiten physikalischer Angriffe erforscht. Der Gefahr, die von diesen Angriffen ausgeht, wird begegnet, indem auf bekannte Angriffe reagiert wird und Gegenmaßnahmen zum Schutz vor ihnen implementiert werden. Bei physikalischen Angriffen, die zwar prinzipiell bekannt sind, jedoch noch nicht praktisch umgesetzt wurden, verhält es sich hingegen anders. Angriffe, deren Realisierung eine hohe physikalische Komplexität zugeschrieben wird, werden weniger ernst genommen. Das Vertrauen darauf, dass diese Angriffe aufgrund ihrer physikalischen Komplexität nicht möglich sein werden, führt dazu, dass auf keiner Ebene Gegenmaßnahmen für sie entwickelt werden. Dieses Vorgehen ist problematisch, wenn sich im Nachhinein durch die Realisierung solcher Angriffe die Einschätzung der Komplexität als falsch erweist.

In dieser Arbeit werden zwei praktische physikalische Angriffe präsentiert, deren Theorie bereits seit mehreren Jahren bekannt ist. Da diese Angriffe jedoch zuvor nicht erfolgreich praktisch umgesetzt wurden, wurde in ihnen keine Gefahr gesehen. Die Komplexität ihrer Durchführung wurde überschätzt. Zunächst stellen wir den photonischen Seitenkanal vor, der neben der zeitlichen die größtmögliche räumliche Auflösung bietet, aufgrund der hohen Kosten bei seiner ersten Anwendung jedoch bisher nicht ernst genommen wurde. Wir zeigen sowohl einfache als auch differentielle photonische Seitenkanalanalysen. Anschließend präsentieren wir einen Fehlerangriff auf paarungsbasierte Kryptographie, der aufgrund der Notwendigkeit zweier unabhängiger präziser Fehler in einer einzigen Paarungsberechnung bei der Entwicklung von Gegenmaßnahmen nicht berücksichtigt wurde. Wir zeigen, wie Angreifer mit Hilfe dieser physikalischen Angriffe geheimes Schlüsselmaterial symmetrischer und asymmetrischer Algorithmen ermitteln können. Anschließend präsentieren wir Gegenmaßnahmen auf Software- und Hardware-Ebene, mit deren Hilfe diesen neuen Angriffen zukünftig standgehalten werden kann.

Anhand der beiden vorgestellten Angriffe zeigt diese Arbeit, dass die Einschätzung physikalischer Angriffskomplexität fehlerhaft sein kann. Es ist daher falsch, auf sie zu vertrauen. Kryptographische Technologien sollten gegenüber sämtlichen physikalischen Angriffen geschützt werden, seien diese bereits praktisch umgesetzt oder nur theoretisch bekannt. Die Entwicklung von Gegenmaßnahmen erfordert nicht die erfolgreiche Durchführung praktischer Angriffe und sollte daher bereits erfolgen, sobald das Prinzip eines Seitenkanals oder eines Fehlerangriffs verstanden ist.

## **Abstract**

Ever since the first side channel attacks and fault attacks on cryptographic devices were introduced in the mid-nineties, new possibilities of physical attacks have been consistently explored. The risk that these attacks pose is reduced by reacting to known attacks and by developing and implementing countermeasures against them. For physical attacks whose theory is known but which have not been conducted yet, however, the situation is different. Attacks whose physical realization is assumed to be very complex are taken less seriously. The trust that these attacks will not be realized due to their physical complexity means that no countermeasures are developed at all. This leads to unprotected devices once the assessment of the complexity turns out to be wrong.

This thesis presents two practical physical attacks whose theory is known for several years. Since neither attack has previously been successfully implemented in practice, however, they were not considered a serious threat. Their physical attack complexity has been overestimated and the implied security threat has been underestimated. First, we introduce the photonic side channel, which offers not only temporal resolution, but also the highest possible spatial resolution. Due to the high cost of its first realization, it has not been taken seriously. We show both simple and differential photonic side channel analyses. Then, we present a fault attack against pairing-based cryptography. Due to the need for at least two independent precise faults in a single pairing computation, it has also not been taken seriously. We show how attackers can reveal the secret key of symmetric as well as asymmetric cryptographic algorithms based on these physical attacks. We present countermeasures on the software and the hardware level, which help to prevent these attacks in the future.

Based on these two presented attacks, this thesis shows that the assessment of physical attack complexity is error-prone. Hence, cryptography should not rely on it. Cryptographic technologies have to be protected against all physical attacks, have they already been realized or not. The development of countermeasures does not require the successful execution of an attack but can already be carried out as soon as the principle of a side channel or a fault attack is understood.

## **Publications Related to this Thesis**

The primary results of this work have been presented in the following publications:

- Blömer, Gomes da Silva, Günther, **Krämer**, Seifert: A Practical Second-Order Fault Attack against a Real-World Pairing Implementation. In Proceedings of Fault Tolerance and Diagnosis in Cryptography (FDTC), 2014, Busan, Korea

- Krämer, Kasper, Seifert: The Role of Photons in Cryptanalysis. In Proceedings of 19th Asia and South Pacific Design Automation Conference (ASP-DAC), 2014, Singapore

- Krämer, Nedospasov, Schlösser, Seifert: Differential Photonic Emission Analysis. In Proceedings of Constructive Side-Channel Analysis and Secure Design Fourth International Workshop (COSADE), 2013, Paris, France

- Schlösser, Nedospasov, **Krämer**, Orlic, Seifert: Simple Photonic Emission Analysis of AES. Journal of Cryptographic Engineering, Springer-Verlag

- Schlösser, Nedospasov, **Krämer**, Orlic, Seifert: Simple Photonic Emission Analysis of AES. In Proceedings of Workshop on Cryptographic Hardware and Embedded Systems (CHES), 2012, Leuven, Belgium

Additionally, Juliane Krämer has authored the following publications:

- Krämer, Stüber, Kiss: On the Optimality of Differential Fault Analyses on CLEFIA. Cryptology ePrint Archive, Report 2014/572

- Krämer: Anwendungen von identitätsbasierter Kryptographie. SmartCard Workshop 2014, Darmstadt, Germany

- Michéle, **Krämer**, Seifert: Structure-Based RSA Fault Attacks. In Proceedings of 8th International Conference on Information Security Practice and Experience (ISPEC), 2012, Hangzhou, China

- Krämer, Nedospasov, Seifert: Weaknesses in Current RSA Signature Schemes. In Proceedings of 14th International Conference on Information Security and Cryptology (ICISC), 2011, Seoul, Korea

Contents ix/x

# **Contents**

|   | Zusa | amment   | fassung                                   |

|---|------|----------|-------------------------------------------|

|   | Abs  | tract .  |                                           |

|   | Pub  | lication | s Related to this Thesis vii              |

| 1 | Intr | oductio  | on 1                                      |

|   | 1.1  | Thesis   | s Statement                               |

|   |      | 1.1.1    | Problem Statement                         |

|   |      | 1.1.2    | Thesis Contributions                      |

|   | 1.2  | Struct   | ture of the Thesis                        |

| 2 | Mat  | hemati   | ical and Cryptological Background 7       |

|   | 2.1  | Ellipti  | c Curves and Bilinear Pairings            |

|   |      | 2.1.1    | Elliptic Curves                           |

|   |      | 2.1.2    | Bilinear Pairings                         |

|   | 2.2  | Crypt    | ographic Algorithms and Protocols         |

|   |      | 2.2.1    | The Advanced Encryption Standard          |

|   |      | 2.2.2    | Identity-Based Cryptography from Pairings |

|   | 2.3  | Side C   | Channel Attacks                           |

|   |      | 2.3.1    | Timing Attacks                            |

|   |      | 2.3.2    | Power Analysis                            |

|   |      | 2.3.3    | Electromagnetic Analysis                  |

|   |      | 2.3.4    | Other Side Channels                       |

|   | 2.4  | Fault    | Attacks                                   |

|   |      | 2.4.1    | RSA                                       |

|   |      | 2.4.2    | Elliptic Curve Cryptography               |

|   |      | 2.4.3    | Symmetric Cryptography                    |

| 3 | Pho  | tonic E  | Emission Analysis 25                      |

|   | 3.1  | Photo    | nic Emission                              |

|   |      | 3.1.1    | Photonic Emission in CMOS                 |

|   |      | 3.1.2    | Detection of Photonic Emission            |

|   |      | 3.1.3    | Applications of Photonic Emission         |

|   | 3.2  | Exper    | imental Setups                            |

|   |      | 3.2.1    | The Target Devices                        |

|   |      | 3.2.2    | Emission Images                           |

|   |      | 3.2.3    | Spatial and Temporal Analysis             |

x/x Contents

| 4   | The     | Photonic Side Channel                                   | 37  |

|-----|---------|---------------------------------------------------------|-----|

|     | 4.1     | Simple Photonic Emission Analysis                       | 38  |

|     |         | 4.1.1 Physical Attack                                   | 39  |

|     |         | 4.1.2 Cryptanalysis                                     | 42  |

|     |         | 4.1.3 Countermeasures                                   | 55  |

|     | 4.2     | Differential Photonic Emission Analysis                 | 58  |

|     |         | 4.2.1 Physical Attack                                   | 58  |

|     |         | 4.2.2 Cryptanalysis                                     | 62  |

|     |         | 4.2.3 Countermeasures                                   | 73  |

| 5   | High    | er-Order Fault Attacks against Pairing Computations     | 77  |

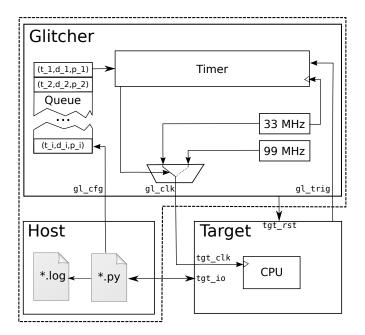

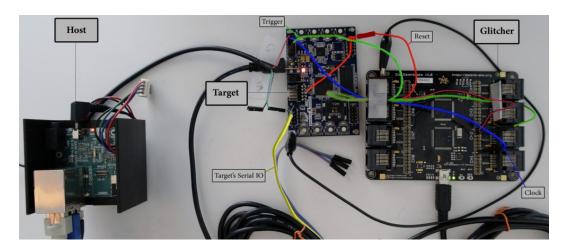

|     | 5.1     | Experimental Setup                                      | 79  |

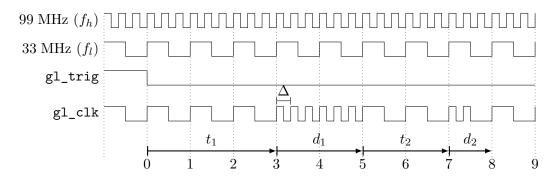

|     |         | 5.1.1 Low-Cost Glitching Platform                       | 79  |

|     |         | 5.1.2 Instruction Skips                                 | 83  |

|     | 5.2     | Physical Attack                                         | 83  |

|     |         | 5.2.1 Realization of Higher-Order Fault Attacks         | 84  |

|     |         | 5.2.2 Second-Order Fault Attack against the Eta Pairing | 85  |

|     | 5.3     | Cryptanalysis                                           | 89  |

|     |         | 5.3.1 Modification of $n$ in the Eta Pairing            | 91  |

|     |         | 5.3.2 Modification of $f$ in the Eta Pairing            | 94  |

|     |         | 5.3.3 Modification of $f$ in the Reduced Tate Pairing   | 96  |

|     | 5.4     | Countermeasures                                         | 98  |

| 6   | Futu    | ire Work                                                | 101 |

|     | 6.1     | The Photonic Side Channel                               | 101 |

|     | 6.2     | Fault Attacks against Pairing-Based Cryptography        | 104 |

| 7   | Con     | clusion                                                 | 107 |

|     | 7.1     | The Photonic Side Channel                               | 107 |

|     | 7.2     | Fault Attacks against Pairing-Based Cryptography        | 108 |

|     | 7.3     | Advice for Cryptographers                               | 109 |

| Ac  | ronyr   | ms                                                      | 111 |

| Lis | st of l | Figures                                                 | 113 |

| Lis | st of . | Tables                                                  | 115 |

|     |         | Algorithms                                              | 117 |

|     |         |                                                         |     |

| Bil | bliogr  | aphy                                                    | 119 |

# Chapter 1

# Introduction

Cryptanalysis is the art and science of revealing secret information of cryptographic systems. Until approximately 20 years ago, cryptanalysts primarily utilized mathematics to analyze cryptographic schemes. In parallel to the development of more sophisticated ciphers, cryptanalysts were also forced to develop stronger analysis methods. To break the Caesar cipher, which was used 2000 years ago, a simple statistical analysis of a ciphertext was sufficient. The Vigenère cipher was also broken with statistical analysis, albeit in the 19th century. Today's cryptanalytic attacks are not as simple as a statistical analysis, but involve complex mathematical techniques: differential cryptanalysis, which is mainly applied to block ciphers, analyzes the relation between differences in plaintexts and differences in ciphertexts [26]. Linear cryptanalysis approximates algorithms and their non-linear operations, respectively, with linear functions to reveal information about the secret key [114]. Related-key attacks study the influence of key-scheduling algorithms on the strength of block ciphers [25]. These attacks are independent of the number of rounds the block cipher undergoes. Even AES-192 and AES-256 can be weakened with related-key attacks [28].

Despite the existence of these attacks, our current knowledge of mathematics and cryptography allows us to construct secure schemes that can withstand such attacks. The mathematical principles of today's ciphers are strong enough to securely protect sensitive data, and practical applications of modern ciphers are not threatened by these attacks.

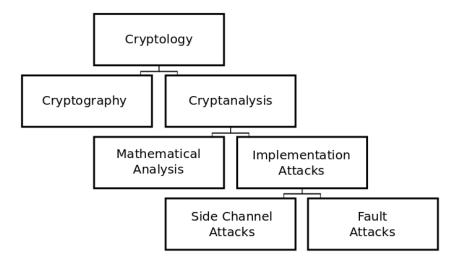

The mathematical strength of an algorithm, however, is only one aspect of the security of a cryptosystem. The resistance against physical attacks is also an important consideration. These do not target the underlying mathematical principles, but the implementation of the cipher. Consequently, they are also called implementation attacks [96]. In addition to the mathematical cryptanalyses, these implementation attacks nowadays also form part of cryptanalysis and can, in turn, be divided into two groups (see Figure 1.1, which is based on [131]). The first group measures physical characteristics of the device performing the attacked cryptographic operations, without modifying the computation. These attacks are called passive attacks or side channel attacks. The first published side channel attack analyzed timing variations of several cryptographic algorithms and was published in 1996 [102]. It was shown that a secret exponent from a modular exponentiation, as used in RSA, can be revealed by successively analyzing the timing variations emerging from the value of the exponent bits. For a standard square-and-multiply algorithm, a 1-bit needs

2/136 Chapter 1 Introduction

more processing steps and is therefore more time-consuming than a 0-bit. It was also presented how timing variations can reveal information about modular reduction, which in turn reveals information about the size of the processed values. Interestingly, the underlying principle of side channel attacks was known long before 1996, at least to secret services: in 1952, a covert listening device was found in the Moscow embassy of the United States. It was a replica of the Great Seal of the United States, presented from Soviet youths to the U.S. ambassador in Moscow already in 1946. This device is known as the Thing, or the Great Seal bug. A radio beam was driven at the antenna from a transmitter outside the embassy. The secret information, i.e, the conversations inside the room, was revealed by analyzing the modulation in the reflected signal emanating from the bug [182]. Thus, with the Great Seal bug, secret information was extracted from physical signals 50 years before Kocher's pioneering publication. The second group of implementation attacks actively modifies the computation and alters operations by, e.g., randomly changing values [119], changing the sign of a value [35], or skipping instructions [13]. These effects can be achieved by various mechanisms [17]. Such attacks are called invasive attacks, active attacks, or fault attacks<sup>1</sup>. In 1997, the first fault attack was published [37]. The attack targets the RSA signature scheme. It was shown that the RSA modulus can be factorized if an attacker induces a fault into the computation of one of the two parts of the signature generation when the RSA CRT version is used. With a single faulty signature and a correct signature, an attacker can reveal the secret key. The authors only presented the theory, but yet demonstrated the threat that hardware faults might pose to cryptography. Today, publications on both side channel and fault attacks include ideas and describe practical implementations.

Thus, even if the mathematical principles of a certain system are strong enough to protect the system against purely mathematical cryptanalysis, it still might be insecure due to strong implementation attacks. Even if there are no mathematical weaknesses, side channel attacks or fault attacks might break such a system. Consequently, not only does sensitive information have to be secured with mathematically secure algorithms, but the concrete implementations of these algorithms also have to withstand physical attacks.

#### 1.1 Thesis Statement

Today, it is generally agreed that side channel attacks and fault attacks pose a threat to cryptographic devices and to the secrets that they store. Accordingly, a great deal of research is conducted to find out which side channels can be used [77, 138] and how they can be optimally exploited [91]. Different algorithms are analyzed with respect to their susceptibility towards these attacks [33, 99, 141]. Findings about

<sup>&</sup>lt;sup>1</sup>Sometimes, the term side channel attack is also used as broader term, e.g., [33, 69, 132]. In that terminology, passive side channel attacks are what we understand as side channel attacks, and active side channel attacks are what we understand as fault attacks. In this work, however, we do not use this terminology.

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

1.1 Thesis Statement 3/136

Figure 1.1: The role of implementation attacks in the field of cryptology.

side channel attack vectors lead to adjustments of the implementations [53] and countermeasures to prevent fault attacks are explored [35, 143]. More sophisticated attacks aim at breaking the improved implementations [10, 69, 106]. The knowledge about side channel attacks has even resulted in a new field of research with the goal to design cryptographic protocols that remain secure even in the presence of leakage from broad classes of side channels [14].

#### 1.1.1 Problem Statement

Knowledge about side channel attacks and fault attacks influences the development of secure devices such as smartcards. Secure hardware vendors put a lot of effort into the development of devices secured against these kinds of attacks. Cryptographic algorithms are not implemented naively, but their implementations are meticulously designed around the knowledge gained from existing attacks.

Cryptographic devices and implementations should be secured against all realistically conceivable kinds of attacks - but it is difficult to determine which attacks are infeasible and which are not. Attacks which have already been conducted are taken into account, but there are many potential attack vectors which could be exploited and have not been used yet. In the past these attacks were often considered infeasible because they were believed to be hugely complex and expensive to perform. Thus, implementations lacked the necessary countermeasures to mitigate such attacks. Unfortunately, when the estimation of the real threat proved wrong afterwards, unprotected devices were in daily use for security applications. The development cycle of cryptographic devices and security applications is too long to react spontaneously to such developments. Vulnerable devices often remain in the field long after they are vulnerable to novel classes of analysis techniques.

Interestingly, in another field of cryptology, the research community does adapt

4/136 Chapter 1 Introduction

to future threats, although it is yet to be determined whether or not this threat will actually materialize. Quantum computers can invert certain one-way functions upon which the security of several modern cryptosystems relies [158]. They can solve both the integer factorization problem and the discrete logarithm problem, and thereby destroy the public-key scheme RSA, the Digital Signature Algorithm (DSA), and the Elliptic Curve Digital Signature Algorithm (ECDSA) [23]. Consequently, post-quantum cryptography is already a vibrant field of research, which aims at finding cryptographic schemes which will persist in the presence of quantum computers.

This thesis demonstrates that anticipation of future threats only affects the mathematical strength of cryptographic algorithms, but not their resistance to potential implementation attacks. Since the potential threat arising from quantum computers by far exceeds the one from yet another implementation attack, the comparison is not ideal. However, overestimating physical attack complexity is easy to mitigate by implementing more countermeasures against implementation attacks, have they already been realized or not.

#### 1.1.2 Thesis Contributions

We present a side channel attack and a fault attack, both of which were considered unrealistic due to their physical complexity prior to the results demonstrated in this work. These attacks target established and time-proven algorithms as well as novel cryptographic protocols.

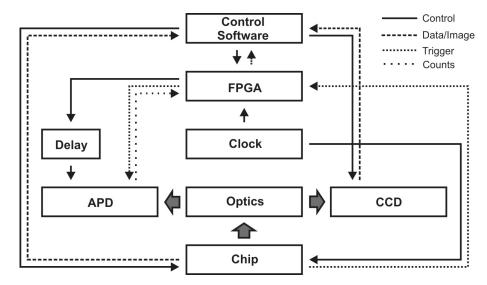

First, we present the photonic side channel. This side channel exploits highly spatially resolved photonic emission of the Device Under Attack (DUA) to reveal the secret key of a cryptographic algorithm. It was first presented in 2008, but was not considered a realistic threat due to the immense cost of more than 2,000,000 € for the measurement setup. When we presented a low-cost approach in 2012, we showed that the initial skepticism towards the applicability of this side channel was not justified. Based on this low-cost setup, we developed the theory of Simple Photonic Emission Analysis (SPEA) and Differential Photonic Emission Analysis (DPEA) and conducted practical attacks. Given the low-cost system and the methodology of SPEA and DPEA, the photonic side channel complements the cryptanalytic tools for attacking cryptography.

The second example is a higher-order fault attack against pairing computations. Pairings are the mathematical building blocks of Identity-Based Cryptography (IBC). Ever since they were suggested for this purpose, fault attacks against them were proposed. However, all of these attacks were only described theoretically until we published our results. Not only higher-order attacks, but even single-fault attacks against pairing computations were previously not practically realized. Second-order fault attacks were even considered to be an unrealistic attack scenario [180]. We conducted the first practical fault attack against a pairing computation, and even conducted it against a real-world pairing implementation. We successfully conducted a second-order fault attack against an implementation of the eta pairing from the RELIC toolkit [12], which was also used for the implementation of Pairing-Based

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

1.2 Structure of the Thesis 5/136

Cryptography (PBC) in Wireless Sensor Networks (WSNs) [127].

By presenting these two examples, we show that reliance upon physical attack complexity is not recommended when it comes to cryptography and the protection of sensitive information. In mathematics, proven results will always remain true. The human estimation of physical attack complexity, however, is error-prone. We have to face attackers who are better than we expect, and thus, cryptography needs also be secured against presumably physically infeasible attacks.

#### 1.2 Structure of the Thesis

In Chapter 2, we give necessary background information. We provide background on elliptic curves and bilinear pairings and explain the AES algorithm and Identity-Based Encryption (IBE). We present relevant information on side channel attacks and on fault attacks. Then, we present the photonic side channel in Chapters 3 and 4. These chapters are based on [104, 105, 149, 150]. We explain the physics of photonic emission and the setups that we used for our photonic side channel attacks in Chapter 3. In Chapter 4, we present these attacks: we start with the Simple Photonic Emission Analysis and explain its application on all variants of AES. We also sketch attacks for other algorithms and discuss countermeasures. The chapter continues with Differential Photonic Emission Analysis. We present our results on AES for different distinguishers and also discuss countermeasures. The second example of an implementation attack which was assumed to be unrealistic is the second-order fault attack on pairing-based cryptography. We present our results in Chapter 5. First, we describe the general attack setup that we developed. Then, we explain how we utilized this setup to conduct the attack against the eta pairing. We used the free software implementation of the eta pairing from the RELIC toolkit [12]. Finally, we present the cryptanalytic steps from the faulty results to the secret key. This chapter is based on [31]. Our ideas for future work for the photonic side channel and for fault attacks against PBC are presented in Chapter 6. In Chapter 7, we conclude this thesis.

# Chapter 2

# Mathematical and Cryptological Background

First, we provide the necessary mathematical background information on elliptic curves and bilinear pairings. We assume the reader is familiar with abstract algebra and basic probability theory. Next, we present the AES algorithm and introduce Identity-Based Encryption (IBE). The chapter continues with the explanation of side channel attacks and fault attacks. The necessary terminology is presented and related work is discussed.

# 2.1 Elliptic Curves and Bilinear Pairings

Some of the definitions in this section can also be given more general. However, we wrote this background as concrete as possible. Therefore, the definitions are often customized to our needs and not as universally valid as they are in most text books.

#### 2.1.1 Elliptic Curves

**Definition 2.1** (Elliptic Curve). An elliptic curve E over a field K is the set of all points  $P = (x_P, y_P)$  which satisfy the Weierstrass equation

$$E: y^2 + a_1 x \cdot y + a_3 y = x^3 + a_2 x^2 + a_4 x + a_6, \tag{2.1}$$

together with  $\mathcal{O}$ , the point at infinity. The coefficients  $a_1, a_2, a_3, a_4, a_6 \in K$  are chosen so that the curve is nonsingular, i.e., for all points  $P = (x_P, y_P)$  its partial derivatives do not vanish simultaneously.

An additive group structure can be defined on E. The group  $(E, \oplus)$ , which we refer to as only E, consists of all points satisfying the Weierstrass equation together with the point at infinity  $\mathcal{O}$ , which is the identity element in E. We denote the additive inverse of  $P \in E$  with -P.

For any extension field L of K, we define the set of L-rational points on E as

$$E(L) = \{(x, y) \in L \times L : y^2 + a_1 x \cdot y + a_3 y - x^3 - a_2 x^2 - a_4 x - a_6 = 0\} \cup \{\mathcal{O}\}.$$

(2.2)

We denote the group order with #E. The main result about the group order is Hasse's theorem.

**Theorem 2.1** (Hasse's theorem). Let E be an elliptic curve defined over a finite field  $\mathbb{F}_q$ . Then,  $\#E(\mathbb{F}_q)$  satisfies

$$|\#E(\mathbb{F}_q) - q - 1| \le 2\sqrt{q}.\tag{2.3}$$

Hasse's theorem only defines boundaries for the cardinality of E. The exact determination of  $\#E(\mathbb{F}_q)$ , which is also called point counting problem, is of critical importance for many cryptographic applications. Methods to solve this problem are discussed in [29].

The following explanation of addition and scalar multiplication in E is based on the chord and tangent law [71], since the pairing algorithms deployed in this work make use of this construction.

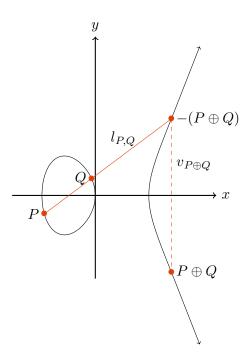

Figure 2.1 shows how the sum  $P \oplus Q$  of two distinct points  $P, Q \in E$  can be determined. For two points P and Q, the line through P and Q is denoted with  $l_{P,Q}$ . Since the Weierstrass equation is of degree 3 in x, there will always be a third intersection point of  $l_{P,Q}$  and the curve [159]. Assuming that  $l_{P,Q}$  is neither the tangent line at P or Q nor vertical, we denote the third point of intersection with  $-(P \oplus Q)$ . If we mirror this point at the x-axis, we obtain  $P \oplus Q$ , the sum of P and Q. We can identify this point by drawing the vertical line  $v_{-(P \oplus Q)}$  through  $-(P \oplus Q)$  and then take the intersection of this line with the curve, see Figure 2.1. This point is the result  $P \oplus Q$ , the sum of P and Q. Hence,  $v_{-(P \oplus Q)} = v_{P \oplus Q}$ . In the case that  $l_{P,Q}$  is the tangent of P or Q, the third point of intersection will be P or Q, respectively. In the case that  $l_{P,Q}$  is vertical, i.e., Q is the reflection of P at the horizontal axis, the third point of intersection is  $\mathcal{O}$ .

To define scalar multiplication, we start with the definition of point doubling. Point doubling is the addition of the point to itself and thus, the procedure is analogous to point addition for two distinct points. To double P and compute [2]P, we draw the tangent line  $g_P$  through P at E. Since this tangent line intersects E with multiplicity 2 at P, there is only one further intersection point of  $g_P$  at E. In the case that the tangent line is not vertical, we denote this third point with  $-(P \oplus P)$  and again reflect it at the x-axis to determine the point  $P \oplus P$ . The line connecting  $-(P \oplus P)$  and  $P \oplus P$  is again denoted with  $v_{P \oplus P} = v_{-(P \oplus P)}$ . In the case that the tangent line at P is vertical, the third point of intersection at E is  $\mathcal{O}$ , the point at infinity. Hence, we have  $[2]P = \mathcal{O}$  in this situation. For the curve which is shown in Figure 2.1, there are three points with a vertical tangent line. These are  $(0,0), (\sqrt{2},0)$ , and  $(-\sqrt{2},0)$ .

Scalar multiplication of elliptic curve points can now be calculated with successive point additions and point doublings. With [n]P, we denote scalar multiplication of P with  $n \in \mathbb{Z}$ . For  $P \in E$  and  $n \in \mathbb{N}$ , we have

$$[n]P = \overbrace{P \oplus P \dots \oplus P}^{n \text{ times}}. \tag{2.4}$$

Consequently, we have

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

**Figure 2.1:** Point addition of two distinct points on the elliptic curve  $y^2 = x^3 - 2x$ .

$$[-n]P = \overbrace{-P \oplus -P \dots \oplus -P}^{n \text{ times}}$$

$$(2.5)$$

and

$$[0]P = \mathcal{O}. \tag{2.6}$$

The point representation that is used in this work is referred to as affine coordinate system and affine coordinates. To speed up group operations and to mitigate side channel attacks, points on elliptic curves can also be represented in different coordinate systems such as projective coordinates [87] and Jacobian coordinates [120].

**Definition 2.2** (Torsion Point). Let E be an elliptic curve. For  $r \in \mathbb{Z}$  we define the set

$$E[r] = \{ P \in E : [r]P = \mathcal{O} \}.$$

(2.7)

These points of finite order are called torsion points and E[r] is the group of r-torsion points.

**Definition 2.3** (Supersingular Curve). Let E be an elliptic curve defined over a field with characteristic p. If  $E[p^n] = \{\mathcal{O}\}$  for all  $n \geq 1$ , E is called supersingular. Otherwise, E is called ordinary.

**Definition 2.4** (Distortion Map). Let E be a supersingular elliptic curve and  $r \in \mathbb{N}$  with  $r \geq 2$ . Let  $P \in E$  so that  $P \in E[r]$  and P is of exact order r. We call a homomorphism  $\psi : E \to E$  distortion map, if  $\{P, \psi(P)\}$  is a basis for E[r] and hence,  $\psi(P)$  is not in the cyclic subgroup generated by P.

Distortion maps were introduced in [177].

**Definition 2.5** (Twist). Let E and E' be elliptic curves over  $\mathbb{F}_q$ . If there is an isomorphism  $\phi_d: E' \to E$  defined over  $\mathbb{F}_{q^d}$  with minimal d, then E' is a degree-d twist of E.

We refer the reader to [29, 30, 52, 101, 159] for a thorough treatment of elliptic curves. Information about elliptic curve cryptography can be found in [29, 30, 52, 87].

#### Elliptic Curve Discrete Logarithm

The Discrete Logarithm Problem (DLP) is a well-known mathematical problem on which cryptographic algorithms such as ElGamal encryption, the ElGamal signature scheme, and the Diffie-Hellman key establishment are based [115]. The analog problem exists for elliptic curves. It is called Elliptic Curve Discrete Logarithm Problem (ECDLP).

**Definition 2.6** (Elliptic Curve Discrete Logarithm Problem). Let E be an elliptic curve over a finite field  $\mathbb{F}_q$  and  $P, Q \in E$  so that there is  $n \in \mathbb{Z}$  with Q = [n]P. The Elliptic Curve Discrete Logarithm Problem (ECDLP) is, given P and Q, to find n.

As it is the case for the DLP on natural numbers, there are simple instances of the ECDLP, while the problem is not efficiently solvable for other groups and points [29]. For details on elliptic curve discrete logarithms and their application, we refer the reader to [71].

#### 2.1.2 Bilinear Pairings

Bilinear pairings are bilinear maps defined over groups on elliptic curves. Originally, they have been used for cryptanalytic techniques [116]. In 2001, however, they gained the research community's attention when they were used to realize IBE [38], see Section 2.2.2. Today, a wide range of different pairings is used [11] and several cryptographic protocols such as attribute-based encryption [144], identity-based signatures [89], and key agreement protocols [94] are based on pairings. Moreover, pairings help to secure useful technologies such as WSNs [129]. Ever since pairings were proposed to be used for IBE, cryptanalysis of pairings and pairing-based schemes became an active field of research, e.g., [7, 72, 183].

For the definition of pairings, we first have to define the embedding degree.

**Definition 2.7** (Embedding Degree). Let E be an elliptic curve defined over the finite field  $\mathbb{F}_q$  and let r be an integer coprime to q with  $r \mid \#E(\mathbb{F}_q)$ . The embedding degree (with respect to r) is the smallest natural number k such that  $r \mid (q^k - 1)$ . It satisfies  $\mathbb{F}_{q^k} = \mathbb{F}_q(\mu_r)$ , where  $\mu_r$  denotes the group of rth roots of unity in  $\overline{\mathbb{F}}_q$ .

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

Thus, the embedding degree is the smallest natural number so that  $\mathbb{F}_{q^k}^*$  has a subgroup of order r, i.e.,  $r \mid (q^k - 1)$ . Since k is the order of q modulo r, i.e., k is the order of q in the unit group  $\mathbb{Z}_r^*$ , it follows that k divides Euler's totient function  $\phi(r)$ . Hence, if r is prime, then k divides (r-1).

**Definition 2.8** (Pairing). Let E be an elliptic curve defined over a finite field  $\mathbb{F}_q$ . We define three finite abelian groups  $\mathbb{G}_1$ ,  $\mathbb{G}_2$ , and  $\mathbb{G}_T$ . The groups  $\mathbb{G}_1$  and  $\mathbb{G}_2$  are subgroups of E, while  $\mathbb{G}_T$  is a subgroup of  $\mathbb{F}_{q^k}^*$ , with k the embedding degree. A pairing is an efficiently computable, non-degenerate bilinear map

$$e: \mathbb{G}_1 \times \mathbb{G}_2 \to \mathbb{G}_T.$$

(2.8)

We refer the reader to [52] for a thorough treatment of bilinear pairings and their application. For details on the selection of pairing-friendly curves we refer to [70].

Most pairings e(P,Q) on elliptic curves are computed by first computing the so-called Miller function  $f_{n,P}(Q)$  [121] followed by an exponentiation to the power  $z = (q^k - 1)/r$ . To understand this Miller function and to study pairings in more detail, we have to address divisors and some of their characteristics.

**Definition 2.9** (Divisor). For an elliptic curve E, a divisor D is a formal sum

$$D = \sum_{P \in E} n_P \cdot \langle P \rangle. \tag{2.9}$$

Only finitely many of the coefficients  $n_P \in \mathbb{Z}$  are nonzero. The divisor associated to the point  $P \in E$  is denoted with  $\langle P \rangle$ .

The divisors generated by the points of E form a free abelian group. We denote the set of all divisors generated by the points of E with Div(E).

We want to define the divisor associated to a rational function. For this definition, we first need to define the order of a rational function at a point of an elliptic curve [159].

**Definition 2.10** (Order of a function at a point). Let E be an elliptic curve defined over a finite field  $\mathbb{F}_q$ ,  $P \in E$ , and  $f \in \overline{\mathbb{F}_q}[E]_P$ . The order of f at P is

$$\operatorname{ord}_{P}(f) = \sup\{d \in \mathbb{Z} : f \in M_{P}^{d}\}, \tag{2.10}$$

where  $M_P$  denotes the maximal ideal of the local\_ring  $\overline{\mathbb{F}_q}[E]_P$ .

For a nonzero rational function  $f = g/h \in \overline{\mathbb{F}_q}(E)$  with  $g, h \in \overline{\mathbb{F}_q}[E]_P$ , we define

$$\operatorname{ord}_{P}(f) = \operatorname{ord}_{P}(g) - \operatorname{ord}_{P}(h). \tag{2.11}$$

If  $\operatorname{ord}_P(f) > 0$ , we say that f has a zero at P while we say that f has a pole at P if  $\operatorname{ord}_P(f) < 0$ . If  $\operatorname{ord}_P(f) \ge 0$ , then f is defined at P and f(P) can be evaluated. Otherwise f has a pole at P and we write  $f(P) = \infty$ .

**Definition 2.11** (Divisor associated to a function). Let E be an elliptic curve defined over a finite field  $\mathbb{F}_q$ , and  $f \in \overline{\mathbb{F}_q}(E)$  a nonzero rational function. The divisor associated to f is

$$\operatorname{div}(f) = \sum_{P \in E} \operatorname{ord}_{P}(f) \cdot \langle P \rangle. \tag{2.12}$$

A divisor is called principal if it is equal to a divisor that is associated to a function. Thus,  $D \in \text{Div}(E)$  is principal if D = div(f) for some nonzero rational function  $f \in \overline{\mathbb{F}_q}(E)$ . We say that two divisors  $D_1, D_2 \in \text{Div}(E)$  are linearly equivalent if  $D_1 - D_2$  is principal. To denote that two divisors are linearly equivalent, we write  $D_1 \sim D_2$ .

**Definition 2.12** (Support of a Divisor). Let E be an elliptic curve and  $D \in \text{Div}(E)$  with  $D = \sum_{P \in E} n_P \cdot \langle P \rangle$ . The support of D is the set of all points  $P \in E$  with  $n_P \neq 0$ . Two divisors are coprime when their supports are disjoint.

For a divisor  $D \in \text{Div}(E)$  and a principal divisor div(f) for some nonzero rational function  $f \in \overline{\mathbb{F}_q}(E)$ , we can define the evaluation of f at D if D and div(f) are coprime. Then, we define  $f(D) = \prod_{P \in E} f(P)^{n_P}$ .

With the help of divisors, we can now define the Miller function, which is the heart of most pairings.

**Definition 2.13** (Miller function). Let E be an elliptic curve defined over a finite field  $\mathbb{F}_q$ . A rational function  $f_{n,P} \in \mathbb{F}_q(E)$ , with  $P \in E$  and  $n \in \mathbb{N}$ , is a Miller function if its divisor satisfies

$$\operatorname{div}(f_{n,P}) = n \cdot \langle P \rangle - \langle [n]P \rangle - (n-1) \langle \mathcal{O} \rangle. \tag{2.13}$$

The Miller function can also be defined recursively as follows [34, 121]:

$$f_{n+1,P} := \begin{cases} 1 & \text{if } n = 0 \\ f_{n,P} \cdot l_{P,[n]P} / v_{[n+1]P} & \text{else.} \end{cases}$$

As stated above, most pairings on elliptic curves are computed by first evaluating the Miller function, followed by an exponentiation. The evaluation of the Miller function can be efficiently computed with the Miller Algorithm, see Algorithm 2.1.

The Miller Algorithm successively computes the required function in  $\lfloor \log_2(n) \rfloor$  iterations. Since this algorithm utilizes a for loop, see Lines 2 to 9, this evaluation is called Miller loop [44]. The value n, which determines the number of loop iterations, is often called Miller bound. The variable f, which is updated during the computation of the for loop until it stores the value of the evaluation of the Miller function, is called Miller variable.

Independent of the concrete design of a pairing, there are three different types of pairings. Following [73], we distinguish between pairings of Type 1, Type 2, and Type 3. These three basic types differ in the similarity of their domains  $\mathbb{G}_1$  and  $\mathbb{G}_2$ .

• In a Type 1 pairing, both groups are equal, i.e.,  $\mathbb{G}_1 = \mathbb{G}_2$ .

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

#### **Algorithm 2.1** Miller Algorithm and final exponentiation.

```

Require: P, Q \in E, n = \sum_{j=0}^{t-1} n_j 2^j with n_j \in \{0, 1\} and n_{t-1} = 1

Ensure: f_{n,P}(Q)^z

1: T \leftarrow P, f \leftarrow 1

2: for j = t - 2 \dots 0 do

f \leftarrow f^2 \cdot g_T(Q) / v_{[2]T}(Q)

T \leftarrow [2]T

4:

if n_i = 1 then

5:

f \leftarrow f \cdot l_{T,P}(Q)/v_{T \oplus P}(Q)

6:

T \leftarrow T \oplus P

7:

end if

8:

9: end for

10: f \leftarrow f^z

▶ final exponentiation

11: return f

```

- In a Type 2 pairing, the groups are different, i.e.,  $\mathbb{G}_1 \neq \mathbb{G}_2$ , but it exists an efficiently computable homomorphism  $\phi : \mathbb{G}_2 \to \mathbb{G}_1$ .

- In a Type 3 pairing, the groups are different, i.e.,  $\mathbb{G}_1 \neq \mathbb{G}_2$ , and there are no efficiently computable homomorphisms between  $\mathbb{G}_1$  and  $\mathbb{G}_2$ .

Type 1 pairings are also called symmetric pairings, while Type 2 and Type 3 pairings are called asymmetric pairings. The choice of the type of the pairing is related to the elliptic curve that is used, e.g., Type 1 pairings are generally implemented using supersingular curves over  $\mathbb{F}_p$ ,  $\mathbb{F}_{2^m}$ , and  $\mathbb{F}_{3^m}$  [153].

Those pairings which are used in cryptography require that their inversion is not efficiently computable. There are four mathematical problems connected to pairing inversion.

**Definition 2.14** (FAPI-1). Given a point  $P \in \mathbb{G}_1$  and a value  $\alpha \in \mathbb{G}_T$ , both chosen at random, the fixed argument pairing inversion problem (FAPI-1) is to find  $Q \in \mathbb{G}_2$  such that  $e(P,Q) = \alpha$  [72].

The problem can also be defined with P unknown and  $Q \in \mathbb{G}_2$  chosen at random. The problem is then called FAPI-2.

Both FAPI-1 and FAPI-2 treat the pairing as a black box and only consider the inputs and the output. However, analogous to the two steps of the pairing calculation, i.e., Miller Algorithm and final exponentiation, the pairing inversion can also be treated as a two-step process [97]. Hence, FAPI-1 is usually split into two parts in the literature: the exponentiation inversion [44] and the Miller inversion [72].

**Definition 2.15** (Exponentiation Inversion). Given the output of the pairing as well as  $P \in \mathbb{G}_1$  and the final exponent z, the exponentiation inversion problem is to find the correct preimage of the final exponentiation, i.e., the field element  $f_{n,P}(Q)$ .

**Definition 2.16** (Miller Inversion). The Miller inversion problem is, given  $n, P \in \mathbb{G}_1$ , and a field element  $f_{n,P}(Q)$ , to find the correct input  $Q \in \mathbb{G}_2$ .

Recently, a novel theoretic idea for pairing inversion was presented [97]. Kanayama and Okamoto show that the Miller inversion does not have to be solved in several cases provided that a generic algorithm for solving the exponentiation inversion exists. Thus, given such an algorithm, pairing inversion can be reduced to exponentiation inversion for a special family of pairings, the  $Ate_i$  pairings. This work was later revised and extended [44].

Related to the inversion of pairings, especially when it comes to fault attacks, is the Hidden Root Problem (HRP), which was introduced only in 2008 [175]. We define the HRP exactly as it was defined in the original publication.

**Definition 2.17** (Hidden Root Problem). Let  $\mathbb{F}_q$  be a finite field with  $q=p^n$  elements, where p is prime and let e be a positive integer with  $e\mid (q-1)$ . Let  $f_x(\cdot):\mathcal{D}(\mathbb{F}_q)\to\mathbb{F}_q$  be a specified map, i.e., the precise description of which is given, depending on x from a domain  $\mathcal{D}$  to  $\mathbb{F}_q$ . Let  $\mathcal{O}_x(\cdot)$  denote an oracle that on input  $\alpha\in\mathcal{D}$  returns

$$\xi_{\alpha} = f_x(\alpha)^e \tag{2.14}$$

for a fixed secret  $x \in \mathbb{F}_q$ . The Hidden Root Problem is to recover x in expected polynomial time in  $\log q$  by querying the oracle repeatedly for chosen  $\alpha_i \in \mathcal{D}(\mathbb{F}_q)$ .

#### The Tate Pairing

We describe the Tate pairing and its reduced variant following [176].

**Definition 2.18** (Tate Pairing). Let E be an elliptic curve defined over  $\mathbb{F}_q$ . Let  $r \mid \#E(\mathbb{F}_q)$  so that r and q are coprime. Let k be the embedding degree. The Tate pairing  $\hat{t}$  is defined as

$$\hat{t}: E\left(\mathbb{F}_{q^k}\right)[r] \times E\left(\mathbb{F}_{q^k}\right) / rE\left(\mathbb{F}_{q^k}\right) \to \mathbb{F}_{q^k}^* / \left(\mathbb{F}_{q^k}^*\right)^r$$

$$(P, Q) \mapsto \hat{t}(P, Q) = f_{r,P}(D_Q).$$

$$(2.15)$$

Here,  $\operatorname{div}(f_{r,P}) = r \cdot \langle P \rangle - r \cdot \langle \mathcal{O} \rangle$  and  $D_Q \sim \langle Q \rangle - \langle \mathcal{O} \rangle$  is coprime to  $\operatorname{div}(f_{r,P})$ .

To yield a unique result instead of a representative of an equivalence class, we define the reduced Tate pairing t.

**Definition 2.19** (Reduced Tate Pairing). Let E be an elliptic curve defined over  $\mathbb{F}_q$ . Let  $r \mid \#E(\mathbb{F}_q)$  so that r and q are coprime. Let k be the embedding degree. The reduced Tate pairing t is defined as

$$t: E\left(\mathbb{F}_{q^k}\right)[r] \times E\left(\mathbb{F}_{q^k}\right) / rE\left(\mathbb{F}_{q^k}\right) \to \mu_r \subset \mathbb{F}_{q^k}^*$$

$$(P, Q) \mapsto t(P, Q) = \hat{t}(P, Q)^{(q^k - 1)/r}.$$

$$(2.16)$$

Thus, the reduced Tate pairing consists of two stages: first the Miller function that is parameterized by P is evaluated at  $D_Q$ , then a final exponentiation follows to ensure that the algorithm outputs a unique value.

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

#### The eta Pairing

The eta pairing can be regarded as an optimized version of the reduced Tate pairing [19, 176]. The optimization consists in a shortened Miller loop. To define the eta pairing, we first need to introduce the Frobenius endomorphism.

**Definition 2.20** (Frobenius Endomorphism). Let E be an elliptic curve defined over a finite field  $\mathbb{F}_q$ . The endomorphism

$$\phi_q: E \to E,

(x,y) \mapsto (x^q, y^q)$$

(2.17)

is called Frobenius endomorphism. The group  $E(\mathbb{F}_q)$  of  $\mathbb{F}_q$ -rational points on E is fixed by  $\phi_q$  since the qth power is the identity on  $\mathbb{F}_q$ .

**Definition 2.21** (eta Pairing). Let E be a supersingular elliptic curve defined over  $\mathbb{F}_q$ . Let  $r \mid \#E(\mathbb{F}_q)$  so that r and q are coprime and let k be the embedding degree. Let n be any integer with  $n = q \mod r$  so that  $(n^k - 1)/r$  and r are coprime. Let  $\mathbb{G}_1, \mathbb{G}_2 \subseteq E$  be restricted to the Eigenspaces of Frobenius with  $\mathbb{G}_1 = E[r] \cap \ker(\phi_q - [1])$  and  $\mathbb{G}_2 = E[r] \cap \ker(\phi_q - [q])$ . The eta pairing  $\eta_n$  is defined as

$$\eta_n : \mathbb{G}_1 \times \mathbb{G}_2 \to \mu_r \subset \mathbb{F}_{q^k}^*$$

$$(P, Q) \mapsto \eta_n(P, Q) = f_{n,P}(Q)^{(q^k - 1)/r}.$$

(2.18)

# 2.2 Cryptographic Algorithms and Protocols

This section first presents the AES algorithm, which is the target of the photonic side channel attacks from Chapter 4. Then, background information on IBC is given.

#### 2.2.1 The Advanced Encryption Standard

The analyses in Chapter 4 focus on the Advanced Encryption Standard (AES). AES is a symmetric encryption algorithm based on the Rijndael cipher [58]. It is ratified as a standard by the National Institute of Standards and Technology of the USA. AES has a fixed block size of 128 input bits and operates on a  $4 \times 4$  matrix of bytes, named the state. Depending on the length of the key, which is 128, 192, or 256 bits, the cipher is termed AES-128, AES-192, or AES-256. The algorithm is specified as a number of rounds that transform the input plaintext into the ciphertext. AES consists of 10, 12, and 14 rounds for 128-, 192-, and 256-bit keys, respectively. Each round consists of four operations SubBytes, ShiftRows, MixColumns, AddRoundKey, except for the final round, which skips the MixColumns operation. Additionally, there is an initial AddRoundKey operation before the first round. Algorithm 2.2 shows the sequence of the rounds for AES-128.

Regarding AES-128, the initial AddRoundKey operation uses the complete secret 128-bit key. Then, each 128-bit round key  $k_i$  is derived deterministically from

#### **Algorithm 2.2** AES-128 Algorithm.

```

Require: plaintext m \in \{0, 1\}^{128}, key k \in \{0, 1\}^{128}

Ensure: ciphertext c \in \{0,1\}^{128}

1: state s \leftarrow m

2: s \leftarrow AddRoundKey(s, k)

3: for i = 1 \dots 9 do

s \leftarrow \text{SubBytes}(s)

s \leftarrow \text{ShiftRows}(s)

5:

s \leftarrow \text{MixColumns}(s)

6:

s \leftarrow AddRoundKey(s, k_i)

7:

8: end for

9: s \leftarrow \text{SubBytes}(s)

10: s \leftarrow \text{ShiftRows}(s)

11: s \leftarrow AddRoundKey(s, k_{10})

12: c \leftarrow s

13: return c

```

this original secret key with Rijndael's key schedule [58]. During each round of AES-192 and AES-256, also a 128-bit round key is used. The key for the initial AddRoundKey operation consists of the first 128 bits of the secret 192- and 256-bit secret key, respectively. The round key of the first round consists of the remaining bits of the secret key. Regarding AES-192, the second half of this round key is derived with the key schedule, while for AES-256, the key schedule is used only from the second round.

In the AddRoundKey step, each byte of the state is combined with a byte of the round key using the exclusive or operation ( $\oplus$ ). In the SubBytes step, each byte of the state is substituted by an affine transformation of its multiplicative inverse over the Galois field  $\mathbb{F}_{2^8}$ . This is the only operation that provides non-linearity in the algorithm. Since this deterministic operation is very costly, a precomputed 8-bit lookup table is often used. This so-called S-Box is shown in Table 2.1. The substitution value of a byte  $b = b_7|b_6|b_5|b_4|b_3|b_2|b_1|b_0$  with  $b_i \in \{0,1\}$  for all  $i \in \{0,\ldots,7\}$  is calculated by deriving the row and column numbers from the byte value. The row number consists of the value of the four Most Significant Bits (msb), i.e.,  $b_7$  to  $b_4$ , and the column number consists of the value of the four Least Significant Bits (lsb), i.e.,  $b_3$  to  $b_0$ . In the ShiftRows step, each row of the state matrix is shifted to the left by 0, 1, 2 or 3 bytes. In the MixColumns step, the four bytes of each column of the state matrix are combined using an invertible linear transformation, resulting in another four bytes.

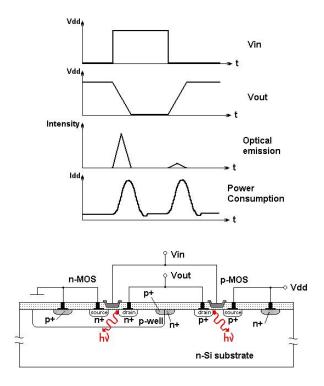

The memory access patterns of AES are particularly susceptible to cryptanalysis [22, 83, 130]. Optical emissions related to AES S-Box accesses are also exploited in the photonic side channel attacks in Chapter 4. The algorithm running on our Device Under Attack (DUA) consists of a software AES implementation. To increase

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

|   | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7          | 8  | 9          | a  | b  | С  | d  | е  | f  |

|---|----|----|----|----|----|----|----|------------|----|------------|----|----|----|----|----|----|

| 0 | 63 | 7c | 77 | 7b | f2 | 6b | 6f | с5         | 30 | 01         | 67 | 2b | fe | d7 | ab | 76 |

| 1 | ca | 82 | с9 | 7d | fa | 59 | 47 | f0         | ad | d4         | a2 | af | 9с | a4 | 72 | c0 |

| 2 | b7 | fd | 93 | 26 | 36 | 3f | f7 | СС         | 34 | <b>a</b> 5 | e5 | f1 | 71 | d8 | 31 | 15 |

| 3 | 04 | с7 | 23 | сЗ | 18 | 96 | 05 | 9a         | 07 | 12         | 80 | e2 | eb | 27 | b2 | 75 |

| 4 | 09 | 83 | 2c | 1a | 1b | 6e | 5a | <b>a</b> 0 | 52 | 3b         | d6 | b3 | 29 | e3 | 2f | 84 |

| 5 | 53 | d1 | 00 | ed | 20 | fc | b1 | 5b         | 6a | cb         | be | 39 | 4a | 4c | 58 | cf |

| 6 | d0 | ef | aa | fb | 43 | 4d | 33 | 85         | 45 | f9         | 02 | 7f | 50 | 3с | 9f | a8 |

| 7 | 51 | a3 | 40 | 8f | 92 | 9d | 38 | f5         | bc | b6         | da | 21 | 10 | ff | f3 | d2 |

| 8 | cd | 0c | 13 | ec | 5f | 97 | 44 | 17         | c4 | a7         | 7e | 3d | 64 | 5d | 19 | 73 |

| 9 | 60 | 81 | 4f | dc | 22 | 2a | 90 | 88         | 46 | ee         | b8 | 14 | de | 5e | 0b | db |

| a | e0 | 32 | 3a | 0a | 49 | 06 | 24 | 5c         | c2 | d3         | ac | 62 | 91 | 95 | e4 | 79 |

| b | e7 | с8 | 37 | 6d | 8d | d5 | 4e | <b>a</b> 9 | 6c | 56         | f4 | ea | 65 | 7a | ae | 80 |

| С | ba | 78 | 25 | 2e | 1c | a6 | b4 | с6         | e8 | dd         | 74 | 1f | 4b | bd | 8b | 8a |

| d | 70 | Зе | b5 | 66 | 48 | 03 | f6 | 0e         | 61 | 35         | 57 | b9 | 86 | c1 | 1d | 9e |

| е | e1 | f8 | 98 | 11 | 69 | d9 | 8e | 94         | 9b | 1e         | 87 | е9 | се | 55 | 28 | df |

| f | 8c | a1 | 89 | 0d | bf | e6 | 42 | 68         | 41 | 99         | 2d | Of | b0 | 54 | bb | 16 |

**Table 2.1:** The AES S-Box, used during the SubBytes operation, in hexadecimal representation. The 4 msb of the input byte determine the row and the 4 lsb determine the column. The element accessed by the input is the substitution value and hence, the next state value.

the frequency of the execution, only the first AddRoundKey and SubBytes operations were computed on the chip after which the input was reset and the measurement restarted. Table 4.8 shows the assembly code of our SubBytes implementation.

#### 2.2.2 Identity-Based Cryptography from Pairings

IBC was invented by Shamir, who presented the idea of this public-key system in 1984 [157]. However, he could not explain back then how to realize such encryption schemes mathematically. Nearly two decades later, in 2001, Boneh and Franklin showed that elliptic curves and pairings can be used to realize IBE [38].

IBE is a form of asymmetric cryptography where the identity of a user is at once his public key. In any form of communication and cryptography, the sender of a message has to know an information about the receiver which is uniquely assigned to him, such as his email address. The idea of IBE is that this information is sufficient to use cryptography and that no further information such as a dedicated public key is necessary. Therefore, IBE facilitates especially those systems which have to manage large numbers of key material.

A system which implements IBE needs a trusted third party or trusted authority, the so-called Private Key Generator (PKG). Following Boneh and Franklin's initial scheme, four probabilistic polynomial time algorithms are used:

- Setup: This algorithm generates all system parameters and the secret master key. Only the PKG knows this master key. The public system parameters include descriptions of the plaintext space  $\mathcal{P}$  and the ciphertext space  $\mathcal{C}$  and of the set of possible identities.

- Extract: The private key of a user is extracted from the secret master key and his identity, i.e., his public key.

- Encrypt: The randomized encryption of a message  $m \in \mathcal{P}$  is computed based on the public system parameters and the identity of the receiver, i.e., his public key.

- Decrypt: The deterministic decryption function outputs a plaintext for given ciphertext  $c \in \mathcal{C}$  and the receiver's private key.

In the FullIdent scheme proposed by Boneh and Franklin, both in the Encrypt and Decrypt step a bilinear pairing is computed [38]. During the Decrypt step, the input to the pairing consists of a part of the ciphertext and the secret key of the receiver of that ciphertext. Hence, it has to be ensured that an attacker cannot gain any information about the secret input to a pairing. Attacks on pairings have therefore become a prominent strand within the research on pairings.

An advantage of IBE is the facilitated key management. Certificates are no longer necessary. Furthermore, the sender can send an encrypted message to the receiver even if the receiver does not know his private key yet. It is likewise possible to provide public keys with a validity period which results in a simple method for key revocation. On the other hand, key escrow is immanent in IBE systems since each private key can be derived from the master key at any time. This is an advantage in the case that each user really trusts the PKG. Otherwise, it is a drawback of such systems. In the case of identity-based signatures, the nonexisting non-repudiation is another disadvantage for the same reason.

Identity-Based Cryptography for Wireless Sensor Networks IBE is especially well suited for those devices with a constrained power supply, such as smartcards and WSNs. On the one hand, WSNs benefit from the non-necessary costly verification of certificates. On the other hand, it is easy to add an additional node since there are no certificates of that node to be verified [48]. Hence, IBE can be used to solve the key distribution problem in WSNs [127]. Another decided advantage is that the existence of a PKG is immanent to WSNs by means of the base station which connects the WSN to other networks. In addition to these advantages, the computation of pairings necessary for IBE is for a given security level more efficient than classical public key cryptography [129]. However, since the PKG can derive all private keys from the master key, in general it is considered a caveat that all users of an IBE system have to trust the PKG.

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

2.3 Side Channel Attacks 19/136

## 2.3 Side Channel Attacks

In a cryptographic side channel attack, the attacker captures physical characteristics of the DUA while it performs computations with secret data. She analyzes these characteristics to reveal secret information, such as the secret key of an encryption algorithm. Side channel attacks have been a significant research area since the seminal papers of Kocher in 1996 and 1999, which introduced the timing [102] and the power side channel [103]. Since then, a plethora of other side channels, applications, and analysis methods have been presented. In this section, we provide the necessary background information about side channel attacks and present a selection of relevant work. Side channel attacks are also called passive or non-invasive attacks [33].

The attacker collects a number of so-called traces to reveal the secret information. In the case of power consumption, "a trace refers to a set of power consumption measurements taken across a cryptographic operation" [103]. Thus, each trace consists of a set of side channel leakage values, each related to a distinct point in time. Side channel attacks are divided into univariate and multivariate attacks. Univariate attacks exploit the leakage of only a single point in time [60], while multivariate attacks exploit multiple aspects of the measurements jointly. Side channel attacks combining multiple points of leakage are also called higher-order attacks [56, 103]. Since protected implementations can generally not be successfully attacked with a univariate attack, higher-order attacks are also a means to break countermeasures [95, 111].

Since in real-world applications access to the DUA is often restricted, an attacker cannot get an unlimited number of traces. Template attacks compensate for a smaller number of traces during the attack by adding an additional attack phase in which the attacker has unlimited access to an identical experimental device [45]. During this phase, she can execute arbitrary code on this device and thereby derive templates which model both the signal and the noise. These templates improve the efficiency of the attack in terms of the required number of traces and let the attacker fully utilize the leakage information from each trace.

For the analysis of side channel information, many different distinguishers exist [60, 90]. Distinguishers are the statistical methods which are applied to side channel measurements. However, often the choice of the distinguisher is of minor importance [113].

If a secret key is the target of a side channel attack, it is often not revealed as a whole, but in separate chunks. These separate chunks are called subkeys. If the AES algorithm is the target of the attack, for instance, each key byte is generally revealed independently.

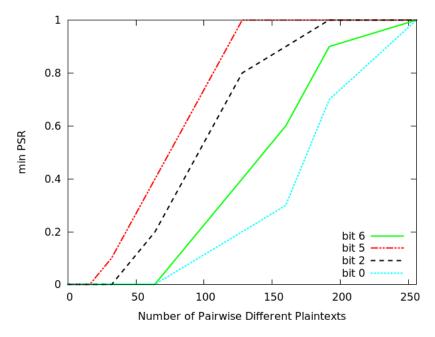

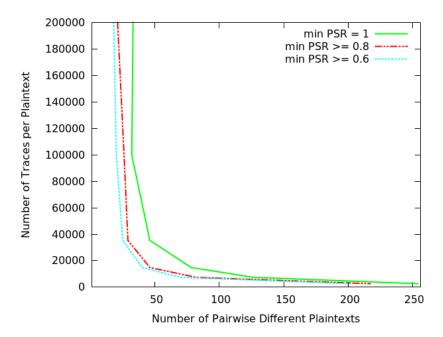

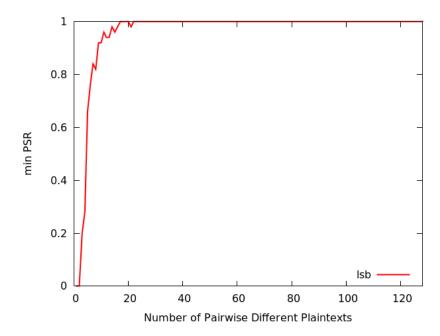

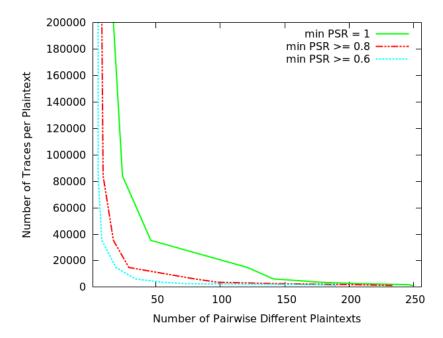

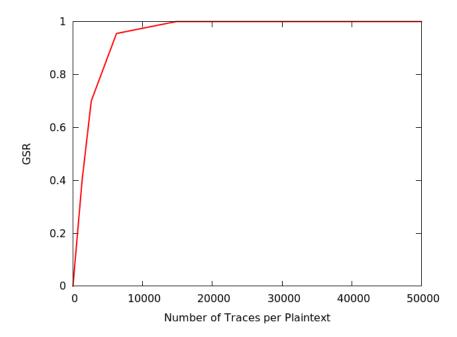

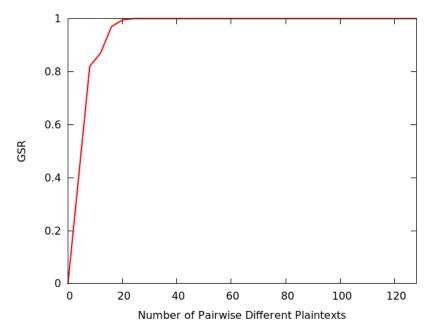

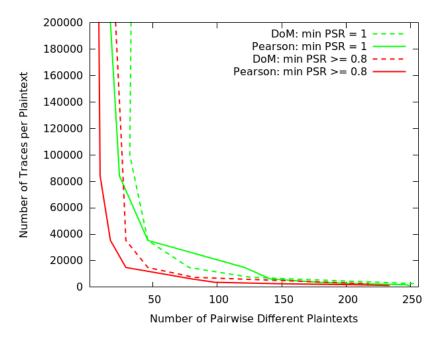

The success rate of an attack can be measured based on its Global Success Rate (GSR) and its Partial Success Rate (PSR). The Global Success Rate is defined as the probability that the complete key is ranked first, i.e., it is the probability of getting the correct value for all key bytes simultaneously [85]. The Partial Success Rate is defined as the probability that the correct subkey is ranked first among all

possible subkeys, i.e., the Partial Success Rate (PSR) is the probability of obtaining the correct value, computed independently for each key byte [90]. Since each key byte has its own PSR, often the minimal PSR (min PSR) is used to describe the attack efficiency [165].

**Example 2.1.** Assume that we have a set of traces and want to attack a 16-byte key. We randomly choose ten subsets of the traces and try to reveal the secret key for each of these subsets. In five cases, we reveal the secret key completely, while in the remaining 5 cases, we do not correctly identify the Least Significant Byte (LSB). Then, the Global Success Rate (GSR) is  $\frac{5}{10} = 0.5$ , while the PSR is 1 for the first 15 key bytes and 0.5 for the LSB. Thus, min PSR is 0.5. Assume now that we never reveal the secret key completely, but in experiment  $i, i \in \{1, ..., 10\}$ , all key bytes except for key byte i are revealed. Then, we have min PSR = 0.9, but GSR = 0.

#### 2.3.1 Timing Attacks

In 1996, a timing attack against several cryptographic algorithms was the first published side channel attack [102]. In a timing attack, the attacker analyzes the time required to perform operations which involve secret key material to extract information about that key material. Often, timing attacks target algorithms which employ an exponentiation with a secret exponent, since the timing strongly depends on the value of the processed exponent bits in unprotected implementations [146]. Timing attacks can also be conducted remotely, e.g., against network servers [42].

A variant of timing attacks, both local and remote, are cache attacks. In a cache attack, the timing information provides information about cache hits and misses and hence, about the cache entries. Therefore, cache attacks often target algorithms using table lookups such as AES. In 2004, Bernstein conducted a known-plaintext cache timing attack on the OpenSSL AES implementation that uses precomputed tables [22]. He extracted a complete 128-bit AES key. The mathematical analysis of our attack presented in Section 4.1 is similar to that analysis. In 2005, Percival revealed an OpenSSL 1024-bit RSA private key by exploiting simultaneous multithreading [135]. This OpenSSL implementation used RSA-CRT for private-key operations. During the attack, 310 out of 512 bits per exponent could be extracted, which is enough for factorizing the modulus.

#### 2.3.2 Power Analysis

The second side channel that was exploited is power analysis. In 1999, Kocher et al. presented Simple Power Analysis (SPA) and Differential Power Analysis (DPA). They define SPA as "a technique that involves directly interpreting power consumption measurements collected during cryptographic operations". In contrast, DPA does not interpret the traces directly, but uses "statistical functions tailored to the target algorithm" [103]. In this seminal work, the Data Encryption Standard (DES) was attacked. After the publication of these results, countermeasures against power analysis have been developed, e.g., masking and hiding [112]. Masking means to

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

2.3 Side Channel Attacks 21/136

make the processed value uncorrelated to the algorithmic value, while hiding means to make the power consumption uncorrelated to the processed value. However, the analysis methods also evolved, and higher-order attacks against DPA-resistant software and hardware have been published [51, 117]. A few years ago it was even shown that successful SPAs are still possible, despite several implemented countermeasures like message padding [55, 106].

Power analysis attacks also target novel algorithms like PBC. In 2006, both SPA and DPA on the eta pairing over binary fields were presented [100]. The authors suggest randomization and blinding as defense against such attacks, both of which are already used in other algorithms such as RSA. In 2009, a DPA against pairing computations was simulated [64]. It was shown how the secret input point to the Miller Algorithm can be revealed by analyzing a modular multiplication and an addition. In 2013, these results were improved and it was theoretically described how the secret input to the Miller Algorithm can be revealed only by a DPA of a modular multiplication [33].

#### 2.3.3 Electromagnetic Analysis

The analysis of electromagnetic radiation as a side channel was already mentioned in the seminal work on power analysis [103]. Electromagnetic emanation is a three-dimensional vector field which changes over time. Instead of observing the near-field emanation of the whole Integrated Circuit (IC), the observation can be restricted to a certain location such as a specific component of the IC. Such localized measurements allow for side channel attacks which exploit location-dependent information leakage, though to a lesser extent than is the case for Photonic Emission Analysis. The level of localization is related to the diameter of the magnetic coil usually used in electromagnetic side channel attacks to acquire the measurements. We refer to Heyszl's PhD thesis for more information on the strengths and limitations of high-resolution measurements for electromagnetic side channel attacks [92].

In 2001, two publications on the electromagnetic (EM) side channel appeared [75, 138]. Both publications stress the advantage that EM analysis has over power and timing analysis: exploitation of locally resolved data leakage. A technical description of EM attacks on smartcards is given in [138]. The authors explain the physics of EM radiation and describe how attacks can be practically realized. However, EM radiation is not analyzed for cryptanalytic purposes in this work. Gandolfi et al. showed by example of a Simple Electromagnetic Analysis (SEMA) against RSA and a Differential Electromagnetic Analysis (DEMA) against the DES how EM attacks can be practically conducted [75]. Both implementations were unprotected against side channel attacks. The authors state that in terms of their experiments, EM analysis outperforms power analysis. In 2002, Agrawal et al. presented a systematic investigation of the EM side channel for Complementary Metal-Oxide-Semiconductor (CMOS) devices [8]. They present concrete results for two different smartcards. They show that EM analysis can even be successful in the presence of power analysis countermeasures. An extended version of their work is also avail-

able [9]. In this work, especially higher order attacks and assessment methodologies for these are examined in more detail.

In 2012, location-dependent electromagnetic leakage was successfully exploited in an attack on an elliptic curve scalar multiplication implementation on a Field Programmable Gate Array (FPGA) using a near-field EM probe [93]. The authors scanned the die surface and collected EM traces at every point. They demonstrated that location-dependent leakage can be used in a template attack and countermeasures against system-wide leakage thus can be circumvented.

#### 2.3.4 Other Side Channels

In addition to these classical side channels, there are also other sources of side channel leakage which can be exploited.

In 2008, a cold boot attack was presented [86]. The authors show how disc encryption keys which are stored in Dynamic Random-Access Memory (DRAM) can be easily stolen if the attacker has physical access to the computer. Contrary to many other side channel attacks, this work assumes a very realistic attack scenario and this attack is a serious security vulnerability. The attack becomes possible since data stored in DRAM does not vanish instantaneously, but fades away gradually when the power is turned off. By cooling the memory, this process can even be slowed down. This attack is considered to be a side channel attack even though the attackers do not capture physical characteristics of the DUA while it performs computations with secret data. They do, however, exploit the physical implementation of a cryptosystem.

In 2013, the acoustic side channel was presented [77]. The authors show how a 4096-bit RSA key can be extracted by analyzing the acoustic frequency spectrum during decryption. The decryption was performed by GnuPG running on a laptop, while the acoustic emanation was captured only with a plain mobile phone. Thus, this attack was launched with low-cost equipment. Although the acoustic side channel has a very low bandwidth which makes such attacks more difficult to conduct, specially crafted chosen messages lead to more discernible leakage in the presented attack.

#### 2.4 Fault Attacks

The principle of fault attacks is to disturb the computation of cryptographic operations by induction of one or more faults. From the faulty result, the attacker learns information about the internal sensitive data such as the secret key. The first fault attack against a cryptographic algorithm was presented in 1997 [37]. Since then, fault attacks have been applied against various cryptographic algorithms [174] and became a standard tool to facilitate cryptanalysis. The attack assumptions can be described in detailed fault models, which include the location and the timing of the fault, and the number and kind of faults. Nowadays, many techniques exist to induce faults, e.g., clock glitching, power glitching, and laser beams [17]. To thwart

<sup>&</sup>quot;Why Cryptography Should Not Rely on Physical Attack Complexity"

2.4 Fault Attacks 23/136

countermeasures against fault attacks, even two faults within one computation have been performed [99, 170]. These attacks are often called second-order attacks [61]. More generally, we call a fault attack with more than one fault a higher-order attack.

#### 2.4.1 RSA

The first fault attack against a cryptographic algorithm, known as the Bellcore attack, was presented in 1997 by Boneh, DeMillo and Lipton against the RSA signature scheme [37]. They showed that the RSA modulus can be factorized if an attacker induces a fault into the computation of one of the two parts of the signature generation in case the RSA CRT version is used. With a single faulty signature and a correct signature under the same secret key, an attacker can reveal the secret key.

Since then, RSA has been a popular target for fault attacks. A hardware-based fault attack against the RSA verification process was presented in 2005 [155] and generalized one year later [122]. The attack consists of forcing the attacked cryptographic device to use a slightly modified modulus instead of the original one by inducing transient hardware faults. Since the factorization of the altered modulus is known, the attacker can calculate a new private key so that the device accepts the signature of any arbitrary message signed with this new key. A similar attack was presented against the signature process in 2006 [41]. The authors even show how the full RSA private key can be recovered by corrupting the modulus. Hence, it was concluded that "RSA public key elements also have to be protected against fault attacks". In the same year, it was even questioned if it is wise to publish public key elements [82]. The authors present an attack against the RSA verification process where they induce not transient, put permanent faults. This allows the forgery of any signature at any time.

Another work that targets the RSA modulus was published in 2012 [119]. The authors developed a purely software-based fault attack against the verification process. They showed that the modulus can be completely replaced when the structures which manage the public key material are attacked. The new modulus can be easily factorized with a high probability. The practicability was demonstrated on a widely deployed conditional access device.

## 2.4.2 Elliptic Curve Cryptography

Fault attacks have also been presented against Elliptic Curve Cryptography (ECC). In 2000, the first fault attack on elliptic curve cryptosystems was presented [24]. The authors present three ideas for faults attacks, all of which are based on the same idea: when the coordinates of a point are modified by a fault, the new point will not be on the original curve. The curve on which the modified point lies is potentially cryptographically less secure. Hence, the ECDLP might be easier to solve on that curve. The authors stress that this attack might even be possible without any fault induction: if the DUA does not explicitly check whether or not the input point is on the specified curve, a malicious user can just input a point with the desired

properties. Later, this work was refined to a more relaxed fault model [50]. Another idea for fault attacks against ECC are sign change attacks [35], in which the signs of intermediate points are changed to facilitate the computation of the secret scalar. It is more difficult to mitigate these attacks, since the modified points still lie on the original curve, so that integrity checks would not detect the fault after such attacks. Sign change fault attacks were also described against PBC [180]. In 2008, an attack tailored to the Montgomery ladder was presented [69]. The authors state that they can reveal the secret scalar with only one or two faults, even in the presence of countermeasures which aim at preventing fault attacks. The attacks also consist in performing operations with the modified point on another curve. In this scenario, the modified point lies on the twist of the original curve.

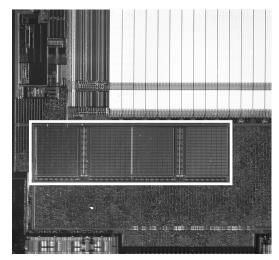

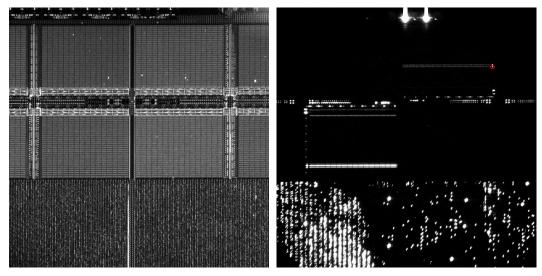

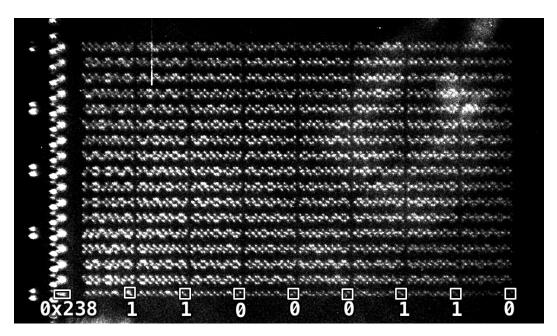

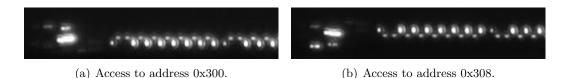

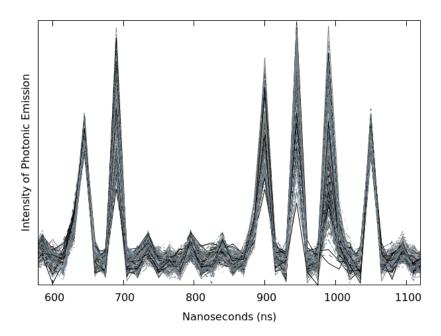

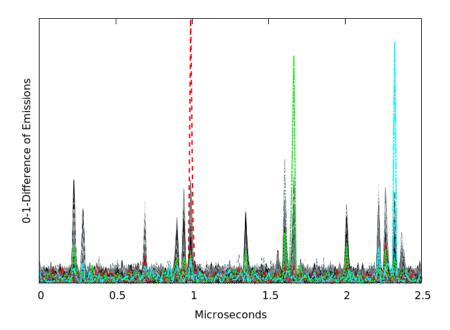

## 2.4.3 Symmetric Cryptography