## A 9-bit, 45mW, 0.05mm<sup>2</sup> Source-Series-Terminated DAC Driver with Echo Canceller in 22nm CMOS for In-Vehicle Communication

vorgelegt von M. Sc. Hossein Ghafarian Mabhout

an der Fakultät IV - Elektrotechnik und Informatik der Technischen Universität Berlin

zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften - Dr.-Ing. -

genehmigte Dissertation

Promotionsausschuss:

Vorsitzender:Prof. Dr. Thomas SikoraGutachter:Prof. Dr.-Ing. Friedel GerfersGutachter:Prof. Dr. Frank EllingerGutachter:Prof. Dr.-Ing. Roland Thewes

Tag der wissenschaftlichen Aussprache: 21. Oktober 2021 Berlin 2022

For my parents, maman and baba, who wanted their son to have a Dr. -Ing. title.

## Abstract

The increasing amount of data transferring within a vehicle is driven by the expanding applications implemented on it, initiated the use of Ethernet as a new standard within the automotive industry to not only increase the data rate but also take into account the strict constraints within the automotive environment such as robustness and electromagnetic interference, etc.

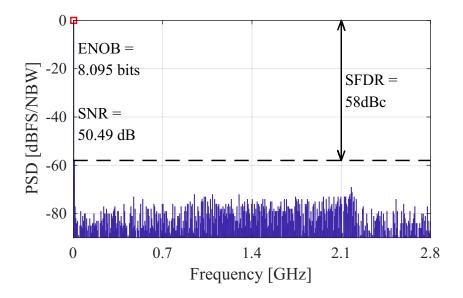

The introduction of Automotive Ethernet (AE) standards started with 100Base-T1 with a data rate of 100 Mb/s. Later, under the task force IEEE P802.3ch, standards up to the data rate of 10 Gb/s are established. The focus of this work is the study of the physical layer of the transceiver suitable for the AE standards from the data rate of 1 Gb/s to 10 Gb/s. This work presents an SST 9-bit TX-DAC driver, that is fully compliant to the new Automotive Ethernet (AE) Standard IEEE P802.3ch for the data rate up to 10 Gb/s. The TX driver design incorporates a highly-correlated timing-matched 9-bit echo DAC canceler (EC-DAC) to eliminate up-to 24.3dB of the transmit power from the RX path, due to the full-duplex transmission scheme. The TX-EC-DAC driver combination inherently provides  $100\Omega$  differential termination and possesses a PVT calibration scheme covering up to 3 sigma process variation with a resolution of  $1.5\Omega$ . Designed and fabricated in a 22nm FD-SOI technology, the TX-DAC enables a 1Vppd PAM4 signal swing with raw data rates up to 11.2Gb/s and Nyquist tone sine wave linearity SFDR of better than 50dBc. The driver pair is backward compatible with all relevant AE Standards 10/5/2.5/1GBase-T1 and occupies the smallest area of only  $0.05mm^2$ . The 9-bit TX-EC-DAC combination dissipates 3/42 mW from dual 0.8/1.2 V power supply with a power efficiency of 2 mW/Gb/s per DAC.

(Keywords: SST driver, TX-DAC, Echo canceling, Automotive Ethernet, NGAUTO, IEEE P802.3ch.)

# Abstrakt

Die Erhöhung der Datenmenge, die innerhalb eines Autos übertragen werden, wird durch zunehmend integrierte Anwendungen angetrieben. Dies hat, um nicht nur die Datenrate zu erhöhen, sondern auch die strikten Auflagen innerhalb des Automobils wie Robustheit, elektromagnetische Interferenz usw. zu berücksichtigen, die Verwendung von Ethernet als neuen Standard in der Automobilindustrie eingeleitet.

Die Einführung von Automotive Ethernet (AE) Standards begann mit 100Base-T1 mit einer Datenrate von 100 Mb/s. Anschließend wurden von der Task Force IEEE P802.3ch Standards für Datenraten von bis zu 10 Gb/s festgelegt. Der Schwerpunkt dieser Dissertation liegt auf der Eignungsanalyse der physikalischen Schicht des Transceivers für Datenraten von 1 Gb/s bis zu 10 Gb/s. In dieser Arbeit wird ein AE Standard IEEE P802.3ch kompatibler 9-Bit TX-DAC Treiber für Datenraten von bis zu 10 Gb/s vorgestellt. Das Design des TX Treibers beinhaltet einen hoch-korrelierten zeitlich-angepassten 9-Bit Echo-DAC-Unterdrücker (EU-DAC) der aufgrund des Vollduplexübertragungsschema bis zu 24.3dB von der Sendeleistung aus dem Empfangspfad eliminiert. Die TX-EU-DAC Treiberkombination hat eine  $100\Omega$  differenzielle Terminierung und beinhaltet ein Kalibrierungsschema das bis zu 3 Sigma Prozessvariationen mit einer Auflösung von  $1.5\Omega$ abdeckt. Entworfen und gefertigt wurde der TX-DAC in einer 22nm FD-SOI Technologie und ermöglicht einen 1Vppd PAM4 Signalpegel mit einer Rohdatenrate von bis zu 11.2Gb/s und einer Nyquist Sinuswellentonlinearität von besser als 50dBc. Das Treiberpaar ist abwärtskompatibel mit allen relevanten AE Standards 0/5/2.5/1GBase-T1 und benötigt eine Fläche von nur  $0.05mm^2$ . Die 9-bit TX-EC-DAC Kombination verbraucht 3/42mWvon einer doppelten 0.8/1.2V Spannungsquelle mit einer Energieeffizienz von 2mW/Gb/s pro DAC.

# List of Own Publications

- Hossein Ghafarian and Friedel Gerfers. A digital calibration technique canceling non-linear switch and package impedance effects of a 1.6 GS/s TX-DAC in 28 nm CMOS. In 2017 IEEE International Symposium on Circuits and Systems (ISCAS), pages 1–4. IEEE, 2017.

- [2] Hossein Ghafarian and Friedel Gerfers. Analysis and compensation technique canceling non-linear switch and package impedance effects of a 3.2 GS/s TX-DAC. In 2017 IEEE 60th International Midwest Symposium on Circuits and Systems (MWSCAS), pages 1172–1175. IEEE, 2017.

- [3] Helia Ordouei, Hossein Ghafarian, and Friedel Gerfers. Analysis of package impedance effects on the linearity of source series terminated DACs. In 2018 IEEE 61st International Midwest Symposium on Circuits and Systems (MWSCAS), pages 250-253. IEEE, 2018.

- [4] Hossein Ghafarian, Helia Ordouei, and Friedel Gerfers. Impedance calibration technique canceling process and temperature variation in source terminated DAC Drivers in 22nm FDSOI. In 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), pages 113–116. IEEE, 2019.

- [5] Friedel Gerfers, Nima Lotfi, Enne Wittenhagen, Hossein Ghafarian, Yuan Tian, and Marcel Runge. Body-Bias techniques in CMOS 22FDX® for mixed-signal circuits and systems. In 2019 26th IEEE International Conference on Electronics, Circuits and Systems (ICECS), pages 466–469. IEEE, 2019.

- [6] Enne Wittenhagen, Marcel Runge, Nima Lotfi, Hossein Ghafarian, Yuan Tian, and Friedel Gerfers. Advanced mixed signal concepts exploiting the strong body-bias rffect in CMOS 22FDX. *IEEE Transactions on Circuits and Systems I: Regular Papers*, 68(1), 2021.

- [7] Hossein Ghafarian, Suhas Shivaprakash, Sanaz Mortazavi, Philipp Scholz, Nima Lotfi, and Friedel Gerfers. A 9-bit, 45mW, 0.05mm2 source-series-terminated DAC driver with echo canceller in 22nm CMOS for in-vehicle communication. *IEEE Solid-State Circuits Letters*, 2021.

In reference to IEEE copyrighted material which is used with permission in this thesis, the IEEE does not endorse any of TU Berlin's products or services. Internal or personal use of this material is permitted. If interested in reprinting republishing IEEE copyrighted material for advertising or promotional purposes or for creating new collective works for resale or redistribution, please go to http://www.ieee.org/publications\_standards/publications/rights/rights\_link.html to learn how to obtain a License.

# Contents

| Lis | List of Own Publications |                     |                                                                    |               |  |  |  |  |

|-----|--------------------------|---------------------|--------------------------------------------------------------------|---------------|--|--|--|--|

| 1   | Intro                    | troduction          |                                                                    |               |  |  |  |  |

| 2   | Auto                     | Automotive Ethernet |                                                                    |               |  |  |  |  |

|     | 2.1                      |                     | History of In-car Networking Standards Within Automotive Industry. | <b>3</b><br>3 |  |  |  |  |

|     |                          | 2.1.1               | Controller Area Network (CAN)                                      | 3             |  |  |  |  |

|     |                          | 2.1.2               | Local Interconnect Network (LIN)                                   | 4             |  |  |  |  |

|     |                          | 2.1.3               | Media Oriented Systems Transport (MOST)                            | 4             |  |  |  |  |

|     |                          | 2.1.4               | FlexRay                                                            | 5             |  |  |  |  |

|     |                          | 2.1.5               | Automotive Ethernet                                                | 5             |  |  |  |  |

|     |                          | 2.1.6               | Comparison of In-car Standards and Outlook                         | 6             |  |  |  |  |

|     | 2.2                      | IEEE8               | 803.2 Ethernet Standard Family                                     | 7             |  |  |  |  |

|     |                          | 2.2.1               | 100Base-T1,1000Base-T1 and NGAUTO Standards                        | 8             |  |  |  |  |

|     | 2.3                      | Transo              | ceiver Architecture                                                | 8             |  |  |  |  |

|     |                          | 2.3.1               | РНҮ                                                                | 8             |  |  |  |  |

|     |                          | 2.3.2               | Cables                                                             | 10            |  |  |  |  |

|     |                          | 2.3.3               | Full Duplex Operation                                              | 11            |  |  |  |  |

|     |                          | 2.3.4               | Transmitter Requirements                                           | 11            |  |  |  |  |

|     |                          | 2.3.5               | EMC Requirements                                                   | 14            |  |  |  |  |

| 3   | High                     | 1 Speed             | d DACs                                                             | 17            |  |  |  |  |

|     | 3.1                      | -                   | Performance Parameters                                             | 17            |  |  |  |  |

|     |                          | 3.1.1               | Static Properties                                                  | 17            |  |  |  |  |

|     |                          | 3.1.2               | Dynamic Properties                                                 | 19            |  |  |  |  |

|     | 3.2                      | DAC 0               | Circuit Implementations                                            | 21            |  |  |  |  |

|     |                          | 3.2.1               | Current-Mode DAC                                                   | 21            |  |  |  |  |

|     |                          | 3.2.2               | Voltage-Mode DAC                                                   | 25            |  |  |  |  |

|     | 3.3                      | Comp                | arison of Voltage-Mode and Current-Mode DACs                       | 29            |  |  |  |  |

|     | 3.4                      | SST D               | DAC                                                                | 30            |  |  |  |  |

|     |                          | 3.4.1               | Architecture and Requirements                                      | 30            |  |  |  |  |

|     |                          | 3.4.2               | Performance, Linearity, Power and Area                             | 31            |  |  |  |  |

|     |                          | 3.4.3               | Linearity Limitations                                              | 32            |  |  |  |  |

|     |                          | 3.4.4               | PVT Problems and Solutions                                         | 45            |  |  |  |  |

|     |                          | 3.4.5               | Ground Scheme Problem                                              | 47            |  |  |  |  |

|     | 3.5                      | SST E               | Ccho cancellation                                                  | 48            |  |  |  |  |

|     |                          | 3.5.1               | Requirements                                                       | 48            |  |  |  |  |

|            | <ul> <li>3.5.2 Passive vs Active Hybrid</li></ul>                       |  |  |  |  |  |

|------------|-------------------------------------------------------------------------|--|--|--|--|--|

|            | Design and Implementation of a 9-bit 6GS/s Source Series Terminated DAC |  |  |  |  |  |

| 4.1        | DAC Architecture                                                        |  |  |  |  |  |

|            | 4.1.1 Power Supply Implementation Scheme                                |  |  |  |  |  |

| 4.2        | Unary and Binary Segmentation                                           |  |  |  |  |  |

| 4.3        | Active to Passive Ratio                                                 |  |  |  |  |  |

|            | 4.3.1 Crow-bar Current Reduction                                        |  |  |  |  |  |

| 4.4        | Termination Calibration                                                 |  |  |  |  |  |

| 4.5        | Echo Canceller Pair                                                     |  |  |  |  |  |

| 4.6        | SST DAC Cell Design Consideration                                       |  |  |  |  |  |

|            | 4.6.1 Unit Cell Layout and Design Consideration                         |  |  |  |  |  |

|            | 4.6.2 Simulating the Device Sizes                                       |  |  |  |  |  |

| 4.7        | Pre-driver                                                              |  |  |  |  |  |

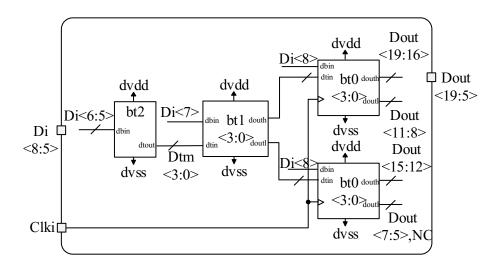

| 4.0        | 4.7.1 Time Synchronizing Blocks                                         |  |  |  |  |  |

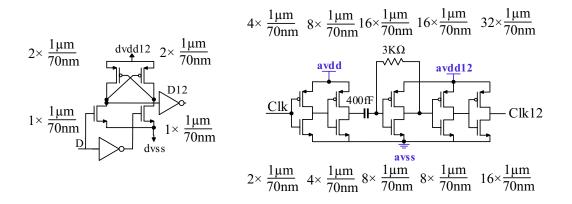

| 4.8        | Level Shifter                                                           |  |  |  |  |  |

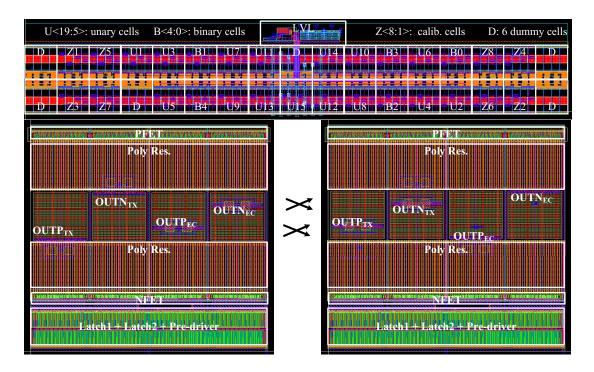

| 4.9        | SST DACs and LVL Layout Floor Plan                                      |  |  |  |  |  |

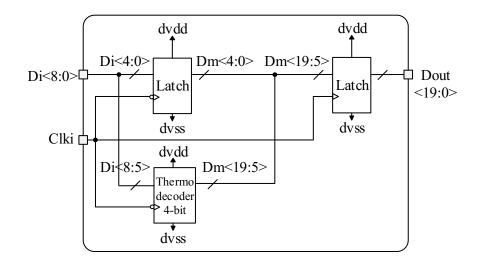

|            | Digital Decoder                                                         |  |  |  |  |  |

|            | DDS Interface                                                           |  |  |  |  |  |

| 4.12       | Simulation Results                                                      |  |  |  |  |  |

|            | 4.12.1 Echo Canceling Performance                                       |  |  |  |  |  |

|            | 4.12.2 Static Properties                                                |  |  |  |  |  |

|            | 4.12.3 Dynamic Properties                                               |  |  |  |  |  |

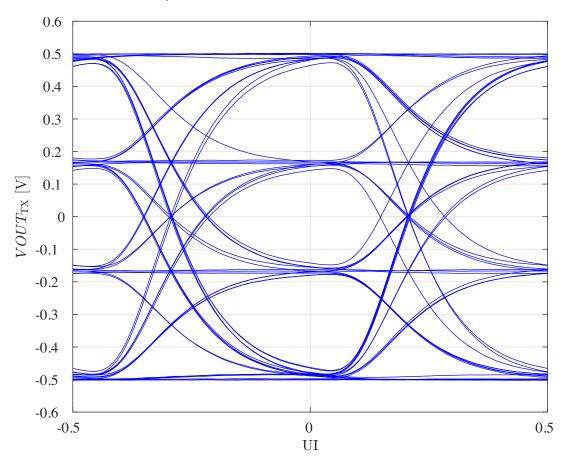

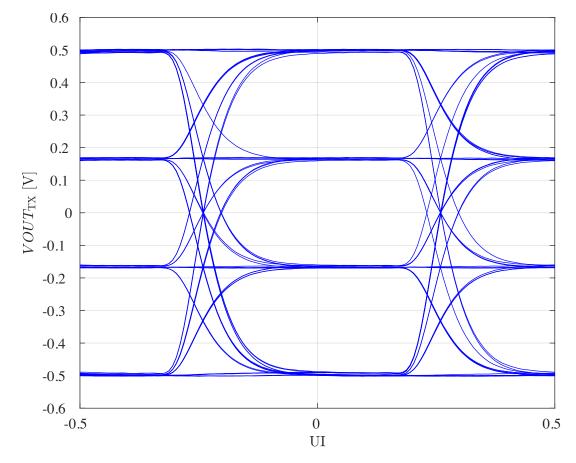

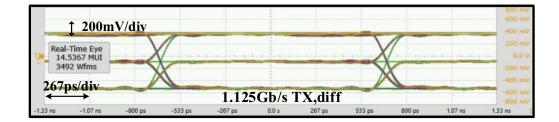

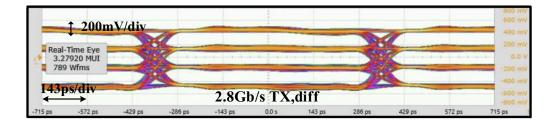

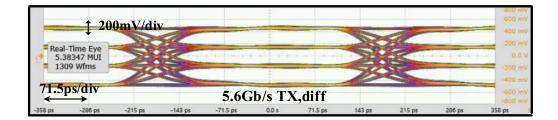

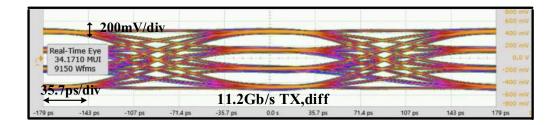

|            | 4.12.4 Eye Diagram                                                      |  |  |  |  |  |

|            |                                                                         |  |  |  |  |  |

|            | asurments                                                               |  |  |  |  |  |

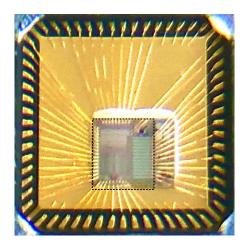

| 5.1        | Test Chip                                                               |  |  |  |  |  |

| 5.2        | PCB Design                                                              |  |  |  |  |  |

| 5.3        | QFN Packaging                                                           |  |  |  |  |  |

|            | 5.3.1 Source Degeneration Technique                                     |  |  |  |  |  |

|            | 5.3.2 Echo Canceling Performance                                        |  |  |  |  |  |

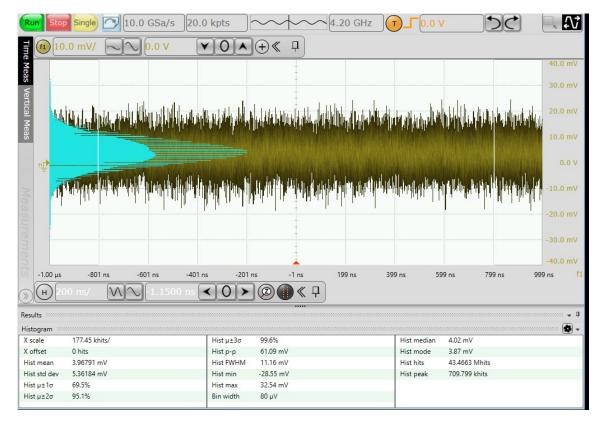

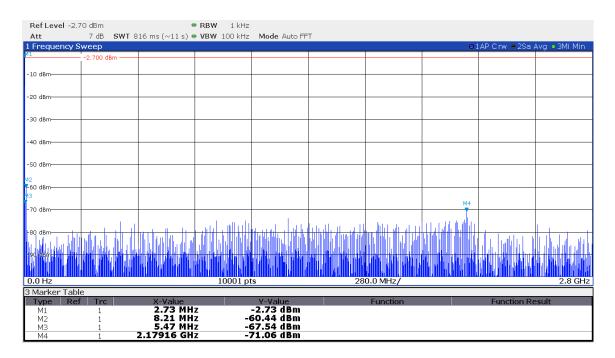

| 5.4        | Dynamic DAC Properties                                                  |  |  |  |  |  |

|            | 5.4.1 Differential Signal                                               |  |  |  |  |  |

|            | 5.4.2 Single Ended Signal                                               |  |  |  |  |  |

| 5.5        | 1000Base-T1 and NGAUTO Compliance Tests                                 |  |  |  |  |  |

|            | 5.5.1 Eye Diagram                                                       |  |  |  |  |  |

|            | 5.5.2 Common Mode Measurement                                           |  |  |  |  |  |

|            | 5.5.3 Transmitter Output PSD                                            |  |  |  |  |  |

|            | 5.5.4 Return Loss                                                       |  |  |  |  |  |

| 5.6        | TX Performance Comparison                                               |  |  |  |  |  |

| Cor        | clusion                                                                 |  |  |  |  |  |

| References |                                                                         |  |  |  |  |  |

| List of Figures | 143 |

|-----------------|-----|

| List of Tables  | 153 |

# 1 Introduction

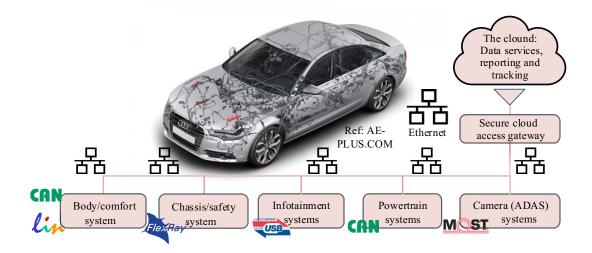

The amount of data transferred has greatly increased with the development of the Internet of Things (IoT) and connectivity between different devices and sub-components. The automotive industry has also evolved with the same rate, adding new features and applications such as driver assisting to self-driving cars and car as a node in a network which uses dozens of sensors around the car [1]. The data from these sensors need to be transferred to the Central Unit (CU) to process and further actuate the target components in the car. In order to transfer the data, various networking technologies such as Controller Area Network (CAN), Local Interconnect Network (LIN), Media Oriented Systems Transport (MOST), FlexRay, etc., have been developed. However, the data throughput of the aforementioned automotive standards is not sufficient for the amount of data being transferred today [2]. Therefore, Ethernet protocol, considered a well-established networking technology, was introduced to the automotive industry to meet the need for a higher data transmission speed.

The automotive industry has successfully introduced 100 Mb/s Ethernet for in-vehicle networks (IVN). The standard IEEE 802.3ch comprises a highly integrated full-duplex multi-speed (1/2.5/5 and 10Gbit/s) IVN PHY+MAC, which needs to meet stringent functional safety requirements (ISO 26262, ASIL- B, etc.) [3].

Realizing Ethernet in the automotive environment requires designing the Physical layer (PHY) to comply with the strict automotive environment standards and focus on different priorities such as power consumption and area in the design, compared to the conventional Ethernet transceivers used in commercial computers. PHY consists of two main components: Physical Coding Sublayer (PCS) and Physical Medium Attachment (PMA), which divide the digital and analog signal processing domains, respectively.

The PMA prepares the signal to be transmitted on the channel via the transmitter, as well as receiving the signal to be decoded for the PCS. The focus of this work is on the analog functionality component of the PHY, presenting the design and implementation of the transmitter within the PMA to comply with the aforementioned Automotive Ethernet (AE) standards.

State-of-the-art of Ethernet transceivers often drives the twisted-pair line (STP/UTP) (shielded/unshielded) directly using a high resolution transmit Digital to Analog Converter (TX-DAC) driver enabling spectral shaping and equalization. TX drivers dissipate most of the power within an Ethernet PHY as they drive the 100  $\Omega$  line. Therefore a power-efficient driver implementation is of prime interest. Furthermore, the TX-DAC resolution should not

only enable the minimum modulation level of PAM4, defined by MultiGBase-T1 standard [4], but also gives the transmitter an extra headroom to perform pre-equalization and power spectrum output shaping.

Given the full-duplex operation, the transmit signal is in the transceiver with the received signal. In order to decode the received signal, the transmit signal power should be subtracted, requiring the implementation of a hybrid solution. Therefore, a transmitter solution satisfying these requirements is one of the main challenges within the PHY implementation, becoming the main focus of this work.

In order to provide a better understanding of the current state of the automotive industry and the requirements set for the Ethernet networking technology, especially the requirements related to the transmitter, the second chapter explains a brief history of networking technologies within the automotive industry. It also presents the requirements of interest on different components of a complying Automotive Ethernet PHY for MultiGBase-T1 (2.5 Gb/s, 5 Gb/s and 10 Gb/s) standards.

The third chapter presents a detailed discussion on the available high-speed Digital-to-Analog Converters (DACs), which can be used for the PHY transmitter. First, to analyze the DACs, some of the static and dynamic properties of the DAC performance is introduced. Next, the two main DAC implementations for the target application, named current-mode DAC and voltage-mode DAC, are introduced. Then, the performance of the DACs is compared in detail to decide on the most optimum solution for the target application. After the analysis, the Source Series Terminated (SST) DAC was found to be the optimum choice to be implemented. The architecture of the proposed SST DAC is studied in detail by highlighting the challenges limiting the performance of the proposed DAC, and possible solutions are presented.

In the fourth chapter, the detailed design of the 9-bit SST DAC operating at 5.6 GS/s is shown. The solutions presented in the third chapter for each of the challenges are utilized and are calculated to fit for the target design. Moreover, simulation results are presented to characterize the DAC meeting the required performance.

The fifth chapter addresses both the characterization setup as well as measurement results to verify the compliance of the proposed TX-DAC to the requirements set by the AE standards.

Finally, a design summary including a state-of-the-art SST driver comparison is presented with the conclusion, in the final chapter.

# 2 Automotive Ethernet

In this chapter, a brief history of the automotive industry's data communication standards is introduced, highlighting the Ethernet standard family. The general architecture of the physical layer within an Ethernet transceiver is introduced and with a detailed study of the requirements and characteristics of parts highlighted in this work.

### 2.1 Brief History of In-car Networking Standards Within Automotive Industry

The need for in-car networking started by introducing sensors and actuators in the car. Automotive manufacturers, however, started developing different standards to enable data communication within the car. The introduction of different standards brought the disadvantage of smaller volumes for the semiconductor vendors, which in turn increases the product's price for each of these solutions.

As time goes by the automotive industry started converging, and today, there is still a variety of networking technologies in use. The main technologies mostly used in cars these days are briefly introduced here and compared with each other in terms of data rate, robustness, and target use case.

#### 2.1.1 Controller Area Network (CAN)

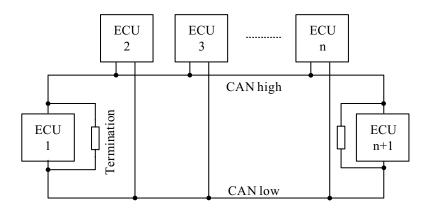

CAN is a bus system in which all Electronic Control Units (ECUs) are connected and share the same wiring, as shown in Fig. 2.1. The decision in which the ECU gets access to the medium is based on the priority level of the message transmitted by the ECU. Nowadays, two different CAN versions are integrated into cars: the High-Speed CAN, used for data rates up to 1 Mbps (HS CAN), and Low-Speed CAN (LS CAN), used for data rates up to 125 kbps. The CAN technology uses Unshielded Twisted Pair (UTP) cables and is a robust choice that allows ECUs in almost all areas of a car to be connected.

Figure 2.1: Typical CAN network diagram.

#### 2.1.2 Local Interconnect Network (LIN)

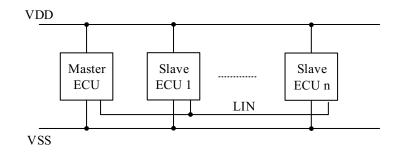

LIN is a cost-efficient solution used for cost-sensitive applications and has few requirements such as basic control of power windows, central locks, etc. LIN is designed as a single-ended, i.e., 1-wire, a system with simple hardware for the transceiver. Single-ended signaling limits immunity and increases emission. Therefore to meet the Electro-Magnetic Compatibility (EMC) requirements, the maximum data rate is limited to 19.2 kbps. An example of a LIN network is depicted in Fig. 2.2 shows up to 16 ECUs sharing the bus, and the Master-Slave concept governs the channel access.

Figure 2.2: Typical LIN network diagram.

### 2.1.3 Media Oriented Systems Transport (MOST)

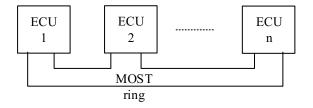

MOST protocol is the response of the automotive industry with the demand to increase the data rate. Using the optical fibers as the medium was the choice to promise the expected

data rate with an EMC compliant solution at a reasonable cost. The MOST protocol is more complicated than the aforementioned CAN or LIN. MOST uses a ring topology as shown in Fig. 2.3 which can handle up to 64 ECUs. The maximum data rate of 13.8 Mbps is possible with this protocol with a unidirectional communication on the fiber.

Figure 2.3: Typical MOST network ring.

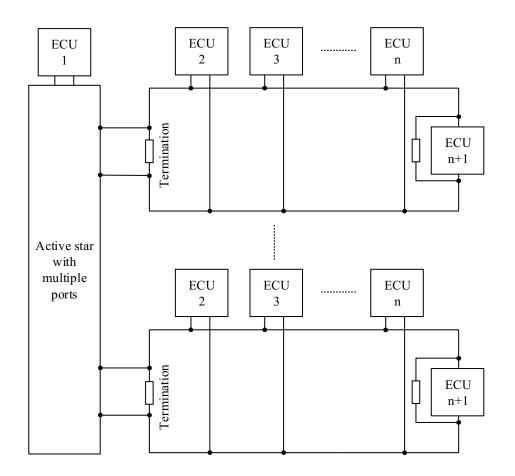

#### 2.1.4 FlexRay

The FlexRay protocol was developed for X-by-Wire applications, eliminating all mechanical fallbacks from the car and having pure electric functions. The key requirements of FlexRay are reliability, determinism, and redundancy, while the gross data rate of FlexRay is 10 Mbps. FlexRay transmits a differential signal on UTP. A small FlexRay system consists of four to five ECUs with linear topology, and with the use of an "active star/star coupler", it is possible to combine several linear topologies in one network as shown in Fig. 2.4 [5].

#### 2.1.5 Automotive Ethernet

Several factors resulted in the introduction of yet another technology: Ethernet for the in-car networking technologies. The most important factor is the increase in the demand for higher data rates [6]. With the trend that the automotive industry is heading, data-driven applications have been added to the car, such as driver assistants, cameras, infotainment systems, etc. Each of these technologies has been provided by one of the previously introduced in-car networking technologies. However, the data rates become the limit and adapting these technologies for higher data rates increases costs. Moreover, various technologies connected through a central gateway to update the software become a challenge as the time it takes to update the software can reach a day due to the low data rate [5].

As a well-established networking standard, Ethernet was the most suitable option to be adapted to be used within in-car networking. The technology provides a sufficient data rate, available in computers and laptops, cost-efficient, and networking technology that enables the idea of handling the car as a node in a larger network. Moreover, a unified network provides convergence of automotive functions with user interface technologies and creates an economy of scale to have a single technology across the industry. Replacing also

Figure 2.4: Typical large FlexRay network diagram with active star.

previously introduced technologies with a single high-speed protocol enhances the flexibility and scalability of in-car networks. Fig. 2.5 shows the use cases where Ethernet can be implemented and replace the older technologies to create a single unified technology across the car.

Ethernet communications are made with differential signaling, improving the robustness and enabling intelligent modulation and filtering on the data. The Automotive Ethernet was introduced with the data rate of 100 Mb/s and the further scaling of this technology to higher data rates is taken by the Institute of Electrical and Electronics Engineer (IEEE).

### 2.1.6 Comparison of In-car Standards and Outlook

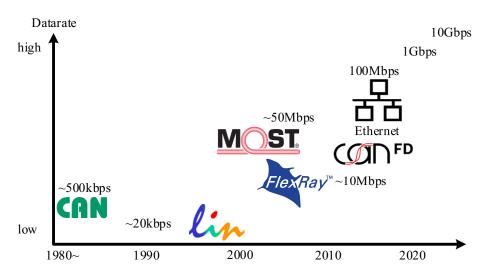

The comparison of the introduced in-car networking technologies is shown in Table. 2.1 in terms of data rate, robustness and target use. Fig. 2.6 shows the timing diagram regarding when each of the technologies is introduced and comparing the data rate of them together.

Figure 2.5: Showing the current in-car networking technologies with their use case in a car and how Ethernet can replace these standards by the ruse of a single technology across the car.

Figure 2.6: Time diagram showing the introduction of the in-car networking standards and comparing the data rate of the technologies.

### 2.2 IEEE803.2 Ethernet Standard Family

IEEE802.3 is a working group within IEEE that defines the Physical Layer (PHY) and data link layer's Media Access Control (MAC) of wired Ethernet.

Automotive Ethernet for  $100 \,\mathrm{Mb/s}$ , once introduced by Broadcom Inc. as the name of BroadR-Reach, was moved to the IEEE standardization working group. This change was

| Technology | Data rate                                  | Robustness              | Target use              |

|------------|--------------------------------------------|-------------------------|-------------------------|

| CAN        | $500\mathrm{kbps}$                         | Differential signalling | Robust ECU control      |

| LIN        | $19.2\mathrm{kbps}$                        | Small data rate         | Low cost control        |

| MOST       | $<25,50,150\mathrm{Mbps}\ \mathrm{shared}$ | Optical medium          | Complex, high-end audio |

| FlexRay    | $< 10 \mathrm{Mbps}\ \mathrm{shared}$      | Differential signalling | X-by-Wire               |

| Ethernet   | $0.1,\!1,\!2.5,\!5,\!10{\rm Gbps}$         | Differential signalling | High data rates         |

Table 2.1: Comparison of discussed in-car networking technologies [5].

made to make this technology open to all vendors, which remove the monopoly of one company providing the technology and favoring the customer to have a better price [5].

### 2.2.1 100Base-T1,1000Base-T1 and NGAUTO Standards

100BASE-T1, which stands for Automotive Ethernet standard with a data rate of 100 Mb/s over a single unshielded twisted pair, was the first series of the Ethernet standards for in-car networking approved in 2015 [6]. But, with the ever-growing amount of data being transferred within a car, a higher data rate was soon in the standardization process and approved by 2016 to enable 1 Gb/s over a single unshielded twisted pair named as 1000BASE-T1.

Quickly, the race for higher data rates leads to introducing higher data rates of  $2.5 \,\text{Gb/s}$ ,  $5 \,\text{Gb/s}$  and  $10 \,\text{Gb/s}$  over a single shielded twisted pair which named 2.5/5/10G-BASE-T1, respectively and got approved by June 2020 [7].

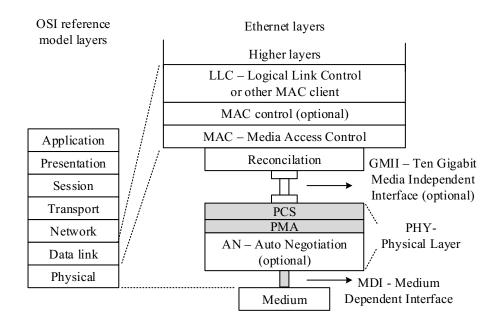

Fig. 2.7 depicts the Ethernet model defined by IEEE802.3 and the International Standards Organization (ISO) Open System Interconnection (OSI) reference model. This model shows where the PHY is defined in the Ethernet model and highlights its different components: physical coding sublayer, physical medium attachment, and auto-negotiation (optional). The Medium in this model is the cable, which for data rates higher than 1 Gb/s is a single STP cable and for lower and equal to 1 Gb/s data rate is a single UTP cable.

### 2.3 Transceiver Architecture

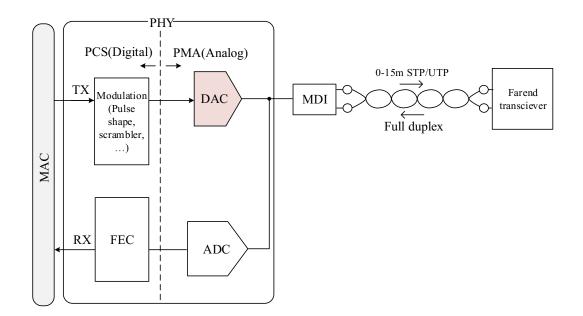

The transceiver architecture showing detailed units within the PHY and MDI is depicted in Fig. 2.8. Different components of such a transceiver are briefly introduced here.

#### 2.3.1 PHY

The PHY is divided into PCS and PMA, which separate the digital and analog functions, respectively. The PHY is normally implemented in a single semiconductor.

Figure 2.7: Relation of IEEE802.3 Ethernet model and the ISO OSI reference model [4].

#### PCS

The PCS receives data from Gigabit Media Independent Interface (GMII) and encodes the input data for the transmitters within the PMA. The input data encoding includes the Pulse Amplitude Modulation (PAM) depending on the data rate standard, scrambling, pulse shaping the signal, etc. The encoding applied to the input data is to increase the robustness of the data transmission and shape the signal spectrum by encoding to complying with the requirements set by the standard [5]. Furthermore, the data received from the PMA goes through a Forward Error Correction (FEC) block to decode the errors.

#### **PMA**

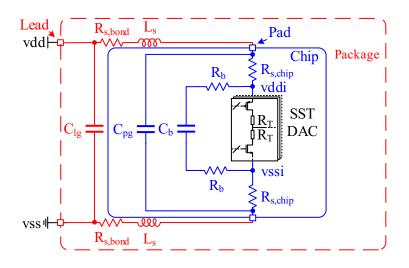

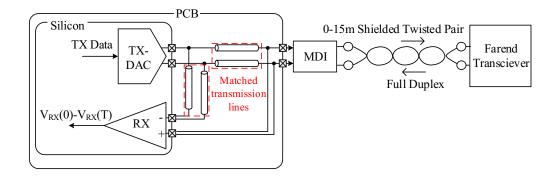

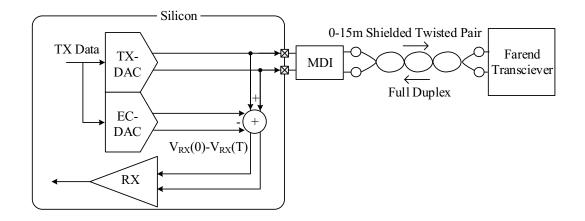

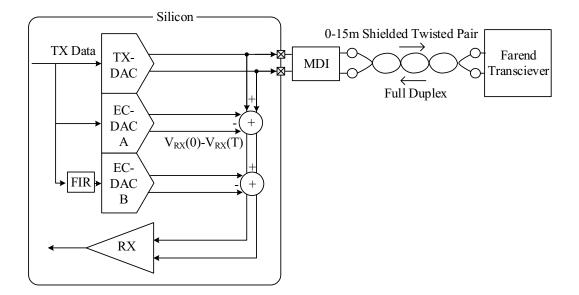

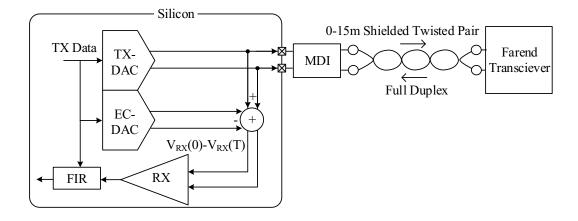

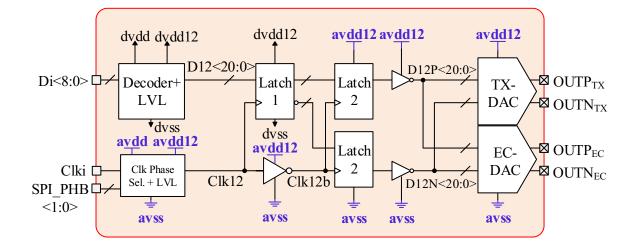

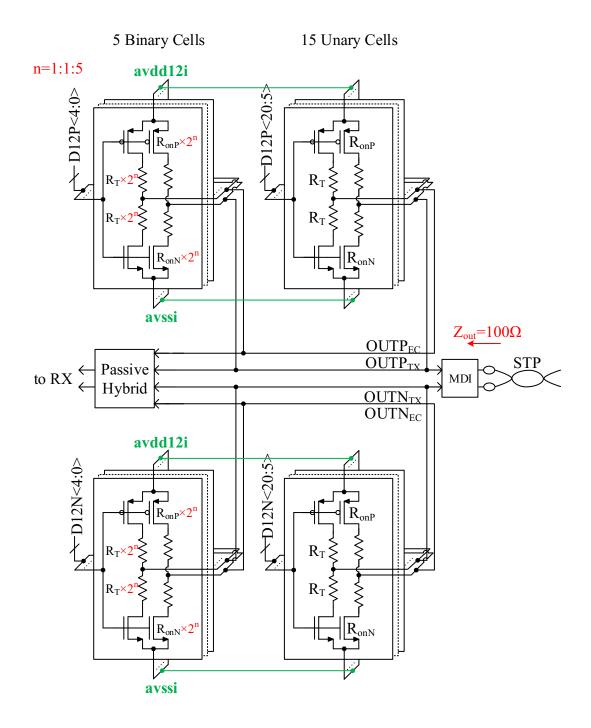

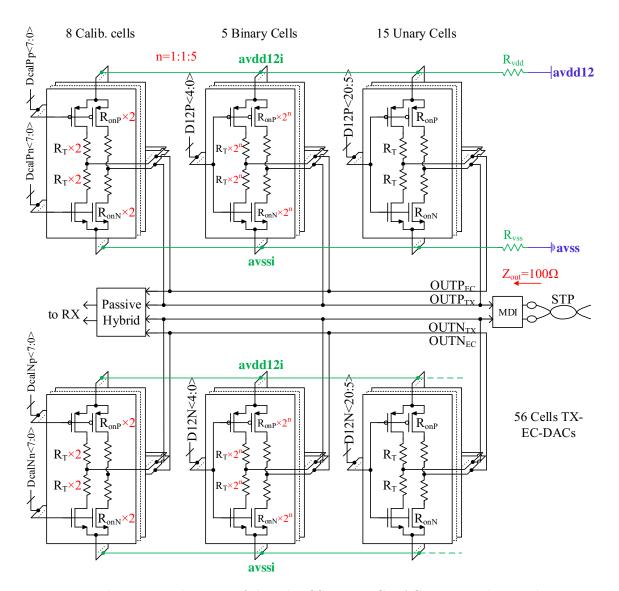

The PMA prepares the signal for the transmission on the channel via the transmitter. In addition, it outfits the received signal to be decoded by the PCS. The DAC transfer the coded digital PAM signal into the analog signal to be transferred on the channel. In the proposed architecture shown in Fig. 2.8, there is an identical DAC to the TX-DAC named EC-DAC, which makes the echo cancellation via the passive hybrid. A hybrid in a full-duplex operation is essential since the received signal and transmit signal are applied on the same channel. Therefore, using a hybrid, the transmit signal is eliminated from the received signal before feeding into the receiver. The detailed discussion of the use of the hybrid and the EC-DAC is discussed in 3.5. The transmit signal is then fed to the Medium Dependent Interface (MDI), which consists of a Common Mode (CM) filter, Common Mode Choke (CMC), and a DC block. After removing the TX power from the received signal, a Low Pass Filter (LPF) is applied to the signal to limit the bandwidth to eliminate the unnecessary noise from the channel. After the LPF, a Programmable Gain Amplifier (PGA) is used to amplify the input signal before feeding it into the Analog to Digital Converter (ADC) to relax the resolution requirements of the ADC. The digital data is then fed to the PCS.

Figure 2.8: The architecture of the Ethernet transceiver showing the units within the PHY and MDI.

#### 2.3.2 Cables

The medium approved for data rates higher than 1 Gb/s is a shielded twisted pair, whereas, for data rates equal or lower than 1 Gb/s, unshielded twisted pair is approved. The shielded twisted pair has a higher bandwidth than the unshielded twisted pair as well as better noise immunity. With increasing 10 fold the data rate and only increasing the modulation level from PAM-3 in 1000Base-T1 to PAM-4 for MultiGBase-T1, the bandwidth needs to increase as well.

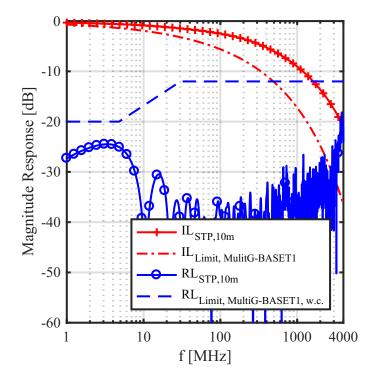

#### STP S-parameter

The S-parameter of a 10 m STP cable suitable for MultiG-BASET1 standards is depicted in Fig. 2.9. The STP link segment should be within the approved limits for the  $S_{12}$ , the insertion loss, and the  $S_{11}$ , the return loss defined by MultiG-BASET1 standard. The insertion loss of each of the link segment should be within

$$IL_{\text{limit,MultiG-BASET1}} \ge 0.002f + 0.68f^{0.45}[dB]$$

(2.1)

where f is the frequency in MHz. Furthermore, to limit the noise at the receiver due to the impedance mismatch, each link segment should be within an acceptable return loss range of

$$RL_{\text{limit,MultiG-BASET1}}(f) \ge \begin{cases} 20 & dB & 1 < f \le 480/2^N \\ 20 - \log_{10}((2^N \times f)/480) & dB & 480/2^N < f \le 3000 \\ 12 - 3N & dB & 3000 < f \le 4000 \end{cases}$$

(2.2)

where f is the frequency in MHz and

$$N = \begin{cases} 0 & IL_{\rm STP}(3\,{\rm GHz}) > 15\,{\rm dB} \\ 1 & IL_{\rm STP}(3\,{\rm GHz}) \le 15\,{\rm dB} \end{cases}$$

(2.3)

In the case of the 10 m STP link segment shown in Fig. 2.9,  $IL_{\text{STP}}(3 \text{ GHz}) \leq 15 \text{ dB}$ , hence N=1.

#### 2.3.3 Full Duplex Operation

One of the main challenges of true full-duplex operation is that the received signal, which is highly attenuated on the 10m UTP/STP, should be detected with a BER less than 1E-12 while simultaneously superimposed with the full-scale transmit signal on the same line. Therefore, the use of an active or passive hybrid is beneficial.

A full-duplex operation on the medium in Automotive Ethernet enables transmitting and receiving data at the same time, effectively doubling the effective data rate on the single STP medium. However, in a full-duplex operation, the TX power of a PHY is present on the medium together with the TX power from the PHY on the far-end. Hence, the use of a hybrid to eliminate TX power is required. The detailed discussion on the implementation of a hybrid is presented in Sec. 3.5. As proposed in Fig. 2.8, a DAC duplicate, EC-DAC, is used to cancel the TX-DAC power echo at the receiver.

#### 2.3.4 Transmitter Requirements

The transmitter with the PMA should provide a maximum of 1 V peak-peak differential output signal when the output is terminated with a 100  $\Omega$  resistive load [4]. Therefore, in order to maximize the power transmission efficiency, the transmitter should be self terminated to 100  $\Omega$  to meet the return loss requirement at the MDI shown in Sec. 2.6. The

transmitter should provide a PAM4 signal for Multi-GBASE-T1, therefore, the transmitter should have a resolution of at least 2-bit. However, in order to have a Relative Level Mismatch ratio (RLM) of greater than 0.95, a minimum of 4-bit is required. Moreover, the stringent requirement of the transmit signal to comply with Power Spectral Density (PSD) and EMC mask, as well as implementing pre-equalization on the TX data for the channel, a higher resolution on the DAC is required. The bandwidth of the transmitter requires to be at least 5.6 GHz to enable PAM4 signaling for the maximum data rate of 10 Gb/s.

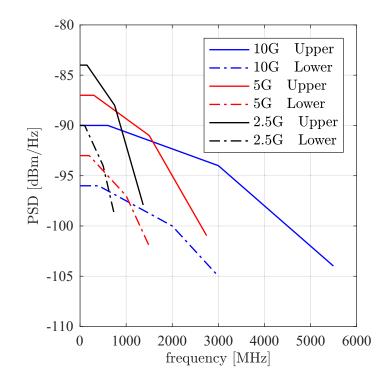

#### PSD

The PSD masks defined by MultiG-BASET1 are dependent on the peak emission requirements, set by Original Equipment Manufacturers (OEMs). The established limit for radiated emission field strength within the frequency range of 70 MHz-1 GHz is  $15 \text{ dB}\mu V$  according to [8]. The transmit peak-peak amplitude of 1 V also affects the PSD mask and considering the system variation and loss effects and required safety margin, the TX power range is within -0.5 dBm to 2 dBm [9]. Given the emission requirements and the signal amplitude, the PSD masks defined for different data rates within MultiG-BASET1 are suggested as shown in Fig. 2.10.

Figure 2.9: S-parameter of a 10 m STP cable and the limit lines for insertion loss and return loss for the worst-case corner. Limit lines are taken from the IEEE802.3 for MultiG-BASET1 standards [4].

$$PSD_{\rm U}(f) = \begin{cases} -90 - K & dBm/Hz & 0 < f \le 600 \times S \\ -89 - K - \frac{f}{600 \times S} & dBm/Hz & 600 \times S < f \le 3000 \times S \\ -82 - K - \frac{f}{250 \times S} & dBm/Hz & 3000 \times S < f \le 5500 \times S \end{cases}$$

(2.4)

$$PSD_{\rm U}(f) = \begin{cases} -96 - K & dBm/Hz & 5 < f \le 400 \times S \\ -95 - K - \frac{f}{400 \times S} & dBm/Hz & 400 \times S < f \le 2000 \times S \\ -90 - K - \frac{f}{200 \times S} & dBm/Hz & 2000 \times S < f \le 3000 \times S \end{cases}$$

(2.5)

where f is the frequency in MHz.

Figure 2.10: The upper and lower mask for the transmit power spectral density for 10GBASE-T1, 5GBASE-T1 and 2.5GBASE-T1 [7].

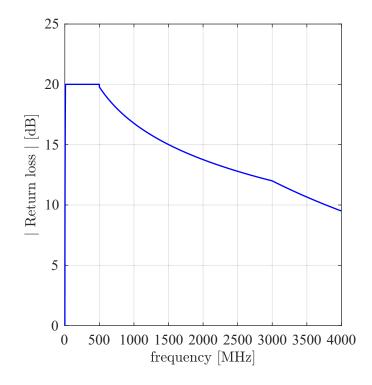

#### **Return Loss**

One of the main requirements in the MDI is the return loss, shown in Fig. 2.11. This transmitter design has a major effect on the return loss in MDI by matching the driver's termination to the cable. According to the -20 dB return loss limit line at DC frequencies up to 500 MHz, it can be calculated that the capacitance mismatch between the TX output

and the load is allowed up to  $320 \,\text{fF}$ . It means that by assuming a  $1 \,\text{pF}$  load capacitance, the TX output capacitance can vary in the range of  $680 \,\text{fF}$  up to  $1.32 \,\text{pF}$ .

$$RL_{\text{MDI}}(f) \leq \begin{cases} 20 - 20 \log_{10} \frac{10}{f} & dB & 1 \leq f \leq 10\\ 20 & dB & 10 \leq f \leq 500\\ 12 - 10 \log_{10} \frac{f}{3000} & dB & 500 \leq f \leq 3000\\ 12 - 20 \log_{10} \frac{f}{3000} & dB & 3000 \leq f \leq 4000 \end{cases}$$

(2.6)

where f is the frequency in MHz.

Figure 2.11: MDI return loss mask according to Eq. 2.6 for 10GBASE-T1, 5GBASE-T1 and 2.5GBASE-T1 [7].

#### 2.3.5 EMC Requirements

The electromagnetic environment of a vehicle moving changes continuously, which can affect the operating of the Ethernet technology. This comes as a security and reliability issue to consider the system's immunity to electromagnetic interference.

The automotive EMC standards used worldwide are published by organizations, IEC/CISPR, and ISO [10]. In an automotive environment, according to the standard set by MultiG-BASET1 the PHY should meet the following requirements [4]:

- $\bullet$  Radiated/conducted emissions: CISPR 25, IEC 61967-1, IEC 61967-4 and IEC 61000-4-21

- $\bullet$  Radiated/conducted immunity: ISO 11452, IEC 62132-1, IEC 62132-4 and IEC 61000-4-21

- $\bullet\,$  Electrostatic discharge: ISO 10605, IEC 61000-4-2 and IEC 61000-4-3

- Electrical disturbance: IEC 62215-3, ISO 7637-2 and ISO 7637-3.

Each of the test setup and limit values should be adjusted to each specific application.

# 3 High Speed DACs

Firstly in this chapter, some of the DAC performance measures which can be calculated and simulated to characterize its performance are introduced. After that, two types of DAC realization, current-mode DAC and voltage-mode DAC, which can directly drive the channel in an Ethernet transceiver at high speed and resolution, are introduced. Each DAC type is discussed in detail to enable comparison based on performance, linearity, power, and silicon area. Next, source series terminated DAC architecture is studied in detail, discussing the challenges in the use of such DAC with possible solutions.

### 3.1 DAC Performance Parameters

A DAC inputs a digital discrete signal and transforms it into a continuous analog signal. The analog signal on the output works as an information carrier in which digital data is modulated. Implementing this circuit using CMOS technology not only modulates the digital input signal to the output but also some of the non-idealities showing up as noise on the output signal. These non-idealities can be due to process mismatch, settling error, noise, parasitics limiting the signal bandwidth, non-linear impedance characteristics, etc. Here some of the standard measures that characterize the DAC performance due to these error sources are introduced. These measures divide into two categories of static and dynamic properties based on the source of the error.

#### 3.1.1 Static Properties

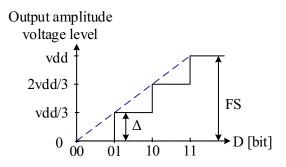

#### Resolution

Fig. 3.1 shows the DC characteristic of a 2-bit DAC. The output voltage levels for an ideal case without any static error is shown in Fig. 3.1 where the straight line has no deviation and each step of the output curve increase with each digital input sequence with an exact step size named  $\Delta$ . In this example, the output amplitude level of 0 corresponds to the Least Significant Bit (LSB), and the output amplitude level of 3 corresponds to the Most Significant Bit (MSB). The defined  $\Delta$  shows the amplitude level increase by one LSB as well. The output LSB step compared to the full-scale output is referred to as the DAC's resolution:

$$Res. = \frac{FS}{\Delta} \tag{3.1}$$

Figure 3.1: Simple 2-bit ideal output amplitude level DAC static characteristic.

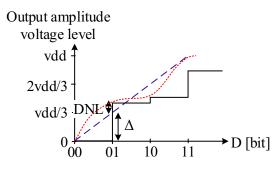

Figure 3.2: Simple 2-bit output amplitude voltage level DAC static characteristic with non-idealities showing the deviation from the ideal curve and DNL measures.

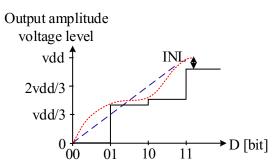

Figure 3.3: Simple 2-bit output amplitude level DAC static characteristic with non-idealities showing the deviation from the ideal curve and INL measures.

#### Static Performance

The static properties of a DAC are due to noise or distortion, which are present at lower frequencies and are data-independent, meaning no memory effect from previous data settling. These types of measures set the best case performance for a DAC as it shows the possible performance without high-frequency non-idealities degrading the performance. The main static properties studied in this work are: gain error, Differential (DNL), and Integral non-linearities (INL). The gain error is the deviation of the input to the output curve from the straight line, which is desired for a perfect digital to analog converter DC characteristic. As input digital code is incremented, an error is introduced as shown in Fig. 3.2 and Fig. 3.3 which also highlight the DNL and INL error at the binary digital input code of  $\theta 1$  and 10, respectively. DNL error considers the differential error added to the output DC characteristic on top of the expected  $\Delta$  increase. However, the INL error shows the total deviation of the analog value from the ideal value. DNL and INL error across the digital input code D can be written as:

$$DNL_{\rm D} = INL_{\rm D} - INL_{\rm D-1} \tag{3.2}$$

and

$$INL_{\rm D} = INL_0 + \sum_{D=0}^{2^N - 1} DNL_{\rm D}$$

(3.3)

where N is the number of bits.

#### 3.1.2 Dynamic Properties

The dynamic properties show the effects of dominating at higher frequencies and introducing errors into the output signal. These types of properties are signal-dependent such as settling error, slewing, jitter, glitches, power supply noise coupling, etc. Here some of the main parameters describing the DAC performance, specifically used in communication theory, are introduced, such as signal-to-noise ratio (SNR), spurious-free dynamic range (SFDR), signal to noise and distortion ratio (SNDR), the effective number of bits (ENOB), etc.

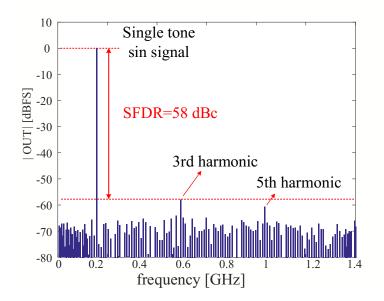

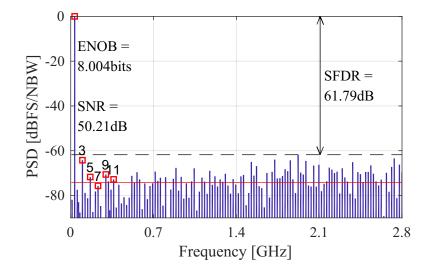

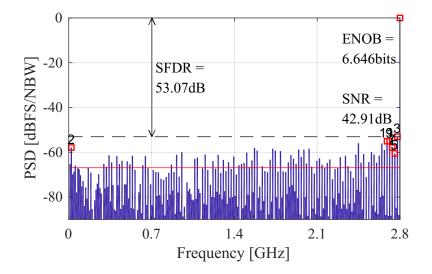

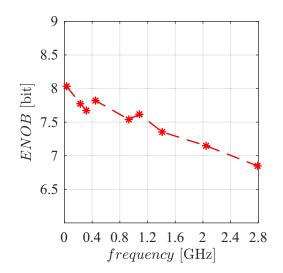

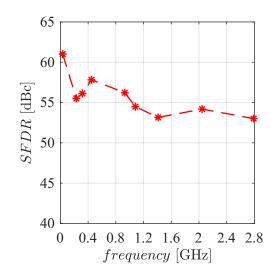

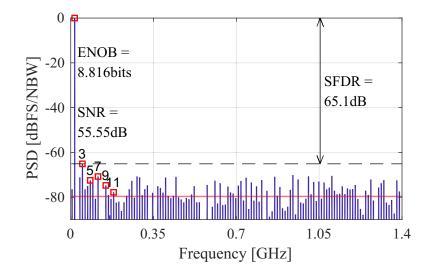

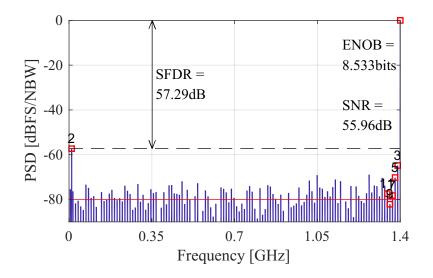

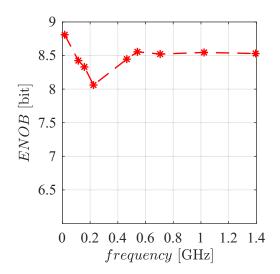

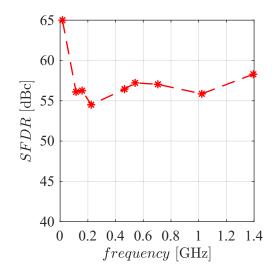

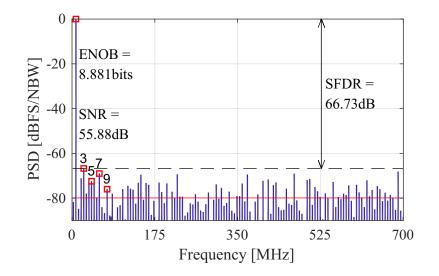

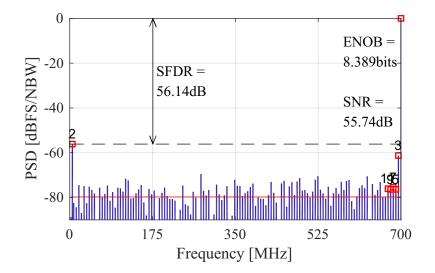

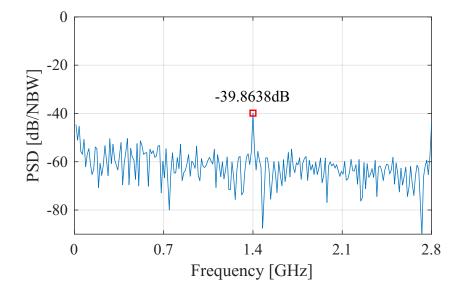

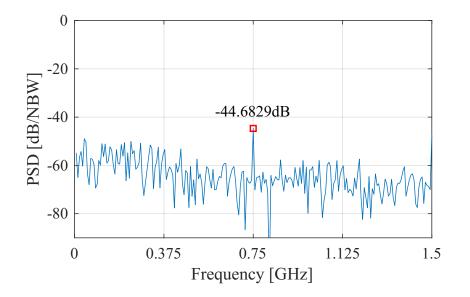

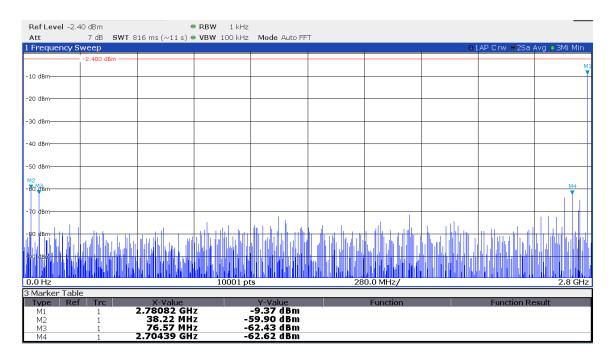

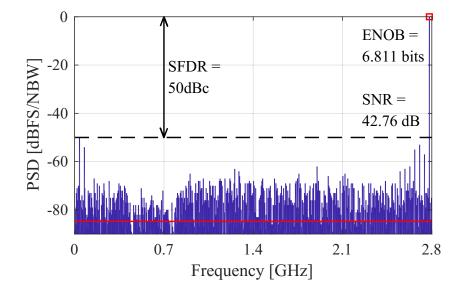

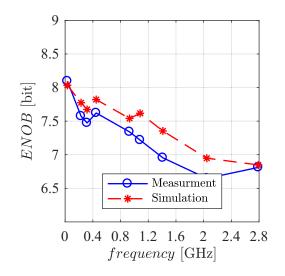

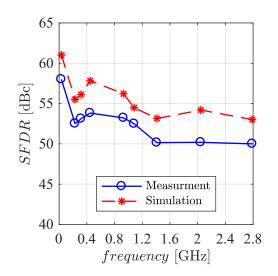

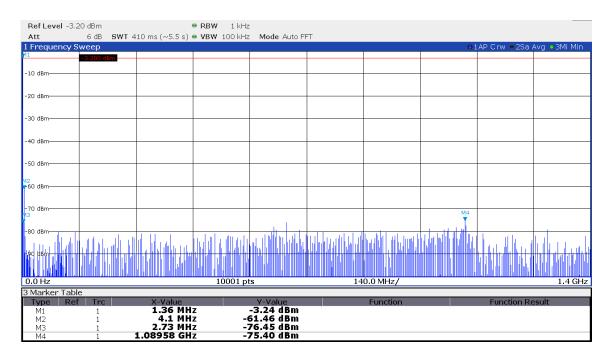

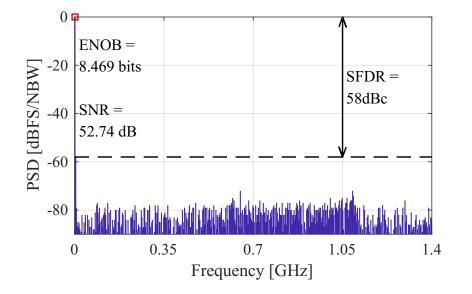

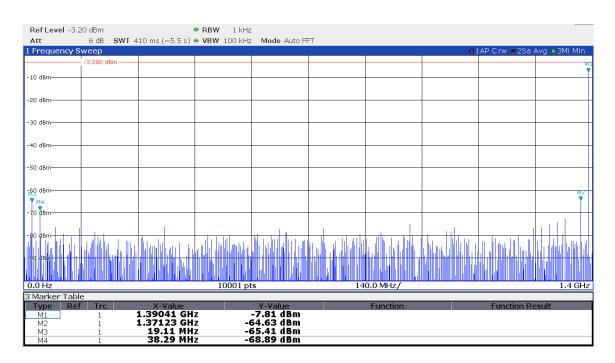

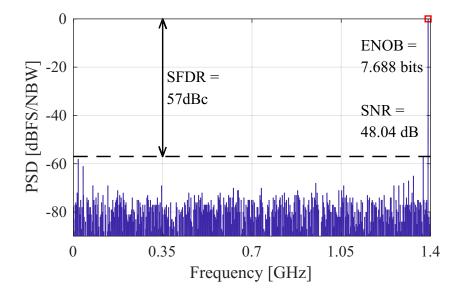

In order to calculate the dynamic properties, a Fast Fourier Transform (FFT) is performed on the analog output signal of the DAC. A simulated frequency spectrum is shown in Fig. 3.4 where a single tone sinusoidal signal is input into a non-linear DAC. The spectrum is shown up to half of the sampling frequency of 2.8 GHz (Nyquist frequency=1.4 GHz). The frequency spectrum is scaled so that the main tone is at zero. The odd harmonics of the main tone, such as 3rd and 5th harmonics, are visible in this spectrum, standing out from the noise floor. The even harmonics are damped since the non-linear DAC under simulation is fully differential. The noise floor is a result of the quantization noise. Above the noise floor, the distortions due to the non-linear effects of the DAC are visible as well.

#### Signal-to-Noise Ratio (SNR)

The power ratio of the main signal and the total noise within a defined frequency band, excluding the harmonic components, provides the SNR ratio:

Figure 3.4: The frequency spectrum of a DAC running at 2.8 GS/s with a single tone sinusoidal signal at its input highlighting SFDR measure and noise floor.

$$SNR = 10 \cdot \log_{10} \frac{P_{\rm s}}{P_{\rm n}} [dB] \tag{3.4}$$

where  $P_{\rm s}$  is the signal power and  $P_{\rm n}$  is the noise power.

#### Spurious-Free Dynamic Range (SFDR)

The SFDR ratio is the ratio of the main signal power and the largest spurious signal within a defined frequency band as

$$SFDR = 10 \cdot \log_{10} \frac{P_{\rm s}}{P_{\rm x}} [dB] \tag{3.5}$$

where  $P_{\rm s}$  is the signal power and  $P_{\rm x}$  is the spurious power. Normally the largest spurious showing up in the spectrum for a differential DAC is the first odd harmonic, the 3rd harmonic.

#### Signal-to-Noise and Distortion Ratio (SNDR)

The SNDR is the ratio of the signal power and the total noise and distortion power within a certain frequency band as

$$SNDR = 10 \cdot log_{10} \frac{P_{\rm s}}{P_{\rm n} + \sum_{k=2}^{\infty}} P_{\rm k}[dB]$$

(3.6)

where  $P_{\rm s}$  is the signal power,  $P_{\rm n}$  is the noise power and  $P_{\rm k}$  is the power of the k-th harmonic.

#### Effective Number of Bits (ENOB)

Certain number of bits that SNDR corresponds to is named as ENOB and calculated as:

$$ENOB = \frac{SNDR - 1.76dB}{6.02dB} [bit].$$

(3.7)

### 3.2 DAC Circuit Implementations

Converting digital data into analog waveform to directly drive a differential impedance of  $100 \Omega$  of a channel is done generally through two architecture types of DACs, namely as voltage-mode and current-mode. In selecting the DACs proposed to be used in this application, it is essential that the minimum peak-peak differential output voltage of 1 V is satisfied. This means a differential current of  $\pm 5 \text{ mA}$  should be supplied between the differential outputs. Therefore the driver should be capable of delivering such rail to rail electrical current change in a limited time to settle defined by the operating frequency. Thus, the two architectures introduced here are the most common options for high-resolution and high-speed demand.

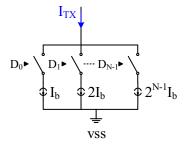

#### 3.2.1 Current-Mode DAC

Current-mode DACs, as the name suggests, as the name suggests, provides a current signal in their output. A simple binary-weighted current-switching DAC is illustrated in Fig. 3.5. Each binary input bit controls a binary-weighted current source scaled to a unit value,  $I_{\rm b}$ . LSB cell is denoted by  $D_0$  and MSB cell by  $D_{\rm N-1}$  for an N-bit DAC. Therefore, the output current of such binary-weighted current-switching DAC is written as:

$$I_{\rm TX} = D_0 \cdot I_{\rm b} + D_1 \cdot 2I_{\rm b} + \dots + D_{\rm N-1} \cdot 2^{(N-1)}I_{\rm b}.$$

(3.8)

The current-steering DAC presented in Fig. 3.5 suffers from dynamic errors. The biasing current cells in this architecture are realized with current mirror switches. When each of the binary-weighted switches turns off, the drain-source voltage on the connected current mirror switch drops to zero. When the corresponding binary-weighted switch turns on again, it

draws a transient current from the output node, introducing an error on the output current,  $I_{\text{TX}}$ . Moreover, the switching activity also introduces fluctuations to the ground voltage, which can cause dynamic non-linearities with the presence of parasitic capacitance and inductance on the ground.

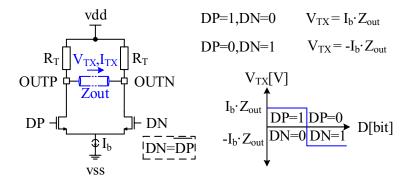

In order to mitigate the aforementioned dynamic errors, the use of current-steering DACs is introduced. A simple circuit implementation of a 1-bit current-steering DAC is shown in Fig. 3.6. Here, the tail current  $I_b$  is steered to the left (DP=1) or the right (DN=1) by the differential pair. Therefore, the voltage fluctuation due to the switching activities across the drain-source voltage of the current mirror switch realizing  $I_b$  is mitigated. Moreover, the differential characteristic of this architecture is also a necessity for driving the differential UTP/STP channels in the target application. In Fig. 3.6, the model of the channel with the impedance  $Z_{\text{out}}$ , as well as termination resistors  $R_{\text{L}}$ , is depicted as well, as these components are necessary for the use of such current-steering DAC for the target application here, to drive a 100  $\Omega$  channel. The use of  $R_{\text{T}}$  provides the self-termination of this driver to match the channel impedance, providing efficient power transmission.

One drawback of using current-steering DAC is to ensure that the current mirror switches are operating in the saturation region. Therefore at least one drain-source voltage is subtracted from the supply voltage vdd, limiting output voltage swing. The current mirrors are required to operate in the saturation region to function well for the purpose of current mirroring [11].

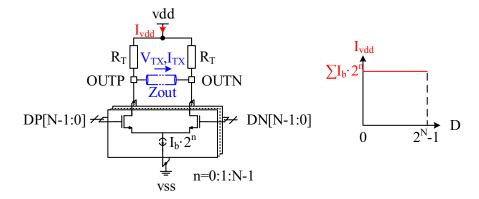

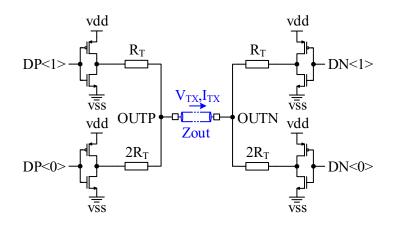

A general circuit implementation of an N-bit binary-weighted current-steering DAC is shown in Fig. 3.7. By injecting  $I_{\text{TX}}$  current into a channel with a known impedance, a defined output voltage can be sensed across the channel. The digital input code in this differential circuit implementation is shown with complementary signals DP[N-1:0] and DN[N-1:0]. The operation of the switches in this architecture is categorized as class-A since not all the current that is drawn is injected into the channel and part of this current is injected into the local termination,  $R_{\text{T}}$ .

The current drawn from the supply is shown. It is constant across the digital input code, one of the major advantages of this architecture in high-speed applications. A constant current drawn from the supply mitigates the noise that can be introduced on the supply rails due to the parasitic capacitance and inductance from the chip packaging and the DAC implementation in silicon. These topics are covered in more detail in the following sections.

#### Segmentation

The binary-weighted architecture shown in Fig. 3.5 and Fig. 3.6 can exhibit a large error or non-monotonicity when the binary input code transition from 011...1 to 100...0, which comes from the mismatch between the current mirror cells [11]. This transition has only 1 LSB change on the output, however, if the accumulated mismatch of the current mirror cells from  $I_{\rm b}$ ,  $2I_{\rm b}$ ,..., $2^{N-2}I_{\rm b}$  is higher than 1 LSB to  $2^{N-1}I_{\rm b}$ , a non-monotonicity has occurred in

Figure 3.5: Simple binary-weighted current-switching DAC.

Figure 3.6: Circuit implementation of a 1-bit current-steering DAC.

Figure 3.7: General circuit implementation of an N-bit current-steering DAC with the current drawn from its power supply plotted across the input digital code.

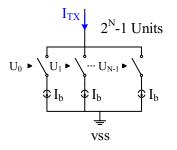

the transfer function. In order to prevent these errors from happening, a segmented DAC architecture is proposed as shown in Fig. 3.8. In a segmented DAC,  $2^N - 1$  thermo-weighted cells are needed. Since all current mirror cells have the same current, a better matching can be achieved comparing to current-mirrors in binary-weighted cells. The same approach can also be considered with the current-steering architecture.

#### **Partial Segmentation**

One main drawback of the full segmentation of the DAC is the increase in the silicon area as each LSB current-mirror cell is designed carefully to minimize the mismatch, as well as increasing the complexity of the coding. Therefore, a trade-off between the binary-weighted and thermo- or unary-weighted should be met in a partially segmented DAC. In a partially segmented DAC, MSB cells are unary-weighted and LSB cells, binary-weighted. This brings a trade-off between the linearity of the DAC, power, and area utilized by it.

Figure 3.8: A simple unary current-switching DAC.

#### Performance, Linearity, Power and Area

By adding all the bias currents across all the cells of a current-steering DAC, the total static power consumption of the main DAC driver can be calculated as:

$$P_{\text{cons.,CM}} = \sum_{n=0}^{n=N} I_{\rm b} 2^{n-1} \cdot \text{vdd} = (2^N - 1) I_{\rm b} \cdot \text{vdd}.$$

(3.9)

Since the current is steered in each cell from one output to the other output in an incident of data change, the total power being drawn from the supply is constant. These types of DACs have the advantage of having current sources to charge and discharge the parasitic capacitors at the outputs fast, hence making it one of the most common DAC implementation for high-speed applications.

The linearity of this DAC is limited to the output impedance of the switches, matching between the switches and bias currents across cells, the timing of the differential controlling signals of DP and DN, clock, data feed-through, etc. Moreover, with scaling down the technology, less headroom is available for switches and the biasing current mirrors.

The area regarding these DACs is mainly addressed to the current mirrors providing a bias current to all the cells. These current mirrors are designed with higher channel length than other devices to minimize the matching effect. Hence, the area of a current-mode DAC is mainly enlarged by the requirement to match the current-mirrors.

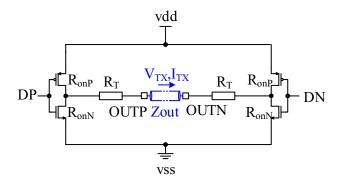

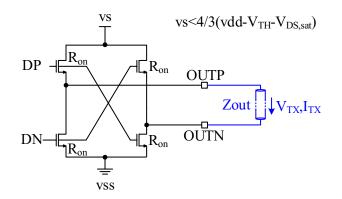

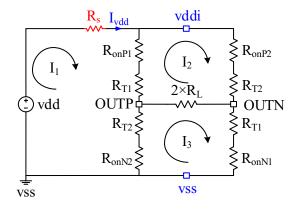

#### 3.2.2 Voltage-Mode DAC

Voltage-mode DACs, as the name suggests, provides a voltage signal in their output. Since such DAC should drive a  $100 \Omega$  differential impedance modeled of the channel, the voltage output signal provided on the output should be capable of delivering such current. Therefore, a resistive type of voltage division is applied rather than capacitive voltage division, which cannot drive the resistive load at high speeds. Voltage-mode DACs use series termination to match the output impedance  $Z_{\text{out}}$  of the channel. A simple 1-bit inverter-based voltage-mode DAC with series termination impedance  $R_{\text{T}}$  is shown in Fig. 3.9. The switches are sized so that the on-resistance of NMOS and PMOS switches are equal ( $R_{\text{onN}} = R_{\text{onP}}$ ). This resistance is mentioned as  $R_{\text{on}}$  throughout this section for simplicity.

To meet the signal integrity, the sum of the termination impedances switches on-resistance  $R_{\text{on}}$  and series resistor  $R_{\text{T}}$  should be equal to the single-ended impedance of the channel  $\frac{Zout}{2}$ :

$$R_{\rm on} + R_{\rm T} = \frac{Zout}{2}.\tag{3.10}$$

In the 1-bit DAC shown in Fig. 3.9, the output driver voltage  $V_{\text{TX}}$  toggles between  $\frac{\text{vdd}}{2}$  when DP=0 (DN=1) and  $-\frac{\text{vdd}}{2}$  when DP=1 (DN=0). This type of voltage-mode architecture is know for the high-swing (rail to rail output voltage swing) and low-impedance switches.

Fig. 3.10 shows a 2-bit inverter-based voltage-mode DAC. In this case, the LSB cell has a termination impedance value of  $2R_{\rm T}$  and on-resistance switches of the LSB cell are also sized to be  $2R_{\rm on}$  comparing to the MSB cell. In the case of the 2-bit architecture, to meet the signal integrity, the parallel combination of the sum of series termination impedances should be equal to the single-ended impedance of the channel  $\frac{Zout}{2}$ :

$$(R_{\rm on} + R_{\rm T}) \parallel 2 \cdot (R_{\rm on} + R_{\rm T}) = \frac{Zout}{2}.$$

(3.11)

Figure 3.9: Circuit implementation of a simple 1-bit inverter base voltage-mode DAC.

Figure 3.10: Circuit implementation of a 2-bit inverter base voltage-mode DAC.

One of the major drawbacks in the voltage-mode DAC shown in Fig. 3.9 is the size of the switches to meet the termination impedance. Normally the switches are sized so that their contribution to the termination impedance is negligible comparing to the termination resistor  $R_{\rm T}$ . This is due to the fact of minimizing the on-resistance non-linearities in the DAC operation. Therefore, an alternative implementation with a low-swing output voltage and high-impedance switches is shown in Fig. 3.11 [12]. In this architecture, all devices are NMOS devices, and to meet the signal integrity, the devices are sized so that the on-resistance of each device when enabled is equal to  $\frac{Zout}{2}$ :

$$R_{\rm on} = \frac{Zout}{2}.\tag{3.12}$$

Noted that in this architecture, the effective  $V_{\text{GS}}$  of the devices on the top and the bottom are different and should be considered for the switch sizing.

Figure 3.11: Circuit implementation of a simple 1-bit low-swing voltage-mode DAC.

Another major drawback of the voltage-mode DAC shown in Fig. 3.9 is the high transient crow-bar currents drawn from the power supply due to the inherent architecture of the inverter. The architecture shown in Fig. 3.12 brings the termination resistor  $R_{\rm T}$  in the push-pull path, lowering the crow-bar current. However, this comes as a drawback of increasing the DAC area and lowering the output bandwidth by doubling the parasitic capacitance at the output node. Moreover, the parasitic capacitance between the drain of the switches and  $R_{\rm T}$ , results in slower settling on the output nodes.

Figure 3.12: Circuit implementation of a simple 1-bit inverter base voltage-mode DAC with termination resistor  $R_{\rm T}$  in the push-pull path.

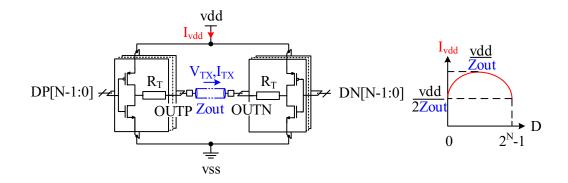

#### N-bit Source Series Terminated DAC

A general circuit implementation of a simple voltage-mode DAC is shown in Fig. 3.13. The current drawn from the power supply showing a parabolic shape across the digital input code is also depicted. This type of DAC is usually called source series terminated (SST)

DAC. As the name suggests, the device is in series with the termination of the DAC. The operation of the switches in this DAC is a class-B mode of operation, and the push-pull mode of operation enables to inject all the current that goes through the supply into the channel. The parabolic shape of the power supply current is one of the inherent features of such DAC which can cause noise on the power supply with PRBS code as the digital input code and drawing a code-dependent current from the power supply. This code-dependent current drawn from the supply can in turn introduce a code-dependent noise on the power supply. In order to overcome this drawback, one can implement a dummy DAC with a reverse parabolic shape to the one shown in Fig. 3.13, to make the total current drawn from supply independent of the digital input code as in Fig. 3.7. However, this comes with doubling the power consumption of the SST DAC which makes it less attractive to the current-steering DAC alternative.

Figure 3.13: General circuit implementation of an N-bit voltage-mode DAC showing as well the current drawn from the power supply across the digital input code.

#### Performance, Linearity, Power and Area

To calculate the static power consumption of the voltage-mode DAC, an integral on the current drawn from the power supply shown in Fig. 3.13 across digital input code. The range of the power consumption of this DAC is calculated as:

$$P_{\text{cons.,VM}} = \left[\frac{\text{vdd}^2}{4R_{\text{T}}}, \frac{\text{vdd}^2}{2R_{\text{T}}}\right]$$

(3.13)

where  $R_{\rm T}$  is assumed 50  $\Omega$ .

The average energy consumption of the DAC also depends on the digital coding applied to the input signal, as if the communication channel used more the average code range instead of the sides for its modulation. Therefore, the average power consumption is closer to its maximum value in the range defined in Eq. 3.13.

The linearity of this DAC is influenced by several factors such as termination impedance linearity, power supply voltage modulation due to the parabolic shape of current demand, matching between the switches, etc.

The area that this DAC requires is mainly driven by the switches and the termination resistance  $R_{\rm T}$ .

# 3.3 Comparison of Voltage-Mode and Current-Mode DACs

To decide which of these type of DAC is the optimum choice, a summarized comparison of the two can make this more clear.

In terms of power, VM DACs are more power efficient using class-B operation, delivering all the current to the channel. In contrast, CM DACs use class-A operation, and part of the current is wasted in the parallel termination structure. To more accurately compare the power consumption of the two, it is assumed that both DACs provide a 1 V peak-peak differential voltage on the channel. Providing this differential output voltage requires vdd = 1 V for VM DAC architecture. The parallel and series termination resistors  $R_{\rm T}$  is assumed equal to 50  $\Omega$  and the impedance of the switches are ignored.

Therefore based on Eq. 3.13, the power consumption range of a VM driver is within [5 mW - 10 mW].

However, providing the same differential output voltage form CM driver requires total bias current of  $\sum_{n=0}^{n=N-1} I_{\rm b} \cdot 2^n \approx 20 \,\mathrm{mA}$  which gives 20 mW as the total static power consumption.

It can be concluded that VM DACs are inherently at least two times and up to four times more power-efficient than CM DACs.

In terms of area, VM DACs inherently are smaller due to the use of a lower number of devices used in its architecture. The current mirror array in CM DACs consumes most of its area as the switches in these current mirrors are designed with a big area to minimize the mismatch error between these switches.

In terms of noise sensitivity, CM DACs are less sensitive to supply noise and support a higher data rate [13]. The current drawn from the power supply of a VM DAC is data-dependent. Thus a data-dependent noise can be modulated on the power supply, depending on the power supply impedance powering this DAC. Moreover, the crow-bar current in VM DACs when both pull-up and -down paths are conducting can create transient current spikes on the current drawn from the power supply  $I_{\rm vdd}$ . Therefore CM DAC has the advantage of a more relaxed requirement on the supply.

The output voltage of VM DACs is limited to the supply voltage level vdd, whereas in CM DACs, the output voltage is limited by the biasing current  $I_{\rm b}$ . Therefore the technology scaling going toward lower supply voltage makes the use of VM DACs more challenging.

# 3.4 SST DAC

Source series terminated DAC proves to be an optimum choice for the target application. The most important factor influencing this choice is the power consumption of such DAC, which can be at least two times and up to four times more efficient than the other possibility, CM DAC. In this section, the SST DAC architecture with few modifications from the general architecture is shown in Fig. 3.13 is presented. The challenges of designing this DAC to meet the requirements are discussed and possible solutions are presented. After that, in the next chapter, the implementation of such solutions is presented and backed up with simulation and measurement results.

#### 3.4.1 Architecture and Requirements

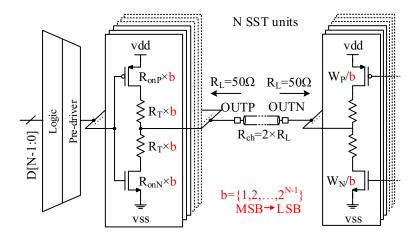

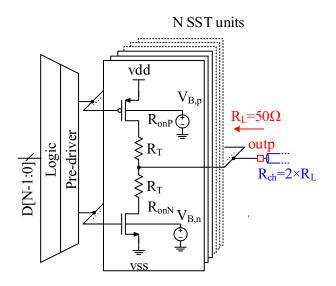

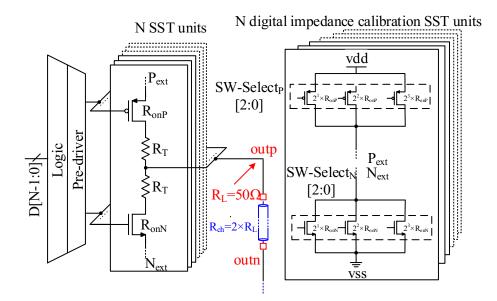

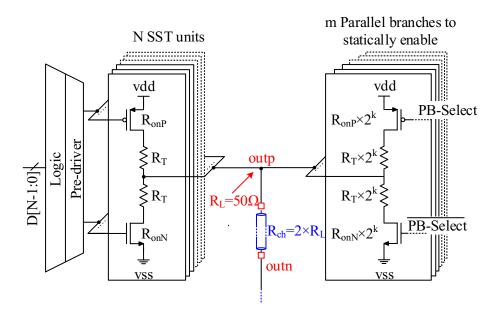

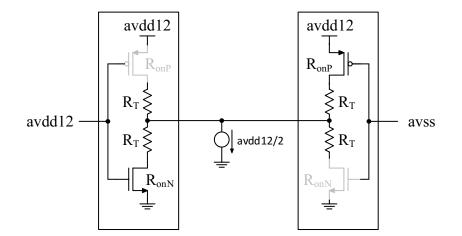

The general architecture of an N-bit SST DAC is shown in Fig. 3.14. Unlike the circuit schematic is shown in Fig. 3.13, in this architecture, the termination resistance  $R_{\rm T}$  is shared in both pull-up and pull-down paths. This lowers the crow-bar current by approximately five times [14]. Details of this modification and the effects are discussed in detail in this chapter. Each of the SST units' termination impedance is built from two components, a resistor  $R_{\rm T}$  in series with MOSFET switches (resistance value  $R_{\rm onN,P}$ ). In this circuit schematic, all the SST cells are binarily segmented, meaning from MSB cells to LSB cells, with each incrementation, the cell's impedance is doubled. Furthermore, the parallel of all the unit cells on each side, OUTP, and OUTN should provide a single-ended termination impedance of 50  $\Omega$ , matching the impedance of the channel. The channel model of the differential twisted pair (UTP or STP cable) is assumed ideally as  $R_{\rm ch} = 100 \,\Omega$ .

$$R_{\rm MSB} = R_{\rm onP} + R_{\rm T} = R_{\rm onN} + R_{\rm T} = R_{\rm on} + R_{\rm T}$$

(3.14)

$$R_{\rm LSB} = R_{\rm MSB} \times 2^{N-1} = (R_{\rm on} + R_{\rm T}) \times 2^{N-1}.$$

(3.15)

Parallel combination of all cells gives:

$$\frac{1}{R_{\rm L}} = \frac{1}{R_{\rm MSB}} \sum_{i=0}^{N-1} 2^{-i} = \frac{1}{R_{\rm MSB}} + \frac{1}{2 \times R_{\rm MSB}} + \dots$$

(3.16)

with the assumption of high number of bits, the approximate value for  $R_{\text{MSB}}$  is:

$$R_{\rm MSB} \approx 2 \times R_{\rm L} = 100 \,\Omega. \tag{3.17}$$

Figure 3.14: The circuit schematic of an N-bit SST DAC [15].

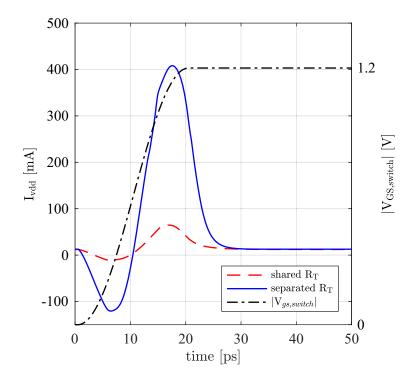

## 3.4.2 Performance, Linearity, Power and Area

Sharing the termination impedance between the active and passive devices, unlike architecture shown in Fig. 3.13, comes with few advantages and disadvantages. The biggest benefit, in this case, is enabling higher operating speed with lower dynamic power consumption. Making the switches big so that it reaches almost zero on-resistance, the capacitance at the gate of these devices requires spending a lot of dynamic power and area to drive the gates, which causes a more stringent requirement on the power supply to provide these high peaks of transient current. This limits the choice of the type of packaging that can be used to place the die and connect the power supply with more expensive solutions. Therefore, active devices participating in the termination come with the advantage of lower power, lower area, and cheaper packaging solutions.

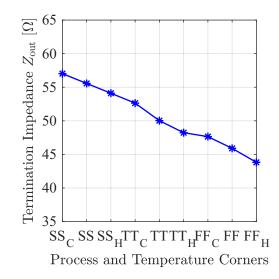

On the other hand, active device on-resistance  $R_{\rm on}$  is highly non-linear comparing to passive devices such as poly resistors. The non-linearity of such devices comes mainly as the dependence of  $R_{\rm on}$  on the voltage drop across it, which is data-dependent in the SST DAC architecture. Therefore a data-dependent non-linearity is added to the termination impedance. This data-dependent variation on the termination impedance not only makes the matching for the target return loss presented in Sec. 2.3.4 challenging but also causes deviation of the analog output voltage level from its ideal value, increasing the INL error. Therefore, the linearity of this DAC is dependent on the ratio in which the termination impedance is divided between the passive to active components  $r_{\rm RM} = \frac{R_{\rm T}}{R_{\rm on}}$ . The choice of this ratio is discussed in detail in the next section.

## 3.4.3 Linearity Limitations

To design an SST DAC, one should consider this trade-off between power, area, package expenses, and linearity. By studying the sources of non-linearity, careful study of the active to passive termination ratio, and the packaging effect, it is shown that this linearity limitation can improve by using the source degeneration effect of active devices. In this case, the mathematical model of a simplified SST DAC is presented to study the static effect of such non-linearities and the improvements which can be suggested. A brief explanation of this approach is presented in [15].

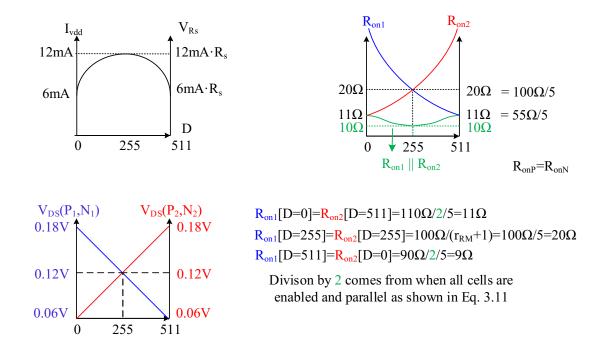

#### Active to Passive Termination Ratio

The trade-off between area/power and linearity performance is given by the ratio between the passive and active termination portion  $r_{\rm RM} = \frac{R_{\rm T}}{R_{\rm on}}$ . Therefore, the resistance of each (active and passive) portion considering a total termination resistance of 50  $\Omega$  is

$$R_{\rm on} = \frac{R_{\rm MSB}}{r_{\rm RM} + 1} \approx \frac{100\,\Omega}{r_{\rm RM} + 1},\tag{3.18}$$

$$R_{\rm T} = \frac{r_{\rm RM} \times R_{\rm MSB}}{r_{\rm RM} + 1} \approx \frac{r_{\rm RM} \times 100\,\Omega}{r_{\rm RM} + 1}.\tag{3.19}$$

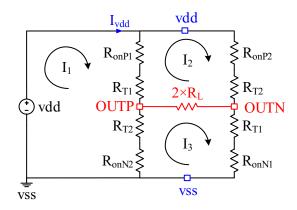

To study the static linearity of the DAC, a resistive model is developed shown in Fig. 3.15 to study the non-linear effect of the MOSFET switches.

Figure 3.15: The equivalent resistive model of the SST DAC.

To study the effect of the switch non-linearities, the first analysis assumes linear switch resistance. The on-resistance  $R_{on}$  in the linear region and it is modeled as

$$R_{\rm on} = \frac{V_{\rm DS}}{I_{\rm D}} = \frac{V_{\rm DS}}{\mu C_{\rm OX}^{\prime} \left(\frac{W}{L}\right) \left(V_{\rm GS} - V_{\rm TH} - \frac{V_{\rm DS}}{2}\right) \cdot V_{\rm DS}}.$$

(3.20)

Assuming the drain-source voltage much smaller than the overdrive voltage,  $R_{\rm on}$  is simplified as

$$R_{\rm oni} = \frac{1}{\mu_i C'_{\rm OXi} \left(\frac{W}{L}\right)_i \left(V_{\rm GSi} - V_{\rm THi}\right)} , \ i = N, P$$

(3.21)

where shows no dependency on  $V_{\rm DS}$ .

The simplified resistor model for active and passive devices as a function of the digital input code, the number of bits, and the ratio of passive to active termination  $r_{\rm RM}$  is calculated as:

$$R_{\text{oni1}} = R_{\text{on}} \times \frac{2^N - 1}{D}, \ R_{\text{oni2}} = R_{\text{on}} \times \frac{2^N - 1}{2^N - 1 - D}, \ \mathbf{i} = \mathbf{N}, \mathbf{P}$$

(3.22)

$$R_{\rm T1} = R_{\rm T} \times \frac{2^N - 1}{D} , \ R_{\rm T2} = R_{\rm T} \times \frac{2^N - 1}{2^N - 1 - D}$$

(3.23)

where N is the number of bits, D is the digital input code value within the range of zero to  $2^N - 1$  and  $R_{\rm on}$  and  $R_{\rm T}$  are given in Eq. 3.18, 3.19. By solving the three Kirchhoff's Voltage Law (KVL) loops (as shown in Fig. 3.15):

$$I_1: \text{vdd} + (I_{\text{vdd}} - I_2) \cdot (R_{\text{onP1}} + R_{\text{T1}}) + (I_{\text{vdd}} - I_3) \cdot (R_{\text{onP2}} + R_{\text{T2}}) = 0; \quad (3.24)$$

$$I_2: I_2 \cdot (R_{\text{onP2}} + R_{\text{T2}}) + (I_2 - I_3) \cdot 2 \times R_L + (I_2 - I_{\text{vdd}}) \cdot (R_{\text{T1}} + R_{\text{onP1}}) = 0; \quad (3.25)$$

$$I_3: I_3 \cdot (R_{\text{onN1}} + R_{\text{T2}}) + (I_3 - I_{\text{vdd}}) \cdot (R_{\text{onN2}} + R_{\text{T2}}) + (I_3 - I_2) \cdot 2 \times R_{\text{L}} = 0.$$

(3.26)

Solving these three KVL loops yields the supply current:

$$I_{\rm vdd} = \frac{\rm vdd}{R_{\rm L}} \cdot \left(\frac{-D^2}{(2^N - 1)^2} + \frac{D}{2^N - 1} + \frac{1}{4}\right).$$

(3.27)

$$V_{\rm OUT} = OUTP - OUTN = \text{vdd} \cdot \left(\frac{1}{2} - \frac{D}{2^N - 1}\right) = \text{vdd} \cdot \left(\frac{1}{2} - \frac{D}{2^N - 1}\right)$$

(3.28)

This shows a fully linear output curve with zero INL error. Calculating for D=0 and D=511, the two rails of the DAC output, one can derive:

$$V_{\text{OUT,diff,peak-peak}} = \text{vdd} \cdot \left(\frac{1}{2} - \left(-\frac{1}{2}\right)\right) = \text{vdd}.$$

(3.29)

For the target application of  $V_{\text{OUT,diff,peak-peak}} > 1 \text{ V}$  in this work, it is possible to conclude that the minimum supply voltage to use for such SST architecture is 1 V. However, there are other design considerations regarding PVT calibration discussed in the next subsection, which lowers down the differential output voltage level. Hence to compensate for the drop in the differential output voltage level, the supply voltage is increased to 1.2 V.

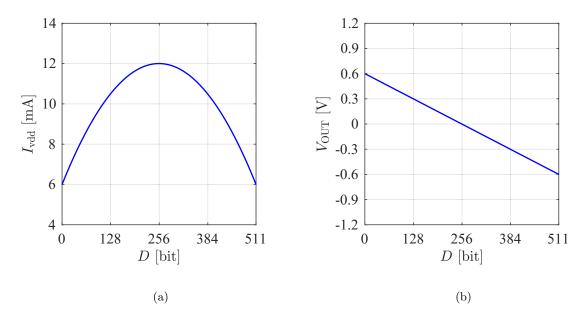

The supply current and the output voltage are plotted across the digital input code shown

if Fig. 3.16(a) and Fig. 3.16(b), respectively. It is assumed for a 9-bit DAC with a supply voltage of 1.2 V in this plot.

Figure 3.16: The power supply current (a) and the DAC output voltage (b) across digital input code.

#### Switch Operating Region

So far, the non-linear behavior of the SST DAC is studied assuming the switches are perfectly linear. However, the drain-source voltage of the switches is data-dependent and introduces a first-order non-linearity, which is considered in the following model.

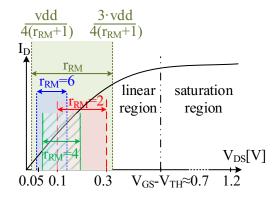

The minimum and maximum drain-source voltage variation of the switches is derived as a function of  $r_{\rm RM}$  showing the range which switch is operating across the digital input code

$$V_{\rm DS,min} = \frac{\rm vdd}{4(r_{\rm RM}+1)}$$

,  $V_{\rm DS,max} = \frac{3 \cdot \rm vdd}{4(r_{\rm RM}+1)}$ . (3.30)

It becomes clear that the smaller the ratio  $r_{\rm RM}$ , the larger the  $V_{\rm DS}$  variation across the digital input code. Therefore, choosing a lower  $r_{\rm RM}$  ratio, the operating region of the switches moves toward the saturation region, causing more non-linear on-resistance of the switch, as shown in Fig. 3.17. The on-resistance model, introduced in Eg. 3.20 can be rewritten to add the drain-source voltage dependency as:

Figure 3.17: The I-V curve of a MOSFET switch highlighting The operating region of the switches with different  $r_{\rm RM}$ .

$$R_{\rm on} = \frac{1}{\mu C_{\rm ox}'\left(\frac{W}{L}\right) \left(V_{\rm GS} - V_{\rm TH} - \frac{V_{\rm DS}}{2}\right)} \tag{3.31}$$

where  $0 < V_{\text{DS}} < (V_{\text{GS}} - V_{\text{TH}})$ . It can be rearranged as:

$$R_{\rm on} = \frac{\frac{1}{\beta \cdot V_{\rm od}}}{1 - \frac{V_{\rm DS}}{2V_{\rm od}}} = \frac{1}{\beta \cdot V_{\rm od}} \cdot \frac{1}{1 - u}$$

(3.32)

where  $\beta = \mu C'_{\text{ox}}\left(\frac{W}{L}\right)$ ,  $V_{\text{od}} = V_{\text{GS}} - V_{\text{TH}}$  and  $u = \frac{V_{\text{DS}}}{2V_{\text{od}}}$ . Applying a Taylor series expansion on Eq. 3.32, one obtains

$$R_{\rm on} = \frac{1}{4\beta V_{\rm od}^3} \cdot V_{\rm DS}^2 + \frac{1}{2\beta V_{\rm od}^2} \cdot V_{\rm DS} + \frac{1}{\beta V_{\rm od}}$$

(3.33)

and

$$\frac{W}{L} = \frac{\frac{1}{4V_{\rm od}^3} \cdot V_{\rm DS}^2 + \frac{1}{2V_{\rm od}^2} \cdot V_{\rm DS} + \frac{1}{V_{\rm od}}}{\mu C_{\rm ox}' \cdot R_{\rm MSB} / (r_{\rm RM} + 1)}.$$

(3.34)

Finally, minimizing the W/L (decrease active device area and in addition to that its gate capacitance), the overdrive voltage  $V_{\rm od}$  should be maximized, and  $r_{\rm RM}$  should be minimized.

To calculate the INL error of the DAC for different  $r_{\rm RM}$  ratios, the W/L ratio of the switches is calculated and replaced in  $R_{\rm on}$  devices modeled in Fig. 3.15.

In order to calculate the W/L ratio based on Eq. 3.34,  $\mu_{\rm P}C'_{\rm ox} = 20 \frac{\mu A}{V^2}$  and  $\mu_{\rm N}C'_{\rm ox} = 40 \frac{\mu A}{V^2}$  for PMOS and NMOS devices are assumed, respectively. Furthermore,  $V_{\rm DS}$  assumed in Eq. 3.34, is for middle of the digital input code, D=256. At this point, the output differential voltage is approximately zero and the voltage on each of the outputs is half of the supply voltage. In this case, one can derive:

$$V_{\rm DS,D=256} = \frac{1.2}{2 \cdot (1 + r_{\rm RM})} \tag{3.35}$$

where vdd = 1.2 V.

The calculated W/L ratio for each NMOS and PMOS devices with

(

(

$r_{\rm RM} = 2$ :

$$W/L)_{\rm P} = 47, (W/L)_{\rm N} = 23.5$$

(3.36)

$r_{\rm RM} = 4:$

$$W/L)_{\rm P} = 94, (W/L)_{\rm N} = 47$$

(3.37)

and  $r_{\rm RM} = 6$ :

$$(W/L)_{\rm P} = 188, (W/L)_{\rm N} = 94.$$

(3.38)

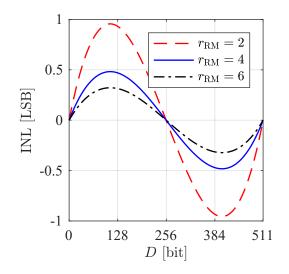

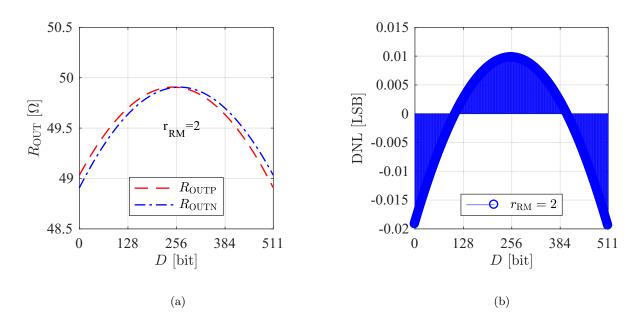

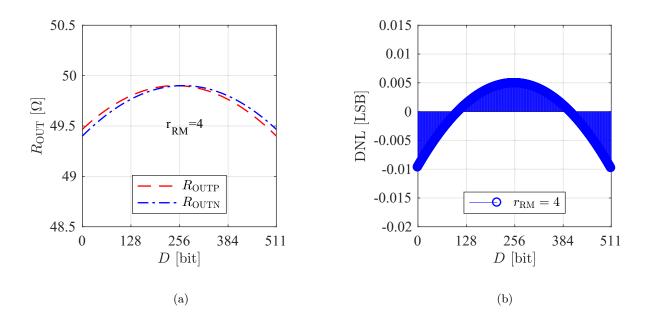

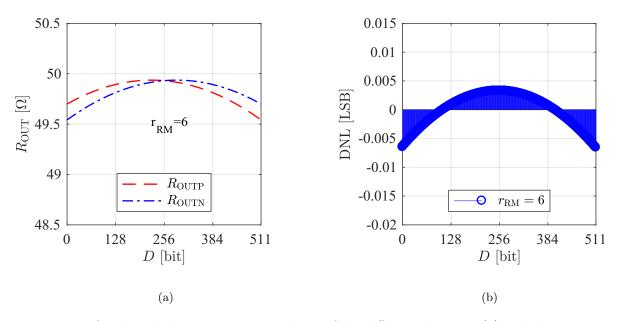

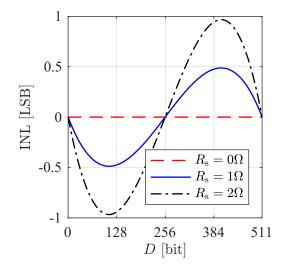

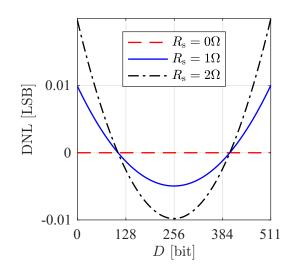

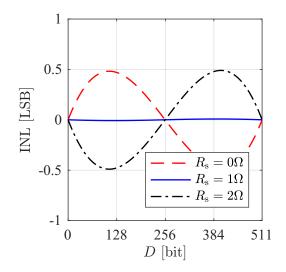

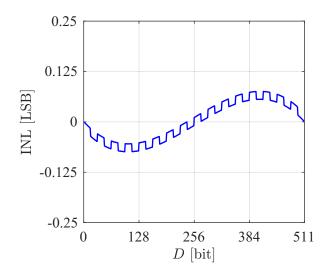

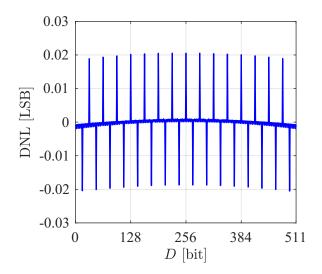

The obtained INL error for  $r_{\rm RM} = 2$ ,  $r_{\rm RM} = 4$  and  $r_{\rm RM} = 6$  is depicted in Fig. 3.18 with the peak-peak INL error of 1.92 LSB, 0.97 LSB and 0.65 LSB, respectively. Furthermore, the DNL error with the single ended output impedance of each of the differential outputs for  $r_{\rm RM} = 2, 4$  and 6 are depicted in Fig. 3.19, Fig. 3.20 and Fig. 3.21, respectively.

Figure 3.18: INL error of the SST DAC across  $r_{\rm RM} = 2, 4$  and 6 with the peak-peak INL error of 1.92 LSB, 0.97 LSB and 0.65 LSB, respectively.

The choice of the ratio  $r_{\rm RM}$  comes with the trade-off between power/area and non-linearity. Moreover, the size of the switches defines as well the input capacitance for the pre-driver stage. The larger the input capacitance, the slope at the gate of the active switches within the SST unit, limits the output is settling as well, which at high-frequency operation, can

Figure 3.19: Single ended termination impedance of the differential output (a) and the DNL error (b) across digital input code with  $r_{\rm RM} = 2$ .

Figure 3.20: Single ended termination impedance of the differential output (a) and the DNL error (b) across digital input code with  $r_{\rm RM} = 4$ ,.

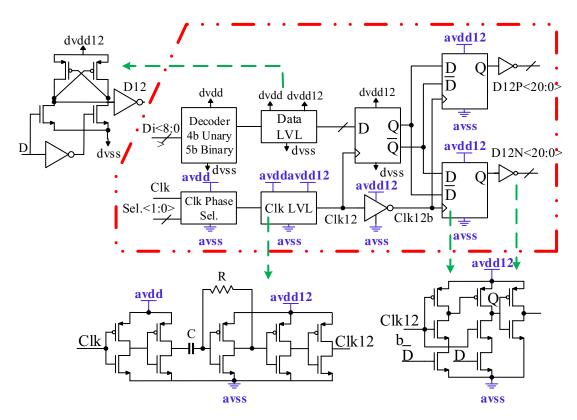

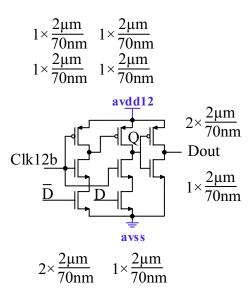

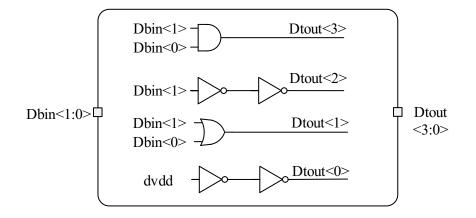

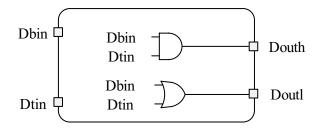

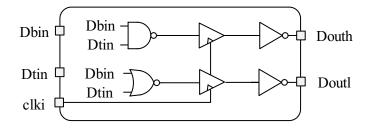

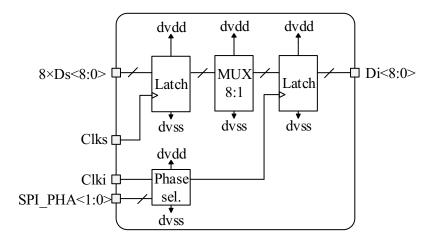

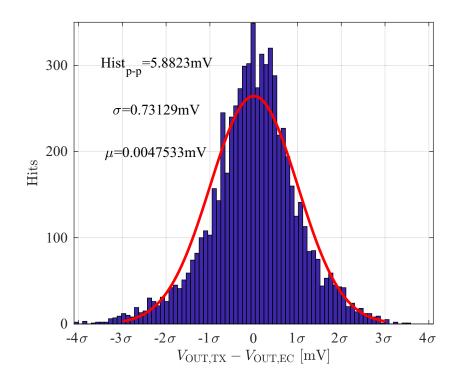

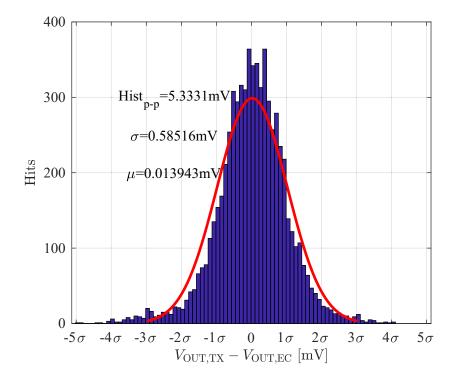

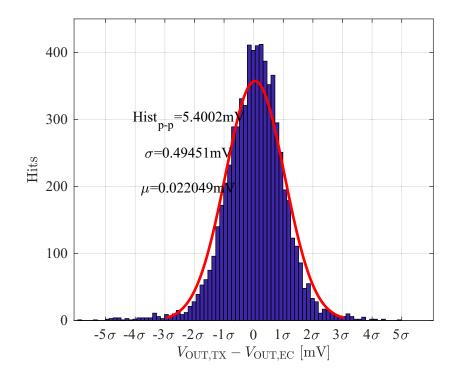

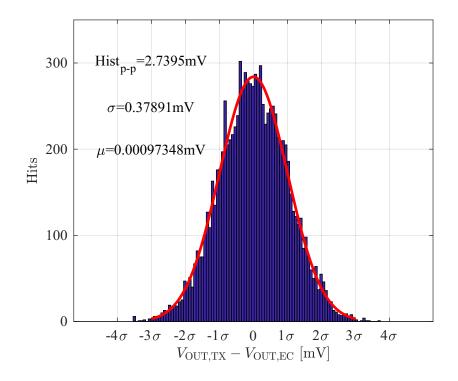

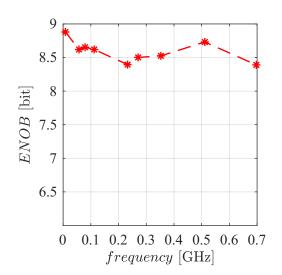

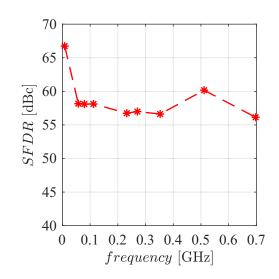

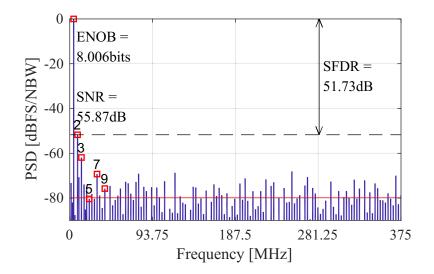

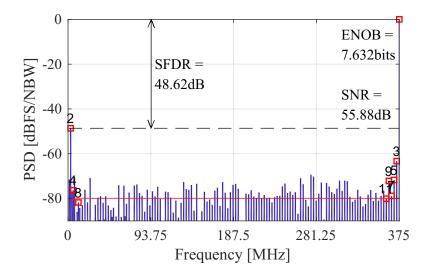

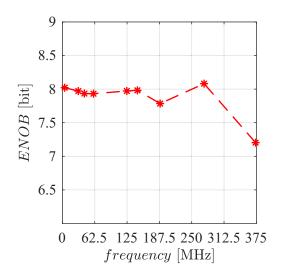

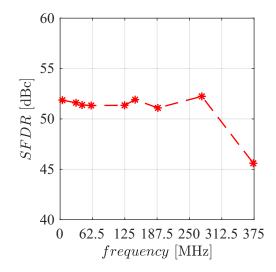

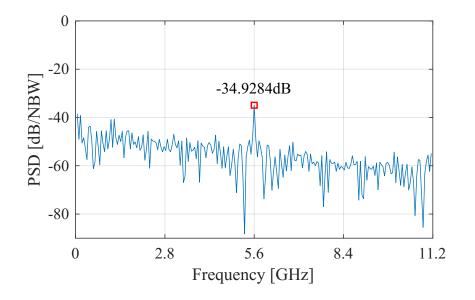

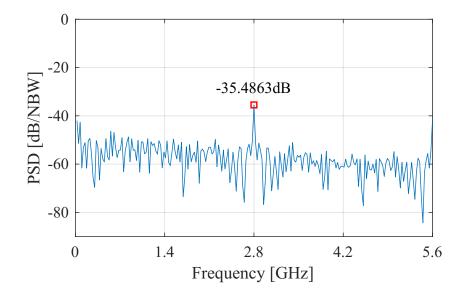

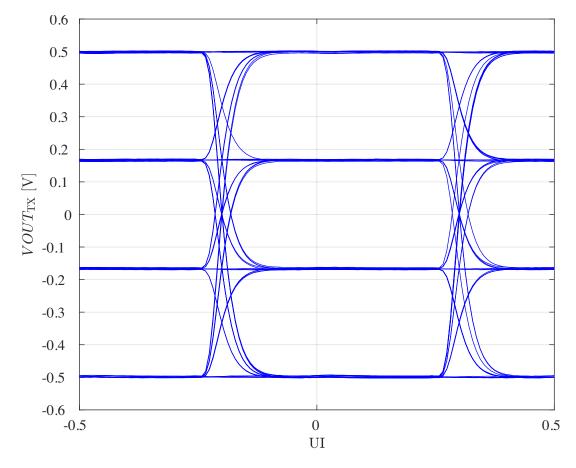

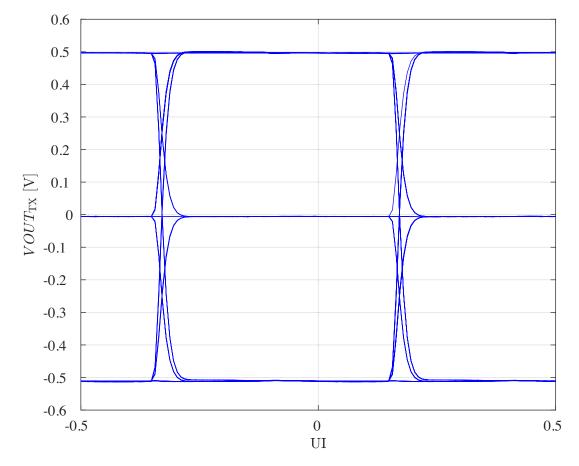

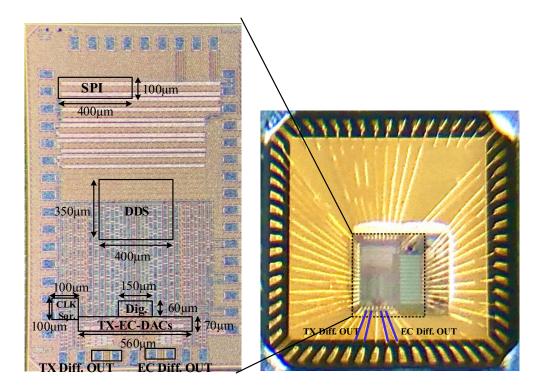

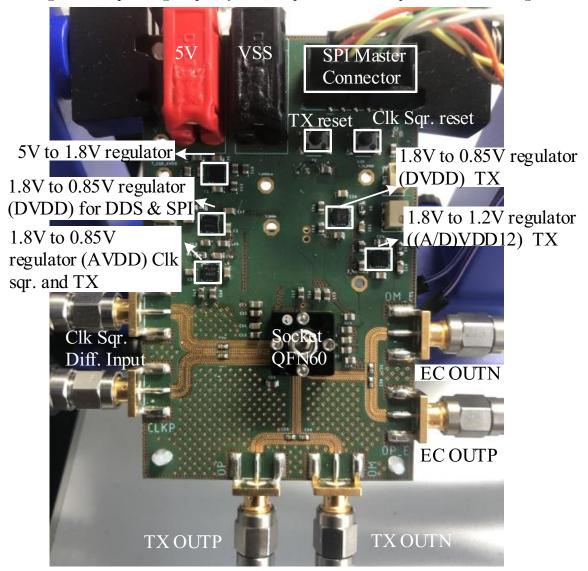

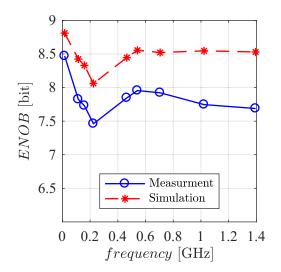

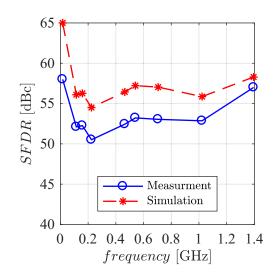

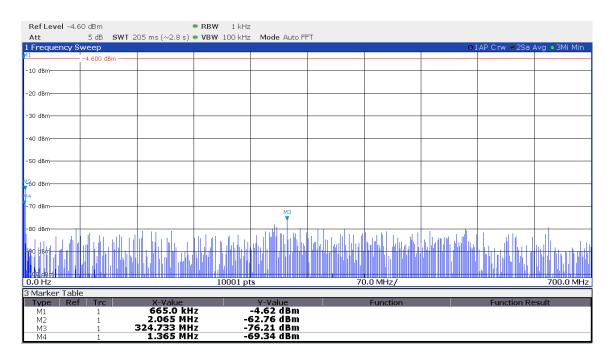

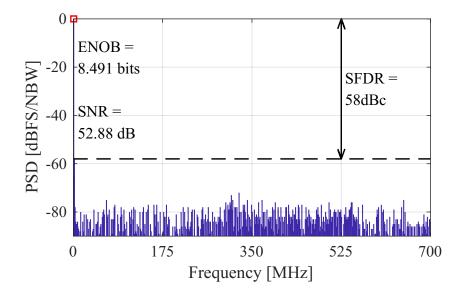

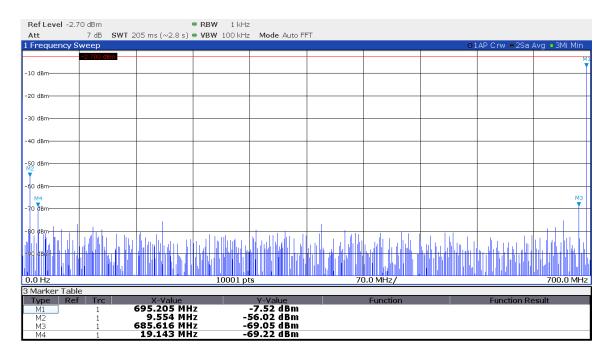

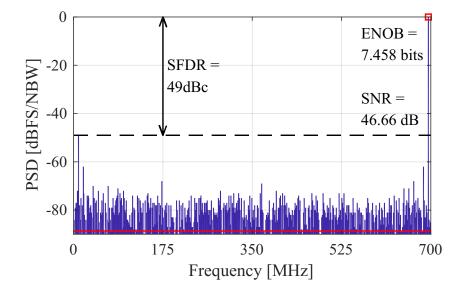

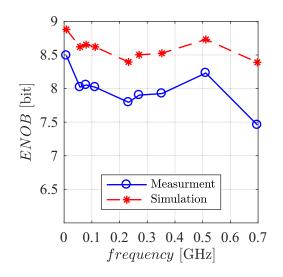

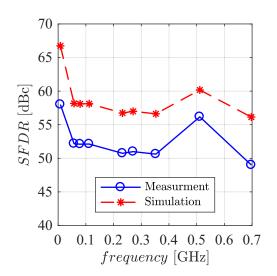

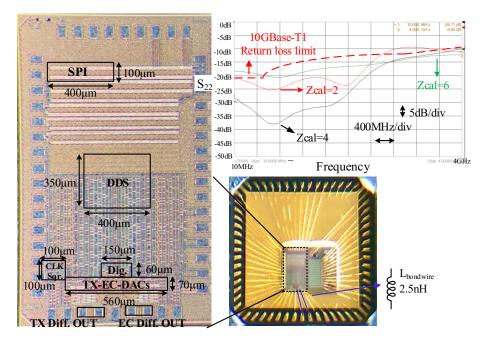

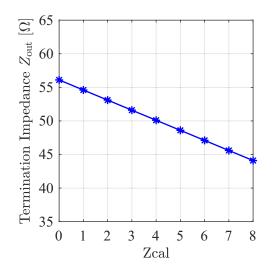

Figure 3.21: Single ended termination impedance of the differential output (a) and the DNL error (b) across digital input code with  $r_{\rm RM} = 6$ ,.