# High-Performance Transceiver Front-Ends in SiGe Technologies for 400 Gb/s Optical Links

vorgelegt von M.Sc. Iria García López

von der Fakultät IV - Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

> Doktor der Ingenieurwissenschaften -Dr.-Ing.-

> > genehmigte Dissertation

Promotionsausschuss: Vorsitzender: Prof. Dr.-Ing. Lars Zimmermann Gutachter: Prof. Dr.-Ing. habil. Dietmar Kissinger Gutachter: Prof. Dr.-Ing. Ahmet Cagri Ulusoy Gutachter: Prof. Dr.-Ing. Friedel Gerfers Tag der wissenschaftlichen Aussprache: 11. April 2019

Berlin 2019

I lovingly dedicate this thesis to my parents, Luis and Marisa, who with their own efforts and sacrifices, have allowed me to reach this far.

Con todo mi cariño, dedico esta tesis a mis padres, Luis y Marisa, que con su esfuerzo y sacrificio me han permitido llegar hasta aquí.

•

# Acknowledgements

The accomplishment of this thesis brings the conclusion to one very important section of my life during which I have experienced tremendous growth, both at a professional and at a (more important) personal level. I heartly wish to acknowledge several remarkable individuals who have contributed to my reaching this point.

I would like to express my most sincere gratitude to my supervisor, Prof. Dietmar Kissinger, who has been an essential reference figure for me during this time. He has provided me the support and motivation necessary to stay on track in this long road and has helped me channeling my efforts by defining clear goals and priorities. He has given me complete freedom to pursue various ideas without objection and has always encouraged me to aim high. I heartly wish to thank him for believing in me and my potential possibly more than I do myself, and for always keep creating opportunities for me to expand professionally.

My most sincere appreciation goes also to my second advisor Prof. Cagri Ulusoy for his mentoring and guidance, which has helped me to shape the majority of this thesis. His knowledge and his vision have challenged me to think more deeply, and his genuine enthusiasm and optimism for what we do have encouraged me to reach more broadly. 2015 has been my most productive year ever! From Cagri I learnt the right way of working in terms of fairness, accuracy and responsibility which has made me a better scientist. I feel very fortunate for having worked with him.

I would also like to thank Prof. Dr.-Ing. Friedel Gerfers for agreeing to review this thesis, and for providing insightful comments and recommendations.

My BIG, most heartfelt thanks go to (now, Dr.!) Pedro Rito, with whom I had the luck to start in parallel the IHP journey. I wouldn't have made it this far without him. His knowledge, his generosity and commitment to work and to helping others have been amazing to witness. It would be *spatially* impossible to recall all the ways in which he has helped me throughout this time; he has been my primary resource for solving my electronics questions and his friendship out of office has been essential to making this period very enriching and joyful. I feel tremendously blessed for having shared this long PhD journey with you! Your brilliance, open-mindedness, dedication and kindness are overwhelming! I look forward to seeing how far you'll reach!

I wish to thank Dr. Daniel Micusik for hiring me in the first place!! Daniel was my first supervisor and put his trust on me when it must have been very difficult to do so... I heartly wish to thank him for his faith in my learning curve. Daniel brought to Pedro and I a workmethodology that has proven extremely useful, and we absorbed much from him in those first two years. I value especially the working-ethics, integrity and enthusiasm that he always transmitted to us. With his deep knowledge and charisma he has inspired me to continue this path. I must extend my acknowledgment to Prof. Lars Zimmermann and to the Photonics department, for creating an exceptional collaborative environment, and to all the colleagues in the Circuit Design department for sharing their wisdom, knowledge and experience. Thank you also to Manja, who made all the administrative work so easy.

Crossing paths with Subhajit has been the biggest gift that the PhD time has brought to me, for which I am inmensely grateful. His friendship has become a pillar in all these years, and his advice and continuous support in so many levels have been central in the completion of this thesis (and, actually, in my life endeavours). He has closely witnessed my ups and downs and has shown a natural talent for dealing with them, helping me to keep things in perspective. Every single page of this thesis has gone under his eyes :) Subhajit, thank you for being so present! You are beyond amazing and I am forever grateful.

Rahul, thank you for your friendship! you have been responsible for a significant part of my happiness (and wild laughter) in Frankfurt (Oder)! Miljana, I loved our long chats! and thank you, of course, to my friends at home, Vanessa and Silvia, for making things stay the same, despite the distance.

Finalmente ... con todo mi corazón, quiero agradecer a mis padres su apoyo incondicional, aliento e inspiración, y el haberme dado la oportunidad de perseguir mis sueños y aspiraciones profesionales. Gracias por entender la distancia, por ser tan *avanzados* en tantos aspectos y por animarme siempre cuando me cansa el camino. Gracias por las conversaciones diarias! y por creer en mi: es por vosotros que soy lo que soy. Gracias a mi hermano, por estar ahí cuando yo estoy lejos. Gracias a mi abuela, mi eterna admiradora! Y a mis abuelos, os recuerdo; sé que estaríais orgullosos de mi. Gracias, GRACIAS, por vuestro amor inmenso! No puedo expresar con palabras cuánto significa para mi.

It seems about time to close this life chapter. IHP has given me all the great opportunities that a PhD student should have and opened up incredible paths ahead of me. Cherishing all my experiences in the past years, I look forward to move onto the new journey!

Frankfurt (Oder), September 2018.

#### Zusammenfassung

Die optische Glasfaserkommunikation ist ein wichtiger Bestandteil in der heutigen industriellen Entwicklung und des wirtschaftlichen Fortschrittes in unserer modernen Gesellschaft geworden. Um die Anforderungen des zunehmenden Datenverkehrs zu erfüllen, die für Anwendungen wie das Internet der Dinge (IoT) und Cloud-Computing benötigt werden, müssen die Bandbreite, die Leistungsaufnahme und die Baugrö $\beta$ e solcher Systeme weiter skaliert werden. Für die nächste 400 Gb/s Generation und nachfolgende optische 1 Tb/s Transponder sind elektronische Frontends als Schnittstelle zu den optischen Übertragungselementen ein untrennbarer Bestandteil, der die Gesamtsystemleistung entscheidend beeinflusst. Die vorliegende Arbeit untersucht neuartige Schaltungskonzepte und Methoden mit dem Ziel der Verbesserung verschiedener Leistungsparameter wie Datenrate, Energieverbrauch und Eigenrauschen von elektronischen Breitbandschaltungen in optischen Transceivern. Als Ergebnis präsentiert diese Arbeit mehrere integrierte Schaltungen in verschiedenen Knoten einer modernen SiGe:C BiCMOS Technologie die den Stand der Technik signifikant verbessern.

Auf der Senderseite (Transmitter, Tx) wird der traditionelle, aber leistungshungrige, Ansatz zur Erzeugung höherwertiger Modulationsformate mit Hilfe von linearen Treibern in Kombination mit einem externen Digital-zu-Analog-Umsetzer (DAC) aufgegriffen und durch die Einführung eines energieeffizienten Tx-Moduls mit integrierter 4-b DAC-Funktionalität deutlich verbessert. Dabei werden zwei Integrationskonzepte untersucht: Ein hybrides Konzept, in dem ein I/Q InP Mach-Zehnder-Modulator (MZM) zusammen mit einem SiGe BiCMOS Treiber integriert wird, welches eine 256-Quadratur-Amplituden-Modulation (QAM) mit einer Symbolrate von bis zu 32 GBd ermöglicht, die in einem Rekord-Energieverbrauchpro-Bit von lediglich 6.4 pJ/bit resultiert, und ein monolithisch integrierter elektronischphotonischer Transmitter, der für den Betrieb einer 4-Level Pulse-Amplituden-Modulation (PAM-4) bis 37 GBd geeignet ist, der bisher höchsten Symbolrate unter Verwendung von Silizium-Photonik-Modulatoren. Die Hybridlösung findet dabei Anwendung bei den klassischen Telekommunikationsreichweiten, während der monolithisch integrierte Tx eine kostengünstige Lösung für Applikationen mit kurzer Reichweite wie Datenzentren bietet. Erfolgreiche elektrooptische (E/O) Messungen wurden für beide Prototypen durchgeführt.

Auf der Empfängerseite (Receiver, Rx) liegt der Schwerpunkt der Arbeit auf der Untersuchung besonders rauscharmer linearer Transimpedanzverstärker (TIA) mit einer hohen Bandbreite. Dabei wird eine rauscharme Designmethodik vorgestellt und darauf basierend TIA-Implementierungen mit weniger als  $10 \text{ pA}/\sqrt{Hz}$  mittlerer eingangsbezogener Rauschleistungsdichte bei einer Datenrate von 100 Gb/s aufgezeigt. Mittels der vorgeschlagenen Vorgehensweise werden darüber hinaus innovative Rx-Konzepte für energieeffiziente Module präsentiert: Ein Benchmark-TIA, der eine Bandbreite von 60 GHz mit weniger als  $5.5 \text{ pA}/\sqrt{Hz}$  Rauschleistungsdichte erreicht, und eine spezifische Lösung für ein PAM-4 Rx-Frontend mit einem integrierten Flash-Analog-Digital-Umsetzer (ADC), der PAM-4 Signale mit einer Datenrate von bis 100 Gb/s demodulieren kann. Zuletzt wird erstmals ein TIA in einer Folded-Kaskode-Architektur unter Zuhilfenahme von bipolaren pnp-Transistoren vorgestellt, um die Vorteile einer komplementären Technologie in energieeffizienten Hochgeschwindigkeits-Empfänger-Frontends zu demonstrieren.

#### Abstract

Optical fiber communication has become the key enabler of today's industrial development, economic progress and modern society. In order to support the increasing data traffic demands required for applications such as the Internet-of-Things (IoT) and Cloud Computing, the bandwidth, power consumption and space density of current systems all need to scale further. For the next generation 400 Gb/s and soon also 1 Tb/s optical transponders, the electronic front-ends that are directly interfacing the photonic devices, are an integral part and strongly influence the overall system performance. This thesis investigates circuit-level methods for enhancing different performance metrics such as high data rate, low power consumption and low noise in various broadband circuits for optical transceivers. Several contributions to the state-of-the-art in such integrated circuits (ICs) are proposed and implemented in different nodes of a modern SiGe:C BiCMOS technology platform.

On the transmitter (Tx) side, the traditional but power-hungry approach used for generating high-order modulation formats based on linear driver amplifiers together with an external digital-to-analog converter (DAC) is revisited. Here, the implementation of energy-efficient Tx modules featuring integrated 4-b DAC functionality is presented. Two integration concepts are explored: a hybrid one, which incorportates an I/Q InP Mach-Zehnder modulator (MZM) together with a SiGe BiCMOS driver demonstrating up to 32 GBd 256-quadrature-amplitude-modulation (QAM) signal modulation with record low energy-per-bit of 6.4 pJ/bit and a monolithically integrated photonics Tx capable of up to 37 GBd pulse-amplitude-modulation (PAM)-4 operation, which is the highest among silicon-photonics (SiPh) modulators. The hybrid solution targets telecom reach, while the monolithically integrated Tx provides a low-cost solution for short range applications. Electro-optical (E/O) measurement results are available for both prototypes.

On the receiver (Rx) side, the focus lies on the development of low noise, high-bandwidth linear transimpedance amplifiers (TIAs). A low noise design methodology is described, and TIA implementations featuring less than  $10 \text{ pA}/\sqrt{Hz}$  averaged input referred current noise density while operating at 100 Gb/s data rate are demonstrated. Based on the proposed design methodology, supplementary advanced Rx concepts towards power-efficient modules are presented: a benchmarking TIA which achieves 60 GHz bandwidth with  $<5.5 \text{ pA}/\sqrt{Hz}$  and a custom solution for a PAM-4 Rx front-end integrating a 2-bit flash analog-to-digital-converter (ADC) capable of demodulating signals at up to 100 Gb/s data rate. Finally, a TIA in folded-cascode architecture which makes use of pnp transistors in order to explore the benefits of a complementary technology in power-efficient high-speed Rx front-ends is also described.

# **Table of Contents**

| Zι            | ısam  | nenfassung v                                         | ii |  |  |  |  |  |

|---------------|-------|------------------------------------------------------|----|--|--|--|--|--|

| A             | bstra | it                                                   | x  |  |  |  |  |  |

| $\mathbf{Li}$ | st of | Figures xi                                           | ii |  |  |  |  |  |

| $\mathbf{Li}$ | st of | Tables xv                                            | ii |  |  |  |  |  |

| 1             | Intr  | oduction                                             | 1  |  |  |  |  |  |

|               | 1.1   | The Zettabyte era: Trends and perspective            | 1  |  |  |  |  |  |

|               | 1.2   | Topography of optical fiber networks                 | 2  |  |  |  |  |  |

|               | 1.3   | Optical transceivers overview                        | 4  |  |  |  |  |  |

|               | 1.4   | Scope and organization of the thesis                 | 5  |  |  |  |  |  |

| <b>2</b>      | Opt   | cal Transceivers Fundamentals                        | 7  |  |  |  |  |  |

|               | 2.1   | Electro-optical devices                              | 7  |  |  |  |  |  |

|               |       | 2.1.1 Photodetector                                  | 7  |  |  |  |  |  |

|               |       | 2.1.2 Optical modulator                              | 9  |  |  |  |  |  |

|               | 2.2   | Mach-Zehnder modulator                               | 9  |  |  |  |  |  |

|               |       | 2.2.1 MZM driving: electrode configurations          | .1 |  |  |  |  |  |

|               |       | 2.2.2 High-order modulation formats generation       | 3  |  |  |  |  |  |

|               | 2.3   | Photonics and electronics integration schemes        | 5  |  |  |  |  |  |

|               | 2.4   | Technology platform                                  |    |  |  |  |  |  |

|               | 2.5   | Circuit design considerations                        | 9  |  |  |  |  |  |

|               |       | 2.5.1 Broadband circuit design                       | 9  |  |  |  |  |  |

|               |       | 2.5.2 High-speed design techniques                   | 21 |  |  |  |  |  |

| 3             | Tra   | asmitter Modules with Integrated DAC Functionality 2 | 7  |  |  |  |  |  |

|               | 3.1   | Introduction                                         | 27 |  |  |  |  |  |

|               | 3.2   | Hybrid I/Q Tx module with InP SEMZM 2                | 9  |  |  |  |  |  |

|               |       | 3.2.1 Package characteristics                        | 0  |  |  |  |  |  |

|               |       | 3.2.2 InP SEMZM: electrical modeling 33              | 81 |  |  |  |  |  |

|               |       | 3.2.3 Segmentation and hybrid integration impact     | 2  |  |  |  |  |  |

|               |       | 3.2.4 Driver design and stand-alone performance      | 6  |  |  |  |  |  |

|               |       | 3.2.5 Functionality verification                     | 2  |  |  |  |  |  |

|               | 3.3   | Monolithically integrated Tx module with SiPh SEMZM  | 7  |  |  |  |  |  |

|          |         | 3.3.1 SiPh Mach-Zehnder modulator                                | 47  |  |  |

|----------|---------|------------------------------------------------------------------|-----|--|--|

|          |         | 3.3.1.1 Si SEMZM: electrical modeling                            | 48  |  |  |

|          |         | 3.3.1.2 $E/O$ co-simulation                                      | 49  |  |  |

|          |         | 3.3.2 Tx module implementation                                   | 49  |  |  |

|          |         | 3.3.3 Functionality verification                                 | 52  |  |  |

|          | 3.4     | Comparison with state-of-the-art                                 | 53  |  |  |

|          | 3.5     | Summary                                                          | 53  |  |  |

| 4        | Low     | v-Noise Differential Receiver Front-Ends                         | 55  |  |  |

|          | 4.1     | Introduction                                                     | 55  |  |  |

|          | 4.2     | Low-noise design methodology                                     | 56  |  |  |

|          |         | 4.2.1 Noise sources                                              | 56  |  |  |

|          |         | 4.2.2 Circuit techniques                                         | 57  |  |  |

|          |         | 4.2.3 Technology role                                            | 61  |  |  |

|          | 4.3     | Transimpedance amplifiers with sub-10pA/ $\sqrt{Hz}$ at 100 Gb/s | 61  |  |  |

|          |         | 4.3.1 Circuit implementation                                     | 61  |  |  |

|          |         | 4.3.2 Functionality verification                                 | 68  |  |  |

|          | 4.4     | Comparison with state-of-the-art                                 | 75  |  |  |

|          | 4.5     | Summary                                                          | 75  |  |  |

| <b>5</b> | Adv     | vanced Receiver Architectures for Power Efficient Modules        | 77  |  |  |

|          | 5.1     | Introduction                                                     | 77  |  |  |

|          | 5.2     | Benchmarking TIA with less than 5.5 $pA/\sqrt{Hz}$               | 81  |  |  |

|          |         | 5.2.1 Circuit implementation                                     | 81  |  |  |

|          |         | 5.2.2 Functionality verification                                 | 82  |  |  |

|          | 5.3     | $100\mathrm{Gb/s}$ PAM-4 Rx front-end                            | 84  |  |  |

|          |         | 5.3.1 Circuit implementation                                     | 85  |  |  |

|          |         | 5.3.2 2-bit flash ADC                                            | 85  |  |  |

|          |         | 5.3.3 Functionality verification                                 | 89  |  |  |

|          | 5.4     | Folded cascode TIA using pnp HBTs                                | 91  |  |  |

|          |         | 5.4.1 Circuit implementation                                     | 92  |  |  |

|          |         | 5.4.2 Functionality verification                                 | 94  |  |  |

|          | 5.5     | Summary                                                          | 96  |  |  |

| 6        | Con     | aclusions                                                        | 99  |  |  |

| Re       | efere   | nces 1                                                           | .01 |  |  |

| Li       | st of   | Publications 1                                                   | 11  |  |  |

|          | crony   |                                                                  |     |  |  |

| A        | on only | onyms 115                                                        |     |  |  |

# **List of Figures**

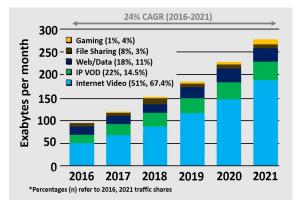

| 1.1  | Cisco forecast for global IP traffic growth from 2016 to 2021 [6]                                                                                       | 2  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----|

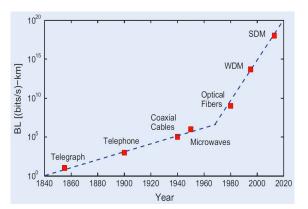

| 1.2  | Historical increase in the B·L product with new technologies [2].                                                                                       | 2  |

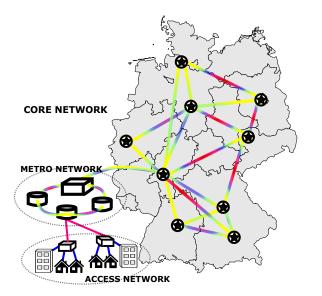

| 1.3  | Architecture of optical networks in Germany. Adapted from [7]                                                                                           | 3  |

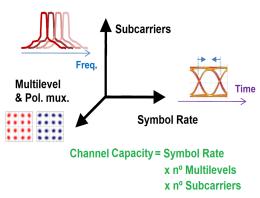

| 1.4  | Dimensions for increasing channel capacity. Adapted from [9]                                                                                            | 3  |

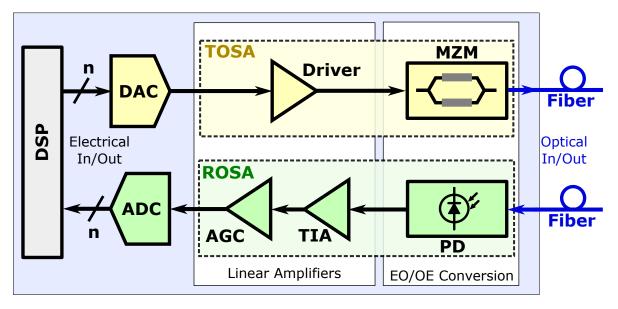

| 1.5  | Simplified block diagram of a DSP-based optical transceiver.                                                                                            | 4  |

| 2.1  | (a) Vertically illuminated p-i-n photodetector cross-section, (b) corresponding                                                                         |    |

|      | electrical equivalent and (c) waveguide p-i-n photodetector [14]                                                                                        | 8  |

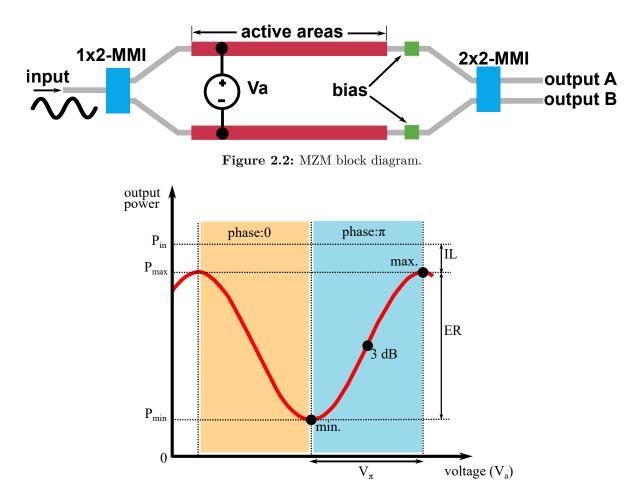

| 2.2  | MZM block diagram.                                                                                                                                      | 10 |

| 2.3  | MZM power transfer function and most common bias points. Depending on the selected modulation format, the modulator is biased in either the 3 dB or the |    |

|      | min. point.                                                                                                                                             | 10 |

| 2.4  | MZM driving schemes: (a) lumped electrode, (b) TWE and (c) segmented                                                                                    |    |

|      | Mach-Zehnder modulator (SEMZM)                                                                                                                          | 12 |

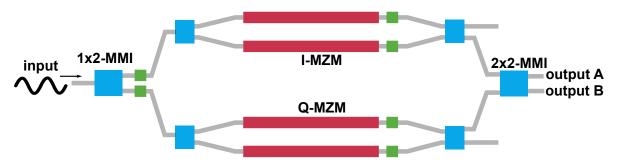

| 2.5  | IQ-MZM block diagram.                                                                                                                                   | 13 |

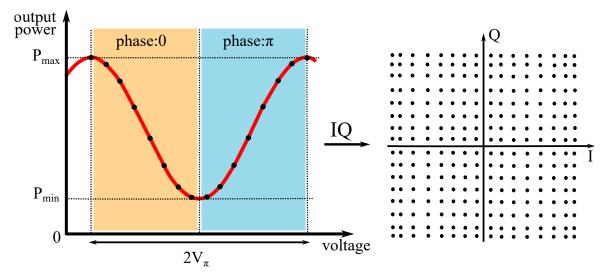

| 2.6  | Generation of 256-QAM with I/Q-MZM. Adapted from [30]                                                                                                   | 14 |

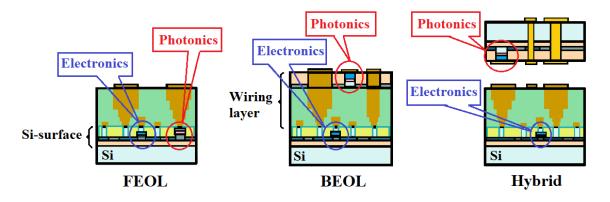

| 2.7  | Schematic cross sections of integration between photonic and electronic circuits.                                                                       |    |

|      | Adapted from [33]                                                                                                                                       | 15 |

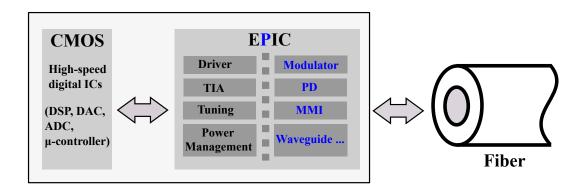

| 2.8  | Multi-chip solution for optical communications link with EPIC [34]                                                                                      | 16 |

| 2.9  | Comparison between BiCMOS and CMOS technologies with respect to RF                                                                                      |    |

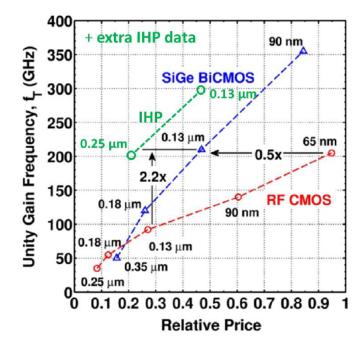

|      | performance vs. cost [36]. $\ldots$                                    | 17 |

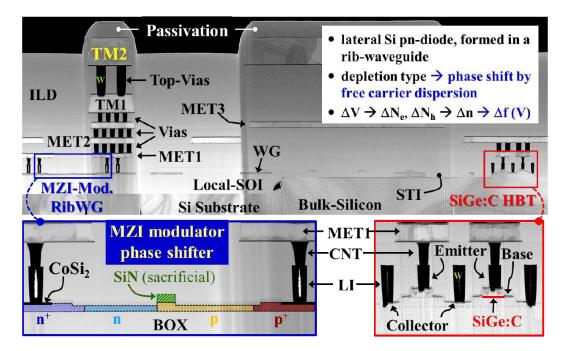

| 2.10 | Photonic BiCMOS cross-sections illustrating monolithically integrated trans-                                                                            |    |

|      | mitter components: Phase-shifter of a Mach-Zehnder interference modulator on                                                                            |    |

|      | SOI and a SiGe HBT fabricated in an adjacent bulk region [34]                                                                                           | 18 |

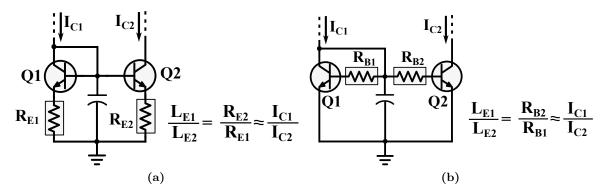

| 2.11 | Biasing scheme with current mirrors: (a) with emitter degeneration resistors                                                                            |    |

|      | and (b) with base resistors.                                                                                                                            | 20 |

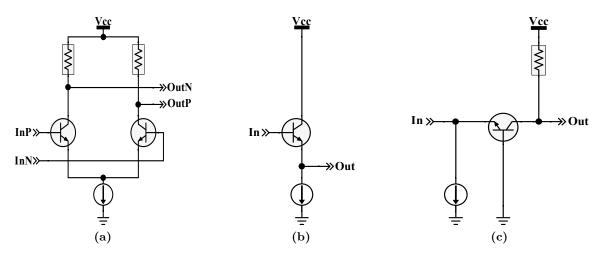

| 2.12 | Basic transistors stages: (a) differential pair, (b) common-collector stage and                                                                         |    |

|      | (c) common-base stage                                                                                                                                   | 21 |

| 2.13 | Series feedback implementation: (a) typical common-emitter stage, (b) common-                                                                           |    |

|      | emitter stage with resistive degeneration, (c) common-emitter stage with                                                                                |    |

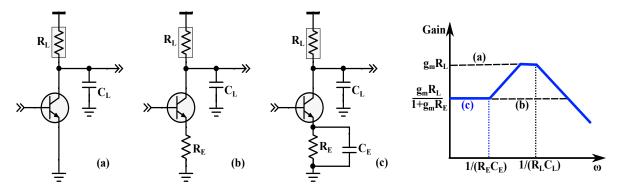

|      | resistive-capacitive degeneration, (d) transfer function                                                                                                | 22 |

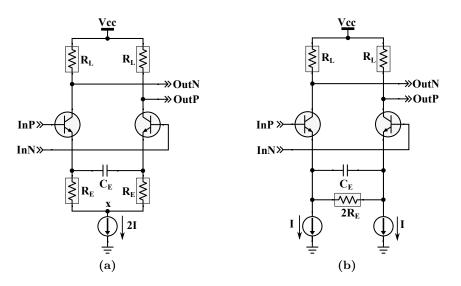

| 2.14 | Capacitive emitter degeneration implementation in a differential pair: (a) in                                                                           |    |

|      | series and (b) parallel configuration.                                                                                                                  | 22 |

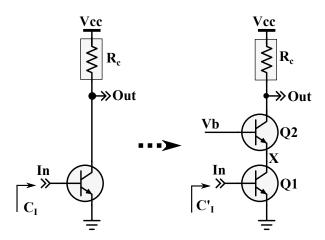

| 2.15 | Common-emitter stage with cascode transistors [50]                                                                                                      | 23 |

## LIST OF FIGURES

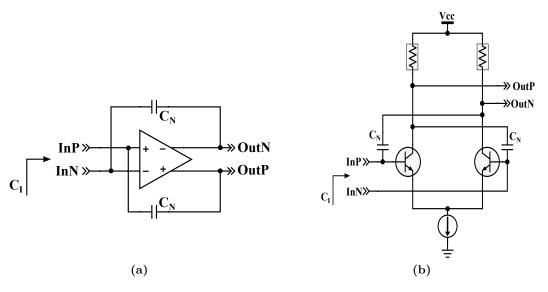

| 2.16 | Negative Miller capacitance compensation: (a) concept and (b) implementation<br>in differential pair.   | 24 |

|------|---------------------------------------------------------------------------------------------------------|----|

| 2.17 | Different inductive peaking configurations: (a) shunt peaking, (b) series peaking,                      | 24 |

| 2.11 | (c) shunt-series peaking, (d) T-coil peaking and (e) equivalent circuit model                           |    |

|      |                                                                                                         | 25 |

|      |                                                                                                         | _0 |

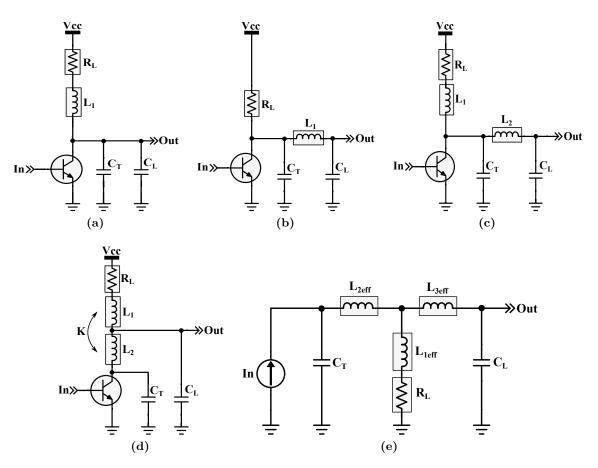

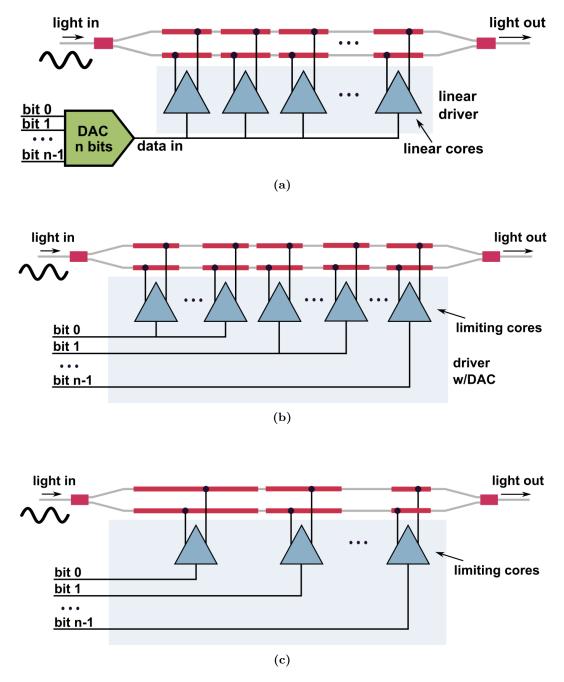

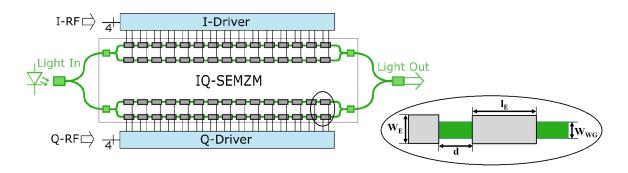

| 3.1  | Transmitter configurations with SEMZMs: (a) linear driving approach, (b)                                |    |

|      | driver with integrated n-bits DAC (c) modulator with thermocode-weighted                                |    |

|      | segmentation.                                                                                           | 28 |

| 3.2  | Simplified block diagram of the Tx module.                                                              | 29 |

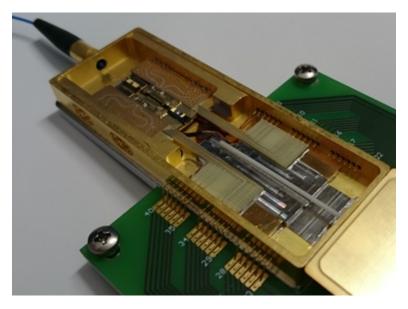

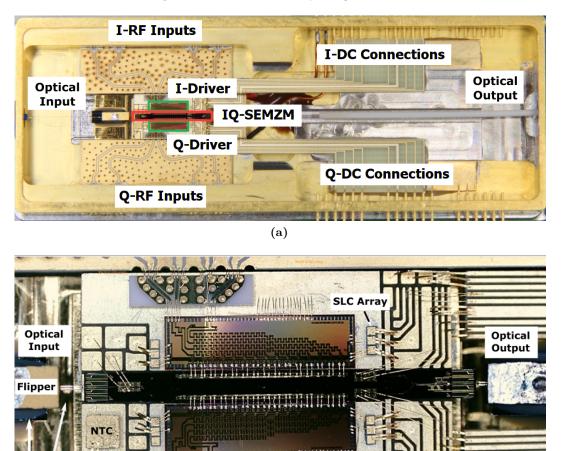

| 3.3  | Picture of the packaged module.                                                                         | 30 |

| 3.4  | (a) Close-up picture of the package with the IQ-SEMZM marked in red and the                             |    |

|      | driver ICs in green. (b) Detailed view of InP IQ-SEMZM and BiCMOS drivers                               |    |

|      | bonding                                                                                                 | 30 |

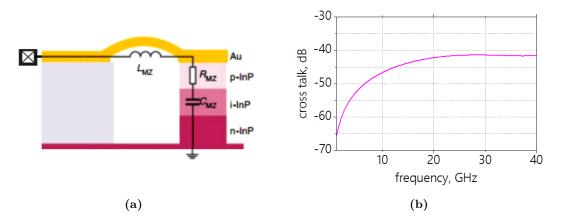

| 3.5  | (a) MZM segment cross section and (b) cross-talk between adjacent segments                              | 32 |

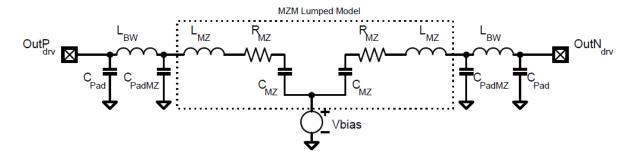

| 3.6  | MZM segment and interconnect electrical model                                                           | 32 |

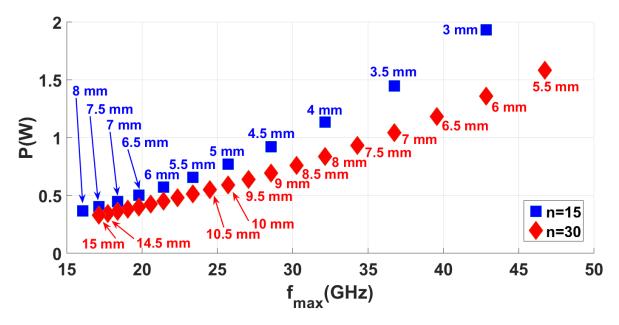

| 3.7  | Dependency between power dissipation (P) and maximum frequency of operation                             |    |

|      | $(f_{max})$ (complying with $\lambda/10$ criteria), with MZM length and number of segments.             | 35 |

| 3.8  | Simplified block diagram of the driver IC                                                               | 36 |

| 3.9  | Michrophotograph of (a) Q and (b) I drivers. $\ldots$                                                   | 37 |

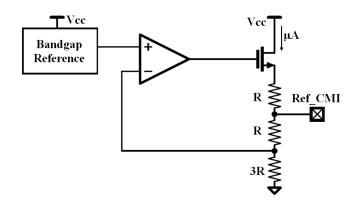

| 3.10 | Generation of Ref_CMI                                                                                   | 37 |

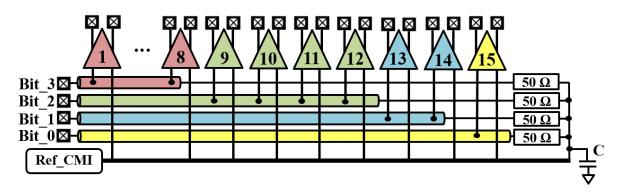

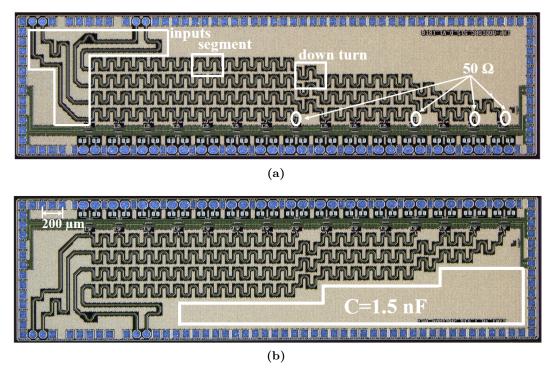

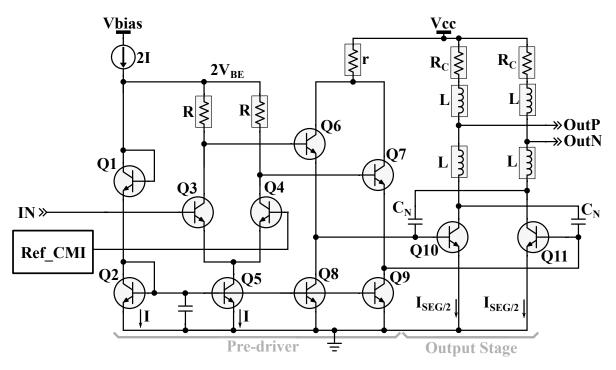

| 3.11 | Driver schematic.                                                                                       | 38 |

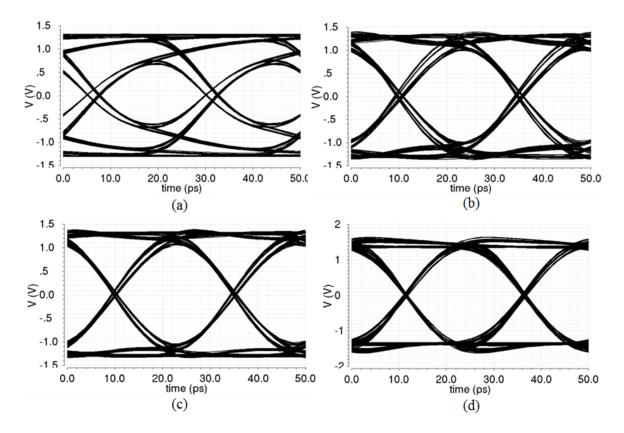

| 3.12 | Simulation results for the eye diagram at $40 \mathrm{Gb/s}$ with (a) no peaking structure,             |    |

|      | (b) bond-wire only, (c) bond-wire together with inductive peaking on-chip, and                          |    |

|      | (d) bond-wire together with inductive peaking and negative capacitance                                  | 39 |

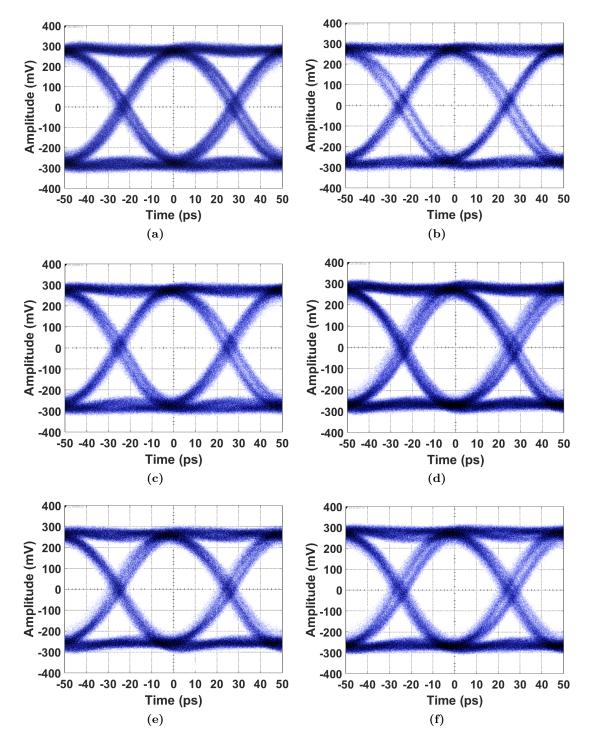

| 3.13 | Eye diagram measurements $@40 \text{ Gb/s}$ from: the I-driver, (a) output 1 (b) output                 |    |

|      | $8,(\mathrm{c})$ output 15 and from the Q-driver, (d) output 1, (e) output 8, (f) output 15.            | 41 |

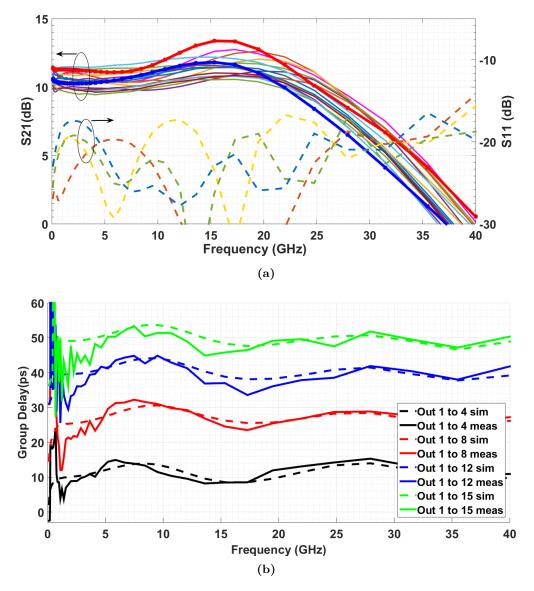

| 3.14 | (a) Measured S11 from all inputs and measured S21 from all outputs vs.                                  |    |

|      | simulated S21 from output 1 (red <sup>*</sup> ) and output 15 (blue <sup>*</sup> ) and (b) measured vs. |    |

|      | simulated group delay                                                                                   | 42 |

| 3.15 | $\rm E/O~S21~SEMZMs$ vs. simulated electrical S21 on last segment only                                  | 43 |

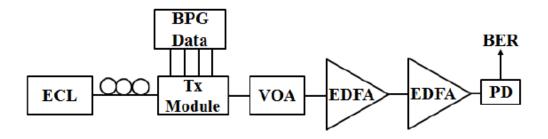

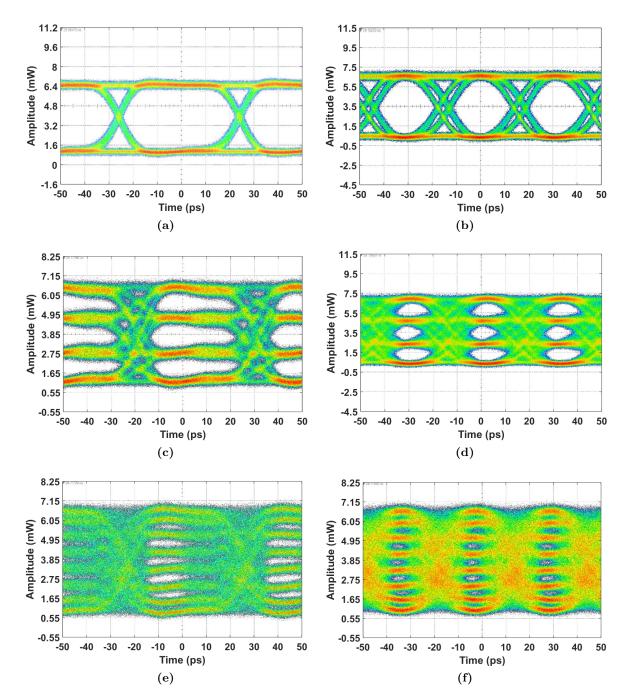

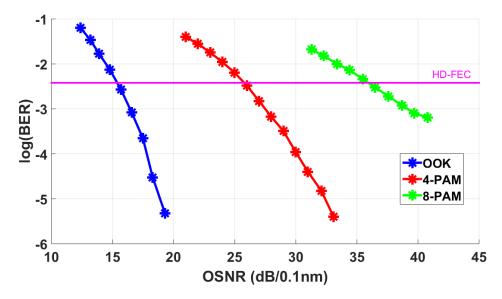

| 3.16 | E/O setup for m-PAM measurements.                                                                       | 43 |

| 3.17 | $\rm E/O$ eye diagrams: (a) OOK @20 GBd, (b) OOK @32 GBd, (c) 4-PAM @20 GBd,                            |    |

|      | (d) 4-PAM @32 GBd, (e) 8-PAM @20 GBd and (f) 8-PAM @32 GBd                                              | 44 |

| 3.18 | BER vs. OSNR curves for the direct detection experiments where a single                                 |    |

|      | SEMZM is driven at $32 \mathrm{GBd}$ .                                                                  | 45 |

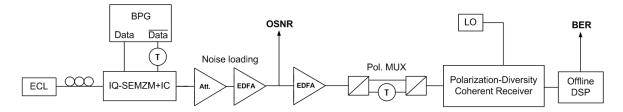

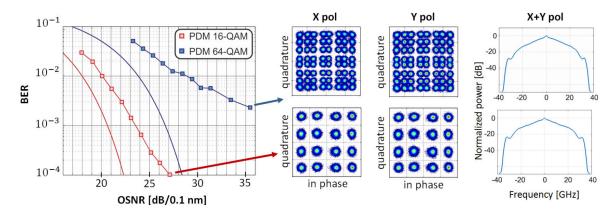

| 3.19 | Experimental setup for the dual-polarization $32\mathrm{GBd}$ m-QAM B2B measurements.                   | 45 |

| 3.20 | BER vs. OSNR curves of the PDM 16-QAM and PDM 64-QAM signals together $$                                |    |

|      | with the theoretical limits, the correspondent IQ constellations at maximum                             |    |

|      | OSNR and the received power spectra after the ADC. Symbols represent                                    |    |

|      | measured BER values and solid lines the theoretical BER in an AWGN channel.                             | 46 |

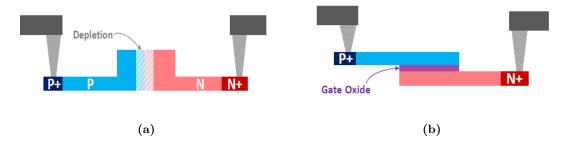

| 3.21 | Cross-section of: (a) depletion-type and (b) accumulation-type phase shifters [73].                     | 47 |

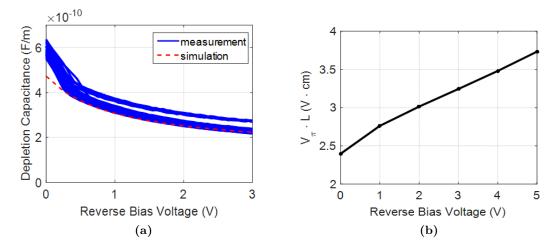

| 3.22 | SiPh MZM segment: (a) cross section, (b) electrical model                                               | 48 |

| 3.23 | (a) Capacitance and (b) efficiency of the modulator with reverse bias voltage                           | 48 |

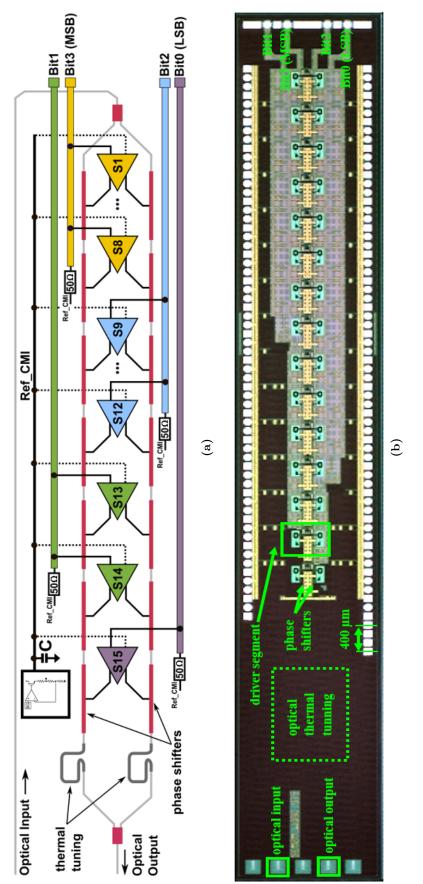

| 3.24 | EPIC Tx with integrated 4-b DAC: (a) block diagram and (b) corresponding                        |            |

|------|-------------------------------------------------------------------------------------------------|------------|

|      | $chip\ microphotograph.\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .\ .$                                 | 50         |

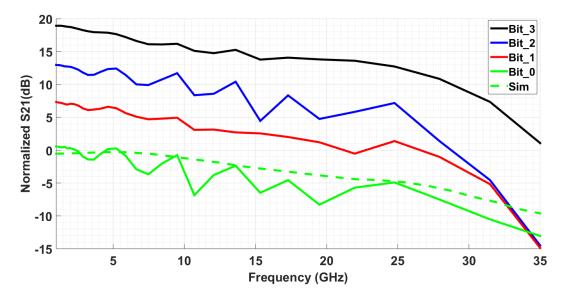

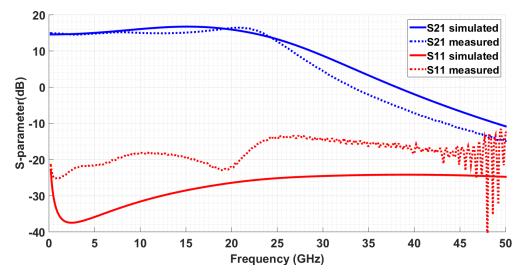

| 3.25 | Measured vs. simulated S-parameters of driver core.                                             | 51         |

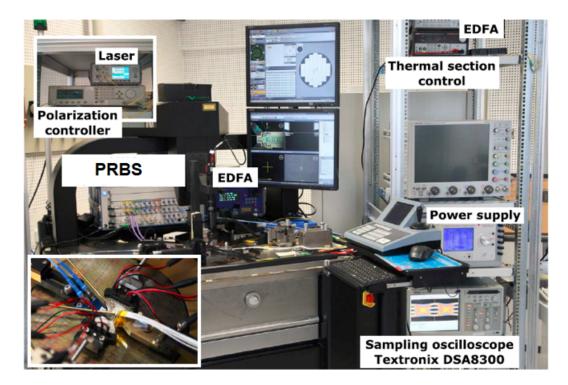

| 3.26 | On-wafer E/O measurements setup. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 51         |

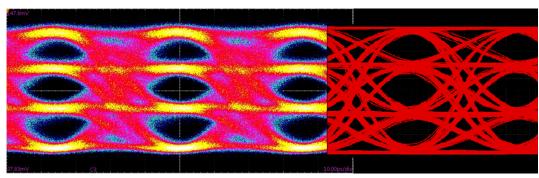

| 3.27 | Measured PRBS31 E/O eye diagrams: (a) at 28 GBd and (b) at 37 GBd, $~$                          |            |

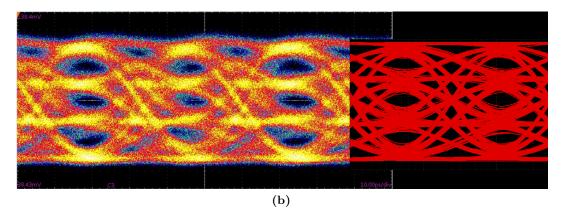

|      | compared to post-layout co-simulation results                                                   | 52         |

| 3.28 | Measured PRBS31 E/O eye diagrams: (a) PAM-8 at 16 GBd and PAM-16 at $$                          |            |

|      | 1 GBd                                                                                           | 53         |

| 4 1  |                                                                                                 |            |

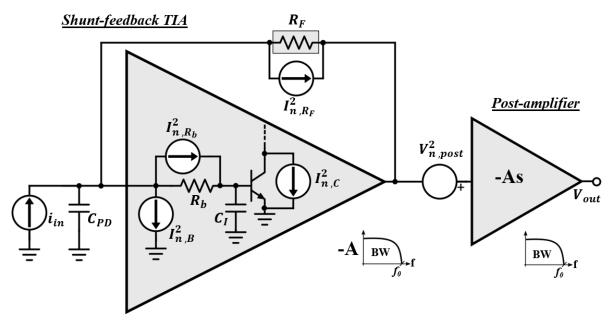

| 4.1  | Front-end of optical receiver in classical cascaded approach comprising bipolar                 | <b>F</b> 0 |

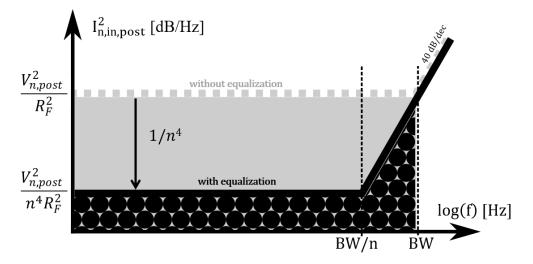

| 4.0  | shunt-feedback TIA stage and post-amplifier.                                                    | 58         |

| 4.2  | Graphic representation of contribution of post-amplifier noise over frequency.                  | 60         |

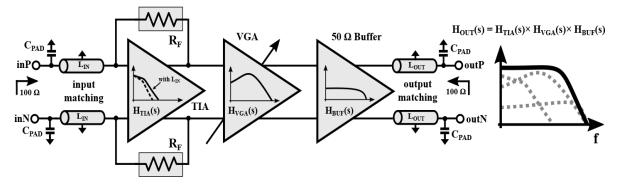

| 4.3  | Block diagram of the TIAs.                                                                      | 61         |

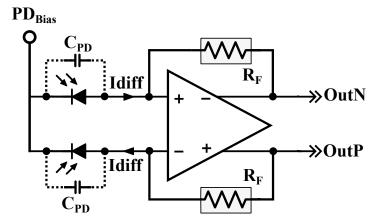

| 4.4  | Rx with balanced inputs.                                                                        | 63         |

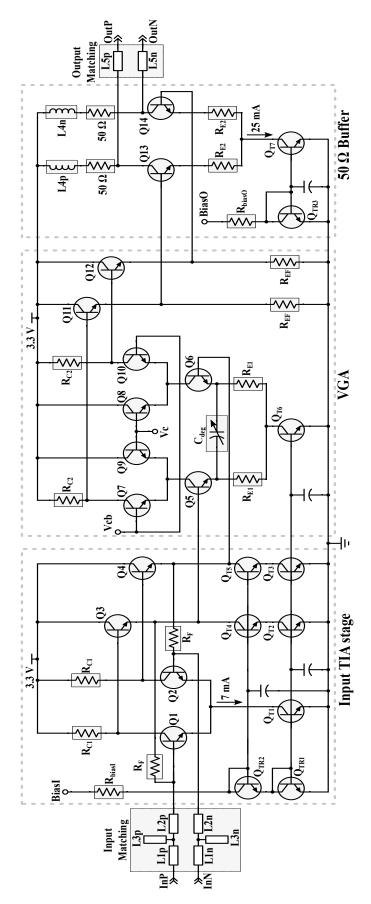

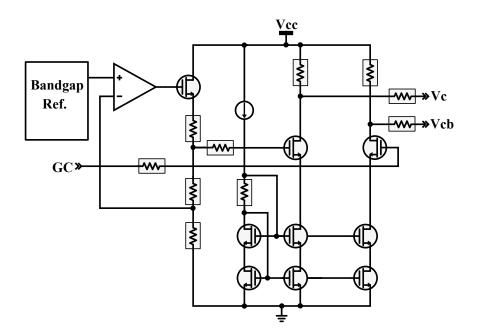

| 4.5  | Schematic of the TIAs                                                                           | 64         |

| 4.6  |                                                                                                 | 65         |

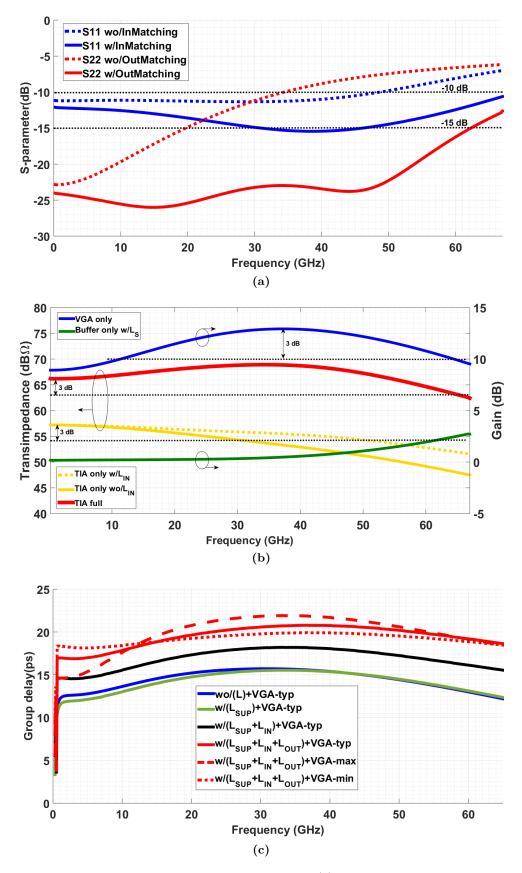

| 4.7  | Post-layout simulation results from G2-TIA: (a) effect of input and output                      |            |

|      | matching structures, (b) gain over frequency for different stages and (c) group                 | 0.0        |

| 4.0  |                                                                                                 | 66         |

| 4.8  | Distribution of the different noise contributions in the integrated input referred              | <b>. -</b> |

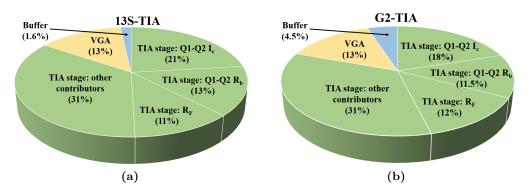

|      | noise: (a) from the 13S-TIA and (b) from G2-TIA                                                 | 67         |

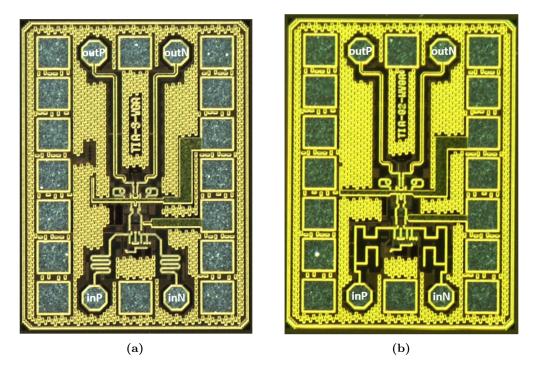

| 4.9  | Chip microphotographs: (a) from 13S-TIA and (b) from G2-TIA                                     | 67         |

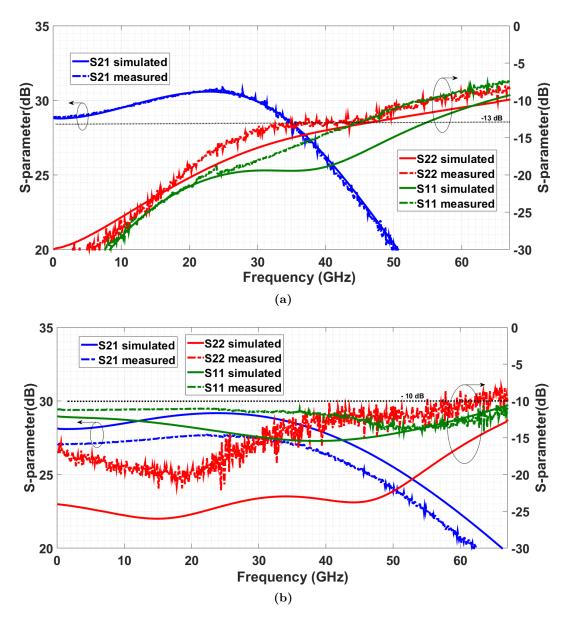

|      | Measured vs. simulated S-parameters: (a) of 13S-TIA and (b) of G2-TIA                           | 68         |

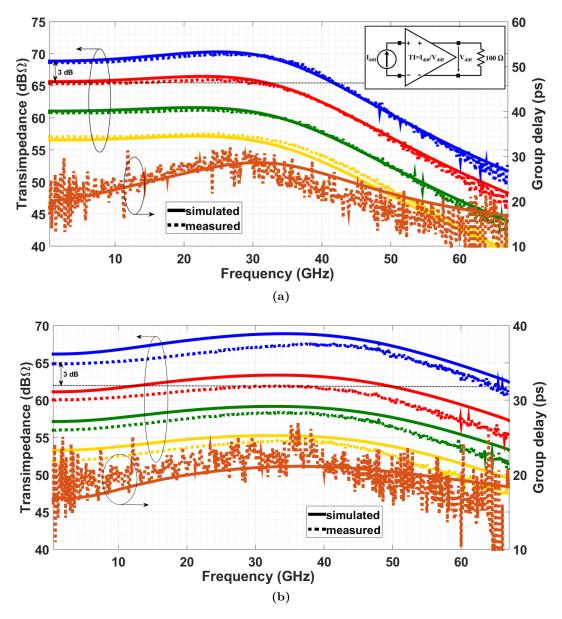

| 4.11 | Measured vs. simulated transimpedance with gain control and group delay: (a)                    |            |

|      |                                                                                                 | 69         |

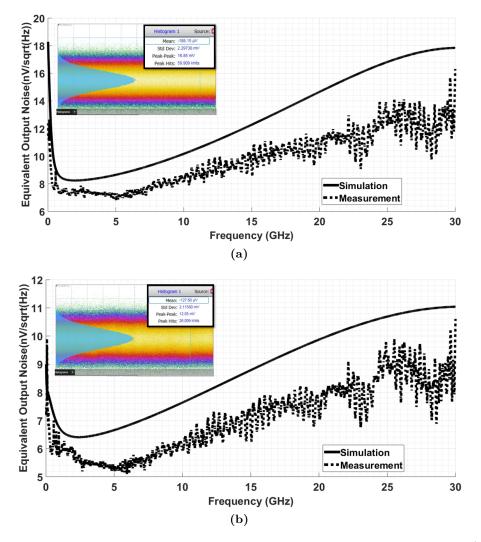

| 4.12 | Measured vs. simulated output-referred noise voltage spectral density: (a) from                 |            |

|      | 13S-TIA and (b) from G2-TIA. Inset in figures displays integrated output noise                  | -          |

| 4.10 | from the histogram function of the oscilloscope                                                 | 70         |

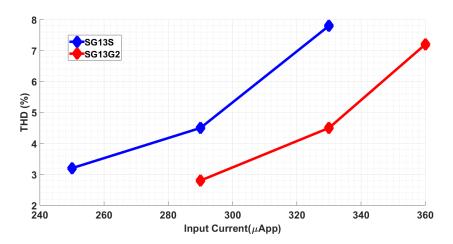

| 4.13 | Measured THD @1 GHz for different input currents in the maximum gain                            |            |

|      | condition.                                                                                      | 71         |

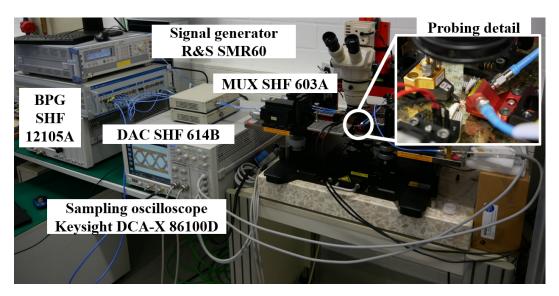

| 4.14 | Time domain measurement setup using 67 GHz components (adaptors, cables,                        |            |

|      | DC-blocks, attenuators).                                                                        | 71         |

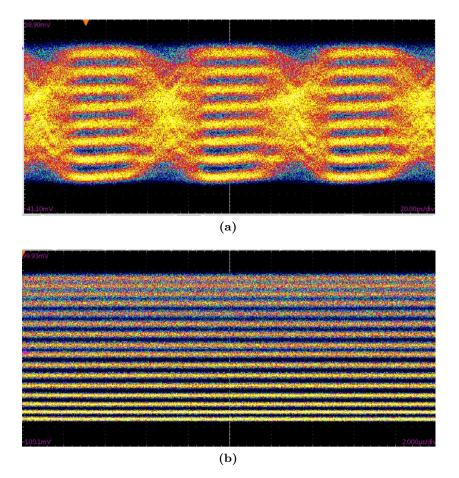

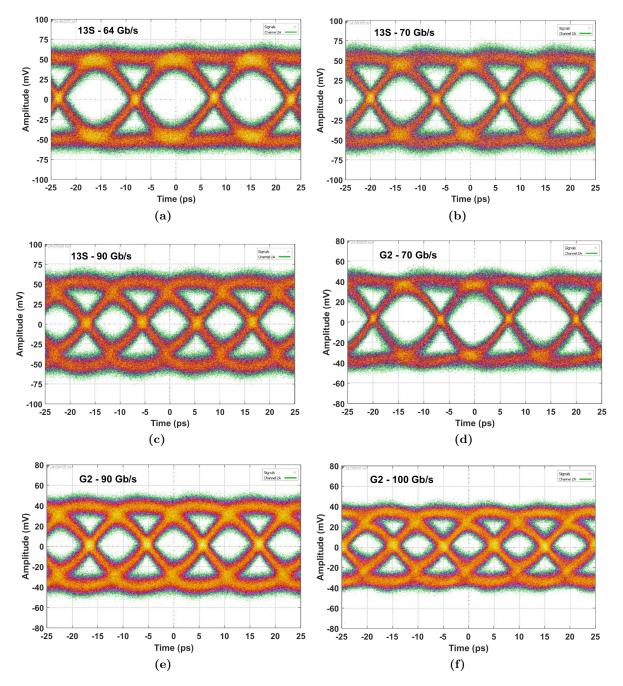

| 4.15 | Time-domain single-ended measurement results @100 $\mu App$ NRZ PRBS31 for                      |            |

|      | 13S-TIA: (a) at 64 Gb/s, (b) at 70 Gb/s and (c) at 90 Gb/s, and for G2-TIA                      | -          |

|      | (d) at 70 Gb/s, (e) at 90 Gb/s and (f) at 100 Gb/s. $\ldots$ $\ldots$ $\ldots$                  | 72         |

| 4.16 | Time-domain single-ended measurement results of PAM-4 PRBS31 for 13S-TIA                        |            |

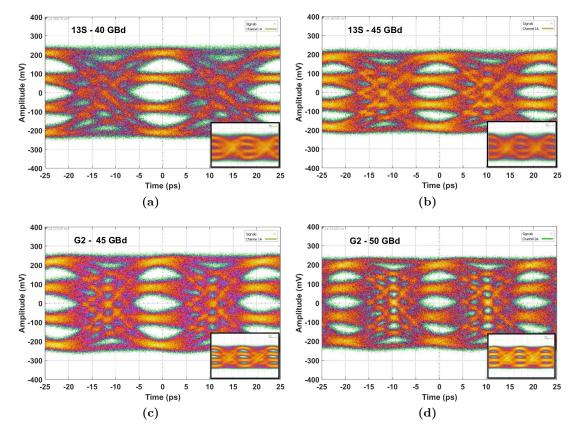

|      | at (a) 40 GBd and (b) 45 GBd and for G2-TIA at (c) 45 GBd and (d) 50 GBd.                       | 73         |

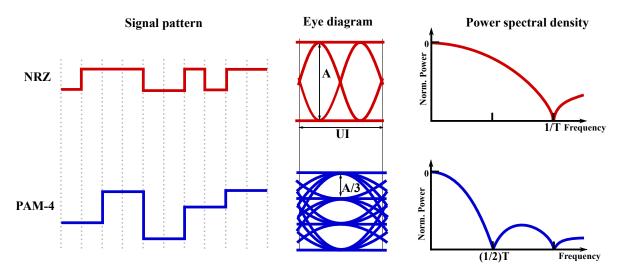

| 5.1  | Schematic representation of NRZ vs. PAM-4 signal patterns, resulting eye                        |            |

|      | diagrams and corresponding power spectral densities                                             | 78         |

| 5.2  | Schematic of the benchmarking TIA                                                               | 79         |

| 5.3  | Chip microphotograph                                                                            | 80         |

| 5.4  | Post-layout simulation results of normalized gain over frequency for different                  | -          |

| -    |                                                                                                 | 80         |

|      | 0                                                                                               | -          |

### LIST OF FIGURES

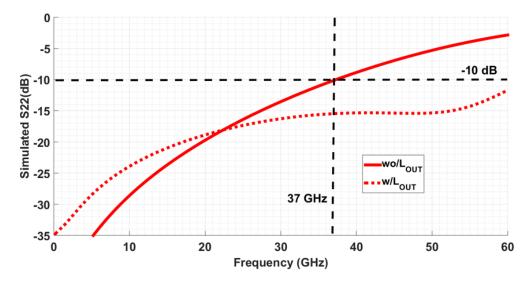

| 5.5                                                                           | Effect of $L_{OUT}$ on the output matching                                                    | 80 |  |  |  |

|-------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|----|--|--|--|

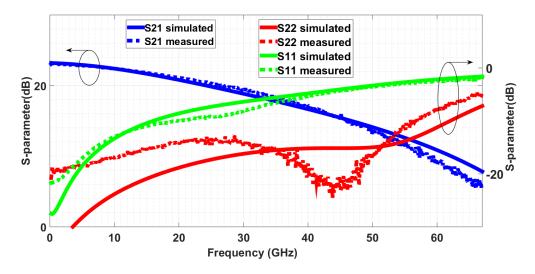

| 5.6                                                                           | S-parameters measured vs. simulated.                                                          |    |  |  |  |

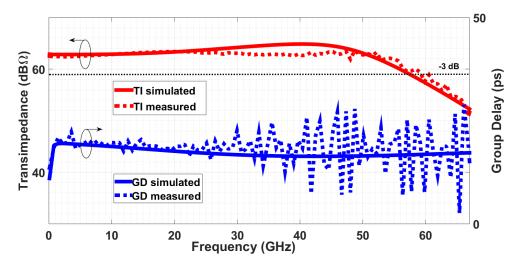

| 5.7                                                                           | 5.7 Transimpedance and group delay measured vs. simulated                                     |    |  |  |  |

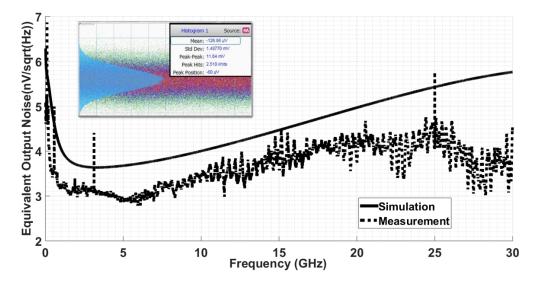

| 5.8 Measured output-referred noise voltage spectral density. Figure inset sho |                                                                                               |    |  |  |  |

| measured integrated output noise from the histogram function of the oscil     |                                                                                               |    |  |  |  |

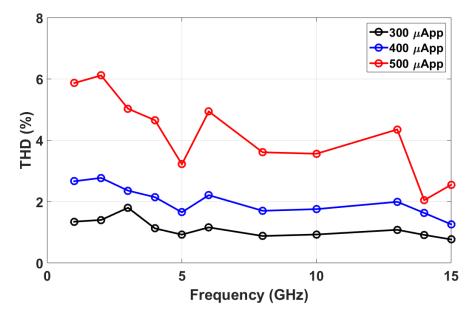

| 5.9                                                                           | 5.9 Measured THD over frequency for different input currents                                  |    |  |  |  |

| 5.10                                                                          | Time domain measurement results of PRBS31 NRZ eye diagrams from single-                       |    |  |  |  |

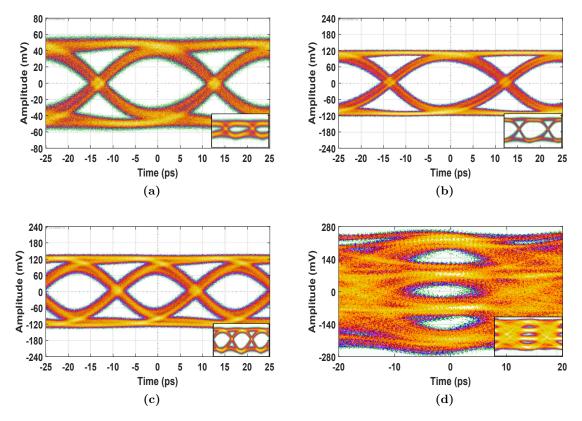

|                                                                               | ended output at (a) 40 Gb/s @170 $\mu \rm{App},$ (b) 40 Gb/s @500 $\mu \rm{App},$ (c) 56 Gb/s |    |  |  |  |

|                                                                               | @500 $\mu \rm App$ and (d) of PRBS7 PAM-4 eye diagram from differential output at             |    |  |  |  |

|                                                                               | 30 GBd @400 $\mu$ App. Insets depict the corresponding input signal                           | 84 |  |  |  |

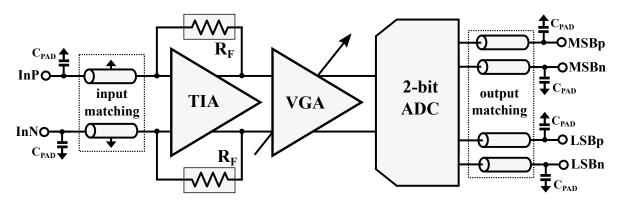

| 5.11                                                                          | Block diagram of the PAM-4 receiver.                                                          | 85 |  |  |  |

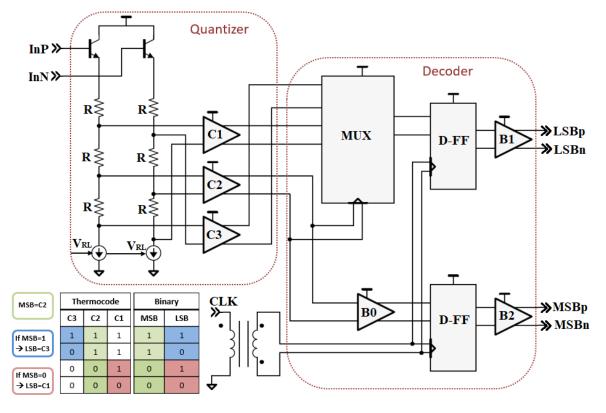

| 5.12                                                                          | Schematic of the 2-bit flash ADC                                                              | 86 |  |  |  |

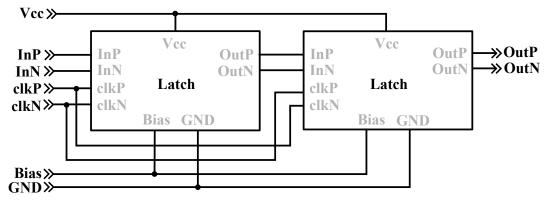

| 5.13                                                                          | Schematic of the 2:1 MUX.                                                                     | 87 |  |  |  |

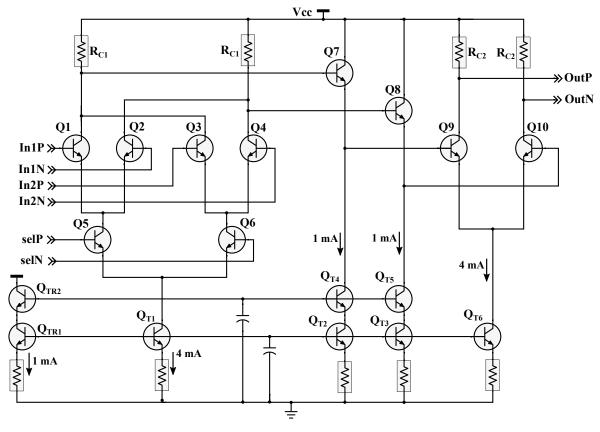

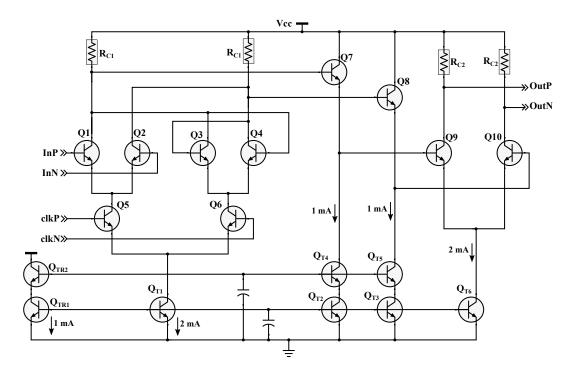

| 5.14                                                                          | 4 Schematic of the D-FF                                                                       |    |  |  |  |

| 5.15                                                                          | Schematic of the latch                                                                        | 88 |  |  |  |

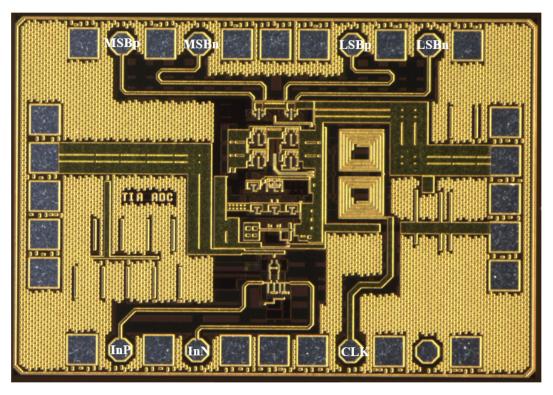

| 5.16                                                                          | Chip microphotograph                                                                          | 88 |  |  |  |

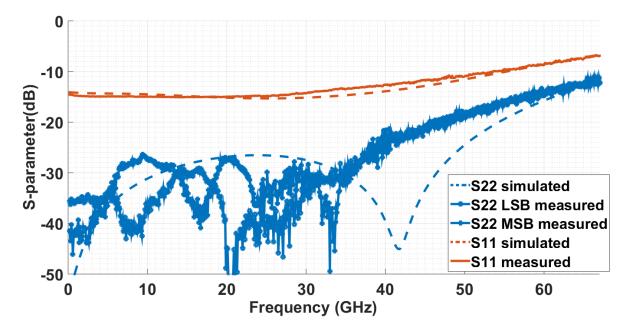

| 5.17                                                                          | 7 S-parameter measurement results vs. simulation from the PAM-4 receiver input                |    |  |  |  |

|                                                                               | and output matching.                                                                          | 89 |  |  |  |

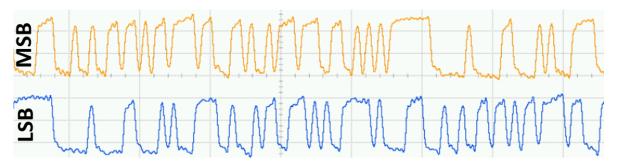

| 5.18                                                                          | MSB and LSB PRBS7 decorrelated patterns at 24 GBd                                             | 89 |  |  |  |

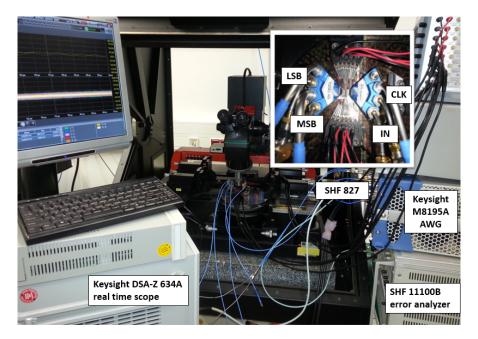

| 5.19                                                                          | Time-domain measurement setup.                                                                | 90 |  |  |  |

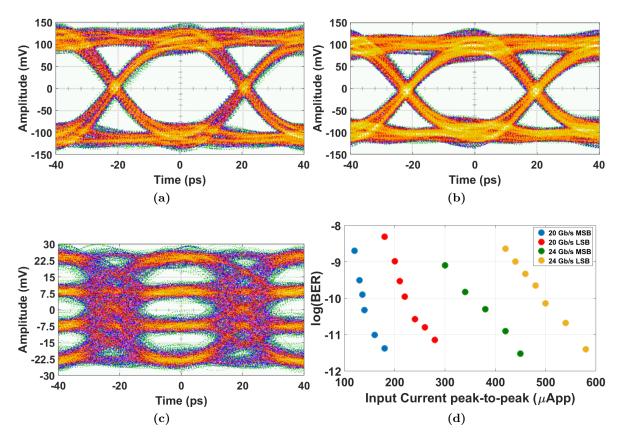

| 5.20                                                                          | 24 GBd single-ended error-free recovered eye diagrams from (a) MSB and (b)                    |    |  |  |  |

|                                                                               | LSB. (c) PAM-4 input signal. (d) BER measurements                                             | 90 |  |  |  |

| 5.21                                                                          | Single-ended NRZ eye diagrams at 50 Gb/s from (a) MSB and (b) LSB                             | 91 |  |  |  |

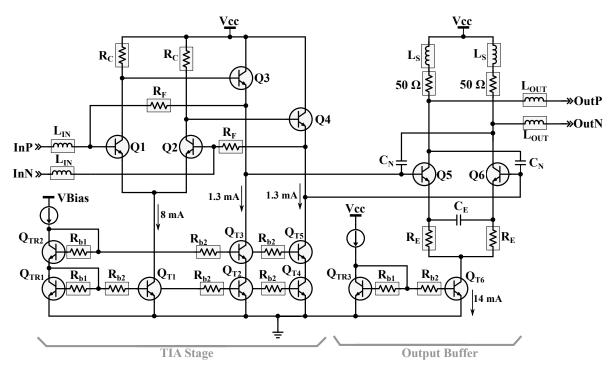

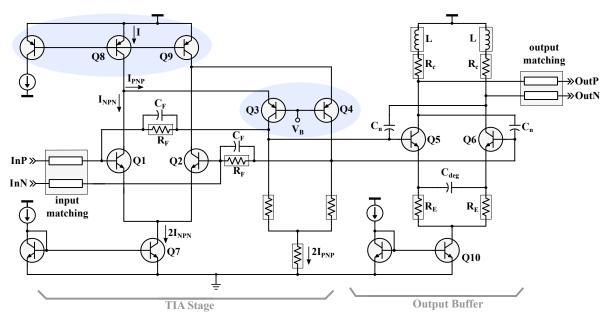

| 5.22                                                                          | TIA stage and $50\Omega$ buffer schematic.                                                    | 92 |  |  |  |

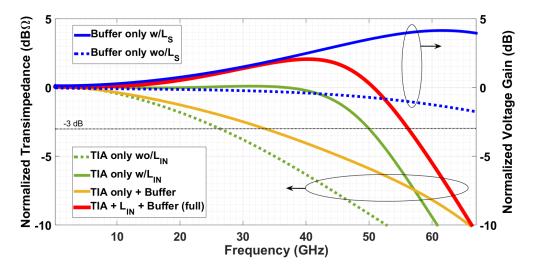

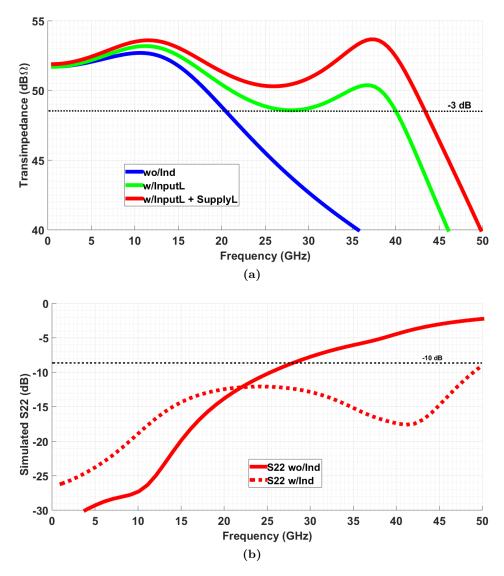

| 5.23                                                                          | Effect of the inductors in (a) bandwidth and (b) output matching. $\ldots$ .                  | 93 |  |  |  |

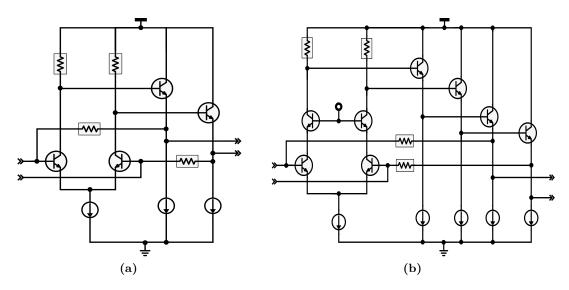

| 5.24                                                                          | Schematic of (a) common-emitter shunt-feedback TIA and (b) npn-only cascode                   |    |  |  |  |

|                                                                               | TIA                                                                                           | 94 |  |  |  |

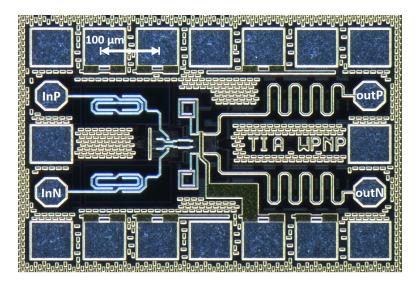

| 5.25                                                                          | Chip microphotograph                                                                          | 94 |  |  |  |

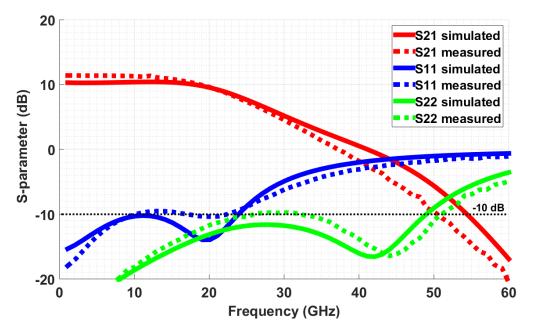

| 5.26                                                                          | S-parameters measured vs. simulated.                                                          | 95 |  |  |  |

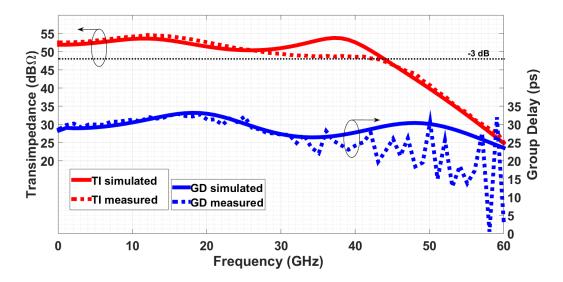

| 5.27                                                                          | Transimpedance and group delay measured vs. simulated. $\ldots$ $\ldots$ $\ldots$ $\ldots$    | 95 |  |  |  |

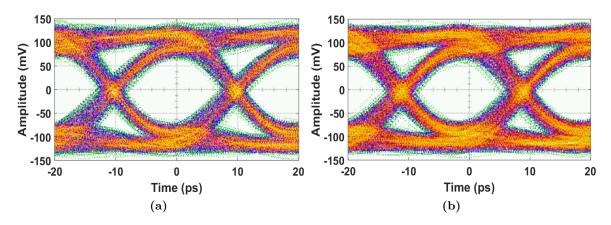

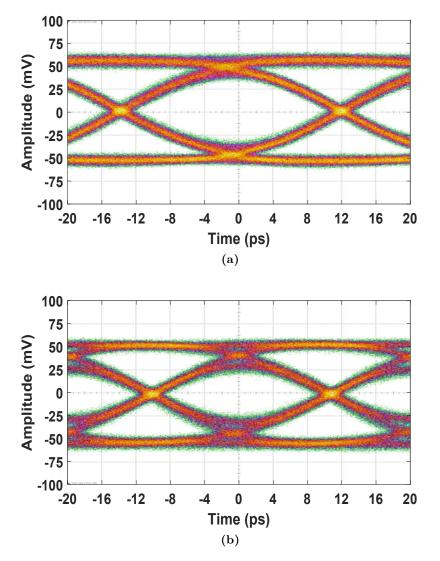

| 5.28                                                                          | Measured single-ended eye diagrams: (a) at 40Gb/s and (b) at 50 Gb/s                          | 96 |  |  |  |

# List of Tables

| 2.1 | Performance parameters of different technology processes                  | 18 |

|-----|---------------------------------------------------------------------------|----|

| 3.1 | Driver design parameters summary                                          | 40 |

| 3.2 | State-of-the-art comparison of Tx with integrated DAC                     | 54 |

| 4.1 | 13S-TIA design parameters summary.                                        | 62 |

| 4.2 | G2-TIA design parameters summary                                          | 62 |

| 4.3 | Measured performance compared with prior published work                   | 74 |

| 5.1 | Evolution of ADCs applied in optical transceivers or instrumentation [61] | 85 |

# Introduction

#### 1.1 The Zettabyte era: Trends and perspective

The advent of the internet in the 1990s caused a sudden global leap in the access and diffusion of information, both in the commercial (business) and domestic sectors. This led to the transition towards the Information Age and an economy based on information technology. The World Wide Web, used initially as a simple electronic billboard, morphed into an interactive consumer exchange platform; e-mail became customary and other traditional media businesses, such as book publishing, music and TV, also experienced the impact of the digitization of information. Enterprises in different domains started exploring the possibilities of capitalization on this new paradigm and led to the establishment of the *connected life* within the social fabric. Since the 2010s, the increase in the number of users and the diversification of connected devices (PCs, tablets, TVs, smartphones), have caused the internet ecosystem to expand rapidly. New applications such as web storage, file sharing, internet video, video-on-demand (VOD) or more recently cloud computing, have grown dramatically [1]; Big Data and the Internet-of-Things (IoT) are becoming a reality. This trend can be observed in the Cisco forecast in Figure 1.1: Global IP traffic is expected to increase nearly 3-fold between 2016 and 2021, with data-centers alone accounting for approximately 70% of the traffic concentration, making them the backbone of today's electronic society. In order to provide satisfactory user experience, this scenario requires essentially one thing: Higher transfer data rates.

Optical fiber communication technologies are the enabling factor behind such growth. Figure 1.2 shows how the B·L product has increased by a factor of  $10^{18}$  with the emergence of different technologies. B stands for bit-rate and L is the distance at which the signal needs to be regenerated to preserve fidelity (repeater distance). It is evident to see the change in slope that occured around 1980, when optical fibers were first used. Optical fiber is lighter, thinner and provides higher bandwidth and lower loss than electrical wiring. Featuring less than 0.25 dB/km attenuation around the emission wavelength of 1550 nm it enables transmission at up to Tb/s data rates across thousands of kilometers [2, 3]. Due to its non-metallic character it is also inmune to electromagnetic interference and crosstalk. High-paralellism techniques such as wave-length division multiplexing (WDM) or space division multiplexing (SDM) can significantly increase the aggregate bandwidth, making it several orders of magnitude faster

Figure 1.1: Cisco forecast for global IP traffic growth from 2016 to 2021 [6].

Figure 1.2: Historical increase in the  $B \cdot L$  product with new technologies [2].

than electrical wiring [2, 4, 5]. The disadvantage of optical communication is the transceiver cost, rendering it traditionally more profitable for the long-haul backbone networks, where production volumes are small and margins from equipment manufacturers are large. In the data-center communication market, volumes are enormous, and growing with time, leading to high pricing pressure. Here, recent advancements in silicon-photonics (SiPh) promise cheaper and scaled optics allowing optical communications to conquer more territory.

## **1.2** Topography of optical fiber networks

The architecture of optical networks in Germany is shown in Figure 1.3 [7], and is traditionally divided into three groups based on the targeted distance: (i) core or long-haul networks, (ii) metro or regional networks and (iii) access networks. Access networks are at the lowest level of the hierarchy, and incorporate the connections of the subscribers to their particular service providers. These networks are currently dominated by copper and radio connections, although the migration towards optical links has already started. Typical data rates in access networks are several hundred Mb/s and evolving towards 1 Gb/s [8]. The aggregated data from access networks is routed to the next level of the hierarchy, the metro or regional networks. These networks connect different local providers together and are based on optical fiber connections. Their internal routing is evolving from typical ring or star topology, as depicted in Figure 1.3, towards meshed architecture featuring redundancy for improved capacity and reliability. Finally, the core networks are at the top of the hierarchy and are responsible for transporting data aggregated by several metro networks, connecting countries with each other.

The recent evolution in cloud computing and data-centers has introduced a new domain in metro networks, termed data-center interconnects (DCI). Two primary types can be distinguished: telecom- DCI and metro- DCI (datacom), which together include the traffic within a data-center, between geographically distant data-centers and from data-center to user. Almost all computation from consumer electronics are directed to data-centers, and enterprises are also shifting most of their computing power outside, outsourcing it to data-centers for cloud and distributed computing.

DCIs are mainly point-to-point links featuring differentiated transmission schemes. In the telecom networks, which cover distances of several hundred km, the maximization of

Figure 1.3: Architecture of optical networks in Germany. Adapted from [7].

Figure 1.4: Dimensions for increasing channel capacity. Adapted from [9].

the product of spectral efficiency and distance is of primary importance. These networks have traditionally relied on WDM, which allows for capacity increase without infrastructure modification. However, upcoming standards such as 400 Gb/s and 1 Tb/s [10] cannot be sustainably accommodated by successively multiplexing lower speed carriers on different wavelengths, limited by power dissipation, form-factor and system complexity. Next generation transceivers must, therefore, resort to alternative dimensions to increase data throughput, namely: the use of digital coherent transmission schemes and/or the increase in the baud rate, as depicted in Figure 1.4. Digital coherent technologies make use of coherent detection together with digital signal processing (DSP), enabling the use of high-order modulation formats such as phase-shift-keying (PSK) and quadrature-amplitude-modulation (QAM), which provide better spectral utilization. Together with digital equalization techniques, such schemes allow for compensation of the fiber impairments in the telecom link. However, they are more susceptible to noise and non-linearities, featuring low optical signal-to-noise-ratio (OSNR) tolerance which limits the maximum achievable reach. On the other hand, higher baud rates relax the degradation in OSNR, but must resort to innovative circuit-level techniques and further advancements in high-speed electronics in order to increase the analog bandwidth.

Meanwhile, short reach optical modems, called "small form-factor pluggables", cover distances ranging from 100 m to 80 km and the key aspect in this arena is the cost and footprint reduction. Thus, datacom communication resorts mainly to intensity-modulation/direct-detection (IM/DD) formats, due to their relative system-level simplicity. Here, strict requirements in terms of low power dissipation and small form factor for pluggable modules must be considered. Thus, for the datacom transceivers, the challenge is to support high bit rates per optical carrier while using low-cost components and low-power electronics, leaving limited power budget for eventual DSP usage to clean up the signals.

Figure 1.5: Simplified block diagram of a DSP-based optical transceiver.

#### **1.3** Optical transceivers overview

Optical transmitters (Txs) and receivers (Rxs) are required to switch between the optical and the electrical domains. Figure 1.5 shows the simplified block diagram of a DSP-based optical transceiver, which is the preferred architecture since the last decade when DSP and data-converters became sufficiently fast [11, 12]. The DSP is the first block of the transmitter, encoding the data according to a modulation format suitable to the particular application. This binary data is converted into an analog signal by the high-speed digital-to-analog converter (DAC) and is then amplified linearly to the specific swing required to drive an electro-optical (E/O) modulator at a sufficient extinction ratio (ER). The ER is the ratio between the optical power of the logical "1" and the logical "0", and determines the signal-to-noise-ratio (SNR) of the link. Finally, the E/O modulator converts the information to the optical domain; the optical carrier is in this way modulated with an envelope that resembles the electrical data. The Rx is responsible for demodulating this envelope information from the optical carrier and converting it back to ditigal values. A photodiode (PD) receives the optical power and transforms it into an electrical current. This current is converted to the voltage domain with a transimpedance amplifier (TIA); the automatic gain control (AGC) provides additional voltage gain to amplify the signal in order to meet the sensitivity of the analog-to-digital-converter (ADC) where the signals are digitized. Lastly, the DSP decodes the data, leaving it ready for further processing. The transceiver is often built around a transmitter optical sub-assembly (TOSA) and a receiver optical sub-assembly (ROSA), which are small packages containing the E/O and the electrical front-end devices as indicated in Figure 1.5, as well as some other optical parts such as lenses and means for optical fiber alignment.

The hardware realizations of such transceivers pose many challenges due to the highoperating frequency, wide bandwidth and low noise requirements, which have led to commercial modules being historically dominated by III-V compound semiconductor technologies such as gallium arsenide (GaAs) and indium phosphide (InP). However, for low-cost, mass-market electronics, silicon technologies (Complementary Metal-Oxide-Semiconductor (CMOS) and SiGe) are preferred. While CMOS provides cost advantages in mass production and lower power consumption, especially for digital circuits, SiGe Bipolar Complementary Metal-Oxide-Semiconductor (BiCMOS) features better noise characteristics and higher breakdown voltages at comparable  $f_T$  [13] and is the platform of choice for the prototypes described in this thesis.

# 1.4 Scope and organization of the thesis

This work focuses on the development of high-performance front-end analog integrated circuits (ICs) (modulator drivers and TIAs), making use of different nodes of the SiGe:C BiCMOS technology of IHP, for the next generation of datacom and telecom optical transceivers. Circuit-level methods for enhancing different performance metrics such as high data rate, low power consumption and low noise are described and demonstrated through the characterization of the fabricated prototypes. The thesis is comprised of total six chapters. After this introduction, it is organized as follows:

**Chapter 2** starts with an overview of the E/O components used in the transceiver modules. Greater detail is given in the description of the E/O modulator, since it is used for the implementation of the Tx modules described in Chapter 3. The theoretical basics of high-speed broadband circuit design, essential to understand the module implementations reported in the subsequent chapters, are presented. A brief description of the different integration approaches and the technology nodes in which the ICs are fabricated are provided as well.

**Chapter 3** presents the implementation of Tx modules featuring integrated 4-b DAC functionality. The first part of the chapter describes a hybrid assembly which incorporates an InP segmented Mach-Zehnder modulator (SEMZM) together with a SiGe BiCMOS driver demonstrating up to 32 GBd 256-QAM signal modulation with record low energy dissipated per bit. In the second part of the chapter, the same concept is implemented in the electronic-photonic-integrated-circuit (EPIC) platform of IHP, demonstrating up to 37 GBd PAM-4 operation, which is the highest baud-rate reported to date among silicon-based modulators.

**Chapter 4** describes a design technique for TIAs, which permits simultaneous low noise and high-bandwidth performance. The method is then verified by means of two analogous TIA implementations in the SG13S and SG13G2 processes with designs that feature less than  $10 \text{ pA}/\sqrt{Hz}$  averaged input referred current noise density while operating at 100 Gb/s data rate.

**Chapter 5** presents advanced Rx architectures aiming at power-efficient modules, based on the low noise design technique described in Chapter 4. First, a benchmarking TIA which achieves 60 GHz bandwidth and integrated input referred noise current density lower than  $5.5 \text{ pA}/\sqrt{Hz}$  is described. High Rx sensitivity is key to a power-efficient optical link. Second, the SG13G2 TIA from Chapter 4 is used to implement a custom solution for a pulse-amplitudemodulation (PAM)-4 Rx front-end capable of demodulating signals at up to 100 Gb/s data rate. Finally, a TIA in folded-cascode architecture which makes use of pnp transistors is described, exploring the benefits of a complementary technology in power-efficient high-speed Rx front-ends.

**Chapter 6** draws conclusions and provides an outlook of future technical challenges for optical communication systems.

2

# **Optical Transceivers Fundamentals**

## 2.1 Electro-optical devices

The electro-optical (E/O) devices, namely the photodetector on the receiver (Rx) and the E/O modulator on the transmitter (Tx) enable the transfer between the electrical and the optical domains and their characteristics largely determine the transceiver's performance and design. Furthermore, co-integration and co-design of these elements with the front-end electronics can potentially improve the overall system performance.

#### 2.1.1 Photodetector

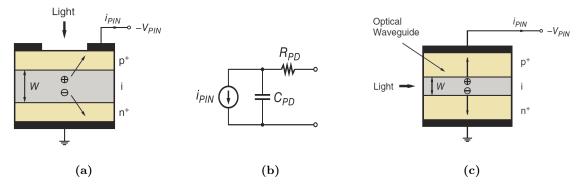

The photodectector transforms the optical signal into electrical current, and it must feature a large response to the received light, sufficiently large bandwidth (BW) for the incoming signal and generate as low noise as possible. One of the most widely used photodetectors is the *p-i-n* photodiode, shown in Figure 2.1a. It consists of a p-n junction with a layer of intrinsic (undoped or lightly doped) semiconductor material sandwiched between the p- and the n-doped materials. The junction is reverse biased with  $-V_{PIN}$  to create a strong electric field in the intrinsic layer. Photons with the proper energy (i.e.  $hc/\lambda > E_g$ , where  $E_g$  is the bandgap energy of the absorption material) enter through a hole in the top electrode (anode), pass through the p-doped material and reach the i-layer. Here they are able to push electrons from the valence band to the conduction band creating electron-hole pairs. These pairs become separated by the strong electric drift field with the holes travelling to the negative terminal and the electrons travelling to the positive terminal, as indicated in Figure 2.1a. As a result, the photocurrent  $i_{PIN}$  appears at the diode terminals. The quantum efficiency ( $\eta$ ) is the fraction of incident photons that stimulate an electron-hole pair contributing to the photocurrent. An ideal photodetector has a 100% quantum efficiency, with  $\eta = 1$ .  $\eta$  depends on the width W of the absorption layer: The wider W, the higher are the chances of absorbing a photon. It also depends on how much light is coupled from the fiber into the detector. Thus, sub-optimal fiber coupling, surface reflection and absorption of the photons as heat or loss due to recombination (as opposed to contributing to the photocurrent) all reduce the  $\eta$  from its ideal value [14].

Electrically, the photodiode (PD) is measured by its *responsivity*, given by R = I/P in A/W, where I is the generated electrical current and P is incident optical power. The

**Figure 2.1:** (a) Vertically illuminated p-i-n photodetector cross-section, (b) corresponding electrical equivalent and (c) waveguide p-i-n photodetector [14].

responsivity is related to the quantum efficiency by the photon energy  $(hc/\lambda)$  and the electron charge q, through (2.1).

$$R = \eta \frac{\lambda q}{hc} \tag{2.1}$$

From this relationship, it is obvious to see that R is proportional to  $\eta$ , and in the same way, longer width of the intrinsic region W will increase the R. However, the value of W also determines the time it takes for the carriers to traverse the absorption layer, and thus, a longer W increases the transit time and reduces the speed of the PD. The transit time depends also on the strength of the electric field: with increasing field strength, the carrier velocity increases and saturates at V<sub>c,sat</sub>. Therefore, the reverse bias voltage (-V<sub>PIN</sub>), must be high enough such that velocity saturation is reached. On the other hand, smaller W not only degrades R but may also limit the BW by increasing the capacitance of the PD, C<sub>PD</sub>, since it reduces the distance between the electrodes (i.e. the capacitor plates). The C<sub>PD</sub> together with the contact and spreading resistances, modelled by R<sub>PD</sub>, as in Figure 2.1b, create also an RC-limiting time constant. The overall BW of the pin PD is limited by the transit-time and this RC-constant, both having inverse relationships with W: If the absorption layer is made thinner to reduce the transit time, the diode capacitance gets larger, and the RC constant becomes more dominant. The BW of the p-i-n PD is modelled by (2.2).

$$BW_{PIN} = \frac{1}{2\pi (W/3.5v_{c,sat} + R_{PD}C_{PD})}$$

(2.2)

Waveguide or edge-coupled PDs, as depicted in Figure 2.1c solve this trade-off between  $\eta$  and BW by illuminating the PD from the side, rather than from the top. In this way, the  $\eta$  is controlled by the horizontal dimension, which can be made large, while the transit time is controlled by the vertical dimension W, which can be made small. However, due to the reduced dimensions of the W to make the diode faster, it is difficult to efficienctly couple the light. Another kind of PD used in optical communication at low speeds is the avalanche photodiode (APD). In these PDs and extra p-layer is inserted to provide optical gain by avalanche multiplication of the electron-hole pairs. APDs feature much higher responsivity than pin PDs but at the expense of more optical noise (excess noise factor); they also require much higher bias voltages to sustain the avalanche multiplication.

#### 2.1.2 Optical modulator

On the Tx side, laser diodes with external modulation are typically used as the optical source for high-capacity and long-span transmission systems. The optical intensity of the semiconductor laser can be modulated internally, via the bias current (direct modulation). However, turning the laser on and off creates electrical and thermal stress, frequency chirp (i.e. output frequency varies with time) and reduced operational lifetimes. In addition, direct modulation of a laser induces oscillations on the rising edge of the pulse (relaxation oscillation) which limit the maximum modulation frequency, typically ranging from 1 to 10 GHz for a vertical cavity surface emitting laser (VCSEL) [15]. These impairments are mitigated by external modulation, where the laser diode is biased to produce a continuous wave (CW) output (i.e. unmodulated) and an external optical modulator placed next to the laser converts the CW light into a data-coded pulse train with correct modulation format. Furthermore, in this way a single light source can feed multiple channels via individual modulators, reducing the power budget of the system.

External modulators are made of materials whose optical properties can be modified by an applied external electrical field. In electro-absorption (EA) modulators, carrier injection is used to induce absorption, which directly modulates the intensity of a propagating mode. These modulators are thus not a suitable choice when simultaneous phase modulation is desired, as in coherent applications. Control over the refractive index of the modulator material can be used to shift the relative phase of two propagating waves such that constructive or destructive interference is produced. This is the principle used in Mach-Zehnder modulators (MZMs) which will be explained in detail in the following section. Alternatively, if a resonant structure is implemented, the change in the refractive index will induce a change in the resonant condition, thus allowing the device to be switched between on- and off- resonance states at a given wavelength. Such devices are called ring-modulators [16]. Although they allow for very compact sizes, they are functional only on a very narrow band, around 100 pm, compared to MZMs, which feature optical bandwidths of more than 20 nm. Narrowband devices are very sensitive to fabrication tolerances and temperature variations, which limits their application. Thus, MZM interferometers are the most commonly used optical modulators in practice, permitting simultaneous phase and amplitude modulation and featuring broad optical bandwidth and zero or tunable frequency chirp [17].

# 2.2 Mach-Zehnder modulator

A MZM is an interference-based optical modulator in which the phase difference between two arms is controlled by an external electrical signal and transformed into amplitude modulation due to the interferometric principle. The block diagram of a standard MZM is depicted in Figure 2.2. The incoming light is coupled into the input waveguide of the modulator and split into two equal parts with the help of a coupler (typically a multi-mode interference (MMI) coupler) and then routed into two waveguides. The two light beams travel through the active areas of the modulator. These active areas are structured as p-n junctions which under reverse bias conditions deplete the waveguide of carriers causing a change in the refractive index and absorption. It is here where the interaction between the electrical signal and the optical wave

Figure 2.3: MZM power transfer function and most common bias points. Depending on the selected modulation format, the modulator is biased in either the 3 dB or the min. point.

occurs and the relative phase difference is generated in accordance with the applied external voltage  $V_a$ . In the last step, the light is recombined using again an appropriate interference structure where the two incoming beams interfere with each other. When the differential phase shift between the two arms equals  $\pm \pi$ , destructive interference occurs, corresponding to the "0" or off-state for the modulator, delivering no light at the output. Conversely, if the relative phase between the two arms is 0° constructive interference will occur, and the output intensity will ideally be the same as that at the input. Between these two cases, the output intensity will vary in accordance with the difference in phase between both arms. In this way phase modulation is turned into intensity modulation [17].

The field applied to the active waveguides induces a change of the material refractive index which is proportional to the field's amplitude and therefore, to the applied voltage  $V_a$ . The voltage required to induce a  $\pi$  phase shift across a phase shifter of length L is known as the  $V_{\pi}$ . The product  $V_{\pi}L$  determines the E/O modulation efficiency, and is an intuitive metric to compare designs. This product depends on several design parameters, including those that directly affect the overlap between the optical and the electrical mode, e.g. the intrinsic region thickness (IRT) and the junction materials. In order to obtain high efficiency, the  $V_{\pi}L$  product should be minimized. Therefore, an efficient MZM requires a shorter active length than a less efficient one, for the same voltage. Similarly, when the active length has already been fixed, a more efficient modulator will require a lower drive voltage to achieve full modulation depth.

The power transfer characteristic of the MZM is depicted in Figure 2.3. It is a non-linear function, leading to a strong dependency of the modulator behavior on the selected operating (working) point. The operating point of the modulator will be chosen in accordance with the targeted modulation format and is adjusted through the bias section of the modulator. This bias section is connected to an external DC voltage. For example, for amplitude modulation the MZM is typically biased in the middle of the linear region (i.e. at the 3 dB point or quadrature point), and driven with an electrical signal of limited amplitude. This ensures that the non-linear extremities of the transfer function are not reached and no distortion of the modulated signal is introduced. Further influences of the working point in the modulation format will be explained later. Apart from the  $V_{\pi}L$  product, the performance of the MZM is quantified also with the insertion loss (IL) and the extinction ratio (ER). The IL of a MZM is defined as the ratio between the maximum optical power guided to the output  $P_{max}$  and the optical power fed at the input  $P_{in}$ , and it provides a measure of how much light is lost. The losses are caused by passive effects such as reflection, absorption and mode-coupling losses, and contribute to the link budget. The ER expresses the modulation depth of the device and is defined as  $P_{max}/P_{min}$ , where  $P_{min}$  is the optical power level seen at the output when the MZM is in the off state.

Small, high-efficiency and high-speed MZMs with low optical losses are available with III-V materials. In particular, InP modulators exhibit a smaller footprint and a lower driving voltage with respect to polymer and LiNbO<sub>3</sub> counterparts [18]. Emerging SiPh MZMs show lower performance in terms of efficiency and achievable bandwidth, although recent developments have also demonstrated high-speed capability [19, 20]. In this work, both InP and SiPh MZMs have been explored for the implementation of different Tx modules. Their particular characteristics and electrical equivalents are described in greater detail in Chapter 3.

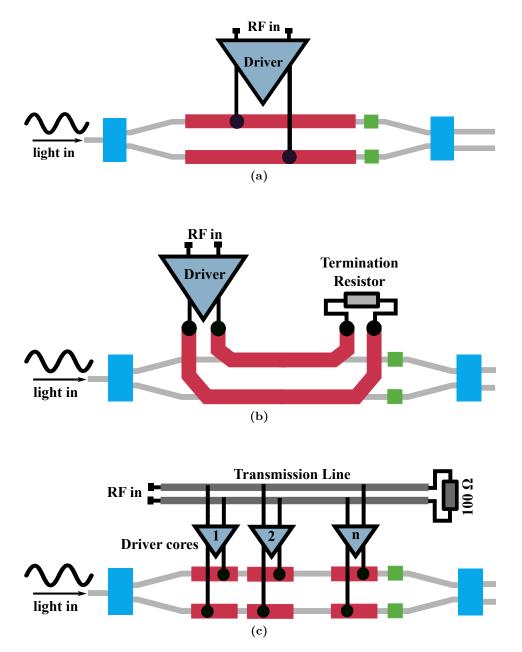

#### 2.2.1 MZM driving: electrode configurations

MZMs are commonly driven in the so-called push-pull configuration in order to achieve chirpfree operation [17]. This applies to two-path interferometric devices in which the two arms are driven in antiphase (i.e.  $V_1$ =- $V_2$ , with  $V_1$  and  $V_2$  being the voltages applied to each arm of the modulator), keeping the phase of the optical output constant. In this way, the MZM renders itself naturally to differential driving configurations ( $V_a = V_1$ - $V_2$ ). The differential modulating signal is applied to the modulator through the electrodes which are deposited over the optical waveguide. As mentioned previously, the electrodes or active areas are p-n junctions operated in reverse bias condition which can be modelled by the junction capacitance. Several electrode configurations have been developed to electrically drive the MZMs at high speeds. Those can be broadly categorized into:

- a. Driving the whole modulator as a lumped element, as it is the typical case for resonant ring modulators [21] or very short MZMs.

- b. Driving of travelling-wave-electrode (TWE) MZM [22].

- c. Driving of segmented Mach-Zehnder modulators (SEMZMs) [23, 24].

Figure 2.4: MZM driving schemes: (a) lumped electrode, (b) TWE and (c) SEMZM.

The lumped element configuration (Figure 2.4a) requires the modulator to be very short in order to satisfy the lumped condition up to reasonable frequencies ( $L \sim \lambda/10$ , with  $\lambda$  being the wavelength corresponding to the maximum targeted RF operating frequency). Therefore, for the same  $V_{\pi}L$  product and comparable frequency of operation, this approach requires low L and high driving voltages that are difficult to achieve; thus obtaining high ERs and high operation speeds becomes challenging. High-speed modulators are commonly driven following the TWE approach (Figure 2.4b), as an evolution from the precedent lumped devices. In this configuration, instead of a large lumped capacitance, the capacitive load is distributed along a transmission line that transforms the reactive (capacitive) behavior of the modulator into a resistive behavior. This line is driven from one end, and it is electrically modeled by a resistor equivalent to the characteristic impedance of the line ( $Z_0$ , typically 50  $\Omega$ ). In this way, the modulators can be made longer, and for the same  $V_{\pi}L$  product they require lower driving voltages. The bandwidth of such a structure is limited by its RC constant. For long

Figure 2.5: IQ-MZM block diagram.

modulators, the performance is also degraded as the parts of the line that are further away from the launching end of the electrical signal are less efficient due to the RF losses. For high speeds, accurate velocity matching of the electrical and optical signal paths must be satisfied: The electrical signal must propagate in the same direction and at precisely the same speed as the optical wave, permitting the phase modulation to accumulate monotonically regardless of frequency. For the TWE approach, with increasing frequency and modulator length, velocity mismatch may cause phase walk-off between the two arms resulting in the cancellation of initial modulation by subsequent anti-phase modulation [25] and ultimately in bandwidth reduction. High-frequency signals suffer also from larger losses while travelling through the TWE. To address these issues, the segmented modulator approach (Figure 2.4c), has been proposed [23]. In the SEMZM, the modulator is divided into segments, small enough to keep their physical dimensions well below a wavelength of an electrical signal travelling down the line. The electrical equivalent of each lumped segment is given mainly by a capacitance, which is then directly driven by a dedicated driver core. Each driver core senses its input voltage from the signal travelling along the transmission line. Ideally, with this scheme the same voltage can be effectively applied along the whole of the modulator length, since this configuration allows for re-generation (loss compensation) of the high-frequency data signal that has been attenuated by travelling through the line. Thus, the length of the modulator L, can be extended beyond limitation, rendering lower required driving voltages. Moreover, having the delay under control on the driver side, velocity matching between optical and electrical waves can be guaranteed, increasing the total performance of the modulator chip. With this approach RF and electro-optic design are effectively decoupled: the transmission line is isolated from the modulator and can be independently designed and optimized considering the constraints from the electrical side. This is the configuration used in this work; in Chapter 3 the role of the number of segments and its relation to the driving voltage, maximum speed and power dissipation is analyzed.

#### 2.2.2 High-order modulation formats generation

Emerging technologies for long-haul and telecom links make use of high-order modulation formats, in combination with coherent detection and digital signal processing (DSP). With coherent detection, all parameters of the optical field (amplitude, phase and polarization) are available in the electrical domain, allowing for the detection of arbitrary modulation formats and constellations. Furthermore, the preservation of the temporal phase enables the use of DSP for the effective compensation of the fiber impairments, i.e. the chromatic dispersion,

Figure 2.6: Generation of 256-QAM with I/Q-MZM. Adapted from [30].

polarization mode dispersion and nonlinearities, permitting the system to operate closer to the ultimate limits of spectral efficiency. On the other hand, when employing these advanced transmission schemes, the complexity of the Txs and Rxs increases, and also higher hardware costs have to be weighed in [26, 27]. The power dissipation required for signal processing contributes significantly to the overall energy requirements of the transceiver, and can reach up to 50% of the total consumption [28]. Due to these reasons, in datacom links direct detection techniques are preferred.

Optical high-order modulation formats can be generated by many different transmitter configurations, whereby, the optical complexity can be reduced through increased electrical complexity and viceversa [29]. By operating the MZM in a dual-drive mode, applying signals to both arms, quadrature-amplitude-modulation (QAM) signals can be generated. However, in this case the modulator is not driven in push-pull fashion, which causes significant chirping of the optical signal and will reduce its performance. A single MZM can be used to modulate the amplitude or the phase of the optical signal. For concurrent multi-amplitude and multiphase modulation, nested MZM structures, also referred to as "I/Q-MZM", are typically used [30]. The block diagram of such an I/Q-MZM is depicted in Figure 2.5. The I/Q-MZM is composed of two parallel MZMs sharing a single optical input and a single optical output. The two modulators are referred to as the children, while the I/Q ensemble is referred to as the parent. Before and after the children, additional MMIs are inserted to serve as splitters and couplers, respectively. Additionally, the second MMI introduces a phase shift of  $\pi/2$  for one of its inputs and thus ensures orthogonality between both branches. Residual undesired phase differences between the two children signals are compensated, thanks to an additional biasing section inserted at parent level [30]. Both children are driven with multilevel signals, which are multiplexed by the parent generating the I/Q signal which transports information in both its amplitude and phase without requiring additional bandwidth. This is the preferred method for generating QAM signals. A convenient representation of amplitude and phase modulated signals can be obtained via the constellation diagram. This diagram results from combining the information contained in the I- and Q- signal symbols on a complex plane, as seen in Figure 2.6. Higher-order modulation schemes are associated to diagrams that are more

Figure 2.7: Schematic cross sections of integration between photonic and electronic circuits. Adapted from [33].

crowded with a larger amount of information conveyed by each constellation point (i.e. the number of bits per symbol). I/Q modulators are biased in the minimum point and typically driven with  $2V_{\pi}$  in order to maximize ER, although the entire complex plane can be covered also with arbitrarily small driving voltage swings. Figure 2.6 represents the generation of a 256-QAM format with an I/Q modulator: on the left side, the characteristic of a single MZM (children) with 16 states divided into two groups of 8 intensity levels is represented; on the right side the corresponding constellation diagram is plotted. The constellation points are unequally spaced because of the non-linearity of the MZM transfer function, when driven with full swing.