## Deterministic Pushdown Automata as Specifications for Discrete Event Supervisory Control in Isabelle

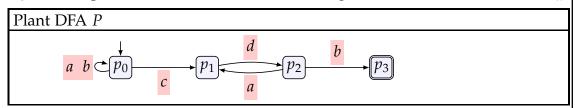

vorgelegt von Dipl. Inform. Sven Schneider ORCID: 0000-0001-9828-618X

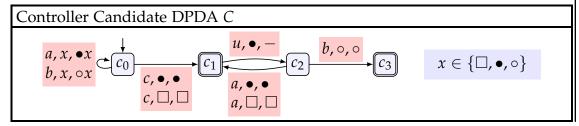

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften – Dr.-Ing. –

genehmigte Dissertation

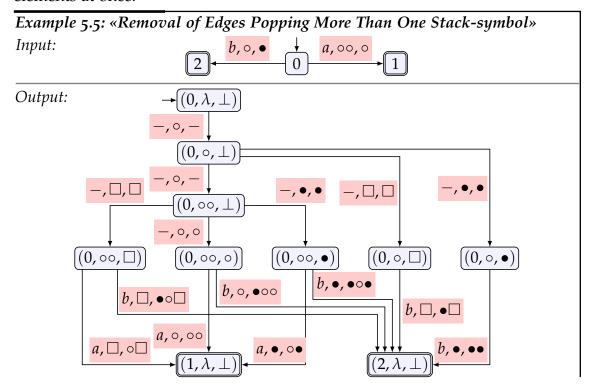

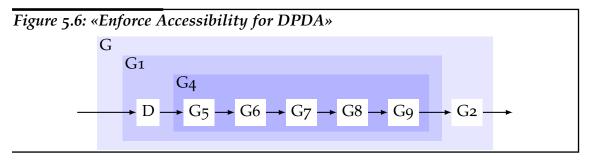

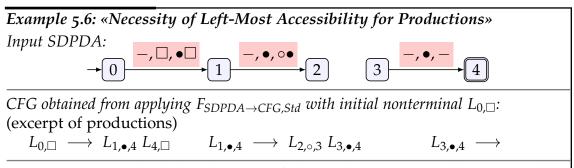

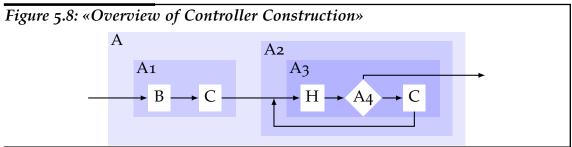

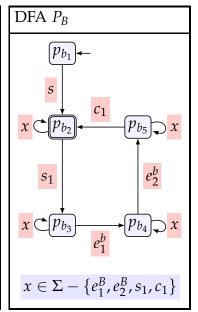

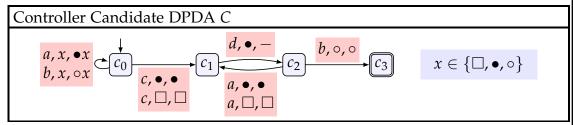

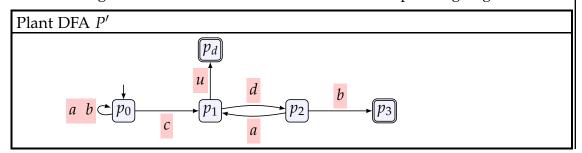

#### Promotionsausschuss:

Vorsitzender: Prof. Dr. Rolf Niedermeier

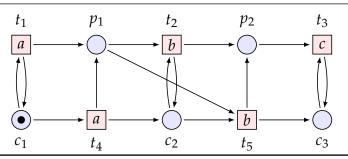

Gutachter: Prof. Dr. Uwe Nestmann

Gutachter: Prof. Dr. Jörg Raisch

Gutachter: Prof. Dr. Holger Giese

Gutachter: Dr. habil. Florian Kammüller

Tag der wissenschaftlichen Aussprache: 26. Februar 2019

Berlin 2019

Deterministic Pushdown Automata as Specifications for Discrete Event Supervisory Control in Isabelle

## Deterministic Pushdown Automata as Specifications for Discrete Event Supervisory Control in Isabelle

Sven Falco Schneider

Technische Universität Berlin Max-Planck-Institut für Dynamik komplexer technischer Systeme Magdeburg Hasso-Plattner-Institut für Digital Engineering gGmbH

### Contents

| Abs          | tract                                                             | ix  |

|--------------|-------------------------------------------------------------------|-----|

| 1. I         | ntroduction                                                       | 1   |

| 2. A         | bstract and Concrete Discrete Event Systems                       | 15  |

| 2.1.         | Discrete Event Systems                                            | 17  |

| 2.2.         | Extended Pushdown Automata                                        | 18  |

| 2.3.         | Parsers                                                           | 22  |

| 2.4.         | Context-free Grammars                                             | 27  |

| 3. A         | bstract and Concrete Supervisory Control Problems                 | 31  |

| 3.1.         | Abstract Supervisory Control Problem                              |     |

|              | for Discrete Event Systems                                        | 33  |

| 3.2.         | Concrete Supervisory Control Problem                              |     |

|              | for Deterministic Pushdown Automata                               | 36  |

| 3.3.         | Correspondence between Abstract and Concrete                      |     |

|              | Supervisory Control Problems                                      | 41  |

| -            | bstract Controller Synthesis Algorithm                            | 45  |

|              | or Discrete Event Systems                                         | 45  |

| 4.1.         | Framework of Abstract Building Blocks                             |     |

|              | for Fixed-point Computation                                       | 47  |

| 4.2.         | Abstract Building Blocks for Enforcing Properties                 |     |

|              | on Discrete Event Systems Least Restrictively                     | 50  |

| 4.3.         | Abstract Controller Synthesis Algorithm                           |     |

|              | for Discrete Event Systems                                        | 53  |

| 4.4.         | On the Termination of the Abstract Controller Synthesis Algorithm | 56  |

| - (          | Concrete Controller Synthesis Algorithm                           |     |

| -            | or Deterministic Pushdown Automata                                | 61  |

|              | Concrete Building Block for the Synchronous Composition           |     |

| 5.1.         | of Deterministic Pushdown Automata                                |     |

|              | with Deterministic Finite Automata                                | 64  |

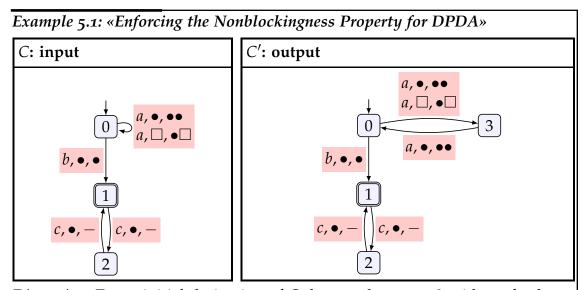

| 5.2          | Concrete Building Block for Enforcing Nonblockingness             | 04  |

| J. <b>2.</b> | for Deterministic Pushdown Automata                               | 65  |

| 5.3.         | Concrete Building Block                                           |     |

|              | for Reducing Controllability to Nonblockingness                   |     |

|              | for Deterministic Pushdown Automata                               | 82  |

| 5.4.         | Concrete Synthesis Algorithm as an Instantiation                  |     |

| - •          | of the Abstract Synthesis Algorithm                               | 85  |

| 5.5.         | On the Termination                                                |     |

| -            | of the Concrete Controller Synthesis Algorithm                    | 87  |

|              |                                                                   | vii |

| 6. Is                | sabelle-based Formal Quality Assurance                 | 89  |

|----------------------|--------------------------------------------------------|-----|

| 6.1.                 | Formal Methods for Quality Assurance                   | 91  |

| 6.2.                 | Isabelle-based Framework of Definitions and Properties | 96  |

| 6.3.                 | Isabelle-based Verification of the Translation         |     |

|                      | of Deterministic Pushdown Automata                     |     |

|                      | into LR(1)-context-free Grammars                       | 116 |

| 7. A                 | pplication and Prototype-based Evaluation              | 141 |

| 7.1.                 | Patterns for Specifications                            |     |

|                      | using Deterministic Pushdown Automata                  | 143 |

| 7.2.                 | Application Domains for                                |     |

|                      | Discrete Event Controller Synthesis                    | 146 |

| 7.3.                 | Applications and Use Cases                             |     |

|                      | of the Concrete Controller Synthesis Algorithm         | 147 |

| 7.4.                 | Prototype Realization                                  |     |

|                      | of the Concrete Controller Synthesis Algorithm         | 154 |

| 7.5.                 | Prototype-based Evaluation                             | 157 |

| 8. R                 | Related, Ongoing, and Future Work                      | 163 |

| 8.1.                 | Related Work                                           | 164 |

| 8.2.                 | Ongoing Work                                           | 188 |

| 8.3.                 | Future Work                                            | 209 |

| 9. S                 | ummary and Conclusion                                  | 219 |

| <u><b>A</b>. L</u>   | Disclaimer on Collaborations and Joint Work            | 225 |

| <b>B.</b> <i>I</i> : | sabelle-based Notation                                 | 227 |

| <u>C. C</u>          | Operational Properties for DPDA Controllers            | 233 |

| <u>D. 7</u>          | he cfgEsplit Semantic for LR(1)-CFG                    | 237 |

| E. <i>B</i>          | aibliography                                           | 249 |

#### ABSTRACT

The problem of supporting the construction of software that is known to satisfy a set of given requirements is one of the grand challenges in software engineering. Herein, we focus on the field of control theory for systems with discrete states and event-based communication. In this field, controllers coordinate components given by a plant to ensure that the amalgamation of controller and plant executes a desired behavior. We focus on the supervisory control problem, which, given a plant and a specification, requires the synthesis of a controller in the form of a piece of software. The least restrictive satisfactory controllers to be synthesized are determined in this problem by the specification and additional well-formedness conditions. Similar problems also occurred in the field of computer science and it is of general importance in application domains such as in parallel, distributed, and embedded systems.

We focus on the fully automatic synthesis of controllers using algorithms. These algorithms construct controllers that are realizable in software and correct-by-construction for the two aforementioned inputs. The applicability of these algorithms is limited by insufficient expressiveness of the formalisms used for plants and specifications. However, expressiveness can not be increased arbitrarily while maintaining solvability of the problem in terms of a synthesis algorithm that solves all problem instances.

Our main contribution is a controller synthesis algorithm that synthesizes a DPDA controller when provided with a DFA plant model and a DPDA specification. This algorithm supersedes earlier algorithms synthesizing a DFA controller when provided with a DFA plant model and a DFA specification because DPDA are strictly more expressive than DFA. The increased expressiveness of DPDA compared to DFA allows for the specification and enforcement of more complex patterns of behavior. Initial approaches to mitigate limitations of our algorithm, such as its nontermination for some specifications stating requirements that are unreasonable from a control-theoretic perspective, are presented in the form of alternative constructions and optimizations.

We employed the interactive theorem prover Isabelle for the formal verification of this controller synthesis algorithm to obtain trustworthy proofs, which are free of faults and omissions. The resulting Isabelle framework for the formalization and verification of algorithms outstrips existing similar frameworks in covered formalisms, semantical properties, and provided results and is designed to be highly extendable in these aspects. It covers the formalisms of DPDA, CFGs, and Parsers as well as the notions relevant for our controller synthesis algorithm such as the unmarked and marked languages, nonblockingness, and controllability.

An evaluation of our algorithm implemented as the Java prototype CoSy shows promising efficiency. This evaluation was based on three examples from manufacturing employing DPDA specifications. Using these examples, we also demonstrate the application of three use cases of our algorithm for controller synthesis, controller verification, and input validation.

#### Introduction

The problem of supporting the *construction of software that is known to satisfy a set of given requirements* is one of the grand challenges in software engineering. We focus on software that interacts with its environment where the requirements then refer to the *closed loop*, which is the amalgamation of the constructed software and the environment. Established processes for the construction of such software vary in their degree of automation: the spectrum ranges from *fully automatic synthesis* to *fully manual implementation*. We focus in this thesis on fully automatic synthesis and present a formally verified synthesis procedure as one of our key contributions.

The fully automatic synthesis has been stated as a problem in the construction of hardware circuits in 1957 [81, 121]. A second formulation of a controller synthesis problem in terms of a game between a player representing the software to be constructed and a player representing the environment was first described as early as 1965 [244, 66, 237, 356]. In this game-based perspective, any finite winning strategy employed by the first player translates to a realization of the software to be constructed. Similar controller synthesis problems appeared in the form of the submodule construction problem in 1983 [245] and the *supervisory control problem* in 1984 [282].

Common to these formulations of control problems is the assumption of a message-based communication between the system and the environment. This assumption is readily satisfied by a variety of systems from the fields of computer science and control theory in which software is required to control or to coordinate components to ensure the execution of desired behavior such as communicating and embedded systems. These control problems are based on the same kinds of inputs: a model of the environment, of how software and environment coalesce into the closed loop, and of the requirements to be satisfied by the software and closed loop. We focus in this thesis on the supervisory control problem and continue now with a more detailed introduction of it.

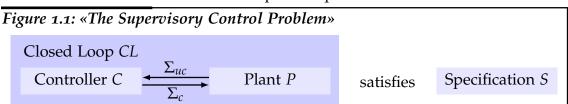

#### → The Supervisory Control Problem

The supervisory control problem [282], for which we present an example on page 5, is a software synthesis problem related to the field of control theory. Hence, a field-specific terminology is used: the environment is called *plant* and the software that interacts with the plant is called *controller*. The purpose of the controller is to limit the behavior of the plant to the boundaries given by an additional specification that states requirements specific to the problem instance. A list of *general requirements*, which includes the satisfaction of the specification, then describes all desirable controllers of which one is to be synthesized. We now continue with a short discussion of the fundamental assumptions on how plant and controller are combined into a closed loop and then also present the requirements to be satisfied by controller and closed loop.

The plant and the controller are assumed to send messages, subsequently called events, to each other using reliable synchronous communication in the closed loop. Synchronous communication means here that the sending and the receiving of a single event occurs in a single (atomic) step that is carried out by sender and receiver at the same time. The reliability and synchronicity of the communication ensure the absence of effects such as event loss, alteration, duplication, insertion, or reordering. The events sent by the plant carry information from *sensors* and the events sent by the controller represent commands to be carried out by *actuators*. The sender and receiver of an event may change their local *state* upon synchronization. The state of a component is thereby given by the local knowledge of that component on the status of the closed loop that it has acquired in the past and that is the foundation for decisions on steps in its future.

The response of the plant (if any) to communication attempts initiated by the controller is predefined because the plant is one of the inputs to be provided. That is, the provided plant model specifies for each state of the plant and each event sent by the controller whether the plant is willing to synchronously receive this event or whether the controller is not able to send the event. Thereby, the controller is limited by the plant model in its capabilities to control the plant. However, since the controller is to be synthesized, the existence of a response to every event sent by the plant is an important requirement, called *controllability*. The satisfaction of controllability by the controller ensures that (a) the state of the controller also includes the relevant information on the state of the plant at the same time, (b) the controller can derive well-founded decisions, and (c) the models for controllers and closed loops are equivalent in formal considerations.

The general requirements of the control problem (which are discussed subsequently) rely on a uniform characterization of the behavior of the plant, the controller, the closed loop, and the specification. This characterization is given for

each of these components by the set of *unmarked behaviors* and a particular subset thereof called the set of *marked behaviors*. The unmarked behaviors of plant and controller are the sequences of events from a finite set  $\Sigma$  that *may* be used in successive steps by this component; the specification also describes such sequences without use of an actual communication partner. The marked behaviors identify a goal region or those unmarked behaviors in which a task has been completed. While every prefix of an unmarked behavior is an unmarked behavior, we permit cases where this does not apply for the marked behaviors. The (un)marked behaviors of the closed loop are given by the intersection of the (un)marked behaviors of plant and controller due to their synchronous composition.

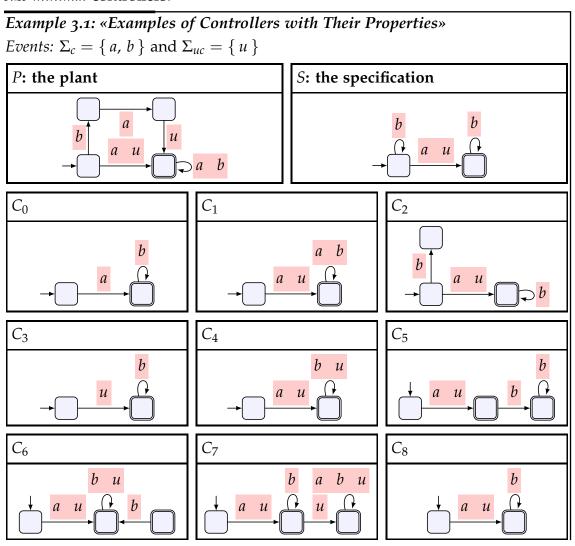

The event set  $\Sigma$  is partitioned into the sets of events  $\Sigma_c$  and  $\Sigma_{uc}$  that are sent by the controller and plant, respectively. The indices c and uc abbreviate controllable and uncontrollable, respectively, and are chosen based on the perspective of the prospective controller. Firstly, the decision on whether or not to send an event from  $\Sigma_c$  is fully controllable by the controller. Secondly, the events that are sent by the plant are not under the influence of the controller and must not be rejected.

The requirement of *controllability* states that the controller never prevents the plant from sending an event by refusing its reception. An example of the notion of controllability is given in Example 1.1|p.4.

The requirement of *specification satisfaction* states that the controller must successfully restrict the (un)marked behaviors of the plant (that is, the uncontrolled behaviors of the plant) to those of the specification (that is, the safe region and the goal region). This means that the (un)marked behaviors of the closed loop must be contained in those of the specification.

The requirement of *nonblockingness* states that every unmarked behavior of the closed loop can be continued to a marked behavior of the closed loop. The notion of nonblockingness is exemplified in Example 1.1|p.4. We conclude that the marked behavior, which is required to be invariantly reachable, is also limited by the marked behaviors of the specification when the specification is satisfied.

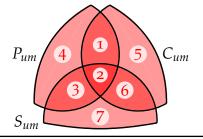

#### Figure 1.2: «Relationship between Plant, Specification, and Controller»

We relate the unmarked behaviors of the plant ( $P_{um}$ ), the specification ( $S_{um}$ ), and the controller ( $C_{um}$ ) using the Venn diagram below. The sets 1 and 2 are the unmarked behaviors of the closed loop where the elements in 1 violate the specification. The sets 3 and 4 are unmarked behaviors of the plant that are prevented by the controller where only the elements in 4 had to be prevented according to the specification. The sets 5, 6, and 7 are permitted by the controller/specification even though the plant is not capable of executing them.

We conclude our presentation by stating the supervisory control problem in terms of its inputs, outputs, and the requirements stated on them. The *inputs* are a plant (model) to be controlled, a specification (model) to be enforced, and the partitioning of  $\Sigma$  into the sets  $\Sigma_{uc}$  and  $\Sigma_c$ . The *output* is a controller (model) to be synthesized that satisfies the three discussed requirements *least restrictively*. The three requirements ensure the absence of undesirable behavior while the property of least restrictiveness ensures a maximal amount of desirable behavior (i.e., the set 3 in Figure 1.2|p.3 should be as small as possible).

The supervisory control problem as stated in [282] also used a second specification that describes marked and unmarked behaviors that must be feasible in the closed loop. However, the satisfaction of this requirement can also be checked a posteriori for a synthesized controller and its induced closed loop.

In addition to the introduction of the two properties of controllability and nonblockingness from before, we demonstrate violations of these two properties in the following example.

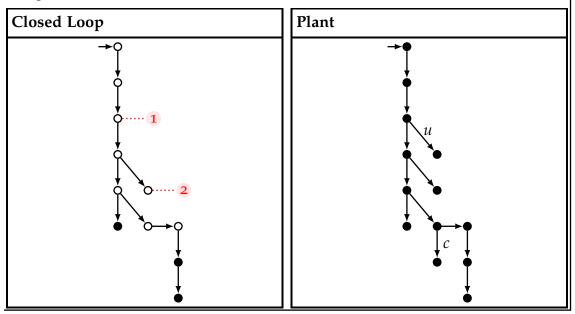

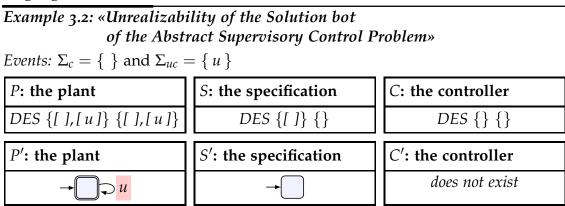

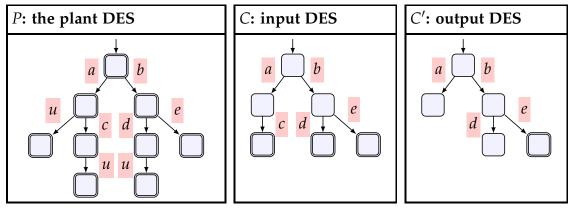

#### Example 1.1: «Properties of Controllability and Nonblockingness»

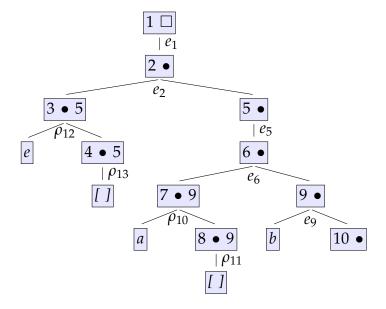

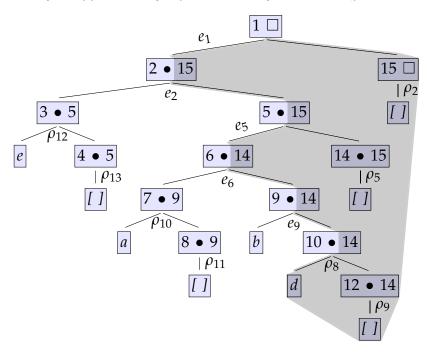

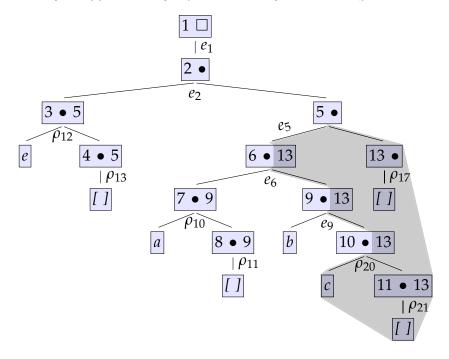

We represent the sets of (un)marked behaviors of components as trees where each path is an unmarked behavior and where each path to a filled node is a marked behavior. The left tree for the closed loop is to be understood as a subtree of the right tree for the plant: we label only the edges that are relevant to our reasoning with the event used in this step and assume  $u \in \Sigma_{uc}$  and  $c \in \Sigma_c$ . The closed loop violates the property of controllability at 1 because it prevents the occurrence of the uncontrollable event u at the designated unmarked behavior. The prevention of the step using the event c is no violation of controllability because c is controllable.

The closed loop violates the property of nonblockingness at 2 because the designated unmarked behavior cannot be continued to a marked behavior.

#### → Automata-based Concrete Supervisory Control Problem

Concrete instantiations of the presented supervisory control problem are obtained by (a) selecting formalisms for modelling plants, specifications, controllers, and closed loops, (b) defining for instances of these formalisms the sets of (un)marked behaviors, and (c) defining an operation that, based on the selected formalisms, constructs for a plant and a controller the induced closed loop. Every instance of the resulting concrete supervisory control problem is then given, as before, by a plant model, a specification model, and a set of events  $\Sigma$  that is partitioned into  $\Sigma_c$  and  $\Sigma_{uc}$  as described.

In this thesis, we employ classes of automata as formalisms to model the four above mentioned components with discrete states and an event-based communication as in [282]. The used classes of automata have the generation of (un)marked behaviors as a built-in concept and constructions for implementing the synchronous composition of plant and controller are available as well. Moreover, these constructions also ensure that the sets of (un)marked behaviors of the closed loop are equal to the intersection of the (un)marked behaviors of the plant and the specification as assumed in the supervisory control problem.

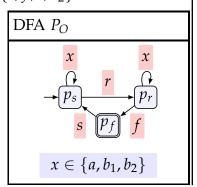

A first concrete supervisory control problem occurred already in [282]. In this concrete problem, to which we refer to as the *pure DFA problem*, all involved components are deterministic finite automata (DFA). Moreover, this concrete problem served as the foundation for the vast majority of further research results in the domain of supervisory controller synthesis thereafter.

In this thesis, we consider a second concrete supervisory control problem in which plants are modelled by DFA, where deterministic pushdown automata (DPDA) allow for more complex specifications, and result in DPDA controllers and closed loops. These DPDA can be understood as DFA that are endowed with a stack of unbounded depth, which permits the storage of information for later reuse at runtime and thereby increases the expressiveness of the specification. Technically, a stack is a sequence of symbols that can only be modified by adding symbols to its left or by removing symbols from its left and that only permits read access to the left-most symbol. The second concrete problem subsumes the pure DFA problem since each DFA is also a DPDA.

We now consider an instance of the second concrete supervisory control problem using a DPDA specification to motivate its meaningfulness.

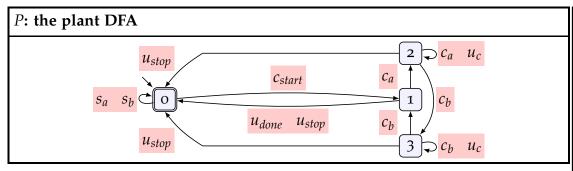

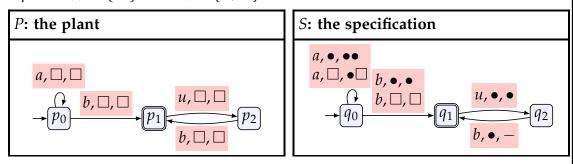

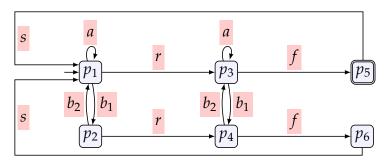

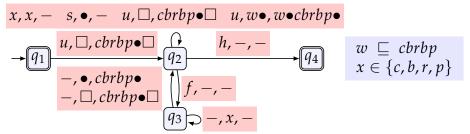

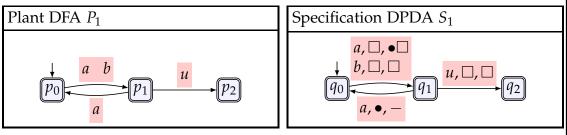

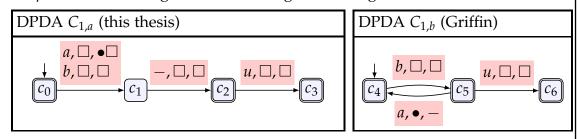

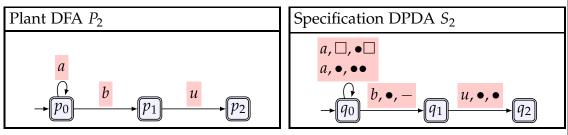

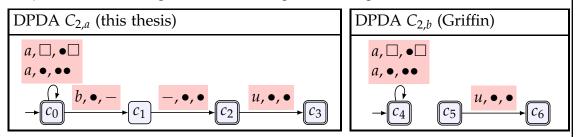

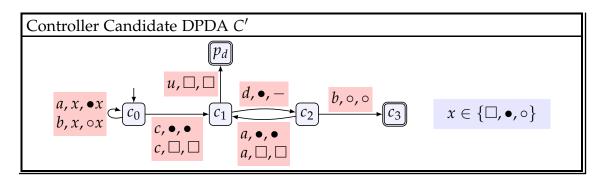

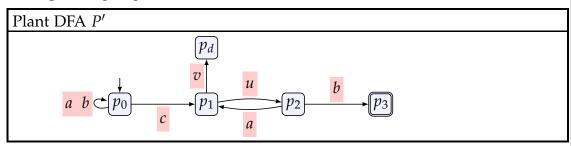

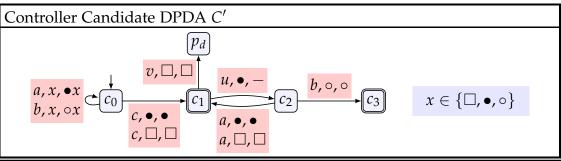

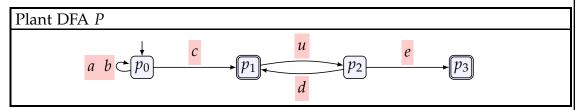

#### Example 1.2: «Validation of Schedules Using Controller Synthesis»

Description of Scenario: A schedule is provided to the plant by an external operator in the form of a list of events that are sent to the plant. The controller to be synthesized records the events of the schedule using its stack and permits only schedules that can be executed successfully to the end. The external operator then initiates the execution of the schedule by the plant and the controller ensures that the plant actually implements the entered schedule.

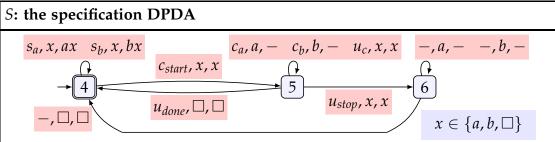

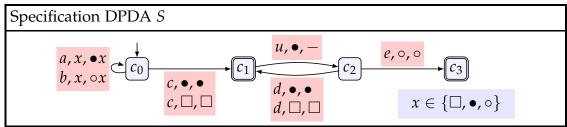

The notation used in the following visualizations for the DFA plant and the DPDA specification is discussed below.

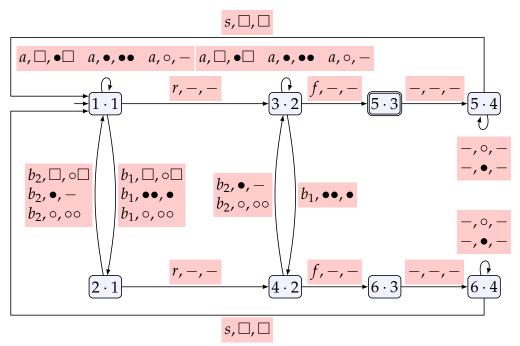

Notation and Semantics: DFA and DPDA are visualized as labelled directed graphs where nodes are called states. The states 0 and 4 are the initial states of the two automata as indicated by the arrow without source state pointing to them. These two states are also marking states as indicated by their double border line and correspond to the goal region for both automata to be reached. Two edges with common source and target are represented by only one edge where the two labels are given next to each other (e.g. the edge from state 1 to state 0 or from state 6 to state 6). The labels of the DFA edges have one component: the event executed. The labels of the DPDA edges have three components separated by commas: the event executed, the symbols that are popped from the top of the stack, and the symbols that are pushed onto the stack. The symbol — is used to denote the absence of symbols and events in a component and the placeholder x is used to specify multiple edges at once. We introduce DPDA in section 2.2|p.18 and subsection 6.2.6|p.112.

The steps of a DFA depend on the states contained in its *configurations*. An application of an edge replaces the state in a configuration, which must be the source state of the edge, with the target state of the edge. Iterated edge applications lead to sequences of configurations called derivations. See also Example 6.2 p.113 for an example of a derivation of another DPDA using two equivalent semantics.

Configurations of DPDA additionally contain the current stack. Moreover, the symbols given in the second component of a label of the edge, say  $w_1$ , must also be on top of the stack, i.e., the stack equals  $w_1v$  for some v, for applicability of an edge. A step then additionally updates the stack of the configuration to  $w_2v$ . The stack initially contains only the special symbol  $\square$ , which denotes the bottom of the stack and which stays there throughout any derivation. DPDA may perform silent steps (e.g. using the edge from state 6 to state 4) executing no event.

Description: In the initial state 0 of the plant, a schedule can be entered by an operator by executing the events  $s_a$  and  $s_b$ . These executions are to be recorded by the controller as specified in state 4 where a and b are pushed onto the stack for each execution of the events  $s_a$  and  $s_b$ , respectively (the symbol x allows for a more compact visualization using edge schemas).

The execution of the event  $c_{start}$  changes the state to 1, ends the phase of entering the schedule, and starts the phase in which the schedule is executed in some process from the concrete application domain. The events executed in this process are limited via the edges between the plant states 1–3 to sequences of at least one  $c_a$ , one  $c_b$ , and at least one  $c_b$  where further  $u_c$  events may be executed in between. The specification then also determines in state 5 how the controller must restrict the plant in these states to implement the schedule by popping symbols a and b from the stack for each execution of one  $c_a$  and  $c_b$ , respectively. When the schedule is completed (that is, when it is empty) and the state 1 has been reached again, the machine can return to the marking state 0 by executing the  $u_{stop}$  event. Finally, the operator may execute the event  $u_{stop}$  to interrupt the execution of the schedule, to reset the schedule in state 6 of the specification, and to also return to the initial state 4.

In this example, we assume that the set of events  $\Sigma$  is partitioned into the sets  $\Sigma_c = \{s_a, s_b, c_a, c_b, c_{start}\}$  and  $\Sigma_{uc} = \{u_c, u_{stop}, u_{done}\}$ . This means that the controller to be synthesized may prevent certain schedules from being entered (e.g. those schedules that request to start with an event  $c_b$ ). This check is carried out when the operator attempts to execute events  $s_a$  and  $s_b$  synchronously with the controller, that is, the schedule is validated before the event  $c_{start}$  is executed. Moreover, the controller to be synthesized can not prevent executions of the uncontrollable event  $u_c$  during schedule implementation.

Discussion: The usage of automata as an operational formalism leads to specifications that describe the usage of the stack by the prospective controller already in great detail. We take advantage of this by using the specification as an initial controller candidate, which is then restricted in further steps. Hence, the DPDA specification can refine the DFA plant because the specification does not distinguish between restrictions that are meant to refine the plant model and those that should be enforced by the prospective controller. However, this specification-based refinement of the plant is limited because the occurrence of events from  $\Sigma_{uc}$  is obtained from the plant alone for controllability.

Moreover, the usage of the stack of DPDA is used here to store the schedule to be implemented and to preemptively check its validity. Such an upfront check is not possible when using DFA specifications where a nonexecutable schedule (entered event-wise at runtime or stored entirely without formal foundation beforehand) would result in a deadlock at runtime.

Finally, resetting the schedule in state 6 requires an unbounded number of internal steps in the controller and, hence, the controller to be synthesized will not have a worst case execution time (WCET). However, a runtime environment that executes the controller can clear the stack in constant time in this example.

#### → *Relevance and Applicability of our Contributions*

The controller synthesis algorithm for solving the pure DFA problem from [282] has been applied successfully in an abundance of domains such as manufacturing, robotics, chemical process control, protocol design for communication, feature interaction management in telephony, queueing systems, traffic control, database systems, hybrid systems, and fault diagnosis [70, 71]. The development of a controller synthesis algorithm in this thesis for more expressive specifications given by DPDA enables the specification and enforcement of even more complex properties and maintains applicability in the described domains.

We determine three complementing use cases for the application of our concrete controller synthesis algorithm. These use cases take advantage of the fact that our algorithm, in the same way as the algorithm provided in [282] for the pure DFA problem, can not only be used to synthesize a controller but can also be used to verify that a provided controller candidate is satisfactory or to determine violations of controllability for a provided controller candidate. These algorithms refine an initially determined controller candidate by (a) identifying violations of the requirements and by (b) removing such violations in a follow up step while maintaining all behaviors without violations.

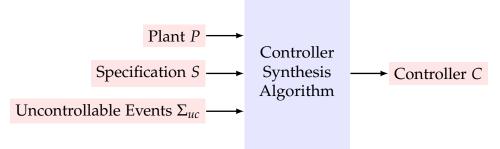

#### Figure 1.3: «Use Cases of Our Concrete Controller Synthesis Algorithm »

*Input/Output Situation for Controller Synthesis:* The standard controller synthesis (first use case) requires no human involvement, but defective inputs can lead to a waste of resources and the resulting controller may not have all required properties in some application contexts.

*Input/Output Situation for Controller Analysis:* The fully automatic analysis of a controller by means of a formal foundation can be useful if a manually constructed controller is to be verified (second use case) or when the specification as the initial controller candidate is to be adapted manually to remove violations by a domain expert (third use case).

We underline the applicability of DPDA specifications in the context of controller synthesis by introducing usage patterns for DPDA specifications (beyond what was used in the scheduling Example 1.2|p.5 above) and demonstrated their usefulness by applying them in examples in chapter 7|p.141. Moreover, DPDA can be much more succinct compared to equivalent DFA and, hence, their usage can ease the process of formalizing and managing also DFA specifications in terms of the required expertise and costs. Additional challenges originating in the use of DPDA and initial steps for their resolution, such as the potential absence of a WCET, are discussed in chapter 8|p.163.

Potential applications of our algorithm for solving the considered instantiation of the supervisory control problem with DPDA specifications in other contexts of computer science for software synthesis (e.g. for solving instances of the submodule construction problem) and extensions of this algorithm further strengthening applicability are discussed in chapter 8|p.163.

Before detailing on our concrete controller synthesis algorithm for the concrete supervisory control problem, we now discuss several additional aspects of systems not covered in this thesis and the alternative approach of manual implementation.

#### → *Scope of this Thesis*

The vast number of combinations of potential (kinds of) traits of the closed loop and the properties of the closed loop to be guaranteed results in a large multidimensional space of instances of control problems defined by means of suitable formalisms capable of capturing these characteristics. Consequently, research focuses on the construction of synthesis algorithms that solve meaningful (classes of) control problems as in [282] and on establishing negative results stating that certain (classes of) control problems defy solution as in [273].

An increased expressiveness allows for more precise modelling of the possible event sequences, but it complicates the problem of fully automatic synthesis because effective and efficient operations must be available (a) for the explicit construction of a closed loop and (b) for the analysis and enforcement of the properties that are required for controllers to be synthesized. For example, Turing machines are beneficial for modelling due to their high expressive power but only structural properties can be analyzed for them. Extending the pure DFA problem by using the more expressive DPDA for expressing specifications is thereby one further attempt to push the boundaries of fully automatic synthesis using one particular choice of formalisms.

Further aspects that have been considered in controller synthesis to increase expressiveness of models/specifications or to enhance decidability such as duration of events, delay between events, probabilistic step decisions, imperfect communication, asynchronous communication, costs, rewards, horizontal composition of controllers, and vertical composition of controllers are not in the scope of this thesis. However, we point out relevant connections and approaches for improving some aspects of our contributions in chapter 8|p.163.

→ Comparison of Fully Automatic Synthesis and Fully Manual Implementation We now discuss general benefits and impediments of fully automatic and fully manual controller construction as well as possibilities of their combination.

As pointed out before, automatic synthesis cannot replace manual construction in all cases because some control problems do not allow for a general solution in terms of a synthesis algorithm when the expressive power of the employed formalisms is too large. However, models of such formalisms that occur in an actual application may be simple enough for manual implementation. That is, there is no known process for obtaining synthesis algorithms from the domain expertise of developers of such manual solutions. We now assume a setting in which both approaches are applicable.

The development of synthesis algorithms imposes additional upfront costs compared to manual construction. However, once an effective, efficient synthesis algorithm has been constructed, the synthesis costs are mostly related to hardware costs and can be reduced by means of techniques such as multithreading while costs in manual construction are related to the required time and human personnel. Moreover, synthesis algorithms are limited to the formalisms for which they have been developed whereas the manual construction is more flexible as it does not require a general solution to *all* problem instances but rather the solution of the single problem instance at hand.

The verification of synthesis algorithms is of particular importance because (a) the manual analysis of each synthesis step would incur further costs and (b) errors in the synthesis algorithms could have arbitrarily adverse effects. After all, the correct-by-construction principle of controller synthesis is the key motivation for its application because the trustworthiness of constructed controllers is vital. Manual implementations of controllers are prone to error and require post-construction analysis using e.g. computer-aided techniques such as simulation, testing, or even more costly techniques of verification such as model checking or manual verification depending on the tractability of the analysis and the desired level of trustworthiness.

A precise understanding of the plant is required in either of the approaches. The manual approach does not depend on the usage of a certain formalism whereas synthesis algorithms require formal inputs. However, the formalization of assumptions on the plant and guarantees given in the form of the specification leads to a precise documentation. While this documentation requires an additional effort in the manual implementation approach, it automatically stays in sync with the synthesized controller. Defective plant/specification models are a common problem of both approaches as they result in controllers that induce closed loops with very limited or even unsafe behavior. While some kinds of modelling defects would be detected by experienced developers, validation techniques for these inputs are indispensable in both approaches.

A first combination of both approaches is given when controllers have been developed using both approaches. These two controllers can then be compared using back to back testing to reveal various implementation errors or modelling defects. Moreover, some controller synthesis algorithms such as the one in this thesis can be used to analyze a provided (possibly manually constructed) solution by verifying the absence of violations of the requirements or by returning descriptions of instances of such violations. Thereby, such synthesis algorithms allow for the combination of manual implementation and fully automatic synthesis with their respective advantages into a powerful technique as explained in the previous paragraph. We conclude this basic comparison of the two approaches by stating that the mentioned advantages and disadvantages may be of varying relevance in different application scenarios.

#### → Approach and Roadmap

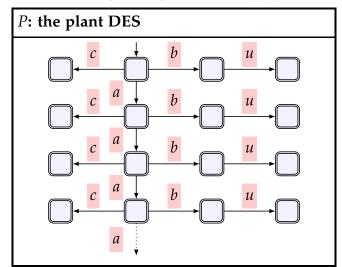

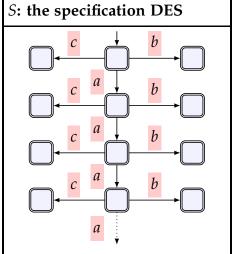

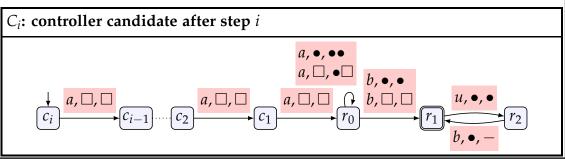

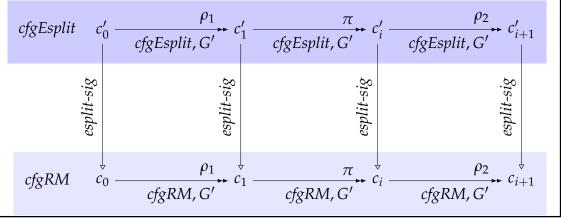

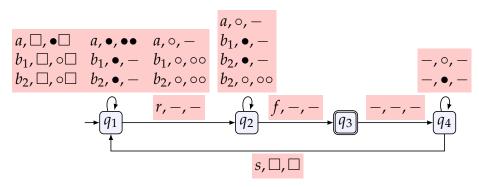

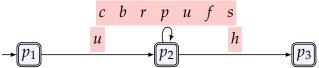

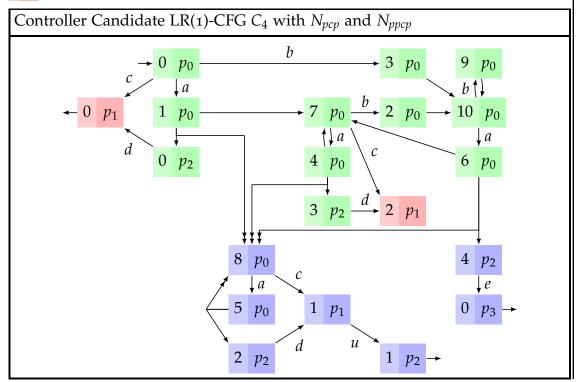

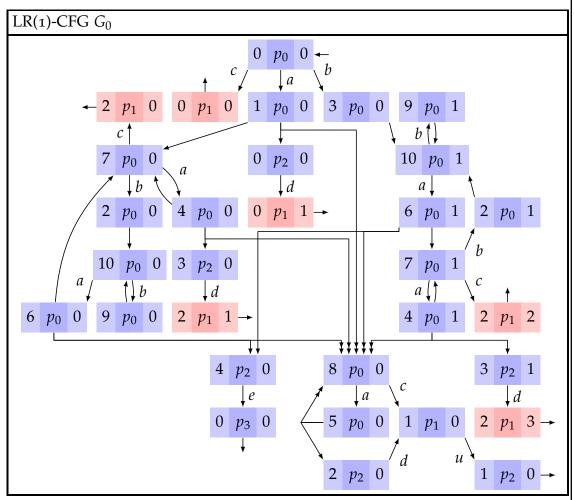

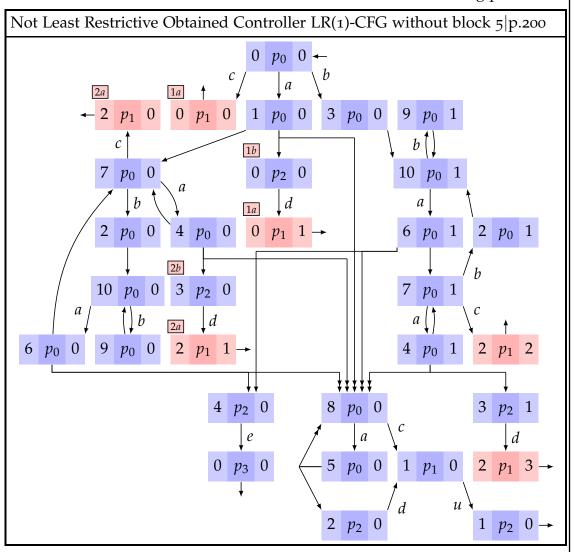

We define our automata-based concrete controller synthesis algorithm as an instantiation of an abstract controller synthesis algorithm, which is constructed using three building blocks for synchronous composition, for enforcing controllability, and for enforcing nonblockingness. The abstract algorithm operates on (abstract) discrete event systems (DES), which are obtained from automata by selecting their two generated languages.

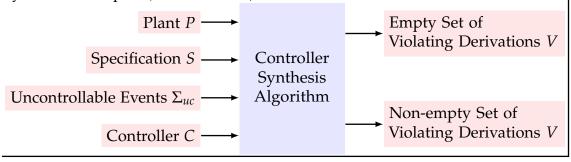

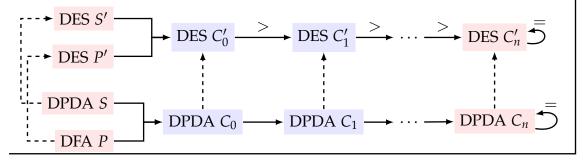

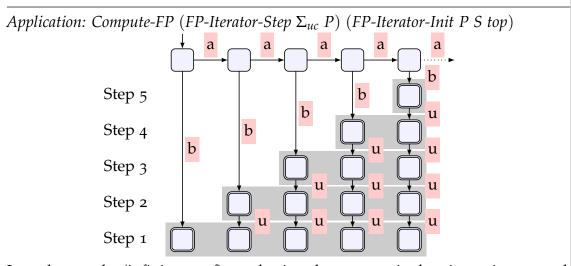

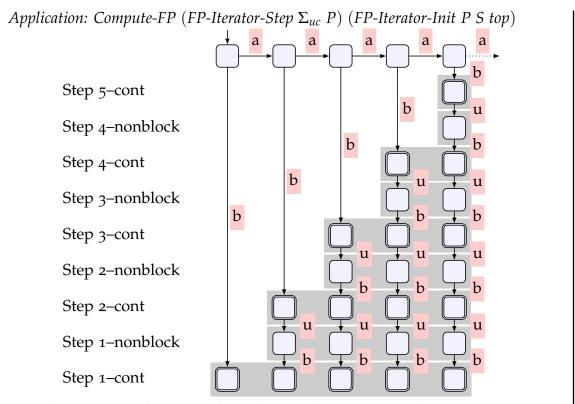

#### Figure 1.4: «Fixed-point Controller Synthesis Algorithm»

Abstract/Concrete Controller Synthesis Algorithm: The arrows represent dataflow and the rhombus represents a test on whether the fixed point has been computed, that is, whether the former controller candidate C is equal to the controller candidate C' obtained from enforcing controllability on C. For our formal verification, we define pre/post conditions for each of the three major building blocks used in this algorithm at the abstract level of DES as well as on the concrete level of automata.

In more detail, the abstract algorithm uses the DES specification *S* as a first controller candidate, computes the closed loop for this controller candidate and the given DES plant *P*, and then enforces the property of nonblockingness on this closed loop to obtain a controller candidate that satisfies the properties of nonblockingness and of specification satisfaction. The abstract algorithm then proceeds by computing a fixed point, starting with this controller candidate, and enforces controllability and nonblockingness alternatingly until the step of enforcing controllability does not further restrict the controller candidate.

We provide automata-based operations instantiating these three building blocks to obtain our concrete controller synthesis algorithm as an instantiation of the abstract algorithm. Consequently, both algorithms operate equivalently on the concrete DPDA controllers and on the abstract DES controllers.

Corresponding Fixed-point Computation of Both Algorithms: The concrete and the abstract synthesis algorithms operate equivalently when being started on the corresponding inputs: a DPDA specification S and a DFA plant P and on the DES abstraction S' and P', respectively. That is, the obtained controller candidates computed by the abstract algorithm will be the abstractions of the controller candidates computed by the concrete controller synthesis algorithm (visualized by the dashed arrow). This correspondence results from the construction of the concrete algorithm as an instantiation of the abstract algorithm and the compatibility of this instantiation with the pre/post conditions provided for both algorithms.

In this thesis, we rely on the interactive theorem prover Isabelle to ensure that our definitions and constructions are type-correct and that the proofs of our theorems are fault-free and omission-free. For this purpose, we developed a framework in Isabelle for the handling of the involved formalisms and the constructions applied on them in our synthesis algorithms. Note, we provide a brief overview of the syntax and semantics of Isabelle in Appendix B|p.227.

Some of the contributions of this thesis (in particular results from section 3.1 | p.33, chapter 4|p.45, section 5.3|p.82, and an example in section 7.3|p.147) have been published in [310, 301, 302] and unreferred in [307, 309]. Further publications [308, 306, 305] are not part of this thesis, but they lay the foundation for future applications of our concrete controller synthesis algorithm. The role of the coauthors for the development of the contributions presented in this thesis is covered in Appendix A|p.225.

#### Contents of this Thesis

> We introduce the abstract and concrete formalisms of discrete event systems, automata, context-free grammars, and Parsers used in our controller synthesis algorithms.

3 | p.31 Abstract and Concrete Supervisory Control Problems

We formally introduce the abstract and the concrete supervisory control problem, which are defined by means of discrete event systems and automata, respectively.

4|p.45 Abstract Controller Synthesis Algorithm for Discrete Event Systems

We formally introduce the above sketched abstract supervisory controller synthesis algorithm including our theory of fixed-point iterators ensuring the computation of the least restrictive DES controller.

5 | p.61 Concrete Controller Synthesis Algorithm for Deterministic Pushdown Automata

> We formally introduce the instantiation of the abstract supervisory control problem for DFA plants and DPDA specifications by providing detailed instantiations of the three major building blocks.

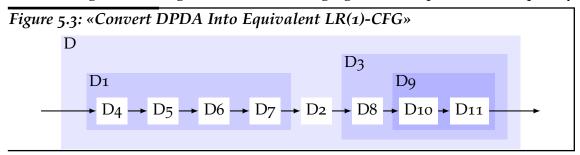

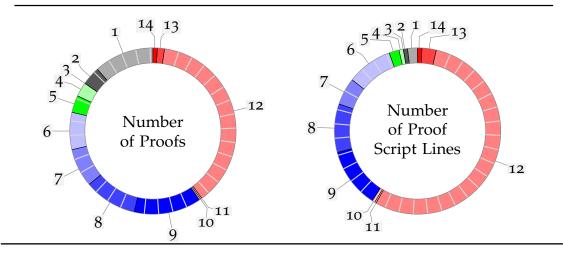

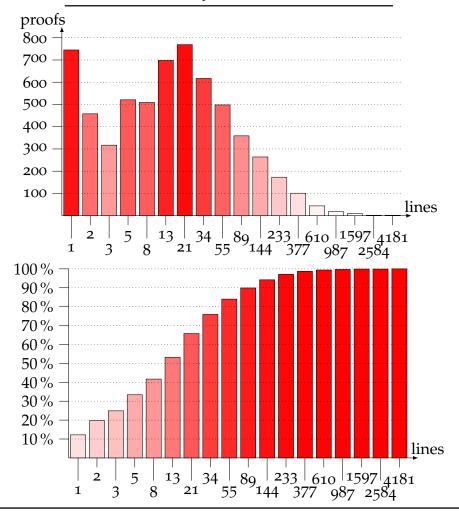

We discuss our general usage of Isabelle and also the Isabelle framework [303] developed specifically for the verification of our formal results. Moreover, we provide a proof idea for our novel proof of the fact that DPDA can be converted into LR(1)-CFG.

7 | p.141 Application and Prototype-based Evaluation

We demonstrate the implementability of our developed concrete controller synthesis algorithm by our prototype implementation CoSy [304]. Moreover, we discuss general applicability of the algorithm by means of usage patterns for DPDA specifications and also consider the efficiency of our implementation.

8 p.163 Related, Ongoing, and Future Work

We outline several meaningful results from ongoing research, provide a discussion of related work as well as recommendations for future work.

9 p.219 Summary and Conclusion

We conclude the thesis with an overall evaluation of our contributions and a discussion of their significance.

## Abstract and Concrete Discrete Event Systems

Our concrete controller synthesis algorithm presented in chapter 5|p.61 requires formalisms for describing plants, specifications, closed loops, and controllers. The inputs and outputs of this algorithm are modelled using the concrete formalisms of DFA and DPDA defined in this chapter. We also introduce extended pushdown automata (EPDA), Parsers, and context-free grammars (CFGs) for models occurring during computations of this algorithm. As a foundational theory, we formalize these concrete formalisms in Isabelle as instantiations of abstract parametrized theories by providing for each parameter of these theories and each concrete formalism an interpretation. We introduce the formalisms in this chapter at an intuitive level and provide relevant details of our Isabelle-based framework in section 6.2 |p.96.

Common to these concrete formalisms is that they define unmarked and marked languages as abstractions of actual and desired behavior. The abstract formalism of DES captures theses two kinds of languages in a novel unified representation, which has distinct benefits over approaches from the literature using only one of the two languages. That is, we benefit from their simplicity and the inclusion of both languages when defining the abstract supervisory control problem in section 3.1|p.33 as well as when defining the abstract synthesis algorithm in chapter 4|p.45 at this high level of abstraction. Moreover, we show in section 3.3|p.41 that DES are a suitable abstraction for models of the used concrete formalisms in the sense that the abstract and the concrete supervisory control problem from section 3.2|p.36 correspond to each other.

#### CONTENTS OF THIS CHAPTER

#### 2.1 | p.17 Discrete Event Systems

We introduce the abstract formalism of discrete event systems (DES) along with basic composition and comparison operations on them. Moreover, we demonstrate that DES determine a complete lattice by instantiating the corresponding parametrized theory.

#### 2.2 p.18 Extended Pushdown Automata

We introduce the concrete formalism of extended pushdown automata (EPDA) with various of its subclasses such as DFA, DPDA, and SDPDA.

#### 2.3 | p.22 Parsers

We introduce the concrete formalism of Parsers, of which instances occur in computations of our concrete controller synthesis algorithm.

#### 2.4 | p.27 Context-free Grammars

We introduce the concrete formalism of context-free grammars (CFGs), which is also used to represent intermediate models obtained in computations of our concrete controller synthesis algorithm.

#### 2.1. DISCRETE EVENT SYSTEMS

We use various concrete formalisms to represent plants, controllers, and specifications in our concrete controller synthesis algorithm in chapter 5|p.61. These formalisms determine for their models *marked and unmarked* languages over an event alphabet. On the one hand, these unmarked languages are prefix-closed and describe all possible evolutions of the models. On the other hand, the marked languages are contained in the unmarked languages and describe all desired evolutions in the sense of safe regions. Our umbrella notion of a discrete event system (DES) [310] captures these two languages and serves as an abstract representation for the models of the concrete formalisms employed in this thesis.

The following definition introduces the type  $\Sigma$  *des* of DES, the constructor *DES*, and the two selectors  $L_{um}^{des}$  and  $L_{m}^{des}$ . The constructor *DES* takes the unmarked language and the marked language (formally given by sets of lists) over elements from a type  $\Sigma$  to construct a DES. The two selectors  $L_{um}^{des}$  and  $L_{m}^{des}$  enable the extraction of the unmarked and the marked languages, respectively, from a DES.

```

Definition 2.1: «Type of DES»

datatype \Sigma des = DES L_{um}^{des} :: \Sigma list set L_{m}^{des} :: \Sigma list set

```

We define the predicate *valid-des* to identify the DESs that satisfy the constraints of prefix-closure and inclusion mentioned above.

```

Definition 2.2: «valid-des» definition valid-des :: \Sigma des \Rightarrow bool where valid-des D \equiv L_m^{des} D \subseteq L_{um}^{des} D \wedge prefix-closure (L_{um}^{des} D) = L_{um}^{des} D

```

While the separation of the event alphabet into controllable and uncontrollable events is required for controller synthesis, we do not include it in our formalization at this level.

DESs determine a complete lattice according to the instantiation of the abstract operations of a complete lattice as given in the following theorem where we make use of operations from the complete powerset lattice over words of events.

```

Theorem 2.1: "Discrete Event Systems Form a Complete Lattice"

bot \equiv DES \  \{ \  \} \  \}

top \equiv DES \  UNIV \  UNIV

less-eq \equiv \lambda A \  B. \  L_{um}^{des} \  A \subseteq L_{um}^{des} \  B \wedge L_{m}^{des} \  A \subseteq L_{m}^{des} \  B

less \equiv \lambda A \  B. \  less-eq \  A \  B \wedge A \neq B

inf \equiv \lambda A \  B. \  DES \  (L_{um}^{des} \  A \cap L_{um}^{des} \  B) \  (L_{m}^{des} \  A \cap L_{m}^{des} \  B)

sup \equiv \lambda A \  B. \  DES \  (L_{um}^{des} \  A \cup L_{um}^{des} \  B) \  (L_{m}^{des} \  A \cup L_{m}^{des} \  B)

Inf \equiv \lambda X. \  DES \  (\bigcap  (L_{um}^{des} \  X)) \  (\bigcap  (L_{m}^{des} \  X))

Sup \equiv \lambda X. \  DES \  (\bigcup  (L_{um}^{des} \  X)) \  (\bigcup  (L_{m}^{des} \  X))

```

By using this complete lattice later on, we deviate from [282] where a complete lattice over only one of both languages is used to state a supervisory control problem. The adequacy of DESs with their integrated handling of (un)marked languages as abstract representations of concrete formalisms for the purpose of controller synthesis is demonstrated in the subsequent chapters where the complete lattice of DES is used extensively in the definition of the abstract supervisory control problem in chapter 3|p.31 and the definition of our abstract controller synthesis algorithm in chapter 4|p.45.

#### 2.2. Extended Pushdown Automata

We introduce, amongst others, the automata formalisms of deterministic finite automata (DFA), deterministic pushdown automata (DPDA) [129], simple deterministic pushdown automata (SDPDA) [189], and deterministic extended pushdown automata (EDPDA) as restrictions of our novel formalism of extended pushdown automata (EPDA) from which they inherit various definitions, results, and semantics.

EPDA contain for every reasonable semantics a stack variable in their configurations, which stores words over an additional alphabet of stack elements. It may be used to record information on previously executed steps and to limit step applicability accordingly. For example, counting events and remembering their orderings enables the description of languages containing (a) bracketed/balanced words such as (()(())) with unbounded nesting depth, (b) words of the form  $u^{2\times n}v^n$  where the event u appears twice as often as the event v, and (c) words of the form  $wxw^{-1}$  that are odd-length palindroms with the center element x not contained in w.

We now define EPDA by introducing their type and by providing restrictions that determine the subset of (valid) EPDA. Note, the edges of EPDA used in this definition are defined subsequently.

#### Definition 2.3: «Type of EPDA and valid-epda»

If Q is a finite set of states,  $\Sigma$  is a finite set of events,  $\Gamma$  is a finite set of stack elements,  $\delta$  is a finite set of edges,  $q_0$  is an initial state in Q,  $\square$  is an end-of-stack element, and F is a finite set of marking states contained in Q, then EPDA G that satisfy *valid-epda* G are of the following form.

```

\{epda\text{-}states = Q, epda\text{-}events = \Sigma, epda\text{-}gamma = \Gamma, epda\text{-}delta = \delta, epda-initial = q_0, epda\text{-}eos = \Box, epda\text{-}marking = F \}

```

We do not partition the event alphabet  $\Sigma$  into controllable events  $\Sigma_c$  and uncontrollable events  $\Sigma_{uc}$  by introducing for them two separate record fields to obtain a general formalization that can also be used for other application domains without being cluttered by such a separation. However, we use the terminology of *marking states* from control theory; these states are also called accepting or final states in computer science.

The edges of EPDA (also called step labels), given in the definition above by the set  $\delta$ , have four different basic shapes. Firstly, each edge contains a source state  $q_1$  and a target state  $q_2$ . Secondly, each edge may contain an event a from the set  $\Sigma$ . Thirdly, each edge contains two words of stack elements to be popped and pushed, respectively. These two words may contain the end-of-stack element  $\square$  only at their end and, moreover, they must agree whether it occurs there.

#### Definition 2.4: «Type of Edges of EPDA and valid-epda-step-label»

If  $q_1$  and  $q_2$  are states from Q, a is an event from  $\Sigma$ ,  $s_1$  and  $s_2$  are words over  $\Gamma$  not containing  $\square$ , x = None or x = Some a, and  $(w_1, w_2) = (s_1, s_2)$  or  $(w_1, w_2) = (s_1 @ [\square], s_2 @ [\square])$ , then the edges e of an EPDA G that satisfy valid-epda-step-label G e are records of the following form.

```

\{edge-src=q_1, edge-event=x, edge-pop=w_1, edge-push=w_2, edge-trg=q_2\}

```

By considering the four cases explicitly we have the following forms.

We now introduce our custom semantics *epdaH* of EPDA by introducing the configurations, the step relation, and the derived notions of determinism as well as the generated marked and unmarked languages.

A configuration is given by a state, a stack of stack elements (which always has a trailing  $\square$  and which is to be read from left to right), and a history variable (which is used to log the events executed so far). The initial configuration is constructed by taking the initial state, the stack containing only the  $\square$  element, and an empty history.

#### Definition 2.5: «(Initial) Configurations of an EPDA in epdaH»

If q is a state from Q, s is a word over  $\Gamma$  not containing  $\square$ , and h is a word over  $\Sigma$ , then configurations of an EPDA are of the following form.

```

\{ epdaH-conf-state=q, epdaH-conf-history=h, epdaH-conf-stack=s @ [ <math>\square  ]\}

```

The unique initial configuration is  $(q_0, [\ ], [\ \Box\ ])$ .

The step relation defines how a configuration Pre can be modified by an edge Edge into a configuration Post. According to the four kinds of edge patterns from above, we also differentiate between four kinds of steps in the following definition. In the steps 1–4 the state is changed from  $q_1$  to  $q_2$ . In the steps 1 and 2 no event is executed whereas in steps 3 and 4 the event a is executed. In the steps 1 and 3 a strict prefix of the stack is popped (hence, the end-of-stack element  $\square$  is not popped) whereas in steps 2 and 4 the entire stack is popped.

#### Definition 2.6: «Step Relation epdaH-step-relation»

If  $q_1$  and  $q_2$  are states from Q, a is an event from  $\Sigma$ , h is a word over  $\Sigma$ , s,  $s_1$ , and  $s_2$  are words over  $\Gamma$  not containing  $\square$ , then there are the following kinds of steps.

```

Step 1 Edge: (q_1, None, s_1, s_2, q_2)

Pre:

(q_1, h, s_1 @ s @ [ \Box ])

Post:

(q_2, h, s_2 @ s @ [ \Box ])

Kind: execute no event, do not observe \square at end of stack

Step 2 Edge: (q_1, None, s_1 @ [ \Box ], s_2 @ [ \Box ], q_2)

Pre:

(q_1, h, s_1 @ [ \Box ])

Post:

(q_2, h, s_2 @ [ \Box ])

Kind: execute no event, observe \square at end of stack

Step 3 Edge: (q_1, Some \ a, s_1, s_2, q_2)

Pre:

(q_1, h, s_1 @ s @ [ \Box ])

Post:

(q_2, h @ [a], s_2 @ s @ [\Box])

Kind: execute event a, do not observe \square at end of stack

Step 4 Edge: \{q_1, Some\ a, s_1 @ [\square], s_2 @ [\square], q_2\}

Pre:

(q_1, h, s_1 @ [ \Box ])

(q_2, h @ [a], s_2 @ [\Box])

Post:

Kind:

execute event a, observe \square at end of stack

```

The iterated application of this step relation results in derivations that are (possibly infinite) sequences of configurations and applied edges. Moreover, initial derivations are those derivations that start in initial configurations and reachable configurations are the configurations in initial derivations.

An EPDA is then deterministic if (during any of its initial derivations) every two distinct steps that are applicable to a common configuration would add different events to the history variable.

#### Definition 2.7: «Determinism for epdaH»

An EPDA is deterministic in *epdaH* if, whenever an initial derivation leads to a configuration c and *epdaH-step-relation* G c  $e_1$   $c_1$  and *epdaH-step-relation* G c  $e_2$   $c_2$  are two applicable steps satisfying *epdaH-conf-history*  $c_1 \sqsubseteq epdaH-conf-history$   $c_2$ , then  $e_1 = e_2$  and  $c_1 = c_2$ .

Nondeterministic EPDA are more expressive than deterministic EPDA (EDPDA) because, for example, they can nondeterministically guess the center of palindroms of the form  $ww^{-1}$ . However, we expect that nondeterministic specifications lead to nondeterministic controllers that would force the runtime environment to maintain not only one current configuration, which would incur additional undesirable costs for the runtime environment and used hardware. Hence, we do not consider nondeterministic EPDA for modelling specifications or controllers in this thesis.

EDPDA are more expressive than DFA because DFA may not change the stack variable and therefore do not benefit from its existence.

The (un)marked language of an EPDA contains the (un)marked words that are obtained from initial derivations d as follows. The unmarked words are the histories contained in configurations of d. The marked words are the histories contained in configurations c of d where (a) c contains a state that is a marking state of the EPDA and (b) all configurations that follow c in d have the same history. The condition (b) is required to ensure a proper correspondence with the standard semantics epdaS (explained in more detail in section 6.2|p.96).

#### Definition 2.8: «unmarked-language and marked-language for epdaH»

The unmarked language of an EPDA is given by all words v over  $\Sigma$  such that some configuration c is reachable by some initial derivation d at index n such that epdaH-conf-history c = v.

An unmarked word is also in the marked language of the EPDA when, additionally, epdaH-conf-state c is a marking state from F and when the history variable is not extended after index n in the derivation d.

Based on the unmarked language and the marked language we define the DES that corresponds to a given EPDA.

#### Definition 2.9: «Conversion of EPDA Using epda-to-des to DES»

If G is an EPDA, then epda-to-des G is a DES defined as

DES (epdaH.unmarked-language G) (epdaH.marked-language G).

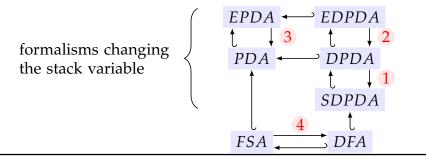

We obtain the other automata formalisms as follows. PDA are EPDA where the *edge-pop* component has length 1, FSA are PDA where the stack variable is never changed, DPDA are deterministic PDA (we use the predicate *valid-dpda*), and DFA are deterministic FSA. Moreover, SDPDA are DPDA (we use the predicate *valid-sdpda*) with only three kinds of edges: edges executing a single event while not modifying the stack, edges pushing a single element to the stack, and edges popping the single top-stack element.

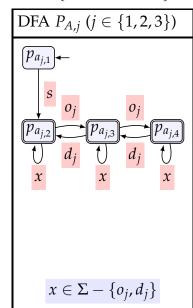

The following figure visualizes the relationship between these automata formalisms. The edges labelled with 1 and 2 are implemented by operations from our concrete controller synthesis algorithm introduced in chapter 5|p.61, the edge 3 is subsumed by our reasoning for edge 2, and the edge 4 is included only for completeness and is not part of our formalization.

#### Figure 2.1: «Relationship Between Automata Formalisms»

*Notation:*  $A \hookrightarrow B$  denotes that A is a subclass of B and  $A \longrightarrow B$  denotes that every  $a \in A$  can be translated into an equivalent  $b \in B$ .

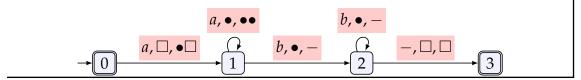

Finally, we provide an example of a DPDA for which no equivalent DFA exists.

#### Example 2.1: «DPDA Example»

The visualized DPDA G generates the marked language  $\{a^nb^n : n \in \mathbb{N}\}$  and the unmarked language  $\{a^nb^m : n, m \in \mathbb{N}, m \leq n\}$ . For this DPDA, the generated unmarked language is the prefix closure of the generated marked language, formally, epdaH.unmarked-language G = prefix-closure (epdaH.marked-language G). Hence, every unmarked word can be extended to a marked word.

#### 2.3. Parsers

Parsing theory is a fundamental and well established research domain in the field of computer science. Many Parser constructions such as LR(k)-Parsers have been developed for the parsing of programming languages. In this thesis we rely on the general notion of Parsers as presented in [325], which relies on [189].

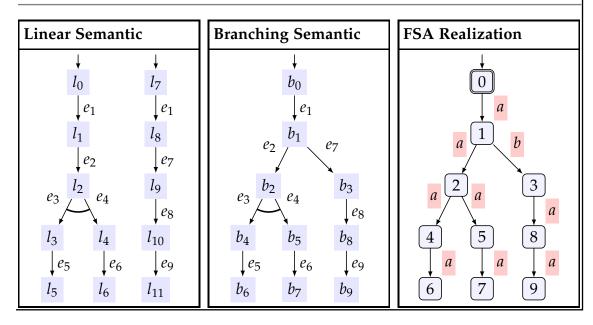

We consider two kinds of semantics in this thesis: branching and linear semantics (see Par. *Branching and Linear Semantics*|p.105 for more details). Branching semantics such as the semantics *epdaH* above for EPDA have a unique initial configuration from which every unmarked word can be executed. Linear semantics have one initial configuration for each potential unmarked word that is contained in the configuration in the form of a scheduler variable to be followed.

For modelling, Parsers have three features that are not available in EPDA.

Partial Execution: Parsers have a refined event mechanism compared to EPDA that decouples the observation of events (by a context) and their execution (by the Parser). That is, Parsers may execute only a prefix of the events observed in a step whereas EPDA execute an event in the step in which it is observed. The fixed scheduler variable, handled implicitly or explicitly in Parser semantics, consists of the observed events that have not been executed so far. These events have to be executed before any subsequently observed events. Also, in parsing theory, the term *look ahead* stands for the list of events (or its length) the Parser can observe in a single step. A longer look ahead allows for more concise Parsers because the look ahead restricts rule applicability as well: the look ahead must be compatible with the fixed scheduler as mentioned above and, in linear semantics, also with the scheduler. From this perspective each EPDA has a look ahead of at most 1 because the event component of an edge of an EPDA has a length of at most 1.

Parsers making use of this feature are intermediately obtained by our concrete controller synthesis algorithm and are translated into Parsers not using this feature by changing the stack variables such that they contain the fixed scheduler variable explicitly (see F2 in section 5.2.3|p.78).

Multiple Event Generation: Parsers may execute/observe any (finite) number of events in a single step whereas EPDA only allow the execution of at most one event at a time.

However, apart from some results from parsing theory, we assume in many of our proofs that the Parser at hand executes at most one event per step.

Processing Terminator: Parsers may fix a special end-of-input event parser-eoi (also called processing terminator) in their steps. Fixing this special event prevents the observation of further events in subsequent steps. That is, in a branching semantics, the Parser may decide to stop the observation of further events by fixing the parser-eoi event and, in a linear semantics, the Parser may detect the parser-eoi event at the end of the scheduler variable. In both cases the Parser may still execute previously observed and not yet executed events and may also operate on the stack.

Parsers observing the processing terminator are intermediately obtained by our concrete controller synthesis algorithm. We remove this usage without invalidating desired semantical properties (see F1 in subsection 5.2.2 p.73).

In our concrete controller synthesis algorithm in chapter 5|p.61, we obtain instances of LR(1)-Parsers, which are a subclass of deterministic Parsers. Then, we verify that these LR(1)-Parsers can be translated into DPDA while preserving the satisfaction of semantical properties that are of interest for controller synthesis.

We define Parsers, which make use of the notion of rules defined below.

#### Definition 2.10: «Type of Parser and valid-parser»

If N is a finite set of nonterminals,  $\Sigma$  is a finite set of events,  $q_0$  is an initial nonterminal in N, F is a finite set of marking nonterminals from N,  $\delta$  is a finite set of rules, and \$ is the end-of-input event from  $\Sigma$ , then Parsers G that satisfy *valid-parser* G are of the following form.

```

\{parser-nonterms=N, parser-events = \Sigma, parser-initial = q_0, parser-marking=F, parser-rules = \delta, parser-eoi = \$ \}

```

The rules of Parsers, given above by the set  $\delta$ , have two different shapes. The first shape is used to change the current stack by exchanging a certain prefix of it, to execute the events of a word  $v_1$ , and to fix the events of  $v_2$  that have not been fixed in an earlier step. The second shape is similar, but it fixes the processing terminator if it has not been fixed in an earlier step and, hence, after applying such a rule only the events from  $v_2$  can be executed subsequently.

#### Definition 2.11: «Type of Rules of Parsers and valid-parser-step-label»

If  $q_1$  and  $q_2$  are nonterminals from N,  $s_1$  and  $s_2$  are words over N,  $v_1$  and  $v_2$  are words over  $\Sigma$  not containing \$, and  $(w_1, w_2) = (s_1 @ s_2, s_2)$  or  $(w_1, w_2) = (s_1 @ s_2 @ [\$], s_2 @ [\$])$ , then the rules r of a Parser G that satisfy valid-parser-step-label G r are of the following form.

```

\{rule\text{-stack-pop } = s_1 @ [q_1], rule\text{-scheduler-pop } = w_1, rule\text{-stack-push} = s_2 @ [q_2], rule\text{-scheduler-push} = w_2 \}

```

By considering the two cases explicitly we have the following forms.

```

(s_1 @ [q_1], v_1 @ v_2 , s_2 @ [q_2], v_2)

(s_1 @ [q_1], v_1 @ v_2 @ [\$], s_2 @ [q_2], v_2 @ [\$])

```

The elements  $q_1$  and  $q_2$  may be interpreted as the source and target state of the rule, which are not separately stored as in the edges of EPDA. We also use the notation  $x_1 \mid y_1 \longrightarrow x_2 \mid y_2$  for rules  $(x_1, y_1, x_2, y_2)$  from [325].

We now introduce our custom semantics *parserHF* of Parsers by introducing the configurations, the step relation, and the derived notions of determinism as well as the generated unmarked and marked languages. The more simple and equivalent semantics *parserS* is explained in subsection 6.2.7 p.114.

A configuration is given by a stack of nonterminals, which is never empty and which is to be read from *right to left*, a history for storing the already observed events, which is extended to the right, and a fixed scheduler of the events observed but not yet executed. The initial configurations are constructed using the initial stack element, an empty history, and an empty fixed scheduler.

#### Definition 2.12: «(Initial) Configurations of a Parser in parserHF»

If s is a word over N, q is from N,  $v_1$  and  $v_2$  are words over  $\Sigma$  not containing f, f is f is a word over f in f in f in f in f in f in f is f in f

```

\{parser HF\text{-}conf\text{-}fixed = f, parser HF\text{-}conf\text{-}history = h, parser HF\text{-}conf\text{-}stack = s @ [ q ] \}

```

By considering the two cases explicitly we have the following forms.

$$(v_2, v_1 @ v_2, s @ [q])$$

$(v_2 @ [\$], v_1 @ v_2, s @ [q])$

The unique initial configuration is  $([ ],[ ],[ q_0 ])$ .

The step relation determines how a configuration Pre can be modified by a rule Rule into a configuration Post. We distinguish between seven kinds of steps due to the interplay between fixed scheduler and history variable. In all seven steps the stack is changed by replacing the top-most elements  $s_1 @ [ q_1 ]$  by  $s_2 @ [ q_2 ]$ . Also, in each of the seven steps the rule must respect the fixed scheduler in the sense that the component rule-scheduler-pop of the rule is either a prefix of the fixed scheduler of the Pre-configuration or has this fixed scheduler as a prefix.

#### Definition 2.13: «Step Relation parserHF-step-relation»

If  $q_1$  and  $q_2$  are from N, s,  $s_1$ , and  $s_2$  are words over N, h,  $v_1$ ,  $v_2$ , and  $v_3$  are words over  $\Sigma$  not containing \$, and  $v_1$ ,  $v_2$ , and  $v_3$  are not empty, then there are the following kinds of steps.

```

Step 1a

Rule: (s_1 @ [q_1], v_1 @ v_2 @ v_3, s_2 @ [q_2], v_3)

Pre: (v_1 , h , s @ s_1 @ [q_1])

Post: (v_3, h @ v_2 @ v_3, s @ s_2 @ [q_2])

Kind: (\neg A), (\neg B), (\neg C), (D), (E)

Rule: (s_1 @ [q_1], v_1 @ v_2 @ v_3, s_2 @ [q_2], v_2 @ v_3)

Step 1b

Pre: (v_1 @ v_2 , h , s @ s_1 @ [q_1])

Post: \{v_2 @ v_3, h @ v_3, s @ s_2 @ [q_2]\}

Kind: (\neg A), (\neg B), (\neg C), (D), (\neg E)

Rule: (s_1 @ [q_1], v_1 @ v_2, s_2 @ [q_2], v_2)

Step 1c

Pre: (v_1 @ v_2 @ v_3, h, s @ s_1 @ [q_1])

Post: \{v_2 @ v_3, h, s @ s_2 @ [q_2]\}

Kind: (\neg A), (\neg B), (\neg C), (\neg D), (\neg E)

Rule: (s_1 @ [q_1], v_1 @ v_2 @ v_3 @ [\$], s_2 @ [q_2], v_3 @ [\$])

Step 2a

Pre: (v_1 , h , s @ s_1 @ [q_1])

Post: (v_3 @ [\$], h @ v_2 @ v_3, s @ s_2 @ [q_2])

Kind: (\neg A), (B), (C), (D), (E)

Rule: (s_1 @ [q_1], v_1 @ v_2 @ v_3 @ [\$], s_2 @ [q_2], v_2 @ v_3 @ [\$])

Step 2b

Pre: (v_1 @ v_2 , h , s @ s_1 @ [q_1])

Post: \{v_2 @ v_3 @ [\$], h @ v_3, s @ s_2 @ [q_2]\}

Kind: (\neg A), (B), (C), (D), (\neg E)

Rule: (s_1 @ [q_1], v_1 @ v_2, s_2 @ [q_2], v_2)

Step 3a

Pre: (v_1 @ v_2 @ v_3 @ [\$], h, s @ s_1 @ [q_1])

Post: \{v_2 @ v_3 @ [\$], h, s @ s_2 @ [q_2]\}

Kind: (A), (B), (\neg C), (\neg D), (\neg E)

Step 3b Rule: (s_1 @ [q_1], v_1 @ v_2 @ [\$], s_2 @ [q_2], v_2 @ [\$])

Pre: (v_1 @ v_2 @ [\$], h, s @ s_1 @ [q_1])

Post: (v_2 @ [\$], h, s @ s_2 @ [q_2])

Kind: (A), (B), (C), (\neg D), (\neg E)

```

*Legend:* We use the following classification of the steps also explained below.

- (*A*) \$ is fixed in the Pre-configuration (i.e., parserHF-conf-fixed ends with \$)

- (*B*) \$ is fixed in the Post-configuration (i.e., *parserHF-conf-fixed* ends with \$)

- (*C*) \$ is observed by the rule (i.e., *rule-scheduler-pop* ends with \$)

- (D) new events are executed (i.e., new events are added to the history)

- (E) the fixed scheduler of the Pre-configuration is entirely removed

Firstly, the labels (A)–(C) are related to the status and the observation of the processing terminator: the processing terminator \$ is not fixed in the Pre- and Post-configurations of steps 1a–1c and in the Pre-configurations of steps 2a and 2b. Vice versa, the processing terminator \$ is fixed in the Post-configurations of steps 2a and 2b and in the Pre- and Post-configurations of steps 3a and 3b. Secondly, the label (D) is related to the execution of further events: in steps 1a, 1b, 2a, and 2b further events are executed and possibly fixed. Finally, the label (E) is related to the removal of the fixed scheduler: in steps 1a and 2a the entire fixed scheduler is removed whereas in the other steps 1b, 1c, 2b, 3a, and 3b a nonempty suffix of the fixed scheduler is retained.

Intuitively a given Parser is deterministic if (during any initial derivation) every two distinct applicable steps would add different events to the history variable.

#### Definition 2.14: «Determinism for parserHF»

A Parser is deterministic in the semantics parserHF if, whenever a given initial derivation reaches a certain configuration c and parserHF-step-relation G c  $e_1$   $c_1$  and parserHF-step-relation G c  $e_2$   $c_2$  are two applicable steps that satisfy that parserHF-conf-history  $c_1 \sqsubseteq parserHF$ -conf-history  $c_2$ , then  $e_1 = e_2$  and  $c_1 = c_2$ .

The (un)marked language of a Parser contains the (un)marked words that are obtained from initial derivations d as follows. The unmarked words are the histories contained in configurations of d. The marked words are the histories contained in configurations c of d where (a) the stack of c ends in a marking stack element of the Parser and (b) all configurations that follow c in d have the same history. As for EPDA, the condition (b) is required to ensure a proper correspondence with the standard semantics parserS (explained in more detail in section 6.2|p.96).

#### Definition 2.15: «unmarked-language and marked-language for parserHF»

The unmarked language of a Parser is given by all words v over  $\Sigma$  such that some configuration c is reachable by some initial derivation d at index n such that parserHF-conf-history c=v.

For a word to be in the marked language of the Parser we additionally require that parserHF-conf- $stack\ c$  is of the form  $s\ @\ [\ q\ ]$  where q is a marking stack element from F and that the history variable is not extended after index n.

Based on the unmarked language and the marked language we define the DES that corresponds to a given Parser.

# Definition 2.16: «Conversion of Parsers Using parser-to-des to DES» If G is a Parser, then parser-to-des G is a DES defined as DES (parserHF.unmarked-language G) (parserHF.marked-language G).

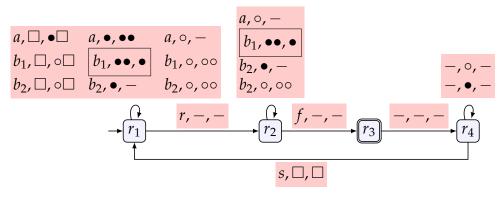

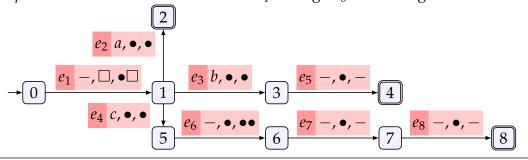

In the following example, we present a Parser that does not rely on any of the three Parser-specific features introduced above.

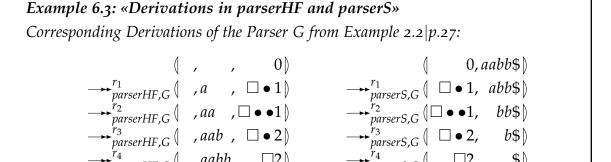

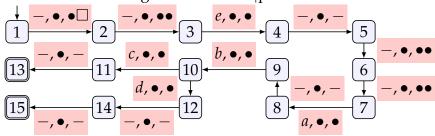

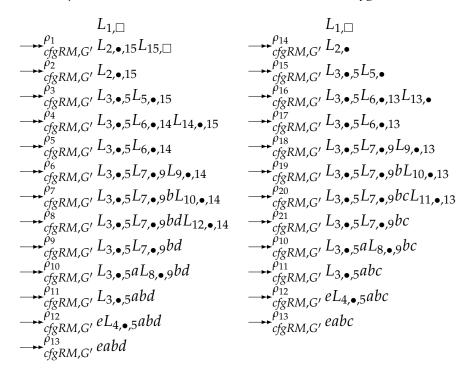

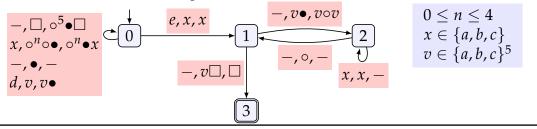

#### Example 2.2: «Parser Example»

The Parser with the initial stack element 0, the marking stack elements  $\{0,3\}$ , and the five rules below has the same unmarked and marked language as the EPDA from Example 2.1|p.22.

$r_1: 0 \mid a \longrightarrow \square \bullet 1 \mid$   $r_4: \bullet 2 \mid b \longrightarrow 2 \mid$   $r_2: \bullet 1 \mid a \longrightarrow \bullet \bullet 1 \mid$   $r_5: \square 2 \mid \longrightarrow 3 \mid$   $r_3: \bullet 1 \mid b \longrightarrow 2 \mid$

#### 2.4. Context-free Grammars

In this section, we introduce the well-known formalism of context-free grammars (CFGs) from [80] and their subclass of LR(k)-CFGs from [189].

Intuitively, CFGs are rule-based replacement systems operating on words over two kinds of elements: events (also called terminals in other contexts) and nonterminals. In each step (of any semantics of CFGs) a single nonterminal that is contained in the configuration is replaced by a (possibly empty) replacement list according to one production of the CFG.

The parsing of programming languages, described by LR(k)-CFG, using LR(k)-Parsers was introduced in [189] and more technical details and results for LR(k)-CFG have been summarized in a consistent notation in [325]. In particular, the LR(k)-CFGs can be parsed deterministically with look ahead k. Also, these Parsers are *correct-prefix-parsers* [325, Volume II, Theorem 9.1, p. 291] stating that errors are detected when they occur, which (a) supports users in finding the syntax errors in their program to be parsed and which (b) is fundamentally required in our control setting as it allows us to execute *only* the desired events.

In the fields of computer science and discrete control theory, the formalism of CFG is not commonly used for the description of running systems. One reason may be that the definition of LR(1)-CFG is more complex compared to the definitions of determinism for formalisms such as DPDA resulting in a more difficult modelling processes of deterministic systems. The formalism of LR(1)-CFG is used in our concrete controller synthesis algorithm from chapter 5|p.61| where we also provide details on their equivalence to DPDA and LR(1)-Parsers.

We now define CFG already using productions that are defined subsequently.

### Definition 2.17: «Type of CFG and valid-cfg»

If N is a finite set of nonterminals,  $\Sigma$  is a finite set of events, S is an initial nonterminal in N, and P is a finite set of productions, then CFGs G that satisfy valid-cfg G are of the following form.

```

(cfg-nonterminals=N, cfg-events=\Sigma, cfg-initial=S, cfg-productions=P)

```

As for EPDA and Parsers, we do not partition the event alphabet  $\Sigma$  into controllable events  $\Sigma_c$  and uncontrollable events  $\Sigma_{uc}$  by introducing for them two separate record fields to obtain a general formalization of CFGs.

The productions of CFGs, given above by the set P, have only one shape. In general, a production is given by a left-hand-side nonterminal and a right-hand-side word over nonterminals and events of the CFG. Formally, we distinguish between nonterminals and events by using words ranging over a custom datatype where the elements beA A and beA b represent nonterminals A and events b, respectively. Informally, we omit the constructors beA and beB and use capital and lower case letters for nonterminals and events, respectively. Given a CFG with a set of nonterminals N and a set of events  $\Sigma$  we define the set of elements of such words by bi-elem-domain N  $\Sigma = \{beA A \mid A . A \in N\} \cup \{beB b \mid b . b \in \Sigma\}$ .

#### Definition 2.18: «Type of Production of CFGs and valid-cfg-step-label»

If A is a nonterminal from N, w is a word over *bi-elem-domain* N  $\Sigma$ , then the productions p of a CFG G that satisfy *valid-cfg-step-label* G p are of the following form.

$$(prod-lhs = A, prod-rhs = w)$$

We introduce subsequently the three semantics *cfgSTD*, *cfgLM*, and *cfgRM* for CFG. They share identical definitions for the (initial) configurations, the generated unmarked language, and the generated marked language, but they differ in their step-relations as explained below.

A configuration of a CFG is given by a word over the set *bi-elem-domain* N  $\Sigma$  and the initial configuration is constructed by taking only the initial nonterminal S.