## A write time of $6\ ns$ for quantum dot–based memory structures

Cite as: Appl. Phys. Lett. **92**, 092108 (2008); https://doi.org/10.1063/1.2890731 Submitted: 22 January 2008 • Accepted: 10 February 2008 • Published Online: 04 March 2008

M. Geller, A. Marent, T. Nowozin, et al.

## ARTICLES YOU MAY BE INTERESTED IN

10<sup>6</sup>years extrapolated hole storage time in GaSb / AlAs quantum dots Applied Physics Letters **91**, 242109 (2007); https://doi.org/10.1063/1.2824884

Quantum dot based memory devices: Current status and future prospect by simulation perspective

AIP Conference Proceedings 1586, 20 (2014); https://doi.org/10.1063/1.4866723

Hole-based memory operation in an InAs/GaAs quantum dot heterostructure Applied Physics Letters **95**, 242114 (2009); https://doi.org/10.1063/1.3275758

🗊 QBLOX

Shorten Setup Time Auto-Calibration More Qubits

Fully-integrated Quantum Control Stacks Ultrastable DC to 18.5 GHz Synchronized <<1 ns Ultralow noise

visit our website >

View Online

Appl. Phys. Lett. **92**, 092108 (2008); https://doi.org/10.1063/1.2890731 © 2008 American Institute of Physics.

## A write time of 6 ns for quantum dot-based memory structures

M. Geller,<sup>1</sup> A. Marent,<sup>1,a)</sup> T. Nowozin,<sup>1</sup> D. Bimberg,<sup>1</sup> N. Akçay,<sup>2</sup> and N. Öncan<sup>2</sup> <sup>1</sup>Institut für Festkörperphysik, Technische Universität Berlin, Hardenbergstrasse 36, 10623 Berlin, Germany <sup>2</sup>Department of Physics, Faculty of Science, Istanbul University, 34134 Vezneciler, Istanbul, Turkey

(Received 22 January 2008; accepted 10 February 2008; published online 4 March 2008)

The concept of a memory device based on self-organized quantum dots (QDs) is presented, enabling extremely fast write times, limited only by the charge carrier relaxation time being in the picosecond range. For a first device structure with embedded InAs/GaAs QDs, a write time of 6 ns is demonstrated. A similar structure containing GaSb/GaAs QDs shows a write time of 14 ns. These write times are independent of the localization energy (e.g., storage time) of the charge carriers and at the moment are limited only by the experimental setup and the parasitic cutoff frequency of the *RC* low pass of the device. © 2008 American Institute of Physics. [DOI: 10.1063/1.2890731]

Mainly, two memory types dominate the present semiconductor memory market: the dynamic random access memory<sup>1</sup> (DRAM) and the flash<sup>2-4</sup> memory. Both types have their advantages and disadvantages concerning access speed. endurance, and storage time. DRAMs provide fast access times (below 20 ns)<sup>5</sup> and good endurance (>10<sup>15</sup> read/write cycles), but the stored information has to be refreshed within tens of milliseconds (they are volatile). Flash memories are nonvolatile with storage times in the order of 10 years but exhibit a bad endurance  $(15^6)$  and a slow write speed  $(\sim \mu s)$ . Development of faster flash memories with better endurance is presently actively pursued. Phase change memories and magnetic random access memories,<sup>o</sup> (MRAM) are two alternative memory concepts which have the potential to replace todays DRAM and/or flash memory. Both concepts are less scalable than charge-based memories. Therefore, charge-based memory concepts superior to present ones concerning speed, retention time, cost, and power consumption are searched for. They have to be scalable to a feature size below 32 nm to extend Moores' law beyond the year 2012.

Self-organized quantum dots (QDs) might provide very fast write times due to their large capture cross section.<sup>8</sup> Earlier work on a nanowire-based memory<sup>9</sup> with multiple InAs QDs separated by thin InP barriers already showed a minimum write time of 15 ns, limited by the resonant tunneling time through the barriers. In this letter, we present a memory concept<sup>10,11</sup> based on QDs, which should enable very fast write times (<ns) independent of the carrier storage time, e.g., in combination also with a long storage time (>10 years). The write time in our concept is limited only by the charge carrier relaxation time from the band edge into the QD states, which is below picoseconds at room temperature,<sup>8,12</sup> more than four orders of magnitude faster than the write time of a DRAM cell. We previously showed for InAs QDs with an Al<sub>0.9</sub>Ga<sub>0.1</sub>As barrier a storage time of seconds at room temperature and proposed more than 10<sup>6</sup> years for GaSb QDs in an AlAs matrix.<sup>13</sup> Here, we demonstrate a fast write time of 6 ns, three orders of magnitude faster than that of present flash memories, for such a QDbased memory structure. This value is at the moment limited only by the parasitic cutoff frequency of the RC low pass.

Much faster write times are expected for improved device structures.

In a conventional flash memory, a Si-based floating gate placed between two SiO<sub>2</sub> barriers stores the electrons. The SiO<sub>2</sub> barriers have the enormous energetic height of 3.2 eV, essential to store electrons for more than 10 years at room temperature. The barrier height is fixed, and during the write process, the floating gate has to be charged with electrons by Fowler–Nordheim tunneling and/or hot-electron injection. Both charging mechanisms cause the two main disadvantages of a flash cell: the slow write time in the order of microseconds and the poor endurance in the order of  $10^6$ write/erase cycles.

Our concept of a QD-based memory eliminates the drawbacks of the "fixed height" of SiO<sub>2</sub> barriers by using a tunable barrier height which can be decreased during the write operation. In addition, using III-V compound semiconductors allows band structure engineering with an *adjustable* localization energy which determines the charge carrier storage time.<sup>13,14</sup> Our concept consists of the following three parts:

- (1) The QDs are used as storage units for the charge carriers (holes or electrons).

- (2) The QDs are placed inside a *p-n* or *p-i-n* diode structure, nearby or inside the depletion region. By modifying the depletion region, the memory operations—storage, writing, and erasing—are realized.

- (3) The read operation is realized by placing a twodimensional electron gas below the QD layer, like in a conventional flash cell.<sup>6</sup> This principle was already demonstrated for the readout process in a QD-based memory by Balocco *et al.*<sup>15</sup>

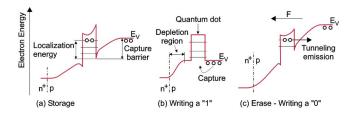

The charge carrier storage and the write/erase operations work as follows, schematically depicted in Fig. 1: At zero bias, the doping concentration and the location of the QDs in the structure are adjusted such that the QDs are inside the depletion region. This represents the storage situation [Fig. 1(a)]. The width of the depletion region can be adjusted by an applied external bias. A forward bias reduces the width, and the QDs are outside the depletion region [Fig. 1(b)]. Hence, in contrast to the flash memory concept with fixed SiO<sub>2</sub> barrier height, the capture barrier is eliminated and very fast capture into the QD states is possible. To erase the in-

0003-6951/2008/92(9)/092108/3/\$23.00

<sup>&</sup>lt;sup>a)</sup>Electronic mail: marent@sol.physik.tu-berlin.de.

FIG. 1. (Color online) Schematic illustration of the storage (a), write (b), and erase (c) processes in the proposed QD-based flash memory based on hole storage. A fast write time is expected since the carrier capture process occurs directly from the band edge.

formation, a high reverse bias is applied to the diode [Fig. 1(c)]. The QDs are inside the depletion region with a strong electric field enabling tunneling of the charge carriers through the triangular barrier.

To prove the feasibility of this concept and to confirm fast write times independent of the storage times, we have measured the write time of two different structures containing type I InAs/GaAs and type II GaSb/GaAs QDs. The first structure contains InAs QDs embedded in a slightly *p*-doped GaAs matrix ( $p \sim 3 \times 10^{16}$  cm<sup>-3</sup>). On its top, a highly *n* doped ( $n \sim 7 \times 10^{18}$  cm<sup>-3</sup>) GaAs cap layer was deposited forming the  $n^+$ -*p* diode. The sample structure is described in detail in Ref. 16. The InAs QDs can now be charged with holes in a controlled way by an applied reverse bias. The second structure contains GaSb QDs inserted also in a slightly *p*-doped region of a  $n^+p$ -diode structure. This structure is described in detail in Ref. 17.

The holes in the QDs (which represent the stored information) were here read out by measuring the capacitance of the p-n diode. The capacitance of a diode structure with embedded QDs depends on the number of holes stored inside the depletion region. A larger capacitance corresponds to unoccupied QDs ("0"), while a smaller capacitance represents a "1," in which the QDs are filled with holes.

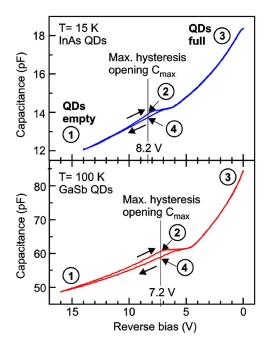

Figure 2 shows the switching between the two states by a hysteresis curve of the capacitance for both samples. At a

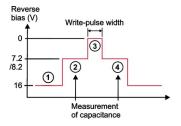

FIG. 3. (Color online) Operation principle for measuring the write time; the labeled numbers refer to the numbers in Fig. 2.

reverse bias of 16 V (point 1), the charge carriers tunnel out of the QDs (erasing of the information). If the reverse bias is now swept from 16 V to the storage situation at 8.2 V (InAs QDs) or 7.2 V (GaSb QDs), the QDs are empty and a larger capacitance is observed (point 2). If the bias is swept to 0 V (point 3), the QDs are charged with holes and a smaller capacitance is observed upon sweeping back to the storage situation (point 4). The maximum hysteresis opening is now defined at the storage position as the difference between both capacitance values for 0 and 1 states.<sup>18</sup>

To study the limit of the write time, series of write pulses were applied with decreasing pulse widths down to 300 ps. The operation principle is schematically depicted in Fig. 3. The cycle started with a 10 s long erase pulse at  $V_r = 16$  V (point 1). Then, the capacitance of the device structure was measured at the storage position (point 2) at 7.2 V (GaSb QDs) and 8.2 V (InAs QDs). A write pulse of  $V_r=0$  V was applied to the device (point 3), and the capacitance was again measured at the storage situation (point 4). The maximum hysteresis opening  $C_{\text{max}}$  was plotted versus the write-pulse width in Fig. 4. The limit of the write time is reached when the QDs are not sufficiently charged anymore. The hysteresis opening  $C_{\text{max}}$  vanishes, and we define the limit as a drop in  $C_{\text{max}}$  to 50%. One measurement cycle takes tens of seconds. Therefore, we reduced the temperature down to 25 K for the InAs QDs to obtain a hole storage time that is longer than one cycle of the write time measurements. Analogously, for the GaSb QDs, a higher temperature of 100 K can be used to get a sufficiently long storage time, as the localization energy in GaSb QDs is more than twice as high than in InAs QDs.

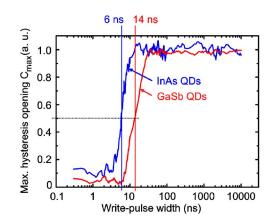

A minimum write time of 6 ns for the InAs QD sample is obtained. For the GaSb QD sample—having a hole localization energy which is more than twice as high—we mea-

FIG. 4. (Color online) Maximum hysteresis opening  $C_{\text{max}}$  for varying writepulse width. The InAs QD memory is sufficiently charged for write pulses down to 6 ns. Analogously, the information in the GaSb QD memory structure can be written down to 14 ns.

sured a write time of 14 ns, three orders of magnitude faster than that of present flash cells. Both write times are almost equal and already in the order of the write time of a DRAM cell. The measured write times are at the moment only limited by the experimental setup and the parasitic cutoff frequency of the RC low pass of the devices, which are slightly different. This assumption is confirmed by additional measurements at different temperatures on the same device which showed a temperature-independent write time and by previous measurements<sup>8</sup> of the same structure, in which average hole capture and relaxation times were found to be in the order of picoseconds. Therefore, much faster write times below 1 ns, as well at room temperature, which are independent of the localization energy should be feasible for improved memory structures having higher external cutoff frequencies.

In conclusion, we have presented a memory concept based on self-organized QDs, enabling very fast write times in combination with long storage times. The physical limitation of the write time of such a QD-based memory is given by the relaxation time of the charge carriers known to be in the picosecond range. We demonstrated here a write time of 14 ns for GaSb/GaAs QDs and 6 ns for InAs/GaAs QDs. These write times are at the moment limited by the experimental setup and the parasitic cutoff frequency of the RC low pass of the devices. Faster write times below 1 ns are expected for improved device structures.

The work was partly funded by the SANDiE Network of Excellence of the European Commission, Contract No. NMP4-CT-2004-500101, by the QD-Flash project in the framework of ProFIT of the Investitionsbank Berlin (IBB), and by the DFG, Contract No. BI 284/29-1. One of the authors (N.A.) gratefully acknowledges financial support from The Scientific and Technological Research Council of Tur-

key (TUBITAK-BIDEB). N.Ö. acknowledges support by the DAAD via TUB.

- <sup>1</sup>R. Waser, *Microelectronics and Information Technology* (Wiley-VCH, Berlin, 2003).

- <sup>2</sup>R. D. Pashley and S. K. Lai, IEEE Spectrum **26**, 30 (1989).

- <sup>3</sup>P. Pavan, R. Bez, P. Olivo, and E. Zanoni, Proc. IEEE **85**, 1248 (1997). <sup>4</sup>R. M. Sherwin, IEEE Spectrum **38**, 55 (2001).

- <sup>5</sup>J. E. Brewer, V. Zhirnov, and J. A. Hutchby, IEEE Circuits Devices Mag. **21**, 13 (2005).

- <sup>6</sup>L. Geppert, IEEE Spectrum **40**, 48 (2003).

- <sup>7</sup>International Technology Roadmap for Semiconductors (ITRS), 2005 ed., 2006.

- <sup>8</sup>M. Geller, A. Marent, E. Stock, A. E. Zubkov, I. S. Shulgunova, A. V. Solomonov, and D. Bimberg, Appl. Phys. Lett. **89**, 232105 (2006).

- <sup>9</sup>H. A. Nilsson, C. Thelander, L. E. Froberg, J. B. Wagner, and L. Samuelson, Appl. Phys. Lett. **89**, 163101 (2006).

- <sup>10</sup>M. Geller, A. Marent, and D. Bimberg, "Speicherzelle und Verfahren zum Speichern von Daten," German Patent Application No. 10, 2006, 059, 110.0 (27 October 2006).

- <sup>11</sup>M. Geller "Investigation of carrier dynamics in self-organized quantum dots for memory devices," Ph.D. thesis, Technical University of Berlin, 2007 (http://opus.kobv.de/tuberlin/volltexte/2007/1561/).

- <sup>12</sup>T. Müller, F. F. Schrey, G. Strasser, and K. Unterrainer, Appl. Phys. Lett. **83**, 3572 (2003).

- <sup>13</sup>A. Marent, M. Geller, A. Schliwa, D. Feise, K. Pötschke, and D. Bimberg, Appl. Phys. Lett. **91**, 242109 (2007).

- <sup>14</sup>A. Marent, M. Geller, D. Bimberg, A. P. Vasi'ev, E. S. Semenova, A. E. Zhukov, and V. M. Ustinov, Appl. Phys. Lett. **89**, 072103 (2006).

- <sup>15</sup>C. Balocco, A. M. Song, and M. Missous, Appl. Phys. Lett. **85**, 5911 (2004).

- <sup>16</sup>M. Geller, E. Stock, C. Kapteyn, R. L. Sellin, and D. Bimberg, Phys. Rev. B 73, 205331 (2006).

- <sup>17</sup>M. Geller, C. Kapteyn, L. Müller-Kirsch, R. Heitz, and D. Bimberg, Appl. Phys. Lett. 82, 2706 (2003).

- <sup>18</sup>The structures are not yet optimized since the carriers are not stored at zero bias. The memory structure can be easily adjusted in a next step to yield a storage situation at zero bias, realized by changing the width between the QD layer and the p-n junction.