# Signal Generation for Millimeter Wave and THz Applications in InP-DHBT and InP-on-BiCMOS Technologies

vorgelegt von

M. Sc. Eng.

Muhammad Maruf Hossain

aus Rajshahi, Bangladesh

Von der Fakultät IV - Elektrotechnik und Informatik

der Technischen Universität Berlin

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

Dr.-Ing.

genehmigte Dissertation

#### Promotionsausschuss:

Vorsitzender: Prof. Dr.- Ing. Friedel Gerfers

Gutachter 1: Prof. Dr. -Ing. Wolfgang Heinrich

Gutachter 2: Prof. Dr. -Ing. Dr.-Ing. habil. Robert Weigel

Gutachter 3: Prof. Dr.- Ing. habil. Viktor Krozer

Tag der wissenschaftlichen Aussprache: 14.07.2016

# **Acknowledgement**

This research work was a journey of a lifetime and it would not have been come to an end if I did not get the support in many ways from many persons in different times under various circumstances. It is a great opportunity to express my gratitude to all of them for their support before moving any further.

First and foremost, I wish to express my deep and sincere gratitude to my research advisor Professor Dr. Wolfgang Heinrich. His wide knowledge and his exceptional way of thinking have been grate value for me. His proper guidance, understanding and inspiration have given me the right way of the research work.

I wish to express my warm and sincere thanks to Professor Dr. Viktor Krozer. His valuable advice and friendly help is really remarkable. His extensive discussion and creative ideas around my work has been also a great value of my research.

I would also like to acknowledge to all the members of the Microwave department for their help and availability, especially Dr. Udo Pursche, Dr. Olof Bengtsson , Dr. Andreas Wentzel, Dr. Michael Hrobak, researcher Mr. Ralf Doerner, Mr. Steffen Schulz and Mr. Thualfiqar Al-Sawaf as well as administrative staff for their support during my research work at FBH

My many thanks also go to Dr. Franz-Josef Schmückle and researcher Mr. Siddartha Sinha for their electromagnetic simulation support during my research. I would also like to thank Dr. Bernd Janke and Dr. Nils Weimann for their kind co-operation and intensive care during chip layout and fabrication in my research.

My plenty of thanks will also go to the former colleagues Dr. Chafik Meliani, Dr. Thomas Jensen and Dr. Tomas Krämer for their valuable discussion and support.

I could not finish my gratitude without giving my friends and family members. They had always given me spontaneous encouragement and love thought out my foreign life and the academy. Most importantly, I would like to give the especial thanks to my dear mother.

It will be unjust if I do not mention the role of my wife Mou during my research work. Her endless love and daily life support have been an inspiration. I am thankful to her for being considerate.

Finally, all of my gratitude would be definitely incomplete if I would forget to thank the most merciful and most gracious creator almighty. It is the spiritual encouragement for me towards finishing my research work.

# **Abstract**

Increasing research activities in the mm-wave and sub-THz bands using different technologies have reached significant achievements over the past few years. A variety of commercial and defense applications are expected to be based on mm-wave and sub-Terahertz integrated circuits in the near future. Silicon-based technologies such as RF-CMOS and SiGe-BiCMOS have shown steady progress, but they are struggling to fulfill the demands due to their limitations in power-handling capability with increasing device speed. III-V technologies offer a higher potential in this regard, but do not allow high levels of integration. In order to move beyond silicon-based technologies while still providing high level of density and complexity, wafer level integration of III-V technologies has become highly interesting due to the overall benefit in terms of performances and complexities.

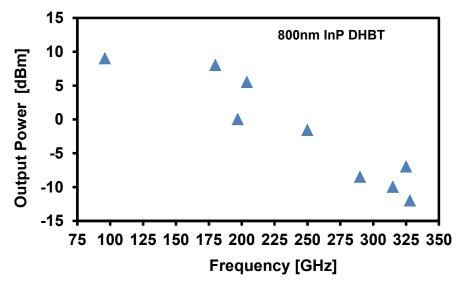

Accordingly, this work focuses on MMIC signal sources in Transferred Substrate (TS) InP-DHBT technology and successful wafer-level circuit integration in InP-on-BiCMOS technology. It is divided in three major parts. In the first part, it presents 96 GHz and 197 GHz fundamental sources using a 0.8 µm InP TS-DHBT process, which deliver +9 dBm and 0 dBm output power with 25% and 4.6% overall DC-to-RF efficiency, respectively. The first part also comprises a 290 GHz harmonic oscillator, which exhibits -9.5 dBm output power and shows 0.5% overall DC-to-RF efficiency. Furthermore, it demonstrates 162 GHz and 270 GHz push-push sources utilizing InP TS-DHBTs on a BiCMOS process, which achieve -4.5 dBm and -9.5 dBm output power and combined overall DC-to-RF efficiencies of 1.5% and 0.4%, respectively.

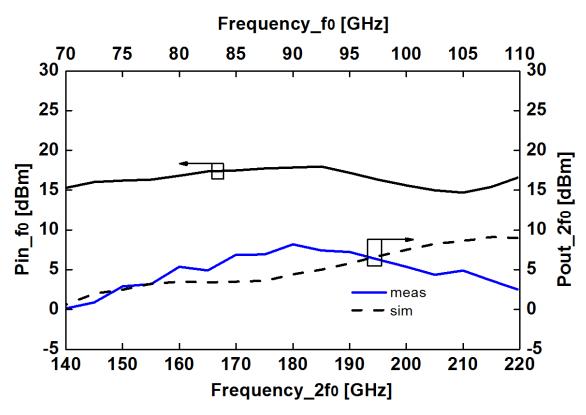

In the second part, multiplier-based signal sources are demonstrated. It presents a full G-band (140-220 GHz) frequency doubler, which delivers +8.2 dBm at 180 GHz and more than +5 dBm in the range 160-200 GHz as well as +2.5 dBm at 220 GHz. The doubler circuit exhibits a power efficiency of 16 % in this frequency range. Also, a 250 GHz single-ended frequency tripler is presented, with -4.4 dBm output power and 3% of DC-to-RF efficiency. The highest frequency is reached by a wideband 328 GHz quadrupler, which delivers -7 dBm output power at 325 GHz and exhibits 0.5 % DC-to-RF efficiency.

The final part is devoted to hetero-integrated circuits and the necessary design considerations. Two 250 GHz and 330 GHz sources are demonstrated that deliver -1.6 dBm and -12 dBm output power, respectively. These are the first hetero-integrated signal sources in this frequency range reported so far.

# Kurzfassung

Die Forschungsaktivitäten in den Millimeter-Wellen- und Sub-THz-Frequenzbändern nehmen stetig zu. Mit unterschiedlichen Technologien konnten in den letzten Jahren erhebliche Fortschritte erzielt werden.

Man kann davon ausgehen, daß in naher Zukunft eine Vielzahl von kommerziellen und militärischen Anwendungen auf integrierten Schaltkreisen im Millimeter-Wellen- und Sub-THz-Frequenzbereich beruhen wird.

Auf Silizium basierende Technologien, wie RF-CMOS und SiGe-BiCMOS, entwickeln sich stetig weiter, unterliegen aber harten Einschränkungen in Bezug auf die erreichbare Maximalleistung bei den steigenden Einsatzfrequenzen.

Diese Probleme lassen sich durch den Einsatz von III-V-Halbleiter-Technologien umgehen, wobei der erreichbare Integrationsgrad signifikant geringer ist.

Die Heterointegration auf Wafer-Ebene erlaubt die Kombination der Vorteile beider Ansätze. Dabei werden beide Technologien in einem Halbleiter-Prozess verwendet, wodurch hohe Einsatzfrequenzen bei hoher Signalleistung und hoher Integrationsdichte realisierbar werden. Die vorliegende Arbeit beschäftigt sich mit Signalquellen, die als integrierte Schaltungen in der Transfersubstrat (TS) InP-DHBT Technologie oder hetero-integriert in InP-on-BiCMOS-Technologie hergestellt wurden. Die Arbeit gliedert sich in drei Hauptteile.

Im ersten Teil werden Signalquellen bei 96 GHz und 197 GHz vorgestellt. Diese wurden im InP-TS-DHBT-Prozess mit einer Emitterbreite von 0.8 µm gefertigt. Die Schaltungen liefern Ausgangsleistungen von 9 dBm und 0 dBm bei Effizienzen von 25 % und 4.6 %. Darüber hinaus wird ein 290 GHz Oszillator auf der dritten Harmonischen vorgestellt, welcher -9.5 dBm Ausgangsleistung bei einer Effizienz von 0.5 % liefert. Ferner werden zwei Push-Push-Quellen bei 162 GHz und 270 GHz aus dem InP-on-BiCMOS-Prozess gezeigt. Diese erreichen Ausgangsleistungen von -4.5 dBm und -9.5 dBm mit Effizienzen von 1.5 % und 0.4 %.

Der zweite Teil der Arbeit beschäftig sich mit Signalquellen, die auf Frequenzvervielfachern basieren. Es wird ein Verdoppler für das gesamte G-Band (140 GHz bis 220 GHz) vorgestellt, welcher 8.2 dBm Ausgangsleistung bei 180 GHz und mehr als 5 dBm Ausgangsleistung von 160 GHz bis 220 GHz liefert. Bei 220 GHz wird noch eine Leistung von 2.5 dBm erreicht.

Der Verdoppler arbeitet mit einer Leistungseffizienz von 16 %. Weiterhin wird ein Frequenzverdreifacher bei 250 GHz präsentiert. Dieser erreicht -4.4 dBm Ausgangsleistung

und eine Effizienz von 3 %. Die höchste Ausgangsfrequenz wird mit einem breitbandigen Vervierfacher um 328 GHz erreicht. Dieser liefert 7 dBm bei 325 GHz mit einer Effizienz von 0.5 %.

Der dritte Teil der Arbeit ist den heterointegrierten Schaltungen und der dafür erforderlichen Entwurfsmethodik, gewidmet. Zwei Quellen bei 250 GHz und 330 GHz mit Ausgangsleistungen von -1.6 dBm und -12 dBm werden vorgestellt. Dabei handelt es sich um die ersten heterointegrierten Signalquellen in diesen Frequenzbereichen.

# Acknowledgement

# **Abstract**

# Contents

| 1 | Introduct             | ion                                                   | 1   |  |

|---|-----------------------|-------------------------------------------------------|-----|--|

|   | 1.1 Motiva            | ation                                                 | 1   |  |

|   | 1.2 Thesis Objectives |                                                       |     |  |

|   | 1.3 Thesis            | 3                                                     |     |  |

| 2 | Technolo              | egy                                                   | 4   |  |

|   | 2.1 Transf            | Ferred Substrate (TS) Process Flow                    | 7   |  |

|   | 2.2 InP-on            | n-BiCMOS Process Flow.                                | 8   |  |

| 3 | Device M              | odelling and Measurement Setup                        | 11  |  |

|   | 3.1 Passiv            | es                                                    | 11  |  |

|   | 3.1.1                 | Transmission Line Theory.                             | 11  |  |

|   |                       | 3.1.1.1 Investigation of Different Transmission Lines | 13  |  |

|   | 3.1.2                 | Resistors                                             | 14  |  |

|   | 3.1.3                 | Capacitors                                            | 15  |  |

|   | 3.1.4                 | Ground Via                                            | 16  |  |

|   | 3.1.5                 | Transition Between InP and BiCMOS                     | 16  |  |

|   | 3.1.6                 | DC and High Frequency RF Pads                         | 17  |  |

|   | 3.1.7                 | Post Layout Analysis                                  | 18  |  |

|   | 3.2 Active            | e Elements                                            | 19  |  |

|   | 3.2.1                 | Small Signal and Large Signal                         | 19  |  |

|   | 3.3 Measi             | urements                                              | 20  |  |

|   | 3.3.1                 | S-parameter                                           | 21  |  |

|   | 3.3.2                 | Spectrum                                              | 21  |  |

|   | 3.3.3                 | Power                                                 | 22  |  |

|   | 3.3.4                 | Oscillator Measurement Methodology                    | 23  |  |

|   | 3.3.5                 | Multiplier Measurement Methodology                    | 23  |  |

| 4 | Millimete             | r Wave and Sub-THz Frequency Oscillators              | 24  |  |

|   | 4.1 Oscill            | lator Circuit Topology                                | 24  |  |

|   | 4.1.1                 | Phase Noise.                                          | 25  |  |

|   | 4.1.2                 | Push-Push Topology                                    | 26  |  |

|   | 4.2 Oscilla           | ators on Transferred Substrate (TS) Process           | 2.7 |  |

|   | 4.2.1       | Design and Characterization             | 27 |

|---|-------------|-----------------------------------------|----|

|   |             | 4.2.1.1 96 GHz Fundamental Oscillator   | 27 |

|   |             | 4.2.1.2 200 GHz Fundamental Oscillator  | 32 |

|   |             | 4.2.1.3 290 GHz Harmonic Oscillator     | 35 |

|   | 4.3 Oscilla | ators on InP-on-BiCMOS Process          | 39 |

|   | 4.3.1       | Design and Characterization             | 40 |

|   |             | 4.3.1.1 Push-Push Oscillator Design.    | 40 |

|   |             | 4.3.1.2 162 GHz Push-Push Oscillator    | 41 |

|   |             | 4.3.1.3 270 GHz Push-Push Oscillator    | 43 |

| 5 | Sub-THz     | and THz Active Frequency Multipliers    | 46 |

|   | 5.1 Design  | Principle and Topology                  | 46 |

|   | 5.1.1       | Purpose of Active Frequency Multipliers | 46 |

|   | 5.1.2       | Single Device Frequency Multiplier      | 47 |

|   | 5.1.3       | Balanced Frequency Multiplier           | 49 |

|   | 5.2 Design  | and Characterization                    | 51 |

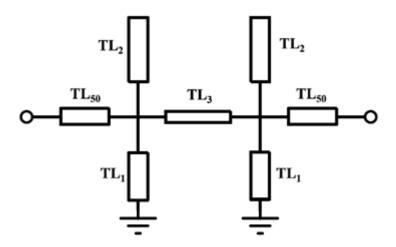

|   | 5.2.1       | W-band Marchand Balun.                  | 51 |

|   | 5.2.2       | 140-220 GHz Frequency Doubler           | 54 |

|   | 5.2.3       | Band Pass Filter Beyond 200 GHz.        | 60 |

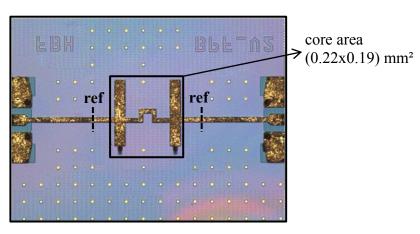

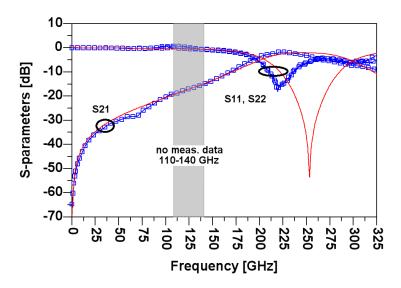

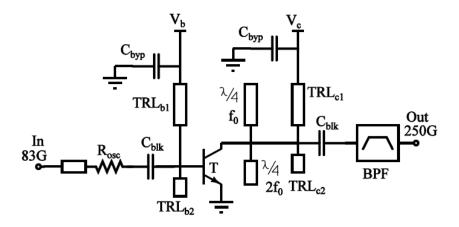

|   | 5.2.4       | 250 GHz Frequency Tripler               | 63 |

|   | 5.2.5       | 330 GHz Frequency Quadrupler.           | 66 |

| 6 | Hetero-In   | tegrated Sources                        | 71 |

|   | 6.1 BiCM    | OS-to-InP Transition                    | 71 |

|   | 6.2 Design  | and Characterization                    | 73 |

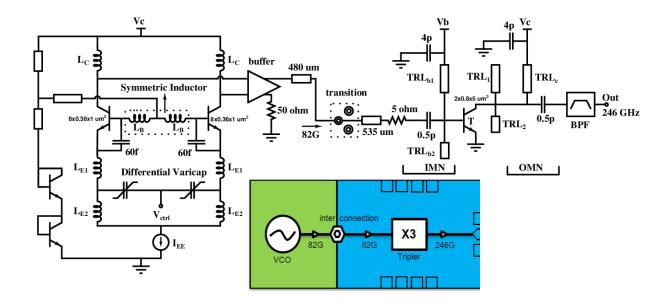

|   | 6.2.1       | 250 GHz Hetero-Integrated Source        | 73 |

|   | 6.2.2       | 330 GHz Hetero-Integrated Source        | 84 |

| 7 | Conclusion  | ons                                     | 88 |

|   | Appendix    |                                         |    |

|   | Reference   | es                                      |    |

**Publications**

Introduction 1.1 Motivation

# 1 Introduction

#### 1.1. Motivation

Recently, a variety of commercial and defense applications that demand for sub-Terahertz and mm-wave integrated circuits have emerged [1]. The frequency range between 100 GHz and 1 THz offers large bandwidth for high-speed communications as well as improved performance of sensors and imaging systems due to short wavelengths. All these systems require signal sources for local oscillators or signal generation. The sources are key building blocks for such applications. Performance targets include particularly a combination of high output power, low phase noise and high DC-to-RF efficiency. In the past years, significant progress has been made in sources for the mm-wave and sub-terahertz frequency range, using various semiconductor technologies. Mostly, these sources have been realized in push-push configuration [2], [3]. Few of them are fundamental frequency sources [4], [5] but they are relatively power-hungry and deliver less output power. Hence, developing efficient fundamental frequency sources at sub-THz and mm-wave frequencies is still the subject of intensive research.

Integrated sources based on frequency multiplication offer many advantages for mm-wave and THz frequencies applications. At present, in the microwave frequency bands fundamental sources are commercially available and mature enough offering high output power and efficiency, low noise, electronic tuning and compact design [6], [7]. Usually, millimeter-wave and terahertz frequency multipliers exhibit broadband, high power handling capabilities and high efficiency. Therefore, a microwave source combined with a millimeter-wave or terahertz frequency multiplier provides a compact broadband tunable source at frequencies from 30 GHz to well above 1 THz [8], [9].

The major challenge in signal generation at such frequencies is that the active devices have to be operated close to, or even above their transit frequencies and close to breakdown voltage as well. Additionally, the quality factor of the passive components degrades compared with lower frequencies. Recently, SiGe and CMOS circuits have been demonstrated operating at frequencies beyond 250 GHz [10], [11]. Nevertheless, due to their more relaxed geometrical dimensions, compound semiconductors such as InP offer better power capabilities. This is why InP is used in the research work presented here.

But it is not sufficient to have individual circuits with decent performance. Integrated components and modules with increased functionality are crucial for successful implementation of system on-chip solutions. At millimeter-wave and THz frequencies system-on chip solutions further improve performance because the number of interconnects is reduced. Nowadays, system-on chip solutions based on CMOS and BiCMOS technologies cover both analog and digital circuits and reach operating frequencies beyond 250 GHz [12], [13]. However, this is achieved at the cost of lower breakdown voltage and thus reduced output power. On the other hand, compound semiconductors such as InP exhibit operating frequencies approaching 1 THz with high power capabilities [14]. Therefore, wafer-level hetero-integration of InP circuits with BiCMOS promises great potential. This is a main motivation behind the research work presented here. Recently, research on InP-on-BiCMOS device level integration has been reported by the DARPA funded consortium [15], [16] and there are ongoing activities to combine GaN-on-Si CMOS [17].

## 1.2. Research Objectives

This thesis investigates realization of signal sources for the frequency range beyond W band in InP TS-DHBT and InP-on-BiCMOS technologies. Since the transferred-substrate process has been made available only recently, emphasis of the work is on exploring capabilities in terms of performance and demonstrating the potential of the hetero-integration technology. The specific research objectives include:

- ➤ Design and characterize fundamental and harmonic fixed-frequency oscillators up to 300 GHz using the InP TS process.

- ➤ Design and characterize signal sources based on multipliers for frequencies beyond 200 GHz using the InP TS process as well as the InP-on- BiCMOS versions.

## 1.3. Thesis Organization

The dissertation is organized as follows: Chapter 2 discusses the InP TS process and the hetero-integrated InP-on-BiCMOS process technology. Chapter 3 describes the active and passive modelling as well as measurement methodology. Chapter 4 presents the general theory of oscillators as well as the design and measurement results of the oscillators in InP TS and InP-on-BiCMOS process technology.

Chapter 5 then is devoted to the circuit topologies and the measured results of the various frequency multipliers developed. Chapter 6 deals with the details of the design procedure and the results of the hetero-integrated signal sources. At the end, Chapter 7 summarizes the contributions of the research work presented in this dissertation and gives an outlook for future designs at mm-wave and THz frequencies.

# 2 Technology

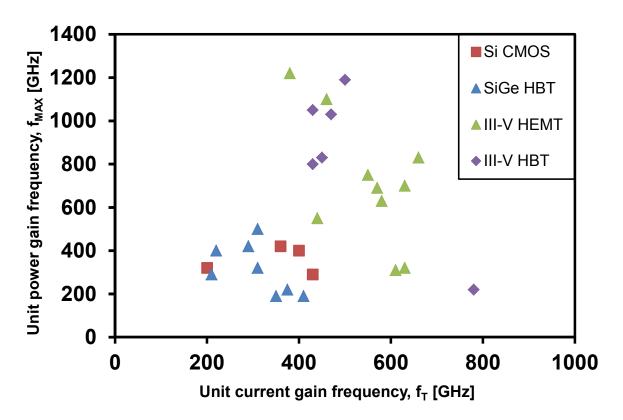

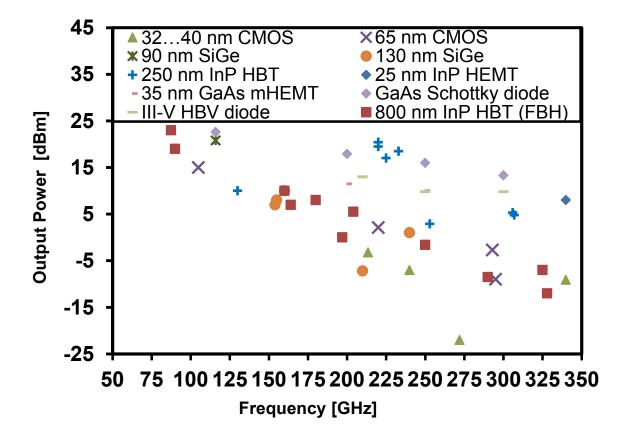

Still growing needs for faster data communication rates and to fill up new application areas up to Terahertz (THz) frequencies raise the question how far traditional semiconductor technologies can satisfy these markets. To address this challenge, advanced semiconductor devices with maximum oscillation frequencies ( $f_{MAX}$ ) of 1 Terahertz or beyond have been developed [18]. Device scaling plays the most important role in this journey. Si technologies based on Si CMOS or SiGe BiCMOS HBTs are preferred for various applications owing to the high integration level, mature design environment, low power and low cost (for high volume). However, its device operation speed is limited by the intrinsic material properties of Si. In contrast, high speed III-V technologies based on GaAs or InP benefit from excellent electron transport characteristics such as high mobility and speed. This is clearly shown in Fig. 1, which compares recently reported unity current gain,  $f_t$  and unity power gain,  $f_{MAX}$ ; values of various III-V and Si-based devices. It is obvious from the plot that the speed of III-V devices, both HBTs and HEMTs, dominate over that of Si devices, exhibiting best f<sub>MAX</sub> exceeding 1.2 THz. It is also true that the operation speed of Si-based devices has been significantly improved over the past years, now reaching up to 500 GHz (see Fig. 2.1) in terms of f<sub>MAX</sub>, which is sufficient for circuits operating well beyond 100 GHz. This is achieved with aggressive device scaling, which increases mask and processing cost. This aggressive device scaling significantly reduces the breakdown voltage and hence the available RF output power. On the other hand, compound semiconductors such as InP exhibit high power capabilities at operating frequencies beyond 200 GHz. This is also clearly visible in Fig. 2.2, which shows recent power trends realized in various circuits on different technologies.

Fig. 2.1. f<sub>T</sub> and f<sub>MAX</sub> of recently reported devices achieved on different technologies [19].

Fig. 2.2. Performance of recently reported circuits operating near or beyond 100 GHz on different technologies.

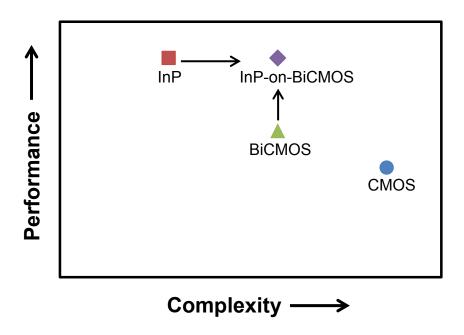

The III-V based devices achieve higher f<sub>T</sub> and f<sub>MAX</sub> values and they deliver higher output power compared to the Si-based technologies. But, their capability in terms of circuit complexity and functionality is lower than for the Si technologies, i.e., CMOS or SiGe BiCMOS. Therefore, combining Si based technologies with a III-V compound semiconductor such as InP offers the possibility to realize compact circuits with benefits from both technologies. This solution combines the high-integration capabilities of the silicon process and the high-frequency high-power potential of compound semiconductor (see Fig. 2.3). Such integrated components and modules with increased functionality are crucial for successful implementation of system-on-chip solutions. At millimeter-wave frequencies and beyond system-on-chip solutions show superior performance compared to other approaches, due to the reduced number of chip-to-chip interconnects in the systems, which become increasingly lossy at high frequencies.

Fig. 2.3. Performance vs complexity in different technologies.

In this work, the main focus is on circuit designs for the FBH 0.8 µm transferred-substrate (TS) InP-DHBT process. The transfer of the substrate, i.e. removing the InP, embedding the HBT in BCB and using AIN as a host substrate, offers several advantages: less extrinsic capacitance, relaxed geometry and better heat conduction by means of replacing InP substrate by AIN substrate. The TS InP-DHBT process flow is briefly discussed in Section 2.2 while Section 2.3 describes the heterogeneous (InP-on-BiCMOS) process.

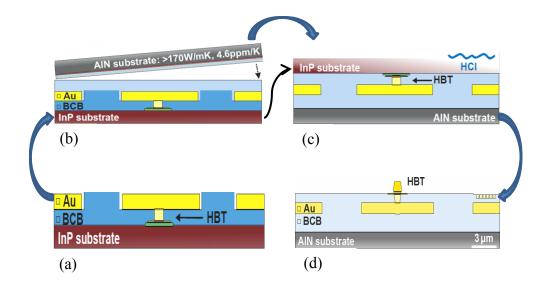

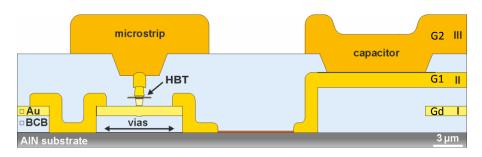

#### 2.1 Transferred Substrate (TS) Process Flow

The TS InP DHBT epitaxial layer composition is similar to conventional DHBTs, but with reduced sub-collector thickness and additional etch stop layers at the bottom for substrate removal. The first step, the front-side process, is the same as for conventional InP-DHBTs. In this step, base and emitter metal is introduced, then emitter mesa is etched and at the end the base metal is deposited. After that, planarization of the device is done by benzocyclobutene (BCB) and then the ground metallization is formed. This completes the front-side process (see Fig. 2.4. a). In the next step the complete structure is bonded upside down onto an AlN wafer with a 2-µm layer of benzocyclobutene (BCB) (see Fig. 2.4. b). After curing the BCB the two wafers form a firm compound. Then the whole structure is flipped as shown in Fig. 2.4. c and the InP substrate including all unnecessary semiconductor material (e.g., the extrinsic collector under the base contacts and base pad) are removed by etching back-tofront, until only the epitaxial layers of the active circuit elements remain. This approach substantially reduces device parasitics, since the transistor is embedded in BCB ( $\varepsilon_r$ =2.65) instead of InP ( $\varepsilon_r$ =11). Thus, operating frequency is increased without transistor downscaling. These features of the transferred-substrate technology make it ideally suited for highfrequency power applications. After removing the InP substrate, collector mesa is etched. At this step, the collector metal is open to access, which can be independently scaled according to the electrical and thermal requirements (see Fig. 2.4. d). In a final step, necessary vertical interconnects are formed and base metal resistor, MIM capacitors (dielectric material: SiNx) and thin-film microstrip transmission lines complete the TS MMIC process. Fig. 2.5 shows the schematic cross-section of the final InP TS DHBT process structure. The TS version used in this work is based on a 0.8  $\mu$ m InP-DHBT technology, which offers  $f_T/f_{MAX}$  values above 320 GHz with BVCEO = 4V [20]. The process has three Au metal layers with  $1\mu m$ ,  $1.5\mu m$ and 4.5 µm thickness, respectively, with a dielectric constant of 2.65. For more details of the TS process flow see [20].

Fig. 2.4. Process flow of the transferred-substrate (TS) InP DHBT fabrication.

Fig. 2.5. Schematic cross-section of the final layer structure.

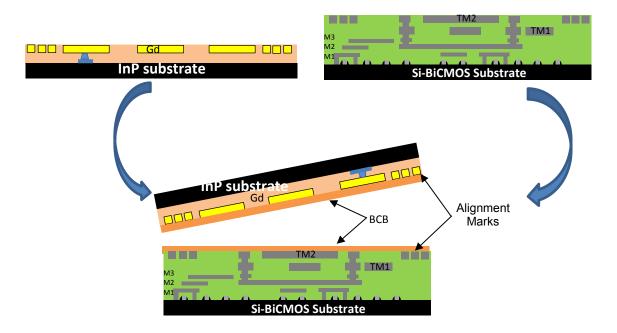

#### 2.2 InP-on-BiCMOS Process Flow

The novelty of the heterogeneous integration InP-on-BiCMOS in comparison with other approaches is the integration of already processed BiCMOS wafers with InP DHBT wafers, providing low-loss interconnects. This ensures minimum interference between the two processes and keeps the high level of maturity of the Si technology from the very beginning. Basically, the process flow is the same as that for AIN substrate discussed above but using a BiCMOS wafer instead of the AIN substrate. In a first step, the desired circuits in BiCMOS technology are processed and, in parallel, the InP D-HBT circuits are prefabricated up to the transistor level using the TS process discussed in Section 2.1. Then, the BiCMOS and the InP wafers are joined by means of wafer-level BCB bonding (see Fig. 2.6). After that the InP substrate including all unnecessary semiconductor material is removed, until only the epitaxial layers of the active circuit elements remain. In the last step, deep vias are etched to

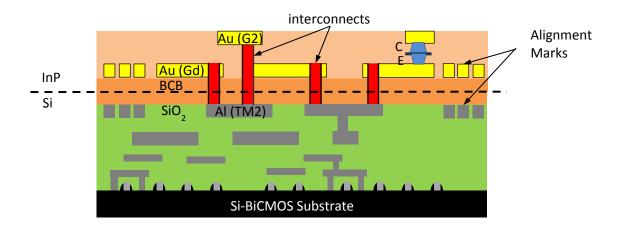

connect the uppermost Si metallization level to the InP part and the remaining InP metallization levels are completed (see Fig. 2.7).

Fig. 2.6. Schematic cross-section of the transferred-substrate InP-on-BiCMOS process.

Fig. 2.7. Schematic cross-section of the final InP-on-BiCMOS environment.

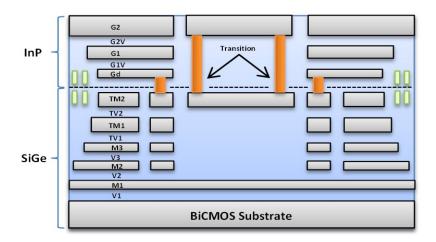

Fig. 2.8 shows the resulting layer stack of the hetero-integration process. On the BiCMOS side, it comprises a 0.25  $\mu$ m technology with  $f_T/f_{MAX} = 180/220$  GHz, the InP part is based on a 0.8  $\mu$ m TS InP-DHBT technology, which offers  $f_T/f_{MAX}$  values above 320 GHz. For

further details of the InP-on-BiCMOS process see [21, 22]. Table 2.1 summarizes the specifications of the InP-on-BiCMOS process .

Fig. 2.8. Layer stack of the hetero-integration process.

Table 2.1 Summarized specifications of the InP-on-BiCMOS process

| Process | Emitter | HBT     | $\mathbf{f}_{\mathrm{T}}/\mathbf{f}_{\mathrm{MAX}}$ | No. of metal     | Passives        | BV <sub>CEO</sub> |

|---------|---------|---------|-----------------------------------------------------|------------------|-----------------|-------------------|

|         | width   | Type    | [GHz]                                               | Layers           |                 | [Volts]           |

|         | [µm]    |         |                                                     | [Thickness]      |                 |                   |

| TS InP  | 0.8     | Common  | >320                                                | 3 gold           | MIM capacitors, | >4.5              |

|         |         | emitter |                                                     | (1.5µm, 2.5µm,   | resistor        |                   |

|         |         | Common  |                                                     | 4.5µm)           | (base metal)    |                   |

|         |         | base    |                                                     |                  |                 |                   |

| SiGe    | 0.25    | Common  | 180/220                                             | 5 aluminium      | MIM capacitors, | >1.9              |

| BiCMOS  |         | emitter |                                                     | (1 µm, 2µm, 3µm) | resistors       |                   |

|         |         | Common  |                                                     |                  |                 |                   |

|         |         | base    |                                                     |                  |                 |                   |

# 3 Device Modelling and Measurement Setup

The major challenge in circuit design at mm-wave and THz frequencies is that the active devices have no accurate model and they have to be operated close to or even above their transit frequencies as well as close to breakdown voltage. Additionally, circuits are more sensitive to parasitics which result in capacitances, resistances, distributed effects etc. Thus, the quality factor of the passive components degrades compared to lower frequencies. The objective of this chapter is to discuss modeling and characterization of the active and passive elements at frequencies beyond 100 GHz. The results were used in the design of the circuits presented in Chapters 4, 5 and 6.

#### 3.1 Passives

Passive circuit elements are critical components of MMIC design. The passive structures discussed here include transmission lines, resistors, capacitors, the high frequency RF pads, DC pads, vias and the interconnection between the InP and the BiCMOS part on the wafer.

## 3.1.1 Transmission Line Theory

In high frequency circuit design transmission lines are described by a distributed-parameter network, where voltages and currents vary in magnitude and phase over its length. This is governed by equations 3.1 and 3.2, where the  $e^{\gamma z}$  term represents wave propagation in the +z direction and the  $e^{-\gamma z}$  term represents wave propagation in the -z direction. The complex propagation constant  $\gamma$  is given by equation 3.3, whose real part  $\alpha$  is the attenuation constant and the imaginary part  $\beta$  represents the phase constant [23].

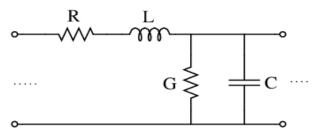

Fig. 3.1. Transmission line equivalent circuit.

L represents the total inductance of the two conductors, and the C their capacitance. The series resistance R denotes the resistance due to the finite conductivity of the conductors, and the shunt conductance G is due to dielectric loss in the material between the conductors.

Generally,  $\gamma$  is a function of frequency. Equation 3.4 provides Z<sub>0</sub>, the characteristic impedance of the transmission line.

$$V(z) = V_0^+ e^{-\gamma z} + V_0^- e^{\gamma z} \tag{3.1}$$

$$I(z) = I_0^+ e^{-\gamma z} - I_0^- e^{\gamma z} \tag{3.2}$$

$$\gamma = \alpha + j\beta = \sqrt{(R + j\omega L)(G + j\omega C)}$$

(3.3)

$$Z_0 = \frac{R + j\omega L}{\gamma} = \sqrt{\frac{R + j\omega L}{G + j\omega C}}$$

(3.4)

In many practical cases, however, the loss of the line is small and can be neglected, which results in a simplification of the above results. Setting R=G=0 yields the propagation constant according to equation 3.5. As expected for a lossless line, the attenuation constant  $\alpha$  is zero. The characteristic impedance simplifies to equation 3.6

$$\gamma = \alpha + j\beta = j\omega\sqrt{LC}

\beta = \omega\sqrt{LC} \quad and \quad \alpha = 0$$

(3.5)

$$Z_0 = \sqrt{\frac{L}{C}} \tag{3.6}$$

Therefore, one has for the wavelength

$$\lambda = \frac{2\pi}{\beta} = \frac{2\pi}{\omega\sqrt{LC}} \tag{3.7}$$

And for the phase velocity

$$v_p = \frac{\omega}{\beta} = \frac{1}{\sqrt{LC}} \tag{3.8}$$

One important feature of the transmission lines is that it causes an impedance transform. A load impedance  $Z_L$  at the end of a line l is transformed to input impedance  $Z_{in}$  as given by:

$$Z_{in} = Z_0 \frac{Z_L + jZ_0 \tan \beta l}{Z_0 + jZ_1 \tan \beta l}$$

$$\tag{3.9}$$

Some special cases are discussed as follows:

Consider the lossless transmission line terminated in a short circuit  $Z_L = 0$ , then

$$Z_{in} = jZ_0 \tan \beta l \tag{3.10}$$

Vice versa, a lossless transmission line terminated by an open, i.e.  $Z_L = \infty$ , yields

$$Z_{in} = -jZ_0 \cot \beta l \tag{3.11}$$

For the particular case of a lossless transmission line with a length of  $l = \lambda/2$ , one has

$$Z_{in} = Z_L \tag{3.12}$$

If the lossless line is a quarter-wavelength long or, more generally,  $l = \lambda/4 + n\lambda/2$  for n = 0, 1, 2, 3, ...

, the input impedance is given by:

$$Z_{in} = \frac{Z_0^2}{Z_I} \tag{3.13}$$

Equation 3.13 describes the principle of a quarter-wave transformer, because it transforms the load impedance to its inverse scaled by the square of the characteristic impedance of the line.

# 3.1.1.1 Investigation of Different Transmission Lines

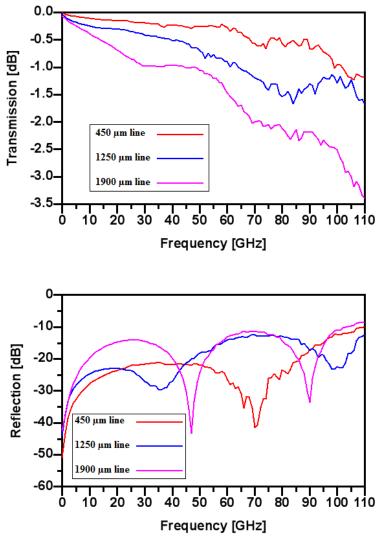

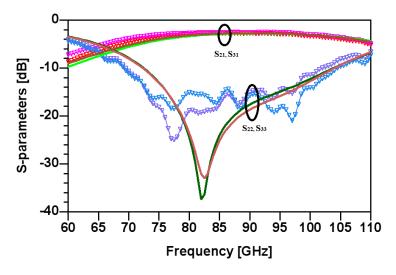

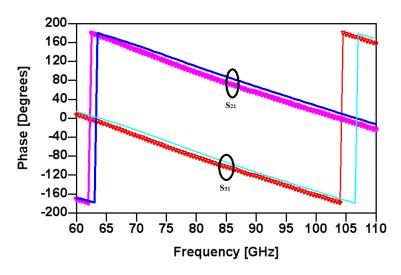

The choice of the transmission line is one of the important considerations in the design of MMIC circuits. In order to achieve low loss high quality factor matching networks, the transmission line choices have to be investigated before moving to the MMIC design environment. For that reason, different line geometries have been investigated. According to the process discussed in Section 2.2, top 4.5  $\mu$ m thick gold (G2) metal is used as a thin film microstrip line with Gd as the ground conductor. The width of a 50 ohm microstrip line in G2 over Gd ground plane is about 12  $\mu$ m (see Fig. 2.5). Fig. 3.2 shows the measured transmission and reflection coefficient of three different lines with 50 ohm characteristic impedance and lengths of 420  $\mu$ m, 1250  $\mu$ m and 1900  $\mu$ m. Fig. 3.2 shows that the loss contribution of a 1 mm long transmission line is around 1 dB up to 110 GHz.

Fig. 3.2. Measured transmission and reflection coefficient of 420  $\mu$ m, 1250  $\mu$ m and 1900  $\mu$ m long transmission lines in the TS InP process (50 ohm thin-flim microstrip with 12  $\mu$ m strip width).

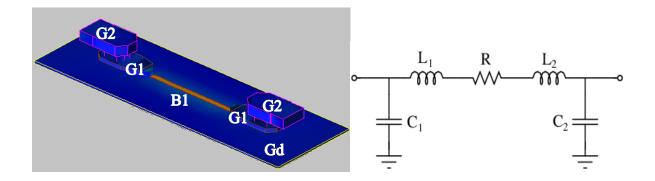

#### 3.1.2 Resistors

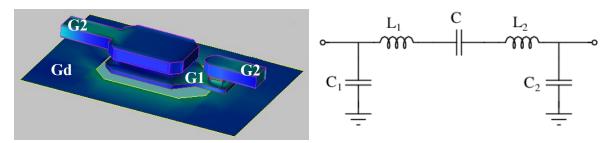

In this work, base metal (B1) resistors have been used in the DC biasing network to avoid unwanted low frequency oscillations. In order to ensure stable circuit operation, also a small resistor (e.g. 5 ohm) was used at the input of the circuit. The resistors have not been employed for any matching network in order to avoid unnecessary losses. For resistor modeling, first a simulation was performed using a 2.5D EM-simulator and then a lumped equivalent circuit model was extracted in ADS. This equivalent circuit model is then applied in circuit simulation. Fig. 3.3 presents the layout and the equivalent circuit model of the 10 ohm resistor. C<sub>1</sub>, C<sub>2</sub> (8 fF) and L<sub>1</sub>, L<sub>2</sub> (8 pF) denote the parasitic capacitances and inductances, respectively.

Fig. 3.3. Layout of the 10 ohm base metal (B1) resistor (left) and generalized equivalent circuit model (right)

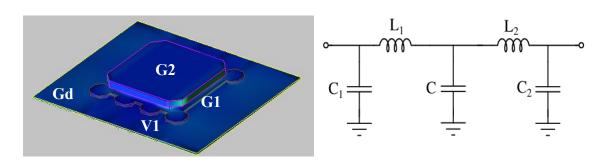

## 3.1.3 Capacitors

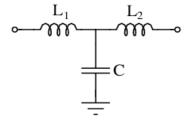

There are two types of MIM capacitors that have been used in this work, depending on their orientation with regard to RF ground. One is the shunt capacitor and the other one is the serial capacitor. Since both capacitor versions include non-negligible parasitic effects, they have not been used for the matching networks. The shunt capacitor was applied only as bypass capacitor and the serial capacitor for DC blocking. Both capacitors have been individually EM simulated and described by an equivalent circuit model in ADS. Fig. 3.4 (a, b) shows the layout and lumped equivalent-circuit model of the 1000 fF capacitor.  $C_1$ ,  $C_2$  (6 fF) and  $L_1$ ,  $L_2$  (9 pH) denote parasitic capacitances and inductances, respectively.

a) Layout of the 1000 fF shunt capacitor (left) and generalized equivalent circuit model (right)

b) Layout of the 188 fF series capacitor (left) and generalized equivalent circuit model (right)

Fig. 3.4. Shunt and serial MIM capacitor layout and equivalent circuit model.

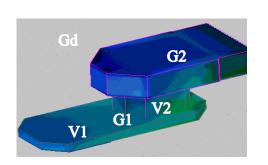

# 3.1.4 Ground Via

The ground via is an important element in the high frequency design environment. This applies to transistors and bias networks as well as to balun and band pass filter. Fig. 3.5 shows the structure of a ground via and its lumped circuit model. C (5 fF), L (0.5 pH) and R (0.3 ohm) denote model parameters.

Fig. 3.5. Layout of the ground via (left) and generalized equivalent circuit model (right).

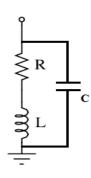

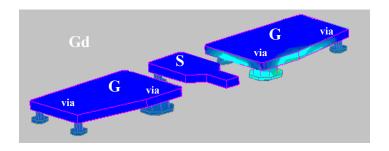

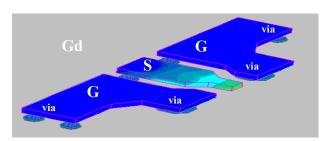

#### 3.1.5 InP-BiCMOS Transition

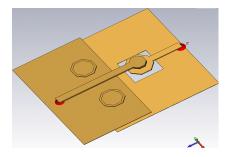

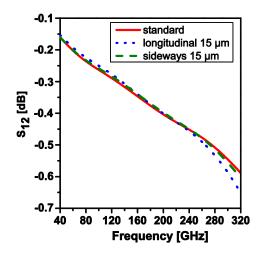

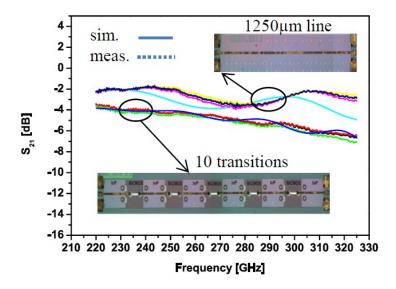

In the hetero-integrated circuit design, the transitions between the BiCMOS and InP part represent one of the most important features. The main issues are to optimize them with regards to misalignment between the BiCMOS and InP wafers and to parasitic effects. Since thin-film microstrip lines are employed in both parts, the signal connection is realized between the top InP gold metal layer (G2) and the top BiCMOS aluminum metal layer (TM2). Vias close to the InP transmission line ensure that a common ground is shared between the InP and BiCMOS circuit parts. Optimization is performed by electromagnetic (EM) simulations employing the 3D solver CST Microwave Studio. After having the optimized results from the EM simulation, an equivalent lumped circuit was extracted in ADS. Fig. 3.6 shows the transition layout with its lumped equivalent circuit model. More details of the transition can be seen in [101], [107].

Fig. 3.6. Layout of the InP-BiCMOS transition (left) and generalized equivalent lumped circuit model (right).

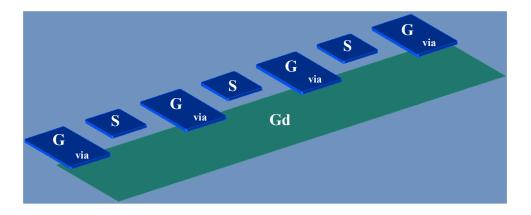

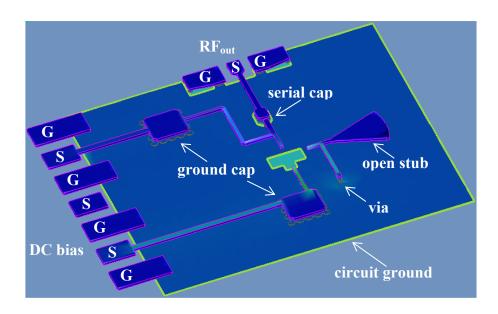

# 3.1.6 DC and High Frequency RF Pads

In this work, two different types of high frequency pads are realized because at different frequency bands the probe tips have different pitches. Both pads are used depending on the input and output frequency. Fig. 3.7 (a) shows the Ground-Signal-Ground (GSG) RF pad which is used for frequencies up to 250 GHz. This pad is optimized for probe pitches from 75  $\mu$ m to 100  $\mu$ m. In order to avoid mechanical problems during on-wafer probing, small mechanical vias were used around the pads corner (see layout). Fig. 3.7 (b) shows the second type of Ground-Signal-Ground (GSG) RF pad which is used for the frequencies beyond 250 GHz. This pad is optimized for probe pitches from 35  $\mu$ m to 70  $\mu$ m. Both pads were optimized using the 3D EM simulation tool CST microwave studio and equivalent circuits were realized in ADS. For DC biasing GSGSG DC pads were used. Fig. 3.8 shows the GSGSGS DC pad with 100  $\mu$ m pitch. Ground pads also include thermal vias down to the AIN substrate, which spread the heat away from the circuit to the AIN substrate (see layout).

(a) Layout of the Ground-Signal-Ground (GSG) RF pad frequency up to 250 GHz (left) and generalized equivalent lumped circuit model (right).

(b) Layout of the Ground-Signal-Ground (GSG) RF pad frequency range from 250 to 350 GHz (left) and generalized equivalent lumped circuit model (right).

Fig.3.7. Ground-Signal-Ground (GSG) high frequency RF pads.

Fig. 3.8. Layout of the GSGSGSG DC pads.

## 3.1.7 Post-Layout Analysis

Post-layout analysis is one of the important steps before moving to chip fabrication in the design of mm-wave and THz circuits. The main purpose of the post-layout simulation is to verify the design compliance with those constraints that are not taken into account during prelayout simulation. In this work, each circuit (without the active devices) was individually verified using ADS 2.5D EM-momentum post-layout simulation. This included all passives, RF and DC pads as well as circuit ground. Fig. 3.9 presents the resulting post-layout structure of a W-band fundamental oscillator.

Fig. 3.9. Structure of a W-band fundamental Oscillator analyzed post layout using 2.5D EM ADS momentum.

#### 3.2 Active Elements

For a successful design the active device performance has to be described properly. In MMIC circuit design at high frequencies, this is a difficult task because transistor behaviors become more complex with increasing frequencies. The description should include small-signal and large-signal characteristics as well as noise. All the characteristics depend on the device size, biasing point, temperature, process, parameter extraction methodology and frequency. These dependencies are not always linear and often must be determined experimentally to fit and/or correct the modeling equations. In this section, the transistor small and large signal model will be discussed.

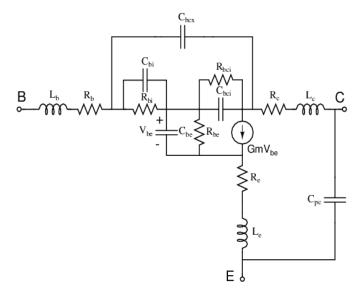

## 3.2.1 Small and Large -Signal Model

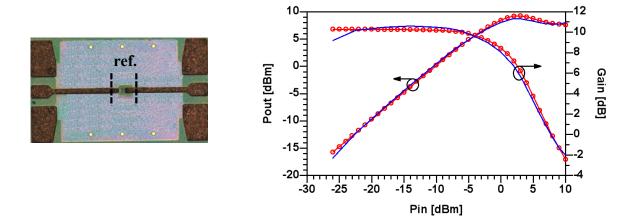

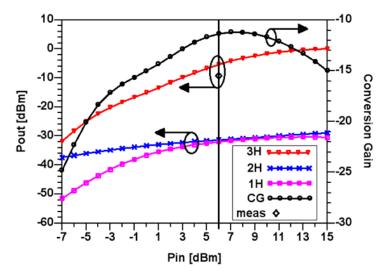

Fig. 3.10 shows the simple HBT's small-signal model. At high frequency, such a simple model often fails to consider effects that are critical for high power high frequency design. Generally, complex model accuracy comes at an expense of simulation speed and resources. However, FBH has developed a TS HBT model that is a good compromise for achieving both high simulation speed and model accuracy. Fig. 3.11 illustrates the large-signal model accuracy in terms of output power and gain compression. More details regarding FBH TS HBT modeling can be found in [24].

Fig. 3.10. Small-signal equivalent circuit model for the TS InP HBT device. The capacitance  $C_{bi}$  is included in the augmented small-signal equivalent circuit model [24].

Fig. 3.11. Measured (solid line w. symbols) and simulated (solid line) large-signal performance of a single finger common emitter HBT at 77 GHz. The device is biased at  $V_{ce} = 1.4 \text{ V}$  with a quiescent current of  $I_{cg} = 22.7 \text{ mA}$  [24].

#### 3.3 Measurements

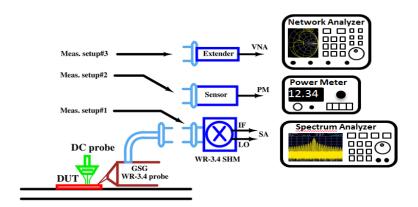

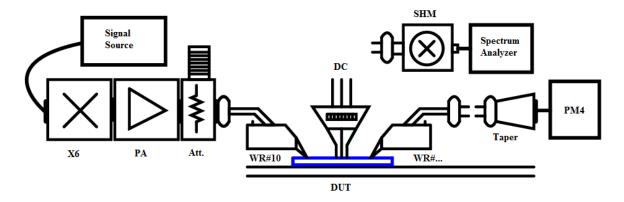

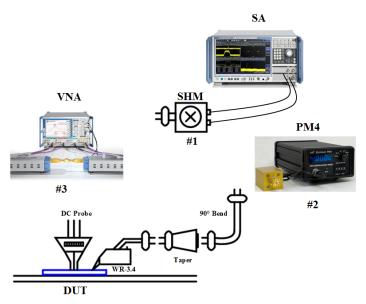

After manufacturing the circuit, the final task is to investigate the performance of the circuit. However, to measure and characterize such mm-wave and THz components have always been a challenge. Generally, high frequency on-wafer circuit measurements reduce characterization time and cost, as they remove the need for additional work intensive dicing and packaging of chips which is the only other alternative method for circuit testing. On-wafer probing of circuits provides quick performance evaluation to improve designs for subsequent circuit fabrication iterations and for screening of circuits in a mass production environment. In this work, all the circuits have been characterized on wafer. The on-wafer measurements discussed here include S-parameter, spectrum and power measurements. Fig. 3.12 shows the on-wafer measurement setup to characterize oscillator circuits (in contrast to S-parameters).

Fig. 3.12. Measurement setup for characterization of signal sources (meas. setup #1 for output spectrum, meas. setup #2 for power measurement, meas. setup #3 for S parameters)

## 3.3.1 S-parameters

S-parameters are the basic measured quantities. They describe how the device under test (DUT) modifies a signal that is transmitted or reflected in forward or reverse direction. In this work, S-parameters have been measured at different frequencies for passive and active components, using a R&S ZVA67 VNA with appropriate R&S frequency extension modules at different frequency bands (e.g. 75-110 GHz, 140-220 GHz, 220-325 GHz) and with respective probes from GGB and Cascade Microtech. For calibration the multiline Thru-Reflect-Line (mTRL) method has been used because its simplicity and accuracy [25, 26]. For multiline TRL calibration, the on-wafer standards short, 200  $\mu$ m 'Thru' line, 100  $\mu$ m symmetric 'Reflect' line, and a set of additional on-wafer transmission lines of different length (e.g. 420  $\mu$ m, 1250  $\mu$ m and 1900  $\mu$ m) were used.

## 3.3.2 Spectrum

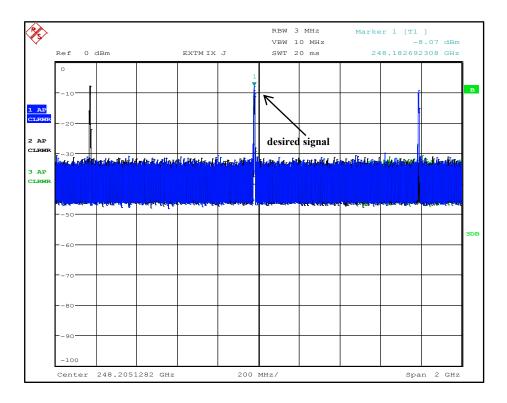

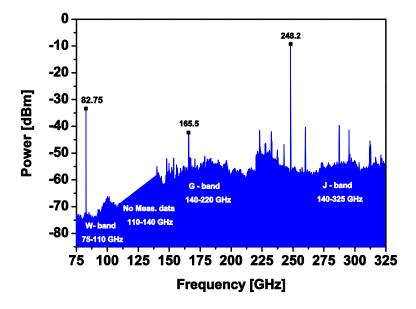

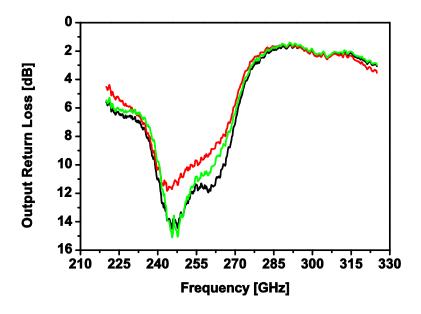

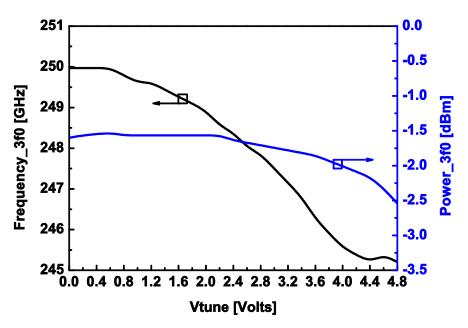

For oscillator characterization, bandwidth and spectral purity spectrum analysis is one of the most important steps. Using a normal setup of a spectrum analyzer, it is difficult to measure the mm-wave and THz frequencies because it has limited frequency range. Therefore, to extend the frequency range of the input signal, an external mixer needs to be used. In this case, the LO frequency is fed to the external mixer, where it is mixed with the RF input from the original input signal. In addition, the harmonics of the LO are mixed with the input signal and converted to new intermediate frequencies. Thus, a wider range of frequencies can be obtained with the same LO. The IF from the external mixer is then returned to the spectrum analyzer [27]. Depending on the required frequency band, the appropriate order of harmonic and the mixer type (3 ports) must be selected. Once the harmonic and the mixer type are selected, the given band conversion loss of the table will be read automatically by the spectrum analyzer. In this work, spectrum analysis was performed using R&S FSUP and FSW signal source analyzer. Since this measurement uses an external mixer, several unwanted harmonics product can be seen in the full band of spectrum. In order to ensure that the correct frequencies are picked, the two sweeps are performed alternately. Fig.3.13 shows two signal traces, one is the test signal (blue) at 248 GHz and the other one is the reference signal (black), which has been obtained by a shift to lower frequencies according to 2x IF/(N x harmonics). Input signals in the desired sideband that are converted by means of the set harmonics are displayed in both traces at the same position on the

frequency axis. Image signals and mixer products caused by other harmonics are displayed in both traces at different positions.

Fig. 3.13. Spectrum characterization: identification of the desired signal at 248 GHz using J band external mixer (Fig. 3.11 meas. setup #1).

#### **3.3.3 Power**

Accurate power measurements above 110 GHz are challenging due to the lack of traceable power sensors. Moreover, it is true that the power meter with power sensor provides accurate power detection, but it receives power in all other harmonics according to power sensor's bandwidth. In order to detect output power as accurately as possible, a preferred waveguide components have been used. In this work, all the circuits have been measured using an Erickson PM4 calorimeter. This meter is a wave guide based calorimeter which uses WR-10 (e.g. 75-110 GHz) wave guide input. The equation 3.14 shows the output power calculation during power measurement. The insertion losses of the probe and waveguide system are estimated given by the vendor at desired frequency bands.

Pout

$$_{\text{(measured)}} = \text{DUT} + \text{Probe}_{\text{(WR-##)}} + \text{Taper}_{\text{(WR-## to WR-10)}} + \text{Waveguide}_{\text{(WR-10 90° bend)}} +$$

$$\text{Waveguide}_{\text{(WR-10 1" length)}} + P_{\text{(sensor)}}.$$

3.14

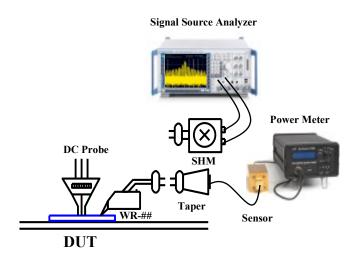

# 3.3.4 Oscillator Measurement Methodology

Characterization of the oscillator was performed in two major steps: First, the oscillation frequency was determined. For this purpose, a ground-signal-ground (GSG) wave guide probe with a sub harmonic mixer (SHM) from RPG for the desired frequency band was connected to the output. The down-converted signal was measured using a FSUP signal source analyzer from Rohde & Schwarz. The second step was to measure the peak power of the circuit. For this purpose, a GSG wave guide probe was connected to a 90-degree WR10 bend and a taper, which connects to the input of a power sensor and an Erickson PM4 power meter.

# 3.3.5 Multiplier Measurement Methodology

The multipliers were characterized in three steps. First, the input power of the multiplier was determined. For the input power, a signal generator from Rohde & Schwarz, a coaxial cable and a full-band WR-10 module, which includes X6 multiplier, attenuator and amplifier, followed by a ground-signal-ground (120-GSG-100-BT) WR-10 waveguide probe from GGB was characterized using a PM4 Erickson power meter. Second, output spectrum and bandwidth were determined. For this purpose, a ground-signal-ground waveguide probe with a dedicated frequency band sub-harmonic mixer (SHM) from RPG was connected to the output of the circuit and then the desired signal was detected using a Rohde & Schwarz spectrum analyzer. The next step was to measure the output power of the circuit as a function of input frequency. To extract the output power of the multiplier, a GSG waveguide probe was connected to a 90-degree WR-10 bend and a taper, followed by the power sensor of the Erickson PM4 power meter.

# 4 MM-Wave and Sub-THz Frequency Oscillators

This chapter deals with the design of the mm-wave and sub-THz frequency oscillators which is a very critical building block in a system. The demand for a highly efficient high output power generation and a low phase noise continues to pose interesting challenges especially for such high frequencies. First, the oscillator topology and the phase noise will be discussed. And then design and characterization of fixed frequency fundamental and harmonic oscillators on TS InP HBT and InP-on-BiCMOS technologies will be described. At the end of this chapter, a performance study of a 96 GHz fundamental oscillator using TS InP and InP-on-BiCMOS technologies will be presented.

# 4.1 Oscillator Circuit Topology

In the most general sense, an oscillator is a nonlinear circuit that converts DC power to an AC waveform. Most RF oscillators provide sinusoidal outputs, which minimizes undesired harmonics and noise sidebands. There are a large number of possible RF oscillator circuits using bipolar or field-effect transistor in either common emitter/source, base/gate, or collector/drain configurations [23]. The analysis of oscillators can be based on two fundamental models: the feedback model or the negative- resistance model. Various type of feedback networks lead to the well-known Hartley, Colpitts, Clapp, and Pierce oscillator circuits [23]. Depending on the oscillator configuration and characteristic, one model may be preferred over the other [28]. According to the feedback model two necessary and sufficient conditions must be met to sustain the steady-state oscillation, which is also known as the Nyquist or Barkhausen criterion. It requires that the gain around the feedback loop must be equal to unity and the total phase shift around the loop must be equal to zero or some multiple of 360 [29]. In a negative resistance model, the active circuit is modeled as a negative resistance in parallel with the resonator. If the Barkhausen criteria are satisfied this negative resistance will exactly cancel the equivalent parallel resistance of the tank circuit and will allow steady oscillation [28].

In order to achieve low phase noise, Cross-coupled or Colpitts type oscillators are commonly used. Although ring or relaxation type oscillator can be found in some applications, they show poor phase noise performance in most RF applications [30]. Furthermore, a reflection type oscillator (also called modified Colpitts) has an advantage regarding phase noise performance.

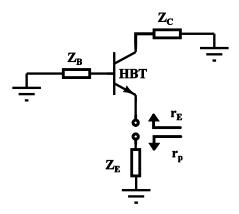

For the reflection type of oscillator, two ports of the active device are terminated by impedances in such a way that the negative resistance appears at the remaining port. And the third impedance is connected to ground to adjust the oscillation frequency. Fig. 4.1 shows the simplified schematic of a reflection-type oscillator. Each port of the active device is terminated by an external impedance to ground, denoted by  $Z_E$ ,  $Z_B$ , and  $Z_C$ , respectively (see Fig. 4.1). These impedances describe the complete bias network, varactor, and also output load. To ensure oscillation startup, the product of the reflection coefficients from the active and passive parts of the circuit must be larger than unity with zero phase. This product is denoted as an open-loop gain. To evaluate this, the circuit has to be split up into two sub circuits. In Fig. 4. 1, the following oscillator is divided in to two sub circuits at the emitter of the transistor and the resulting open-loop gain is derived as [31]

$$r_P r_E = S_v 4.1$$

The reflection type oscillator has been studied widely in the literature [32, 33].

Fig. 4.1. Simplified schematic of the reflection type oscillator.

#### 4.1.1 Phase Noise

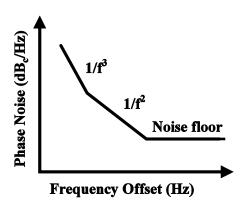

One of the primary tasks in developing transmit and receive modules is to realize low oscillator phase noise. This is necessary not only in the development and production of state-of-the-art communications systems, but also in broadband applications such as radar. An ideal oscillator would have a frequency spectrum that consists of a Dirac delta function centered at the output frequency [37]. However, in general the real oscillators are implemented with physical devices. These devices have inherent noise which manifests itself in both the amplitude and phase of the oscillator output. The amplitude variations can be well-controlled and they have less impact on system performance. But phase variations may be in discrete

(mixer product or harmonics), or random (thermal or random noise sources) in nature [23]. Fig. 4.2 shows a typical phase noise plot with three different phase noise characteristic regions; namely, the  $1/f^3$  region, the  $1/f^2$  region and the frequency independent noise floor. The  $1/f^3$  noise appears at very low frequency offset for active devices. Noise in  $1/f^2$  is the primary concern of oscillator design. This region results from thermal noise sources in the oscillator. Finally, the flat section at high frequencies is usually seen in the measurement, and can be attributed to the noise floor of the circuit or measurement instrument. The phase noise of oscillators has been studied widely in the literature and noise modeling is discussed in the time domain [34] and also in the frequency domain [35, 36].

Fig. 4.2. Typical oscillator phase noise spectrum.

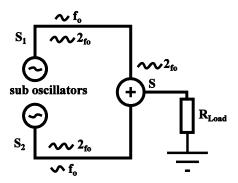

# 4.1.2 Push-Push Topology

The basic principle of push-push approach is to employ a symmetric topology with the spectral components at the fundamental frequency  $f_0$  (and all odd harmonics) operated differentially, i.e., 180 degrees out-of-phase. The general signals of the two sub oscillators are given by

$$S_1(t) = \sum_{n=0}^{\infty} (a_n \cdot \sin(n\omega_0 t + \varphi_n))$$

(4.2)

$$S_2(t) = \sum_{n=0}^{\infty} (a_n \cdot \sin(n\omega_0 t + \varphi_n + n\pi))$$

$$\tag{4.3}$$

The spectral components have the same amplitudes  $a_n$  and differ only in phase by  $n\pi$  while n is the harmonic index. The output signal is the sum of the two sub oscillator signals

$$S(t) = \sum_{n=2,4,...}^{\infty} (2. a_n. \sin(n\omega_0 t + \varphi_n))$$

(4.4)

These signals are combined so that the fundamental signal and the odd harmonics cancel out due to the phase difference, while the second harmonic  $2f_0$  and even harmonics add constructively (see Fig. 4.3). Hence, in a proper operating push-push oscillator, power is delivered to the load only at the even harmonics  $2f_0$ ,  $4f_0$ , ..... Efficient operation of the circuit is obtained, when both sub oscillators operate at the same idling frequency  $f_0$  and stable odd mode operation is ensured [38].

Fig. 4.3. The push-push principle.

# 4.2 Oscillators on Transferred Substrate (TS) DHBT Process

This section presents design and measured performance of a highly efficient 96 GHz, a 197 GHz fundamental oscillator and a 290 GHz harmonic oscillator. These oscillators have been fabricated using the transferred substrate (TS) DHBT process, which is described in Section 2.2.

## 4.2.1 Design and Characterization

#### 4.2.1.1 96 GHz Fundamental Oscillator

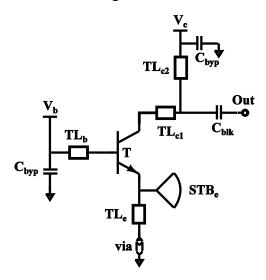

The oscillator circuit developed uses a single emitter-finger HBT with an emitter size of  $0.8 \times 5~\mu\text{m}^2$  and a  $f_T/f_{MAX}$  of 370/370 GHz. In order to keep power consumption as low as possible and to achieve the maximum oscillation frequency, the circuit is designed as single-transistor structure based on a reflection-type oscillator topology, with the HBT operated in common base configuration. The schematic diagram of the circuit is shown in Fig. 4.4. In this oscillator's design, the emitter port of the transistor is used as a split point to make the

oscillator sub circuits called active and passive part. The active part of the circuit consists of transmission lines  $TL_b$ ,  $TL_{c1}$ ,  $TL_{c2}$  and the HBT, the passive part of the circuit includes the radial stub and the transmission  $TL_e$  with a ground via.

Fig. 4.4. Schematic of the 96 GHz fundamental oscillator.

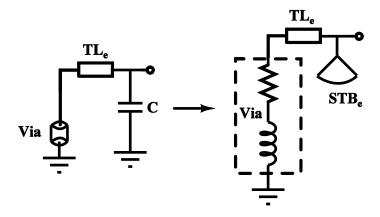

A transmission-line section TL<sub>b</sub> is used to boost the negative impedance seen when looking into the emitter and collector of the transistor (T). In addition, the impedances formed by the lines TL<sub>c1</sub> and TL<sub>c2</sub> on the collector side cause the transistor (T) to become more unstable. To achieve the required oscillation condition in the passive part of the oscillator, the transmission line TL<sub>e</sub> and the parallel MIM capacitor are used to adjust the phase slope and magnitude. Fig. 4.5 shows the passive part of the oscillator circuit. In order to avoid a frequency shift due a small MIM capacitor value and its parasitic, a radial stub (STB<sub>e</sub>) has been introduced. All transmission lines are realized as thin-film microstrip geometries. To fulfil the stable oscillation condition, the phase steepness of the reflection coefficient on the emitter port is set to zero by optimizing TLc1, TLc2, TLe and the radial stub (STBe) with a ground via. The collector lines TL<sub>c1</sub> and TL<sub>c2</sub> are also used for impedance matching and to maximize the output power. The circuit is designed so that it can operate without any resistive feedback or particular biasing topology, which would decrease efficiency. A blocking capacitor (C<sub>blk</sub>) is included at the output to facilitate future integration with frequency multipliers or mixers. Finally, post layout simulation has been performed and optimized using ADS harmonic balance simulation tool, assisted by a 2.5D planar EM-simulator.

Fig. 4.5. Passive sub circuit at the emitter port of the oscillator.

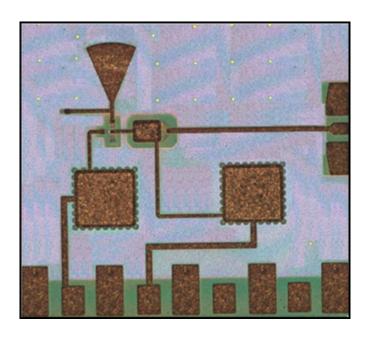

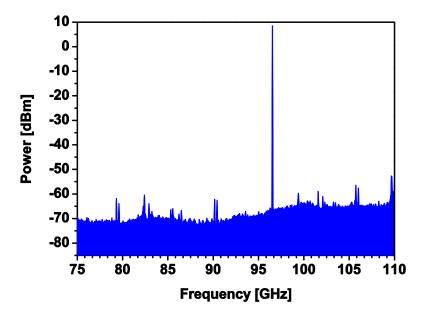

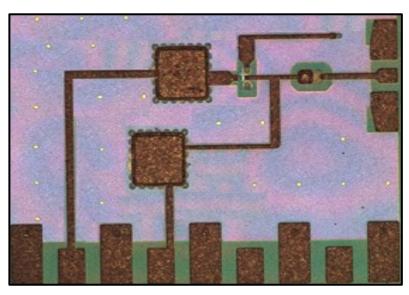

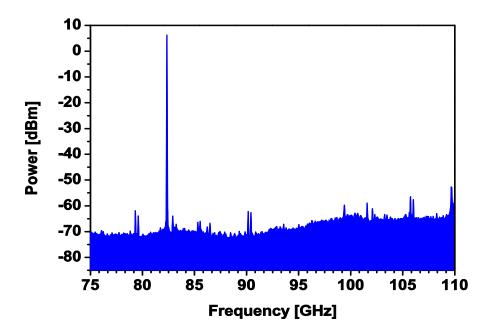

Fig. 4.6 shows a chip photograph of the designed oscillator circuit. The chip area is  $0.9 \times 0.8 \text{ mm}^2$ . The circuits were characterized on-wafer with the setup shown in Fig. 4.7. The output spectrum of the oscillator is investigated using a W band ground-signal-ground (GSG) with a pitch of  $100 \, \mu m$  on-wafer WR-10 waveguide probe from GGB industries and WR-10 sub-harmonic mixer (SHM) from RPG. The principle of signal source characterization is described in Section 3.3.4. Fig. 4.8 shows the deembedded measured spectrum.

Fig. 4.6. Chip photo of the 96 GHz fundamental oscillator.

Fig. 4.7. Test setup for frequency spectrum and output power.

In order to measure actual peak power of the circuit, probe and waveguide system losses have to be deembedded. The insertion loss of the output probe is 1.35 dB as given by the vendor and the waveguide bend and tapers are estimated to contribute 3 dB insertion losses in the 96 GHz band. Accordingly, the measured output power values need to be corrected by +4.35 dB to account for the losses of probe, waveguide extension, and tapers. Thus, one arrives at an actual output power of +8.7 dBm. DC consumption is only 30 mW from a 1.6 volts power supply, which corresponds to 25 % DC-to-RF efficiency.

Fig. 4.8. Measured output frequency spectrum of the 96 GHz fundamental oscillator (cable and prober loss deembedded).

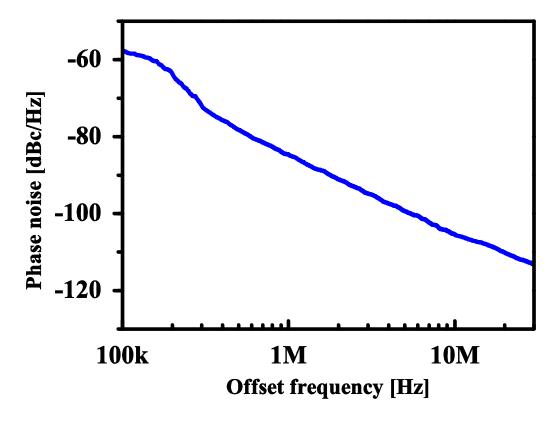

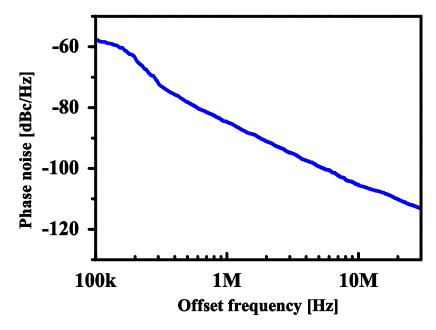

The phase noise measurement was performed using an FSUP signal source analyzer. A common easier and faster procedure has been followed in FSUP analyzer, where all important oscillator parameters, such as power, loop bandwidth and IF gains are set automatically in order to generate stable setting for the analyzer PLL loop. The measured phase noise characteristics of the implemented oscillator are presented in Fig. 4.9. One finds values of -90 and -118 dBc/Hz at offsets of 1 MHz and 10 MHz, respectively. According to equation 4.5, a figure of merit (FOM) of -176 and -184 is achieved, respectively. This is an excellent value for this frequency range and a free-running VCO.

$$FOM = L(\Delta f_m) - 20\log\left(\frac{f_0}{f_m}\right) + 10\log\left(\frac{P_{diss}}{1mW}\right)$$

(4.5)

where  $L(\Delta f_m)$  describes the phase noise at an offset frequency  $(\Delta f_m)$ . The second term takes the oscillation frequency (fc) and the last term describes the dc power consumption. Table 4.1 benchmarks the performance of presented oscillator with other published results around 100 GHz frequency range on different technologies. As can be seen, the realized source offers high output power and achieves the best values for DC-to-RF efficiency. It has been published in [125].

Fig. 4.9. Measured phase noise performance of the 96 GHz fundamental oscillator.

Table 4.1 State-of-the-art oscillator around 100 GHz in different technologies

| Ref./<br>Year | Technology              | Frequency [GHz] | P <sub>OUT</sub><br>[dBm] | P <sub>DC</sub><br>[mW] | DC-to-RF<br>Efficiency | Phase noise<br>[dBc/Hz]         | FOM*             |

|---------------|-------------------------|-----------------|---------------------------|-------------------------|------------------------|---------------------------------|------------------|

|               |                         |                 |                           |                         | [%]                    | @ Offset                        |                  |

| [39]<br>2007  | 1000nm<br>InP DHBT      | 98              | 3                         | 360                     | 0.55                   | -90 @ 1 MHz                     | -164.3           |

| [40]<br>2009  | 350nm<br>SiGe HBT       | 80.75           | 12**                      | 240                     | 6.6                    | -97 @ 1 MHz                     | -171.3           |

| [41]<br>2010  | SiGe HBT                | 100             | 8                         | 70                      | 9                      | -88 @ 1 MHz                     | -169.6           |

| [42]<br>2011  | 130nm SiGe<br>HBT       | 92.5            | 6**                       | 90                      | 4.52                   | -102 @ 1 MHz<br>-124.5 @ 10 MHz | -181.8<br>-184.3 |

| [43]<br>2011  | 130nm<br>SiGe HBT       | 83.6            | -16                       | 108                     | 0.0223                 | -108 @ 10 MHz                   | -166.1           |

| [44]<br>2013  | 65nm<br>CMOS            | 103.3           | -2                        | 21                      | 3                      | -112.1 @ 10 MHz                 | -179.2           |

| [45]<br>2013  | 65nm<br>CMOS            | 105             | 4.5                       | 54                      | 5.2                    | -93 @ 1 MHz                     | -176             |

| [46]<br>2014  | HEMT<br>GaN             | 92.7            | 10                        | 648                     | 1.54                   | -90.2 @ 1 MHz                   | -161.4           |

| This<br>work  | 800nm<br>TS InP<br>DHBT | 96              | 8.7                       | 30                      | 24.7                   | -90@ 1 MHz<br>-118 @ 10 MHz     | -176<br>-184     |

<sup>\*</sup>calculated by using equation 4.5 \*\* differential output

#### 4.2.1.2 200 GHz Fundamental Oscillator

In order to evaluate the performance of a fundamental oscillator beyond 100 GHz, a 200 GHz fundamental oscillator has been investigated. This oscillator circuit uses a single emitter-finger HBT with an emitter size of  $0.8 \times 5~\mu\text{m}^2$  and  $f_T/f_{MAX}$  of 370/370 GHz. Similar design procedures as in Section 4.2.1.1 were followed. In this design, the  $TL_{e1}$  transmission line is used instead of a radial stub because the realized capacitor at such a high frequency is smaller compared to low frequency design (see Fig. 4.10). The complete schematic including bias network of the 200 GHz fundamental oscillator is shown in Fig. 4.10.

Fig. 4.10. Schematic of the 200 GHz fundamental Oscillator.

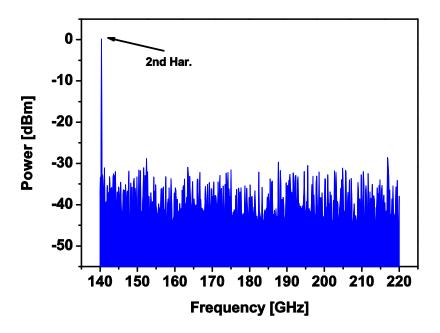

Fig. 4.11 shows a chip photograph of the designed oscillator circuit. The chip area is  $0.85 \times 0.6 \text{ mm}^2$ . The circuits were characterized on-wafer with the setup illustrated in Fig. 4.7. The output spectrum of the oscillator is investigated using a G band ground-signal-ground (GSG) with a pitch of 50  $\mu$ m on-wafer WR-5 waveguide probe from GGB industries and WR-5 sub-harmonic mixer (SHM) from RPG. The measurement procedure of the signal source is mentioned in Section 3.3.4. Fig. 4.12 shows the deembedded measured spectrum.

Fig. 4.11. Chip photo of the 200 GHz fundamental oscillator.

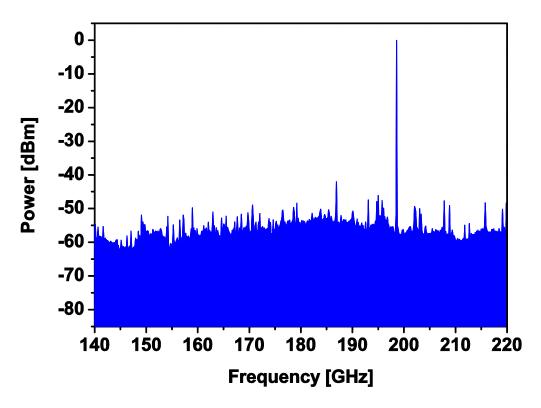

Fig. 4.12. Measured output frequency spectrum of the 200 GHz fundamental oscillator (cable and prober loss deembedded).

For power, the measured output power levels need to be corrected by a value of 7.5 dB to account for the losses of the probe, waveguide extension, and tapers. After correcting for the losses, one obtains an oscillator output power of 0 dBm. The DC power consumption is only 22 mW from a 1.4 volts power supply, which corresponds to 4.6 % DC-to-RF efficiency. Phase noise is estimated from the measured output spectrum to be below -82 dBc/Hz at 1 MHz offset. Table 4.2 benchmarks the performance of realized oscillator with other published frequency source results on different technologies. As can be seen, the realized source offers among the highest output powers in the 200 GHz frequency range and achieves the best efficiency. It has been published in [47].

Table 4.2 State-of-the-art oscillator in different technologies

| Ref./<br>Year | Technology              | Frequency<br>[GHz] | P <sub>OUT</sub> [dBm] | P <sub>DC</sub><br>[mW] | DC-to-RF<br>Efficiency<br>[%] | Phase noise<br>[dBc/Hz]<br>@ Offset |

|---------------|-------------------------|--------------------|------------------------|-------------------------|-------------------------------|-------------------------------------|

| [48]<br>2007  | 500nm<br>InP DHBT       | 210                | 2                      | 60                      | 2.6                           | N/A                                 |

| [49]<br>2008  | 35nm<br>InP HEMT        | 330                | -5.7                   | 16                      | 1.7                           | N/A                                 |

| [50]<br>2009  | 90nm<br>CMOS            | 196.5              | -19                    | 29                      | 0.087                         | -94 @ 1 MHz                         |

| [51]<br>2010  | 253nm<br>InP DHBT       | 267.4              | -2.1                   | 110                     | 0.56                          | -96.6 @ 10 MHz                      |

| [52]<br>2010  | 130nm<br>SiGe HBT       | 184.2              | -11                    | 95                      | 0.084                         | N/A                                 |

| [53]<br>2012  | 65nm<br>CMOS            | 290                | -1.2                   | 325                     | 0.23                          | -78 @ 1 MHz                         |

| [54]<br>2012  | 90nm<br>CMOS            | 228                | -6.2                   | 86.4                    | 0.3                           | -90.5 @ 1 MHz                       |

| [55]<br>2013  | 130nm<br>SiGe HBT       | 201.5              | -7.5                   | 30                      | 0.64                          | -87 @ 1 MHz                         |

| This<br>work  | 800nm<br>TS InP<br>DHBT | 197                | 0                      | 22                      | 4.6                           | -82@ 1 MHz                          |

#### 4.2.1.3 290 GHz Harmonic Oscillator

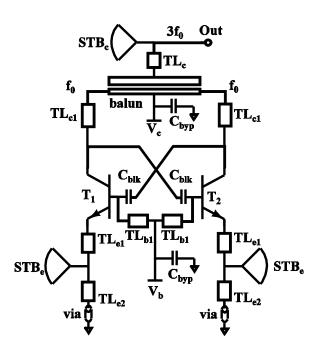

This section presents a 290 GHz harmonic oscillator. The harmonic oscillator was synthesized employing a third harmonic J-band cross-coupled oscillator topology. The oscillator is based on a fundamental cross-coupled designed at 96 GHz with the harmonic extraction using a Marchand balun. The Marchand balun is used as a band pass filter with sufficient fundamental and second harmonics rejection. Fig. 4.13 presents the simplified schematic diagram of the harmonic oscillator. The first consideration was to design a fundamental cross-coupled oscillator in both the small-signal and large-signal case. The crosscoupled oscillator circuit uses a single emitter-finger HBT with an emitter size of 0.8 ×5 µm<sup>2</sup> and ft/fmax of 280/300 GHz each. In order to keep power consumption as low as possible and to achieve the maximum oscillation frequency, the oscillator circuit is designed as single transistor structure. The transmission lines TLc1, resonators using radial stubs (STBe) and transmission lines (TLe1, TLe2) are optimized to generate negative impedance seen when looking into collector of the transistor pairs (T1, T2). All transmission lines are realized as thin-film microstrip geometries. The entire transmission line network in the layout including an additional cross connection and the vias were considered to fulfill the oscillation condition (see Fig. 4.13).

Fig. 4.13. Schematic of the harmonic Oscillator.

The capacitive coupling  $C_{blk}$  in the feedback path permits the base bias voltage to be adjusted through  $V_b$ . It also prevents the base collector junction from being forward biased, and therefore optimizes the signal amplitudes at the base nodes without driving the transistor into saturation. In this manner, the cross-coupled oscillator design is completed. After that a compact broad band Marchand balun was realized at 290 GHz center frequency. The transmission line  $TL_c$  and the radial stub  $STB_c$  are used for impedance matching and to maximize the output power. In order to avoid complex layout routing, the collector bias voltage  $V_c$  of the transistor pair  $(T_1, T_2)$  was fed through the balun. A harmonic balance analysis was performed to ensure the oscillator functionality. The transmission lines, including the Marchand balun were optimized using a 2.5D EM-simulator.

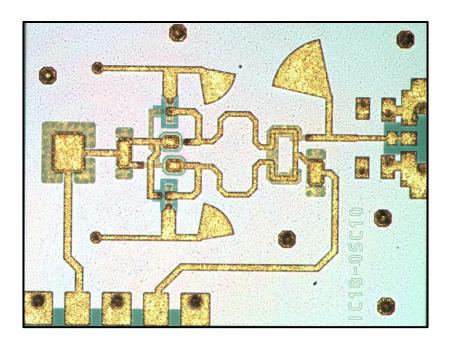

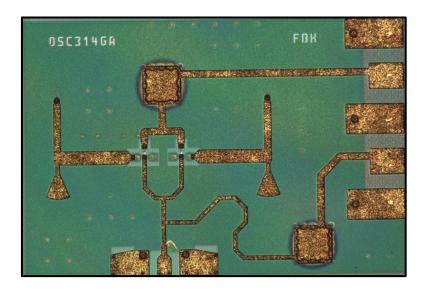

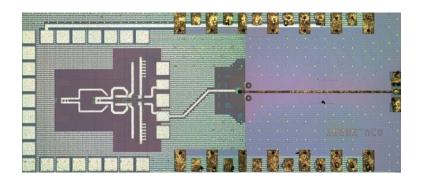

Fig. 4.14 shows the chip photograph of the harmonic oscillator circuit. The chip area of the oscillator circuit is  $1\times0.75$  mm<sup>2</sup> including RF and DC pads. The output RF GSG pad is designed to fit both 100  $\mu$ m and 50  $\mu$ m pitch GSG on wafer probing. This RF pad is also optimized for future flip chip mounting. Thermal vias are visible on top of the chip photo, which extend down to the AlN substrate to spread the heat away from the transistor.

Fig. 4.14. Chip photo of the 290 GHz harmonic oscillator.

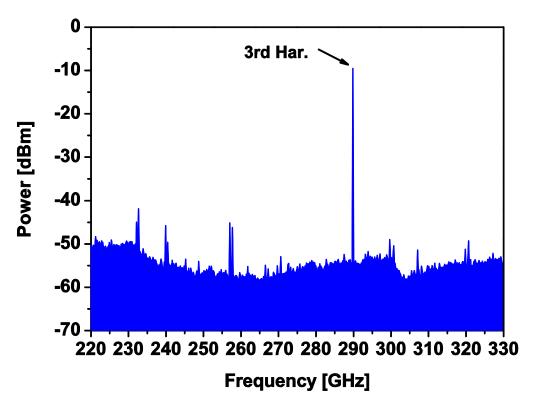

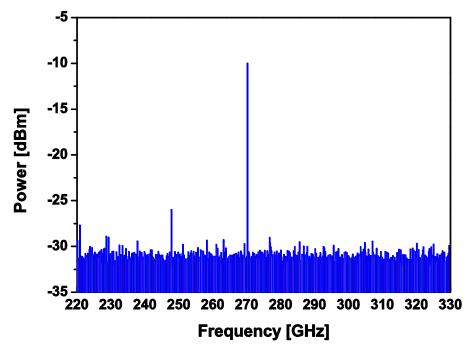

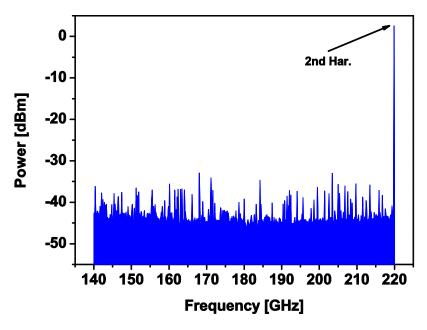

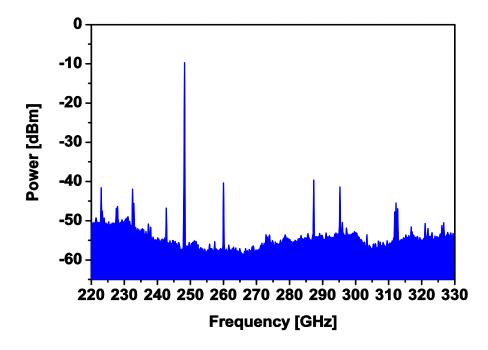

The output of the oscillator is measured using a J-band ground-signal-ground (GSG) on-wafer WR-3.4 waveguide probe from Cascade Microtech with a dedicated WR-3.4 sub-harmonic mixer (SHM) from RPG. The test setup for frequency spectrum and output power is shown in Fig. 4.7. The characterization of the circuit is described in Section 3.3.4. The measured output spectrum is presented in Fig. 4.15.

Fig. 4.15. Measured output frequency spectrum of the 290 GHz harmonic oscillator (cable and prober loss deembedded).

In order to investigate output power of the circuit, the waveguide system loss (this includes probe, waveguide and taper) needs to be estimated. The insertion loss of the output probe is 5.5 dB as provided by the vendor and the waveguide bend and tapers are considered to contribute 3 dB insertion loss in the 290 GHz band. After having all the losses, the measured output power values need to be corrected by +8.5 dB. Thus, one arrives at an actual output power of -8.5 dBm. The DC power consumption is only 28 mW from 1.5 volts power supply, which corresponds to 0.5 % DC-to-RF efficiency. An accurate phase noise measurement using a spectrum analyzer at such high frequencies is very difficult, due to the impact of the down-conversion mixer and the relatively high phase noise of the local oscillator (LO) used. Table 4.3 benchmarks the performance of realized harmonic oscillator with other published harmonic oscillator results using different technologies. As can be seen, the implemented oscillator offers good output power beyond 220 GHz frequency range and achieves the best efficiency values. It has been published in [56].

Table 4.3 State-of-art comparison reported harmonic oscillators beyond 220 GHz on different technologies

| Ref./<br>Year | Technology                         | f <sub>MAX</sub><br>[GHz] | Harmonic<br># | f <sub>OSC</sub><br>[GHz] | P <sub>OUT</sub><br>[dBm] | P <sub>DC</sub><br>[mW] | DC-to-RF<br>Efficiency<br>[%] |

|---------------|------------------------------------|---------------------------|---------------|---------------------------|---------------------------|-------------------------|-------------------------------|

| [57]<br>2012  | 65nm<br>CMOS                       | ~200                      | 4             | 290                       | -1.2                      | 325                     | 0.23                          |

| [57]<br>2012  | 65nm<br>CMOS                       | ~200                      | 4             | 320                       | -3.3                      | 339                     | 0.14                          |

| [58]<br>2012  | 65nm<br>CMOS                       | >195                      | 3             | 288                       | -1.5                      | 275                     | 0.23                          |

| [59]<br>2011  | 130nm<br>CMOS                      | 135                       | 3             | 256                       | -17                       | 71                      | 0.03                          |

| [59]<br>2011  | 65nm<br>CMOS                       | ~200                      | 3             | 482                       | -8                        | 61                      | 0.3                           |

| [60]<br>2008  | 90nm<br>CMOS                       | 160                       | 4             | 324                       | -46                       | 12                      | 2.1e-6                        |

| [61]<br>2012  | 90nm<br>CMOS                       | ~175                      | 3             | 228                       | -6.5                      | 86.4                    | 0.26                          |

| [62]<br>2009  | 130nm<br>SiGe                      | >280                      | 4             | 312                       | -62.4                     | 58                      | 0.01e-6                       |

| [63]<br>2007  | 130nm<br>SiGe                      | 275                       | 2             | 278                       | -20                       | 132                     | 0.008                         |

| [64]<br>2014  | 130nm<br>SiGe                      | 450                       | 2             | 367                       | -8                        | 64                      | 0.25                          |

| [65]<br>2014  | 800nm<br>InP TS D-HBT<br>on BiCMOS | 300                       | 2             | 270                       | -9.5                      | 31                      | 0.4                           |

| This work     | 800nm<br>InP TS D-HBT              | 300                       | 3             | 290                       | -8.5                      | 28                      | 0.5                           |

#### 4.3 Oscillators On InP-on-BiCMOS Process

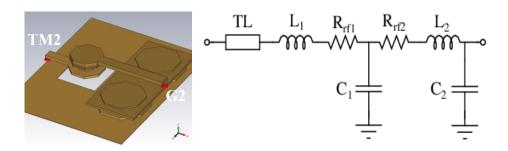

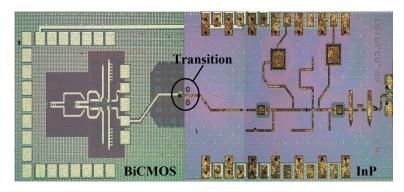

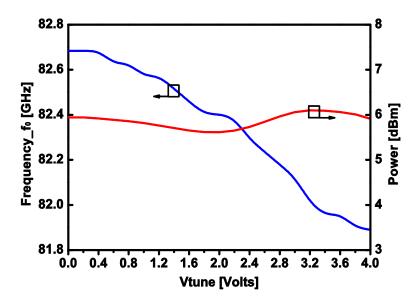

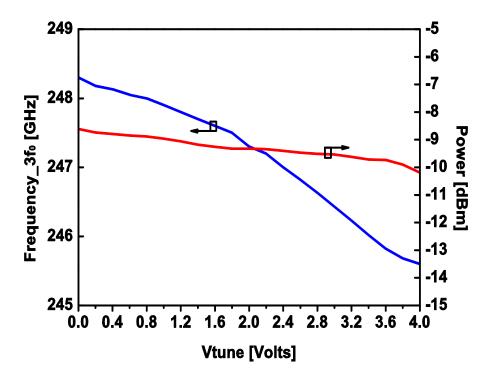

This section presents design and measured performance of two 162 GHz and 270 GHz push-push oscillators. The advantages of push-push oscillators are that they can provide relatively high mm-wave output power, exhibit low phase noise and allow extending the output frequency close to the maximum oscillation frequency of the transistors or even beyond. It can also be used for locking the oscillator with a PLL loop operating at the fundamental frequency instead of the second harmonic [66], thus saving one divide-by-two stage. These oscillators have been fabricated using transferred substrate (TS) InP-DHBT on SiGe BiCMOS process. The InP-DHBT-on-BiCMOS process offers both InP HBT and BiCMOS technologies but in this case only the InP part has been used. The InP-on-BiCMOS process is described in Section 2.3.

#### 4.3.1 Design and Characterization

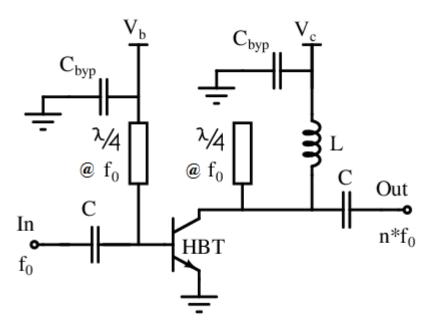

#### 4.3.1.1 Push Push Oscillator Design

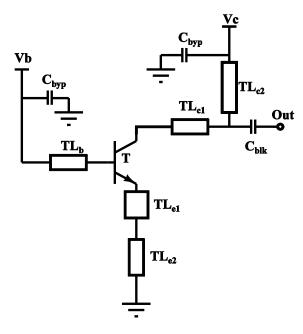

In this section, the proposed push-push oscillator was synthesized based on a reflection-type oscillator topology. The first consideration was to design one sub-oscillator in both the small-signal and large-signal case. The sub-oscillator circuit uses a single emitter-finger HBT with an emitter size of  $0.8\times5~\mu\text{m}^2$  and  $f_T/f_{MAX}$  of 280/300 GHz. In order to keep power consumption as low as possible and to achieve the maximum oscillation frequency, the sub-circuit is designed as single transistor structure, with the HBT operated in common base configuration.

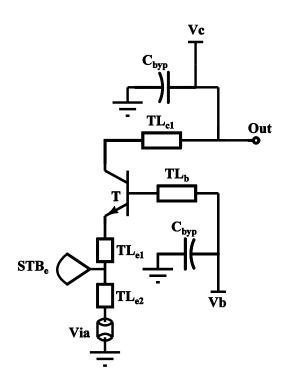

Fig. 4.16. Schematic of the sub oscillator.

A transmission-line section  $TL_b$  is used to boost the negative impedance seen when looking into the emitter and collector of the transistor (T). (see Fig. 4.16) The transmission lines are all realized as thin-film microstrip geometries. The impedances formed by the lines  $TL_{c1}$  on the collector and the line  $TL_e$  on the emitter side cause the transistor (T) to become more unstable and define the steepness of the phase. To fulfill the oscillation condition, the phase of the reflection coefficient at the emitter port is set to zero by optimizing  $TL_{c1}$  and adding a resonator using a radial stub and a transmission line with a ground via. In this manner, one sub-oscillator configuration is completed. In general, there are three possible

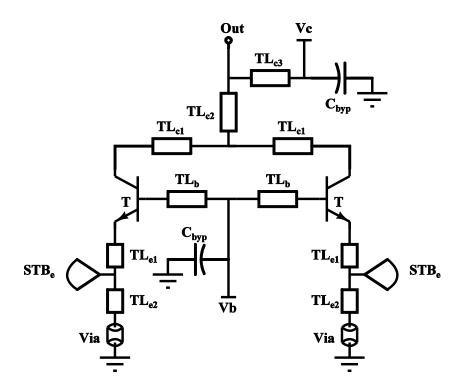

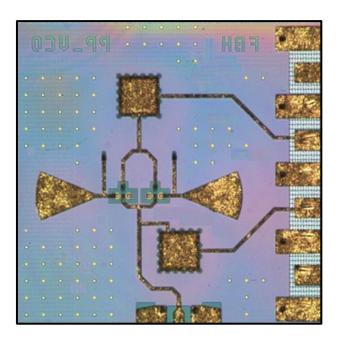

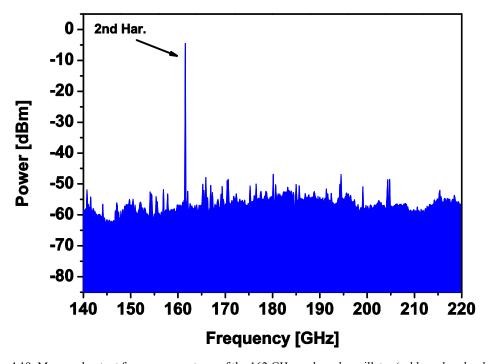

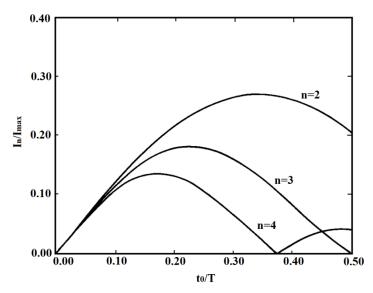

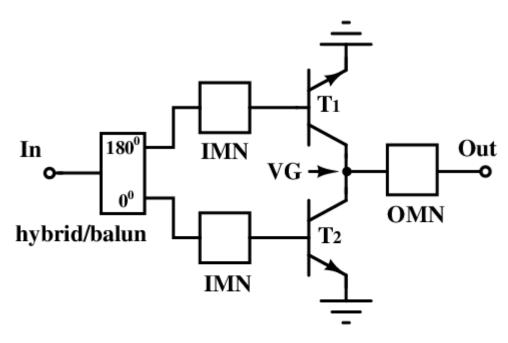

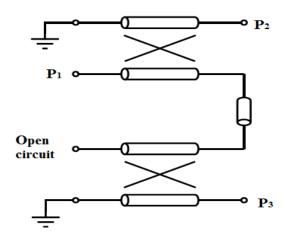

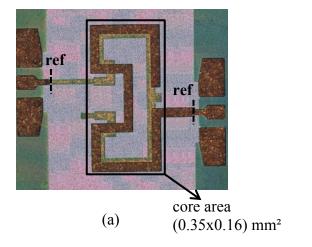

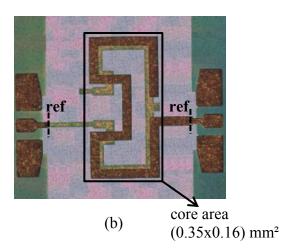

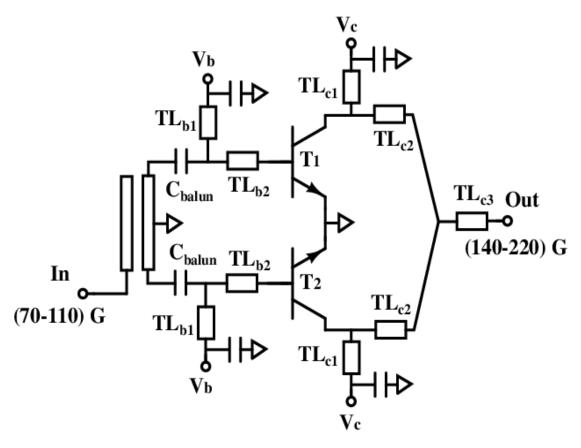

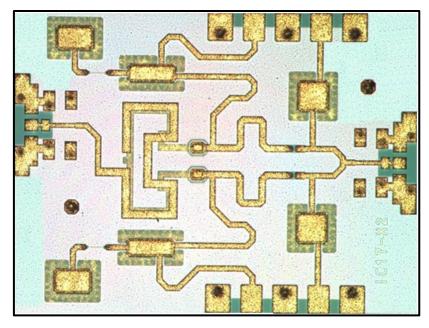

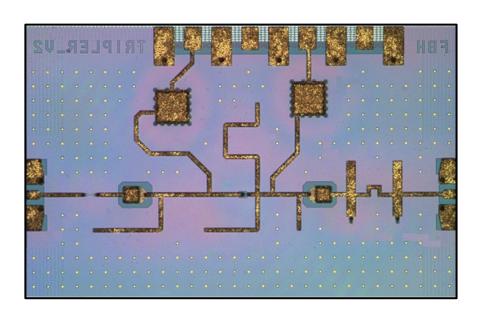

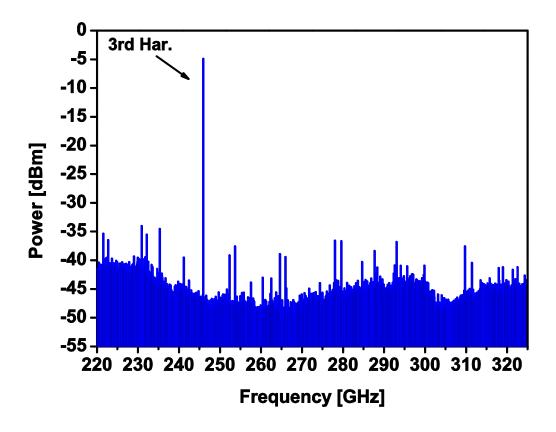

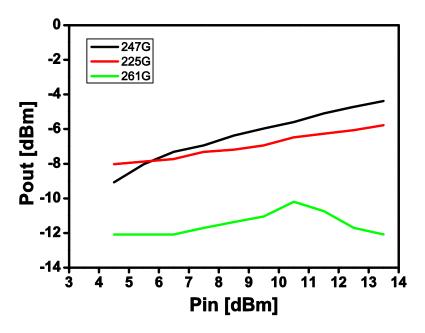

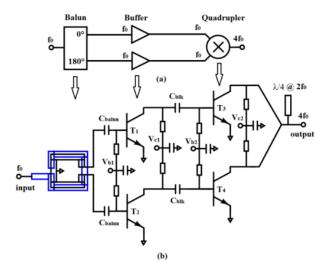

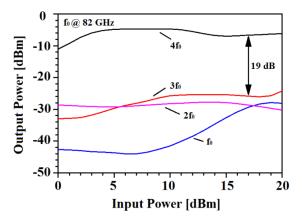

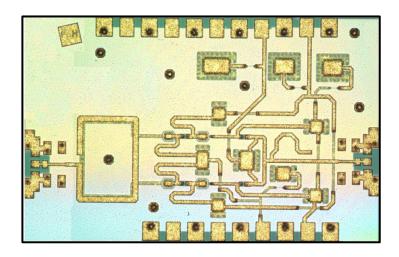

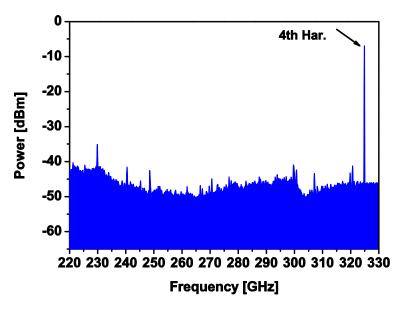

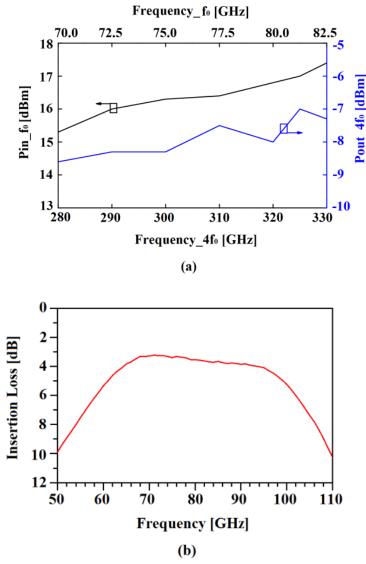

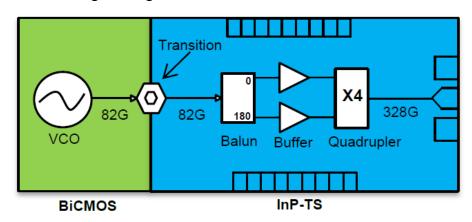

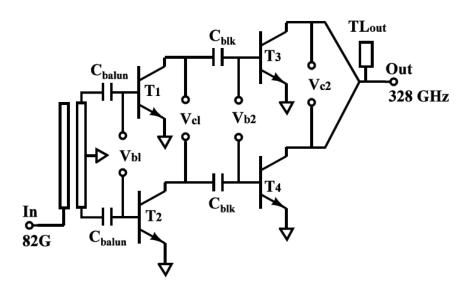

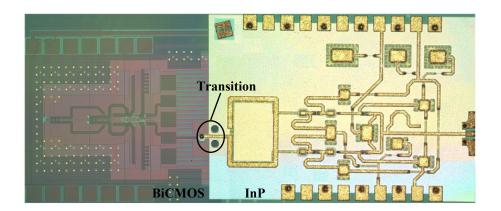

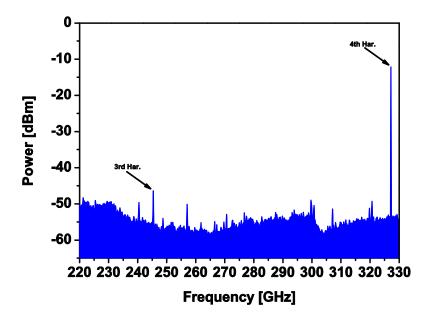

ways to extract the second harmonic push-push output of the HBTs. It can be taken either from the base, emitter, or collector. The largest signal swing can be obtained at the collector by directly shorting the differential output, similar to the drain-connected HEMT push-push oscillators proposed in [67]. A further advantage of directly shorting the fundamental output at the collector is that the large-signal swing at this node is reduced, enabling more robust operation in terms of base collector breakdown [66]. The circuit diagram of the whole oscillator including its bias network is drawn in Fig. 4.17. The collector lines TL<sub>c2</sub> and TL<sub>c3</sub> are used for impedance matching and to maximize the output power. A harmonic balance analysis was performed to ensure the push-push oscillator functionality. The transmission lines were optimized using Agilent ADS, assisted by a 2.5D planar EM-simulator.