## Modeling Attack Security of Physical Unclonable Functions based on Arbiter PUFs

vorgelegt von

Master of Science (SUNY)

Nils Wisiol ORCID: 0000-0003-2606-614X

an der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades Doktor der Naturwissenschaften – Dr. rer. nat. –

genehmigte Dissertation

Promotionsausschuss:

Vorsitzender: Prof. Dr.-Ing. Jan Nordholz Gutachter: Prof. Dr. Jean-Pierre Seifert Gutachter: Prof. Dr. Marian Margraf Gutachter: Prof. Dr. Stefan Katzenbeisser Gutachter: Prof. Debdeep Mukhopadhyay, Ph.D.

Tag der wissenschaftlichen Aussprache: 25. April 2022

Berlin 2022

The concept of Physical Unclonable Functions (PUFs) is an attempt to base cryptography on physical possession. This is in contrast to conventional cryptography, where the essential difference of participants in a cryptographic protocol is their knowledge of secret information such as keys and nonces.

The literature has a rich body of suggestions for the realization of PUFs. This thesis explores designs of variants and compositions of the Arbiter PUF, which has been introduced in 2002 as a CMOS-compatible, electrical PUF design, and has received much research attention since then, albeit being insecure with respect to modeling attacks.

After revisiting modeling attacks on the Arbiter PUF and XOR Arbiter PUF, we demonstrate attacks against the Lightweight Secure XOR Arbiter PUF, Feed-Forward Arbiter PUF, and the Interpose PUF. We introduce two novel PUF designs, the Beli PUF and the LP-PUF, and analyze their security against modeling attacks. We concluding that the LP-PUF is resilient against currently known modeling attacks.

Physical Unclonable Functions (PUFs) sind ein Versuch, Kryptographie auf der Basis von physikalischem Besitz aufzubauen, anstatt, wie bisher üblich, Teilnehmer eines kryptographischen Protokolls anhand ihrer Kenntnis oder Unkenntnis eines kryptographischen Geheimnisses wie beispielsweise Schlüsseln oder Nonces zu unterscheiden.

In der Literatur gibt es viele Vorschläge für die Implementierung von PUFs. Diese Dissertation untersucht PUF Designs, welche auf Variationen und Kombinationen des Arbiter PUF Designs beruhen. Arbiter PUFs wurden 2002 als CMOS-kompatibles, elekrtisches PUF Design vorgestellt und haben in der Wissenschaft viel Aufmerksamkeit erhalten, wenn auch die Arbiter PUF unsicher hinsichtlich Modellierungsangriffen ist.

Nach der Vorstellung bisheriger Modellierungsangriffe auf die Arbiter PUF und XOR Arbiter PUF zeigen wir Angriffe auf die Lightweight Secure XOR Arbiter PUF, Feed-Forward PUF und Interpose PUF. Anschließend stellen wir zwei neue PUF Designs, die Beli PUF und die LP-PUF vor und untersuchen ihre Sicherheit gegen Modellierungsangriffe. Wir folgern, dass die LP-PUF resilient gegen bekannte Modellierungsangriffe ist.

# Contents

| 1. | Intro | oductio  | n                                   | 5  |

|----|-------|----------|-------------------------------------|----|

| 2. | Phys  | sical Uı | nclonable Functions                 | 9  |

|    | 2.1.  |          | ty Properties and Metrics           | 9  |

|    | 2.2.  |          | xer Model                           |    |

|    | 2.3.  | Model    | ing Attacks                         | 12 |

|    |       | 2.3.1.   | Machine Learning Attacks            | 13 |

|    |       | 2.3.2.   | Specialized Attacks                 |    |

|    |       | 2.3.3.   |                                     |    |

|    | 2.4.  | Hardw    | vare Security                       |    |

| 3. | XOF   | R Arbit  | er PUF                              | 16 |

|    | 3.1.  | Arbite   | r PUF                               | 16 |

|    | 3.2.  | XOR A    | Arbiter PUF                         |    |

|    | 3.3.  | Metric   | °S                                  | 20 |

|    |       | 3.3.1.   |                                     |    |

|    |       | 3.3.2.   | Implementation                      | 23 |

|    | 3.4.  | Logist   | ic Regression Attack                | 23 |

|    | 3.5.  | Physic   | al Attacks                          | 28 |

|    | 3.6.  | Neural   | l Network Attacks                   | 28 |

|    |       | 3.6.1.   | Revisited: Santikellur et al.       | 29 |

|    |       | 3.6.2.   | Revisited: Aseeri et al             | 30 |

|    |       | 3.6.3.   | Revisited: Mursi et al.             | 32 |

|    |       | 3.6.4.   | Comparison                          | 40 |

|    | 3.7.  | Arbitr   | arily Large XOR Arbiter PUFs        | 41 |

|    |       | 3.7.1.   | Stability                           | 42 |

|    |       | 3.7.2.   | Arbiter PUF                         | 43 |

|    |       | 3.7.3.   | Majority Vote Arbiter PUF           | 44 |

|    |       | 3.7.4.   | XOR Arbiter PUF                     | 46 |

|    |       | 3.7.5.   | Number of Votes Required            | 48 |

|    |       | 3.7.6.   | Simulation                          | 50 |

|    | 3.8.  | Reliab   | ility-Based Attacks                 | 50 |

| 4. | XOF   | R Arbit  | er PUFs with Input Transformation   | 53 |

|    |       |          | Transformations: Classic vs. Random | 53 |

|    |       | -        | Pseudorandom Input Transformation   |    |

|    |       | 4.1.2.   | Local Minima                        | 55 |

|     | .2. Input Transformations: Lightweight Secure                          |      |

|-----|------------------------------------------------------------------------|------|

|     | 4.2.1. Feature Vector Correlation                                      | . 56 |

|     | 4.2.2. Improved Attack                                                 | . 58 |

|     | .3. Permutation PUF                                                    | . 60 |

| -   |                                                                        | 60   |

| 5.  | nterpose PUF                                                           | 62   |

|     | .1. Splitting Attack                                                   |      |

|     | 5.1.1. Initial Modeling of the Lower Layer via Random Interpose Bits . |      |

|     | 5.1.2. Modeling of the Upper Layer                                     |      |

|     | 5.1.3. Divide-and-Conquer Attack                                       |      |

|     | .2. Results and Performance Analysis                                   |      |

|     | .3. Neural Network Splitting Attack                                    |      |

|     | .4. Variants of the Interpose PUF                                      |      |

|     | 5.4.1. Design Details and Motivation                                   |      |

|     | 5.4.2. Empirical Results of Deep Learning Modeling Attacks             | . 75 |

| 6   | eed-Forward Arbiter PUF                                                | 77   |

| 0.  |                                                                        |      |

|     | .1. Design                                                             |      |

|     | 2. Evolution Strategies Attacks                                        |      |

|     | .3. Neural Network Attack                                              | . 77 |

| 7.  | Beli PUF                                                               | 82   |

| ••• | .1. Design                                                             |      |

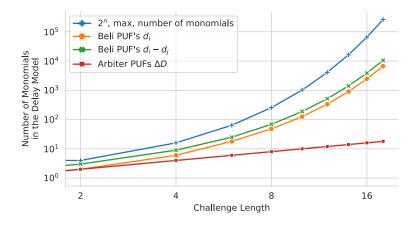

|     | .2. Model Based on Additive Delay Model                                |      |

|     | .3. Implementation and Metrics                                         |      |

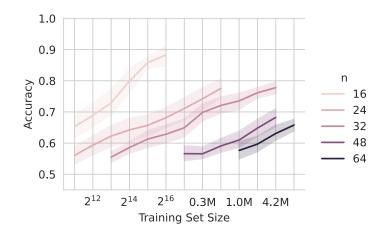

|     | .4. Generic MLP Attack                                                 |      |

|     | .5. Specialized Neural Network Attack                                  |      |

|     | .o. Specialized Neural Network Attack                                  | . 01 |

| 8.  | P-PUF                                                                  | 91   |

|     | .1. Design                                                             | . 91 |

|     | .2. Metrics                                                            |      |

|     | .3. Splitting Attack                                                   |      |

|     | .4. Reliability Attack                                                 |      |

|     | .5. MLP Attack                                                         |      |

|     | .6. Limitations                                                        |      |

|     |                                                                        |      |

| 9.  | ypuf: Python Software Library for PUF Research                         | 101  |

| 10  |                                                                        | 100  |

| 10  | Conclusion                                                             | 102  |

| Bi  | iography                                                               | 105  |

| Α.  | Arbiter PUF Additive Delay Model                                       | 114  |

| В.  | Permutation PUF                                                        | 116  |

# 1. Introduction

In all cryptographic applications deployed today, what distinguishes the legitimate user from an adversary is the knowledge of secret information, usually called the *secret key*. Such secret keys are found everywhere where cryptography is used, including in computers of microscopic scale embedded in digital door keys, credit cards, and passports. As cryptographic algorithms and implementations matured over the years, attacks based on weaknesses of the used ciphers and software code became harder, and gaining access to the secret key itself became an important attack strategy, as a revealed secret key causes all security guarantees of the employed scheme to collapse [AK96; Mah97; KK99].

To remove this weakness, a branch of research on *Physical Unclonable Functions* (PUFs) emerged [Pap+02], where the difference of the legitimate user and adversary is not defined by knowledge, but by possession of a physical object. The physical object, called PUF token, is assumed to exhibit highly individual physical behavior when prompted with an electric or optical input. Further, it is assumed to be (physically) unclonable, meaning that it is inherently impossible to produce two exactly identical tokens. The envisioned secret-free cryptography shall be based on this unique response behavior of each individual unclonable token.

While such PUF-based, secret-free cryptography is by definition immune against attacks that recover any secret key, it may be possible to study the individual behavior of a PUF token and extrapolate its behavior using a mathematical model, in which case it is impossible for a remotely connected party to tell original PUF token and mathematical model apart. In this case, the security of any cryptographic application would collapse, just like in the case of a leaked secret key.

An important tool to create such models from observed behavior is *machine learning*, a highly parameterized and generic approach to create predictions from observed data by using specialized software. In the past two decades, machine learning has emerged as the tool of choice for *PUF modeling attacks* [Gas+04; Rüh+10], where an attacker creates a model of a PUF token which can be used to predict PUF responses with high accuracy, thereby breaking the token's security. Studies on modeling attacks hence represent an essential part of research on PUFs and secret-free cryptography.

In the past 20 years, a large variety of PUF designs and attack strategies have been developed. In this thesis, we revisit milestone designs and attacks, present new analysis strategies, and conclude with a novel PUF design secure against all known modeling attacks.

In Chapter 2, we formally introduce the notion of Physical Unclonable Functions and discuss desired security properties, most importantly, existential unforgeability under chosen and known message attacks.

In Chapter 3, we discuss the design rationale of the Arbiter PUF and XOR Arbiter

PUF, and detail on a variety of different attacks on this PUF design. This includes a discussion of a mathematical model for XOR Arbiter PUF behavior, comparison of different machine learning attacks (including different attacker models), a summary of physical attacks, an extension of the XOR Arbiter PUF that enables mitigation of some attacks by increasing security parameters.

As a different extension of the XOR Arbiter PUF, we discuss XOR Arbiter PUFs with input transformations in Chapter 4. Here, we introduce the correlation attack on the Lightweight Secure PUF and propose a mitigation against it, the Permutation PUF.

In Chapter 5, we discuss the Interpose PUF design as an extension of the XOR Arbiter PUF and demonstrate the Splitting Attack, which reduces the security level of the Interpose PUF to the level of an XOR Arbiter PUF (with respect to the corresponding attacker model).

Subsequently, we discuss modeling attacks on Feed Forward Arbiter PUFs in Chapter 6.

In Chapter 7, we discuss the Beli PUF, an extension of the Arbiter PUF design with respect to its inner works (as opposed to composing larger PUFs out of Arbiter PUFs). We derive a model of the Beli PUF and demonstrate a modeling attack based on it.

Chapter 8 proposes the LP-PUF, a PUF design that we show is resilient against all modeling attacks discussed in this thesis, both for the known and chosen message attack model.

Chapter 9 gives an overview over pypuf, a Python library that includes most code and data used in this thesis. Finally, Chapter 10 summarizes our work and suggests future research directions.

## List of Publications

This dissertation is based on the following publications. The contributions of the author are detailed below.

[WM19] Nils Wisiol and Marian Margraf. "Why Attackers Lose: Design and Security Analysis of Arbitrarily Large XOR Arbiter PUFs". In: *Journal of Cryptographic Engineering* 9.3 (Sept. 2019), pp. 221–230. ISSN: 2190-8516. URL: https://doi.org/10.1007/s13389-019-00204-8 (visited on 10/11/2019)

The authors of the paper jointly developed the theorems and proofs. The author of this dissertation further contributed implementation, data collection, and data analysis of the empirical PUF stability values.

• [Wis+20a] Nils Wisiol et al. "Breaking the Lightweight Secure PUF: Understanding the Relation of Input Transformations and Machine Learning Resistance". In: *Smart Card Research and Advanced Applications*. Ed. by Sonia Belaïd and Tim Güneysu. Lecture Notes in Computer Science. Cham: Springer International Publishing, 2020, pp. 40–54. ISBN: 978-3-030-42068-0

In this work, the author of this dissertation provided an efficient implementation of the attack, developed the analysis methodology, collected and analyzed the experimental data, and developed the countermeasure for the attack, the Permutation PUF.

• [WP20] Nils Wisiol and Niklas Pirnay. "Short Paper: XOR Arbiter PUFs Have Systematic Response Bias". In: *Financial Cryptography and Data Security*. Ed. by Joseph Bonneau and Nadia Heninger. Lecture Notes in Computer Science. Cham: Springer International Publishing, 2020, pp. 50–57. ISBN: 978-3-030-51280-4

The author of this dissertation contributed data collection and analysis as well as a theoretical explanation for the observed phenomenon. He further added the corresponding interpretation and drew the suggested conclusions.

• [Wis+20b] Nils Wisiol et al. "Splitting the Interpose PUF: A Novel Modeling Attack Strategy". In: *IACR Transactions on Cryptographic Hardware and Embedded Systems* (June 2020), pp. 97–120. ISSN: 2569-2925. URL: https://tches.iacr. org/index.php/TCHES/article/view/8584 (visited on 09/01/2020)

The author of this dissertation developed the attack strategy of this work jointly with Christopher Mühl. He contributed the formalization of the attack, as well as the implementation, data collection, data analysis, and interpretation of the attack complexity. The authors of this paper jointly contributed the interpretation of the results.

[Wis+21a] Nils Wisiol et al. Neural-Network-Based Modeling Attacks on XOR Arbiter PUFs Revisited. Tech. rep. 555. 2021. URL: https://eprint.iacr.org/2021/555 (visited on 04/28/2021)

The author of this dissertation discovered the discussed implementation error as well as the replication experiments (with the exception of the replication of Mursi et al. [Mur+20], which was developed jointly). He further developed the improved LR attack, conducted the hyperparameter optimization, data collection, and data analysis. He also contributed the presentation of the results.

• [Agh+22] Anita Aghaie et al. "Security Analysis of Delay-Based Strong PUFs with Multiple Delay Lines". Jan. 2022

In this work, Johannes Tobisch and the author of this dissertation jointly authored the mathematical model of the Beli PUF and the modeling attacks. The author was responsible for the formal analysis of the Beli PUF delay model as well as for implementation and analysis of the modeling attacks.

• [Wis21] Nils Wisiol. Towards Attack Resilient Arbiter PUF-Based Strong PUFs. Tech. rep. 1004. 2021. URL: https://eprint.iacr.org/2021/1004 (visited on 08/19/2021)

This work was authored without collaboration.

• [Wis+21b] Nils Wisiol et al. *Pypuf.* Zenodo. June 2021. URL: https://zenodo. org/record/3901410 (visited on 07/07/2021)

The author of this dissertation is the maintainer of pypuf and, at the time of writing (Version 3.2.1), contributed virtually all simulation, attack, and metric implementations.

Additionally, the author also collaborated in the following publications.

• [WM18] Nils Wisiol and Marian Margraf. Attacking RO-PUFs with Enhanced Challenge-Response Pairs. Tech. rep. 862. 2018. URL: https://eprint.iacr. org/2018/862 (visited on 10/11/2019)

The author developed and formalized the attack.

## 2. Physical Unclonable Functions

Physical<sup>1</sup> Unclonable Functions (PUFs) have been proposed as a method to tie cryptography to a computing device or possession of a physical token. While the exact notion varies, PUFs are usually physical objects that represent a noisy implementation of a mathematical function. Several different use cases have been envisioned, including FPGA IP-protection [SS06; Gua+07], secure key storage [HBF07], and authentication [Pap+02]; also using PUFs as cryptographic primitives has been considered [Brz+11].

In the literature, several different notions of PUFs exist. In this thesis, we opt to use the notions given by Armknecht et al. [Arm+16], which summarize and generalize earlier notions found in the literature [Pap+02; Gas+02; Gua+07; Arm+09; Arm+11; Brz+11; Mae13]. In this framework, a *PUF token* (also *PUF instance* or, abbreviated, *PUF*) is modeled as a *probabilistic mapping*  $f : \mathcal{D} \to \mathcal{R}$ , often with  $\mathcal{D} = \{-1, 1\}^n$  and  $\mathcal{R} = \{-1, 1\}$ . The notion of probabilistic mapping is used in favor of using functions to stress that due to noise, the same input may yield different responses on different occasions. We write  $r \leftarrow f(c)$  to denote that a *response* (a.k.a. *output, behavior*)  $r \in \mathcal{R}$ is generated by PUF f on *challenge* (a.k.a. *input, stimulus*)  $c \in \mathcal{D}$ .

We define a *PUF design* to be the list of all PUFs originating from the same manufacturing process along with the according probability distribution.

Some authors distinguish *strong* and *weak* PUFs depending on the size of their domain  $\mathcal{D}$ , where in the case of strong PUFs, the size of the domain is exponential in the security parameter, and sub-exponential otherwise. PUFs considered in this work have exponentially-sized domains, i.e. are considered strong PUFs.

## 2.1. Security Properties and Metrics

Armknecht et al. [Arm+16] define a variety of PUF security properties with respect to a security parameter  $\lambda$  and attackers using probabilistic polynomial time algorithms. Not all PUF applications require that all of the following properties hold; security definitions predating these general notions considered only subsets.

We re-state some of the security requirements defined by Armknecht et al. [Arm+16]and derive the security metrics of *reliability*, *uniqueness*, and *bias* to be used in this work. The reason to use *metrics* instead of *requirements* is that we are usually unable to conduct an asymptotic analysis of the relevant quantities, but have to resort to simulations fixed

<sup>&</sup>lt;sup>1</sup>Sometimes, a distinction between *Physical* Unclonable Functions and *Physically* Unclonable Functions is made, where the former refers to physical functions that are unclonable (in some sense), and the latter refers to functions (in some sense) which are physically unclonable. We note that both notions can be abbreviated as PUF; the precise meaning of PUF in the context of this work is given by the formal definitions in this chapter.

to security parameters from a certain set. Motivated by the structure of the Arbiter PUF (introduced in Chapter 3), we simplify the notions to the case  $\mathcal{D} = \{-1, 1\}^n$  and  $\mathcal{R} = \{-1, 1\}$ . In this work, the challenge length n is closely related to the security parameter  $\lambda$ . For the Arbiter PUF, we have  $\lambda = n$ ; for other PUF designs, n is one of several security parameters.

For the sake of easier notation, we chose to model bits as values from  $\{-1, 1\}$  rather than  $\{0, 1\}$ . All results can be transformed into  $\{0, 1\}$  notation by "encoding" bits with the function  $\rho : \{-1, 1\} \rightarrow \{0, 1\}$ , where  $\rho(1) = 0$  and  $\rho(-1) = 1$ . This way, we can write  $\rho(b) = \frac{1}{2} - \frac{b}{2}$  and have the convenient property  $\rho(b_1 \cdot b_2) = \rho(b_1) \oplus \rho(b_2)$ , i.e. a group homomorphism, where  $\oplus$  denotes addition modulo 2 and  $\cdot$  denotes multiplication over  $\mathbb{Z}$ .

**Definition 1** (Intra-Distance Requirement). [Arm+16] Whenever a single PUF is repeatedly evaluated with a fixed input, the maximum distance between the corresponding outputs is at most  $\delta_1$ . That is for any PUF f and any  $c \in \mathcal{D}$ , it holds that

$$\Pr\left[\max_{i \neq j} \left\{ d\left(r_i, r_j\right) \right\} \le \delta_1 \mid c \in \mathcal{D}, r_i \leftarrow f(c) \text{ for } 1 \le i \le t \right] = 1 - \epsilon(\lambda).$$

We restrict the intra-distance requirement to PUFs mapping n bits to 1 bit and set  $\delta_1 = 0$  and t = 2 to obtain the notion of *reliability*.

**Definition 2** (Reliability). For a fixed PUF instance f and challenge c, we define *reliability* to be the probability that f will return the same response when queried twice with c, i.e.

$$\Pr[r_1 = r_2 \mid r_i \leftarrow f(c), i \in \{1, 2\}]$$

For a fixed PUF instance f, we define the *reliability* R(f) to be

$$R(f) = \mathbb{E}_{c \in \mathcal{D}} \left[ \Pr\left[ r_1 = r_2 \mid r_i \leftarrow f(c), i \in \{1, 2\} \right] \right].$$

Some reliability of the PUF is needed for it to be practically usable. Higher reliability values are desirable, with values of 1 meaning perfectly reliable. For low reliability, PUF responses are no longer reproducible, depriving the PUF of one of its key features. Note that this definition explicitly includes the case that different challenges c may have different reliability values, which plays an important role on reliability-based attacks on XOR Arbiter PUFs (Section 3.8).

**Definition 3** (Inter-Distance II Requirement). [Arm+16] Whenever multiple PUFs are evaluated on a single, fixed input, the minimum distance among them is at least  $\delta_3$ . That is for any PUF  $f_i$  for  $1 \leq i \leq m$  and any  $c \in \mathcal{D}$ , we have

$$\Pr\left[\min_{i\neq j} \left\{ d\left(r_{i}, r_{j}\right) \right\} \geq \delta_{3} \mid c \in \mathcal{D}, r_{i} \leftarrow f_{i}(c) \text{ for } 1 \leq i \leq m \right] = 1 - \epsilon(\lambda).$$

We restrict the inter-distance II requirement to PUFs mapping n bits to 1 bit and set  $\delta_3 = 1$  and m = 2 to obtain the notion of *uniqueness*.

**Definition 4.** [Uniqueness] For a PUF design  $\mathcal{P}$ , we define the *uniqueness* U( $\mathcal{P}$ ) to be

$$U(\mathcal{P}) = 1 - 2 \operatorname{E}_{f_i \sim \mathcal{P}} \left[ \left| \frac{1}{2} - \Pr_{c \in \mathcal{D}} \left[ r_1 = r_2 \mid r_i \leftarrow f_i(c) \right] \right| \right].$$

The uniqueness measures the difference in behavior of randomly chosen PUF tokens of the same PUF design. If they show correlation or similarity in their behavior, an attacker can use this fact to guess PUF responses of one instance with the assistance of another, unrelated PUF instance. The optimal value of  $U(\mathcal{P})$  hence is 1, arising from the case when  $r_1 = r_2$  happens with probability 1/2.

**Definition 5.** For a PUF design  $\mathcal{P}$ , we define the *bias* B( $\mathcal{P}$ ) to be

$$\mathbf{B}\left(\mathcal{P}\right) = \mathbf{E}_{f \sim \mathcal{P}}\left[\mathbf{E}_{c \in \mathcal{D}}\left[f(c)\right]\right],$$

with zero being the optimal value, given that the responses are from  $\{-1, 1\}$ . (For PUFs with more than one response bit, which are not studied in this work, Armknecht et al. [Arm+16] generalize this to the notion of *min-entropy*.) A low bias is required to reduce the probability that the attacker guesses correctly by choosing the most likely response.

Armknecht et al. [Arm+16] define the notion of *unforgeability* capturing the idea that the PUF's responses should not be predictable based on observed examples of its behavior. While this is also referred to as *unpredictability*, the notion as defined by Armknecht et al. is closely related to the security notions in the context of digital signatures schemes, where "unforgeability" is used. The notion can be parameterized in two dimensions, one specifying precisely which responses of the PUF are unforgeable, the other specifying which capabilities the attacker precisely has available. We give an informal overview over the different flavors of unforgeability, referring the reader to Armknecht et al. [Arm+16] for precise definitions.

In its strongest sense, unforgeable means that the attacker is unable to predict the behavior of the PUF for any (unseen) challenge. This case is referred to as *existential unforgeability* (EUF). The weaker version of *universal unforgeability* (UUF) asserts that the attacker is unable to predict the behavior of the PUF for a challenge chosen uniformly at random.

There are two important classes of attacks the adversary can use to predict ("forge") PUF responses. The weaker attack is the *known message attack* (*KMA*), where the attacker has knowledge of the challenge to the PUF, but cannot choose. The stronger attack setting is the *chosen message attack* (*CMA*), where the attacker can choose the input to the PUF.

We obtain the four PUF unforgeability notions of EUF-CMA, EUF-KMA, UUF-CMA, and UUF-KMA, with EUF-CMA being the strongest notion of security among the four, and UUF-KMA being the weakest.

Even stronger than EUF-CMA unforgeability are the notions of *indistinguishability* (different PUF instances cannot be distinguished based on their observed behavior) and *pseudorandomness* (PUF instances cannot be distinguished from random functions based on their behavior) [Arm+16].

Related to the notion existential unforgeability (EUF) is the question if observed behavior reveals information about the PUF behavior on *related*, i.e. slightly modified, challenge inputs [GTS18].

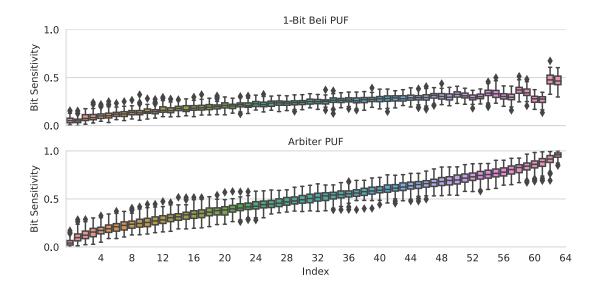

**Definition 6.** For a PUF design  $\mathcal{P}$ , we define *bit sensitivity*  $BS_i(\mathcal{P})$  to be the probability that the response of the PUF changes when the *i*-th input bit is flipped (denoted  $x^{\oplus i}$ ),

$$BS_{i}(\mathcal{P}) = E_{f \in \mathcal{P}} \left[ \Pr_{c \in \mathcal{D}} \left[ f(c) \neq f(c^{\oplus i}) \right] \right].$$

A proper bit sensitivity for all input bit positions  $i \in \{1, ..., n\}$  is necessary (but not sufficient) to prevent attackers from predicting responses when the response to a related challenge is known. The optimal value is 1/2.

While bit sensitivity can only capture one aspect of existential unforgeability, it is an interesting value, as it also relates to the *learnability* of a PUF (when viewed as a Boolean function, Section 2.3.3). Furthermore, Arbiter PUFs have a non-optimal bit sensitivity, so this is an important metric for the analysis of PUF designs based on Arbiter PUFs.

## 2.2. Attacker Model

The standard attacker model for PUFs is based on the promise of increased hardware security of PUF tokens, compared to the traditional approach of cryptographic hardware extended by secure key storage. Hence, in the standard PUF attacker model, the adversary gets physical access to the PUF token for some limited amount of time [Wis+20b]. During this time, a large number of different attacks is conceivable. While this work considers attacks operating on the challenge-response behavior of the PUF, the assumed physical access to the PUF hardware also enables other important classes of attacks which we summarize in Section 2.4.

For the attacks using information about the challenge-response behavior of the PUF, we distinguish chosen message attacks (CMA) and known message attacks (KMA). While the physical access to the PUF generally motivates the study of CMAs, in some cases it is also appropriate to study the weaker KMAs, as done in prior works [Gas+02; Gua+07; Arm+11]. This can be motivated by suggestions for PUF-based authentication protocols which mitigate CMAs by technical means [Maj+12; Yu+16; Yu+14] or by the fact that some KMAs are successful even without choosing challenges (Table 10.1).

## 2.3. Modeling Attacks

Attacks that build a mathematical model from observed challenge-response behavior of the PUF are the main focus of this work. Models that can predict PUF responses with high accuracy can be used as drop-in replacement for the PUF token and can be used to make remote parties believe that the attacker is in possession of the PUF when they are actually not. Security against modeling attacks is captured by the notion of unforgeability as defined in Section 2.1. There exists a large body of research on PUF modeling attacks in the literature, which can roughly be divided into modeling attacks using (practical) machine learning algorithms, modeling attacks using provable methods, and modeling attacks that use specialized machine learning algorithms.

### 2.3.1. Machine Learning Attacks

Machine learning is the field of using algorithms for making predictions based on observed data. Based on a number N of observed examples given as pairs of input  $x_i \in \mathcal{D}$  and output  $y_i \in \mathcal{R}$ , called the training set  $T = \{(x_i, y_i) \mid 1 \leq i \leq N\}$ , a machine learning algorithm outputs a model  $M : \mathcal{D} \to \mathcal{R}$ . The model has high accuracy if the predictions M(x) match observed data well, with x chosen uniformly at random in  $\mathcal{D}$  but omitting known examples from T.

The concept of machine learning matches the attacker definition of the notion of PUF unforgeability (Section 2.1) and is thus well-suited to study PUF modeling attacks. Machine learning was also outside the context of PUFs portrayed as the "opposite" of cryptography [ODo14].

One of the first machine learning algorithms is the Perceptron [MP69], which is also used for the first PUF modeling attack [Gas+04]. While this modeling attack and followup work [Rüh+10] used machine learning algorithms that can only output models of a certain class of functions, with increasing popularity of *deep learning*, also PUF modeling attacks started to use machine learning algorithms that are not restricted to a certain class of models [Yas+16; SBC19; Mur+20; Wis+21a].

Machine learning modeling attacks are usually demonstrated on data obtained either by simulating PUF behavior, or by collecting data from a PUF prototype, or both. They are hence fixed to a certain set of used security parameters. The run time of the attacks is often measured as wall-clock time and thus highly dependent on the used software and hardware, operating system, and configuration.

#### 2.3.2. Specialized Attacks

In contrast to fully generic approaches and approaches only restricted to a broad class of model functions, machine learning algorithms can also be combined with classical algorithms to design highly specialized attacks. This is often useful when attacking PUF embedded in additional logic or when attacking PUFs composed of several different PUF primitives. Delvaux [Del19] demonstrated a collection of such attacks, targeting five PUFs with accompanying obfuscation logic. In Section 3.8, we present a specialized reliability-based attack on the Arbiter PUF. Also the *Splitting Attack* on the Interpose PUF [Wis+20b] presented in Section 5.1 can be understood as a specialized attack in this sense.

#### 2.3.3. Provable Attacks

A third important class of PUF modeling attacks is constituted by applying the theory of *probably approximately correct* (*PAC*) learning algorithms to mathematical models of PUFs. Let  $\mathcal{B}_n$  denote the set of all Boolean functions  $f : \{-1, 1\}^n \to \{-1, 1\}$ . Informally, a subset  $\mathcal{C} \subseteq \mathcal{B}_n$  is said to be *PAC-learnable* if there exists an efficient probabilistic algorithm A that, given access to examples of a function  $f \in \mathcal{C}$ , outputs, with high probability, a hypothesis that achieves high prediction accuracy.  $\mathcal{C}$  is referred to as the *concept class* of A.

For a more formal definition, we quantify the notions of high probability and high accuracy, as well as detail on the access that Algorithm A has on the function f.

**Definition 7.** [ODo14] A probabilistic algorithm A learns a concept class C with error  $0 < \varepsilon < \frac{1}{2}$  if for any  $f \in C$ , with probability at least 90%, A outputs a hypothesis h which satisfies

$$\Pr_{x \in \{-1,1\}^n} \left[ f(x) \neq h(x) \right] \le \varepsilon.$$

Algorithm A can either have access to random examples, i.e. A can draw pairs (x, f(x)) where x is uniformly random in  $\{-1, 1\}^n$ , or have access to queries, i.e. A can request the value f(x) for any  $x \in \{-1, 1\}^n$  of its choice.

The access models correspond to the definitions of known message attack (KMA) and chosen message attack (CMA) of Section 2.1. The choice of 90% is arbitrary; choosing other numbers such as 51% or larger will yield equivalent definitions [ODo14]. The study of PAC learning was initiated by Valiant [Val84] and first used in the context of PUFs by Ganji, Tajik, and Seifert [GTS16]. In contrast to empirical machine learning attacks, algorithms in the PAC learning framework are analyzed on concept classes derived from mathematical models of PUFs, rather than on simulated or real-world data. Hence, analysis of PAC learning algorithms can yield information on the asymptotic complexity of such modeling attacks, rather than just information on a fixed security parameters.

In follow up work, Ganji, Tajik, and Seifert [GTS18] used the PAC-framework to demonstrate modeling attacks against the Bistable Ring PUF using the LMN-Algorithm [LMN93] that are provably resilient to noisy examples in the training set. The proof relies on the assumption that the PUF exhibits only a very limited number of influential bits [Gan+16]. This assumption is justified by observing FPGA data provided by Yamamoto et al. [Yam+14].

The observation that certain properties of the Boolean function implemented by PUFs can give way to provable learnability enabled the use of testing function metrics to gauge the PUF modeling attack resilience [Ngu+16; GFS19].

Using a semi-automated approach, Chatterjee, Mukhopadhyay, and Hazra [CMH20] extended this approach by using metrics in the PAC-framework to analyze composite PUF designs for their PAC learnability. This way, they found the Interpose PUF (Chapter 5), the Feed-Forward Arbiter PUF (Chapter 6), and others to be PAC-learnable.

## 2.4. Hardware Security

As PUFs are considered an alternative to cryptography based on secret keys [Gas+02; Pap+02] to mitigate hardware attacks [AK96; Mah97; KK99], such attacks are included in the attacker model (Section 2.2) and need to be considered when assessing the security of PUFs.

Here, we review hardware attacks on SRAM PUFs [Gua+07] and (XOR) Arbiter PUFs (Chapter 3); later we restrict our attention to modeling attacks in the known message attack or chosen message attack model (Section 2.1) for the remainder of this work.

For SRAM PUFs<sup>2</sup>, Helfmeier et al. [Hel+13] and Nedospasov et al. [Ned+13] demonstrated attacks that are not only able to extract the supposedly secret SRAM value using a variety of methods, but also showed that a SRAM *hardware clone* can be produced. This goes beyond modeling attacks presented in this work not only by using hardware attack surface, but also by producing a functionally identical piece of hardware, rather than just a simulation based on a model. Further extraction methods for SRAM PUFs were later presented by Lohrke et al. [Loh+16].

Tajik et al. [Taj+14] demonstrated an attack based on photon emission analysis on the Arbiter PUF (Chapter 3) that can create a high-precision model even when challenges and responses to the PUF are unknown. Their methodology has data complexity linear in the security parameter. For these reasons, their methodology must be considered a very powerful attack, albeit requiring some preparation on the hardware under attack.

Power and other side-channel attacks also can be threat to PUF implementations. Aghaie and Moradi [AM20] proposed a general technique to protect PUF implementations against attacks based on power side channel analysis.

Ruhrmair [Ruh20] offers a taxonomy with respect to hardware attacks on PUFs.

<sup>&</sup>lt;sup>2</sup>Note that SRAM PUFs  $f : \mathcal{D} \to \mathcal{R}$  have domains of small size and are thus trivially insecure in the EUF-KMA model considered in this work, but constitute an important area of research for PUF hardware attacks.

# 3. XOR Arbiter PUF

## 3.1. Arbiter PUF

An Arbiter PUF is a PUF based on electrical signal delays that vary from chip to chip. It was introduced by Gassend et al. [Gas+02], who argue that the due to mask, temperature, and pressure variations during manufacturing, differences in delays can exceed 5% of the total delay value and are increasing with shrinking device sizes.

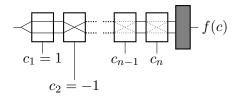

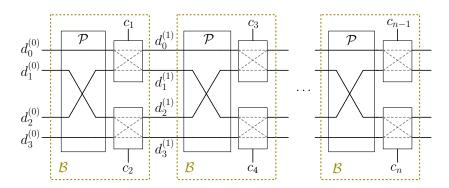

To utilize this intrinsic variability of Arbiter PUFs, two electrical signals start at the same time and travel through a circuit of n stages for a chosen design parameter  $n \in \mathbb{N}$ . At each stage, one bit of the *n*-bit challenge determines whether the signals travel straight through or are interchanged. With the hardware implementation in mind, the stages are sometimes called *multiplexers*. At the end of this *arbiter chain*, an *arbiter* determines on which input a signal arrives first and outputs the result as the *response*. The schematics of an Arbiter PUF are shown in Figure 3.1.1.

Gassend et al. [Gas+04] showed how to model the behavior of Arbiter PUFs using the *additive delay model*. In this model, it is assumed that the total delay of the signal in the Arbiter PUF is the sum of all individual delays along its path. This enabled them to conduct a modeling attack using the Perceptron algorithm [MP69] and to demonstrate high prediction accuracy of their model. Even though their experiments were conducted on FPGAs, this indirectly confirms the accuracy of the additive delay model. A detailed evaluation of the parameters of the additive delay model was done by Lim et al. [Lim+05]. A CMOS implementation of the Arbiter PUF has been studied by Maes et al. [Mae+12]. Delvaux and Verbauwhede [DV13] and Tajik et al. [Taj+14] later confirmed the accuracy of the additive delay model also for proof-of-concept designs implemented in CMOS and FPGA technology, respectively; Utz, Tobisch, and Becker [UTB16] confirmed the

Figure 3.1.1.: Schematic representation of an Arbiter PUF. After setting up the challenge  $c_1, \ldots, c_n$  on the bottom (one for each *stage*), an electrical signal is input on the left-hand side and travels though the circuit. The *arbiter* shown on the right-hand side (gray box) detects if a signal arrives at the top or bottom input first and outputs the response bit f(c) accordingly.

accuracy of the model for commercial Arbiter PUFs.

The additive delay model of Arbiter PUFs is convenient to write when using  $\{-1, 1\}$  as bit values (instead of the more traditional  $\{0, 1\}$ ), as done by Wisiol et al. [Wis+21a].

An Arbiter PUF with n stages, once set up with a challenge  $c \in \{-1, 1\}^n$ , accumulates signal propagation delays for two electrical signals traveling though the stages of the Arbiter PUF. At the *i*-th stage, the additional delays for the two signals are either  $d_i^{\text{TT}}$ and  $d_i^{\text{BB}}$  (if c = -1 and the signals travel straight through) or  $d_i^{\text{TB}}$  and  $d_i^{\text{BT}}$  (if c = 1and the signals are interchanged). We define the total accumulated delay *after* the *i*-th stage as  $d_i^{\text{T}}$  for the top output of that stage, and  $d_i^{\text{B}}$  for the bottom output of that stage. Additional delays are added at each stage, i.e.

$$\begin{split} d_i^{\rm T} &= \begin{cases} d_{i-1}^{\rm T} + d_i^{\rm TT} & (c = -1) \,, \\ d_{i-1}^{\rm B} + d_i^{\rm BT} & (c = 1) \,, \end{cases} \\ d_i^{\rm B} &= \begin{cases} d_{i-1}^{\rm B} + d_i^{\rm BB} & (c = -1) \,, \\ d_{i-1}^{\rm T} + d_i^{\rm TB} & (c = 1) \,. \end{cases} \end{split}$$

The initial delays are zero,  $d_0^{\rm T} = d_0^{\rm B} = 0$ . The delay difference after the *i*-th stage is  $\Delta D_i = d_i^{\rm T} - d_i^{\rm B}$ ; we abbreviate the delay difference after the *n*-th stage to  $\Delta D_n = \Delta D_{\rm Model}$ . This value depends on the given challenge, often denoted *c*, so we sometimes also write  $\Delta D_{\rm Model}(c)$  to emphasize on this dependency.

**Theorem 8.** For  $n \in \mathbb{N}$  and given stage delay values  $d_i^{\text{TT}}, d_i^{\text{TB}}, d_i^{\text{BT}}, d_i^{\text{BB}} \in \mathbb{R}^+$ , with  $1 \leq i \leq n$ , there exists  $w \in \mathbb{R}^n$  and  $b \in \mathbb{R}$  such that for all  $c \in \{-1, 1\}^n$ , it holds that

$$\Delta D_{\text{Model}}(c) = \langle w, x \rangle + b,$$

where  $x = (x_i)_i = \left(\prod_{j=i}^n c_j\right)_i$ . For even *n* we have

$$w = \frac{1}{2} \begin{pmatrix} d_1^{\mathrm{TT}} - d_1^{\mathrm{BB}} - d_1^{\mathrm{BT}} + d_1^{\mathrm{TB}} \\ -d_2^{\mathrm{TT}} + d_2^{\mathrm{BB}} + d_2^{\mathrm{BT}} - d_2^{\mathrm{TB}} + d_1^{\mathrm{TT}} - d_1^{\mathrm{BB}} + d_1^{\mathrm{BT}} - d_1^{\mathrm{TB}} \\ d_3^{\mathrm{TT}} - d_3^{\mathrm{BB}} - d_3^{\mathrm{BT}} + d_3^{\mathrm{TB}} - d_2^{\mathrm{TT}} + d_2^{\mathrm{BB}} - d_2^{\mathrm{BT}} + d_2^{\mathrm{TB}} \\ \\ & \vdots \\ -d_{n-2}^{\mathrm{TT}} + d_{n-2}^{\mathrm{BB}} + d_{n-2}^{\mathrm{BT}} - d_{n-2}^{\mathrm{TB}} + d_{n-3}^{\mathrm{TB}} - d_{n-3}^{\mathrm{BB}} + d_{n-3}^{\mathrm{BT}} - d_{n-3}^{\mathrm{TB}} \\ \\ d_1^{\mathrm{TT}} - d_{n-1}^{\mathrm{BB}} - d_{n-1}^{\mathrm{BT}} + d_{n-1}^{\mathrm{TB}} - d_{n-2}^{\mathrm{TT}} + d_{n-2}^{\mathrm{BB}} - d_{n-2}^{\mathrm{BT}} + d_{n-2}^{\mathrm{TB}} \\ \\ -d_n^{\mathrm{TT}} + d_n^{\mathrm{BB}} + d_n^{\mathrm{BT}} - d_n^{\mathrm{TB}} + d_{n-1}^{\mathrm{TT}} - d_{n-1}^{\mathrm{BB}} + d_{n-1}^{\mathrm{BT}} - d_{n-1}^{\mathrm{TB}} + d_{n-1}^{\mathrm{TT}} - d_{n-1}^{\mathrm{BB}} + d_{n-1}^{\mathrm{BT}} - d_{n-1}^{\mathrm{TB}} \\ \end{pmatrix},$$

Similar formulae exist for odd n.

The proof is relegated to Appendix A.

As the final response bit of the Arbiter PUF is determined by whether there is a signal at the top or bottom input of the arbiter element first, we can conclude that for an *n*-bit Arbiter PUF with physical parameters  $w \in \mathbb{R}^n$  and given challenge  $c \in \{-1, 1\}^n$ , the response *r* will be

$$r = \operatorname{sgn} \Delta D_{\operatorname{Model}} = \operatorname{sgn} \left( \langle w, x \rangle + b \right),$$

using the above definition for  $x \in \{-1, 1\}^n$ . Assuming there is no evaluation noise, from this model we can derive a function  $f : \{-1, 1\}^n \to \{-1, 1\}$  which models the Arbiter PUF behavior by setting  $f(c) = \langle w, x \rangle + b$ .

The additive delay model can thus be understood as a hyperplane in n dimensions, dividing the edges of the Boolean cube  $\{-1,1\}^n$  (and, by extension,  $\mathbb{R}^n$ ) into two regions labeled by the -1 and 1 responses of f. The boundary between the two regions is a linear, or in case of nonzero bias, affine subspace of  $\mathbb{R}^n$ . In this sense, the model can be understood as *linear*; the behavior of the PUF can be described as *linearly separable*.

For a given challenge c, the corresponding value of x according to above definition is referred to as *feature vector*, as it facilitates the modeling of the Arbiter PUF as linearly separable function. Note that the values of w and b only depend on the physics of the PUF, whereas the values of x only depend on the given challenge.

The observation that Arbiter PUFs can be modeled as hyperplanes in  $\mathbb{R}^n$  lead Gassend et al. [Gas+04] to use the Perceptron algorithm to create models of Arbiter PUF instances, as it is suitable to learn linearly separable functions.

If we assume certain properties of the Arbiter PUF manufacturing process, such as that the delays are distributed according to a Gaussian distribution [Gas+02], we can also derive statements about the distribution of the w and b in the class of all Arbiter PUFs.

**Corollary 9.** Assuming the delays  $d_i^{\text{TT}}$ ,  $d_i^{\text{TB}}$ ,  $d_i^{\text{BT}}$ ,  $d_i^{\text{BB}}$  for an Arbiter PUF are distributed according to a Gaussian with all the same mean and variance  $\sigma_{\text{Model}}^2$ , the weights w and bias b of  $\Delta D_{\text{Model}} = \langle w, x \rangle + b$  are distributed according to

$w_0 \sim \mathcal{N}\left(0, \sigma_{\text{Model}}^2\right), \quad w_i \sim \mathcal{N}\left(0, 2\sigma_{\text{Model}}^2\right), \quad b \sim \mathcal{N}\left(0, \sigma_{\text{Model}}^2\right).$

Implementation of arbiter chains in hardware produce noisy responses. To obtain valid predictions for the behavior and security of Arbiter PUFs, this noise needs to be modeled, but is not covered by the additive delay model. For any challenge  $c \in \{-1, 1\}^n$ , we thus model the *noisy* PUF delay value  $\Delta D$  as

$$\Delta D(c) = \Delta D_{\text{Model}}(c) + \Delta D_{\text{Noise}}, \qquad (3.1.1)$$

where  $\Delta D_{\text{Noise}}$  is a Gaussian random variable with zero mean and a variance  $\sigma_{\text{Noise}}^2$  depending on measurement conditions and implementation. Note that this model does not make any assumptions about the distribution or model of  $\Delta D_{\text{Model}}(c)$ . Delvaux and Verbauwhede [DV13] were the first to propose this model and proved its accuracy in a noise-based side-channel attack (Section 3.8). The accuracy of the model was later confirmed in follow-up studies [Taj+14; Bec15].

## 3.2. XOR Arbiter PUF

The successful modeling attack against the Arbiter PUF by Gassend et al. [Gas+04] using the Perceptron algorithm motivated the introduction of a new PUF design. As the Perceptron algorithm is restricted to modeling functions which are linearly separable but

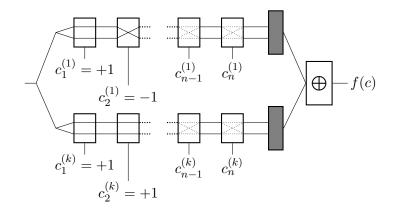

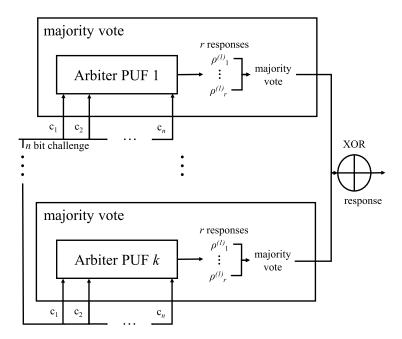

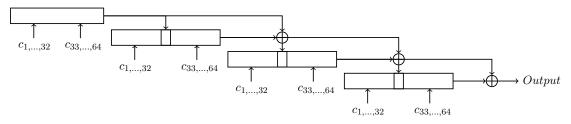

Figure 3.2.1.: Schematic representation of an 2-XOR Arbiter PUF; the scheme can be extended to include more arbiter chains. After the challenge is set up, a rising edge is input on the left-hand side, with the arbiters at the end of each chain (shown as gray rectangles) measuring if the top line or bottom line shows a signal first. During this process, the  $n \cdot k$  challenge bits decide at each stage (white rectangles) if the signal paths are crossed or not. The arbiter result bits of each line are then XORed and output on the right-hand side.

cannot model the parity function [MP69], Suh and Devadas [SD07] proposed the XOR Arbiter PUF. In the XOR Arbiter PUF, a number of k Arbiter PUFs is implemented in parallel. Any given challenge is applied to all k Arbiter PUFs, which are evaluated separately. Then, the parity of the resulting k response bits is the final 1-bit response of the XOR Arbiter PUF. The schematics of an XOR Arbiter PUF are depicted in Figure 3.2.1.

While each Arbiter PUF has linearly separable responses, the XOR Arbiter PUF does not have this property. Instead, the decision boundary cannot be modeled by an *n*dimensional hyperplane anymore. In this sense, adding XOR operations increases the *nonlinearity* of the model.

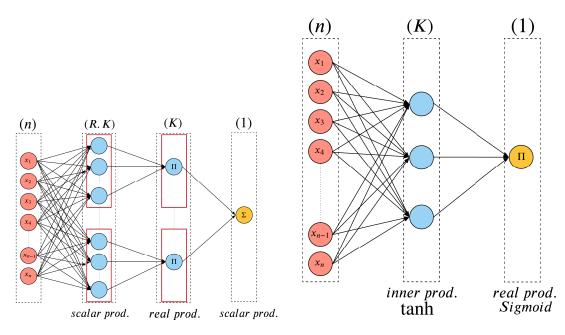

Nevertheless, the additive delay model can be extended to XOR Arbiter PUFs. Note that when using  $\{-1,1\}$  as bit values, the parity function can be written as the real product of bit values. Hence, using the noise-free variant of the model and writing  $f^{(l)}$  with  $1 \leq l \leq k$  and  $f^{(l)}(c) = \operatorname{sgn} \langle w^{(l)}, x \rangle + b^{(l)}$  for the individual Arbiter PUFs in a k-XOR Arbiter PUF modeled by f, we obtain

$$f(c) = \prod_{l=1}^{k} f^{(l)}(c) = \prod_{l=1}^{k} \operatorname{sgn} \left[ \left\langle w^{(l)}, x \right\rangle + b^{(l)} \right]$$

= sgn  $\left[ \prod_{l=1}^{k} \left( \left\langle w^{(l)}, x \right\rangle + b^{(l)} \right) \right].$  (3.2.1)

## 3.3. Metrics

The quality of the XOR Arbiter PUF can be measured by the security metrics of bias, reliability, and uniqueness as introduced in Section 2.1. The unforgeability of XOR Arbiter PUFs will be discussed after this section.

### 3.3.1. Systematic Bias of XOR Arbiter PUFs

XOR Arbiter PUF bias can be analyzed by expanding the product of the additive delay model (Equation (3.2.1)) to observe the resulting threshold term. In order to focus on the *systematic* bias of XOR Arbiter PUF designs, we assume each Arbiter PUF to be independently chosen and *unbiased*<sup>1</sup>.

The term  $\prod_{l=1}^{k} \langle w^{(l)}, x \rangle = \prod_{l=1}^{k} \sum_{i=1}^{n} w_i^{(l)} x_i$  in Equation (3.2.1) is a polynomial of degree k over variables  $x_i$  that take values in  $\{-1, 1\}$ . Hence, f(c) is a polynomial threshold function of degree at most k, including some monomials of the form  $x_i^k \cdot \prod_{l=1}^{k} w_{l,i}$ . If (and only if) k is even, these monomials contribute to the threshold term. When k is odd, no product will degenerate into a constant term, i.e. perfectly unbiased Arbiter PUFs will yield a perfectly unbiased XOR Arbiter PUF. As an example, a 2-XOR Arbiter PUF can then be modeled as

$$r(c) = r_1(c) \cdot r_2(c) = \operatorname{sgn}\left[\sum_{\substack{i,j \\ i \neq j}} w_{1,i} w_{2,j} x_i x_j + \sum_{\substack{i,j \\ i = j}} w_{1,i} w_{2,j}\right].$$

(3.3.1)

It can be seen that even assuming unbiased building blocks, we obtain a non-zero threshold term of  $\sum_{i=1}^{n} w_{1,i} w_{2,i}$ . While the expectation of this value in the manufacturing process is zero, a high variance causes the 2-XOR Arbiter PUF to likely have significant bias. In other words, any 2-XOR Arbiter PUF consisting of two *unbiased* arbiter chains is biased with probability 1.

**Theorem 10.** The responses of independently chosen unbiased Arbiter PUFs queried on the same challenge are not statistically independent.

*Proof.* Let  $r_1, r_2$  be models of unbiased Arbiter PUFs with parameters  $w_i^{(1)}$  and  $w_i^{(2)}$  for  $1 \leq i \leq n$  chosen independently at random and  $w_0^{(1)} = w_0^{(2)} = 0$  as defined in (Theorem 8). As demonstrated in Equation (3.3.1), the bias of  $r_1(c) \cdot r_2(c)$  is non-zero and hence<sup>2</sup>  $\Pr[r_1(c) \cdot r_2(c) = 1] \neq 1/2$ . However, assuming statistical independence we have

$$\Pr[r_1(c) \cdot r_2(c) = 1] = \Pr[r_1(c) = r_2(c)] = \frac{1}{2}.$$

<sup>&</sup>lt;sup>1</sup>The effect observed in this section can also be observed using Arbiter PUFs which are biased according to bias distribution as shown in Corollary 9. We chose to show the effect on unbiased Arbiter PUFs to exhibit the effect more clearly.

<sup>&</sup>lt;sup>2</sup>An approximation of  $E_c[r(c)]$  in dependence of the bias values can be obtained using the Berry-Esseen-Theorem to approximate  $\sum_{i,j} w_{1,i} w_{2,j} x_1 x_2$  for  $i \neq j$  as a Gaussian random variable with variance  $\sigma^2$  over uniformly chosen random challenges, resulting in  $E_c[r(c)] \approx \operatorname{erf}\left(\frac{\sum_{i=1}^n w_{1,i} w_{2,i}}{\sigma\sqrt{2}}\right)$ ; the value  $\sum_{i=1}^n w_{1,i} w_{2,i}$  in turn follows (in the manufacturing random process) a distribution composed of

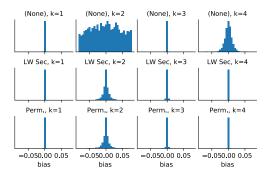

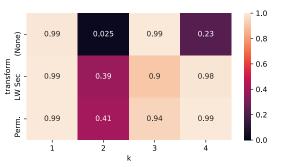

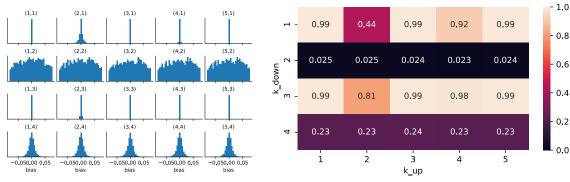

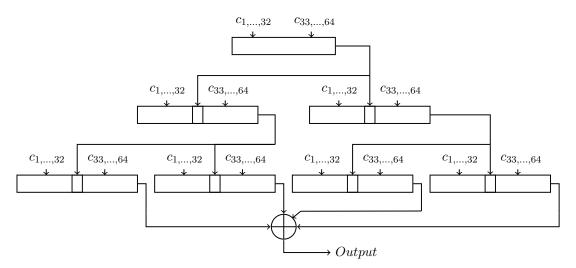

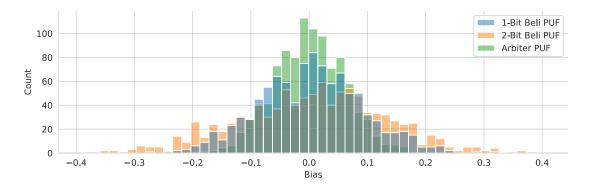

(a) Histogram of bias estimates. A bias value of zero represents perfectly unbiased responses.

(b) Proportion of instances that passed the NIST frequency test at significance level 1%.

Figure 3.3.1.: Analysis results for simulated 64-bit k-XOR Arbiter PUFs, k-Lightweight Secure PUFs (Chapter 4) and k-Permutation XOR Arbiter PUFs (Chapter 4) build from unbiased Arbiter PUFs. For each type and size, 5000 instances were sampled and queried with one million uniformly random challenges each.

Such bias may be problematic for novel designs based on a single XOR Arbiter PUF, but with transformation of the challenge (Chapter 4) as well as for designs based on several XOR Arbiter PUFs, like the Interpose PUF (Chapter 5). As an example, Theorem 10 can be extended to cover all input transformations that result in the same challenge for each arbiter chain.

We emphasize that this analytical result holds regardless of any implementation weakness and must be considered a *systematic* weakness of the XOR Arbiter PUF design.

We confirmed the systematic XOR Arbiter PUF bias in simulations (Chapter 9) for different XOR Arbiter PUF sizes and input transformations, including the Interpose PUF. All simulations are based on the additive delay model with standard Gaussian weights and were conducted using *unbiased* arbiter chains. The distribution of the systematic bias is based on sampling 100 instances each; the bias of each instance is estimated using 1,000,000 responses to uniformly random challenges.

In Figure 3.3.1 we show the estimated bias distribution for XOR Arbiter PUFs and Lightweight Secure PUFs, which confirm our theoretical findings. As expected, the systematic bias is only present for PUFs with an even number of arbiter chains, while PUFs with an odd number of arbiter chains remain (systematically) unbiased. The bias variance becomes smaller as k increases. The statistical significance of these findings can be confirmed by applying a bias test like the one specified in NIST's SP-800-22 test suite [Ruk+10]: while our simulation passes the tests on 99% of XOR Arbiter PUF instances whenever k is odd; it fails for almost all instances when k = 2, and fails for the majority

the sum of product-normal distributions, which has increasing variance for increasing n. Extending the setting, for higher (but even) k the distribution narrows as the variance of the product-normal distribution narrows. The later effect can be observed in our simulations, cf. Figure 3.3.1.

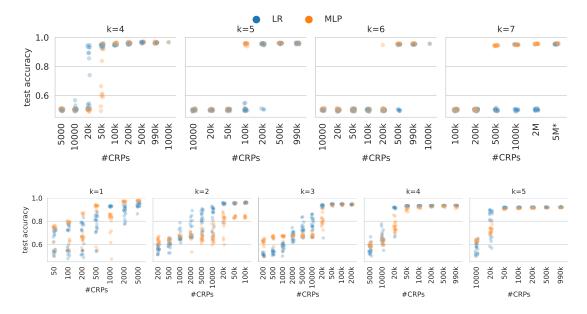

(b) Proportion of instances that passed the NIST frequency test at significance level 1%.

Figure 3.3.2.: Analysis results for simulated 64 bit  $(k_{up}, k_{down})$ -Interpose PUF instances build from unbiased Arbiter PUFs. For each size, 5000 instances were sampled and queried with one million uniformly random challenges each.

of instances when k = 4 (see Figure 3.3.1). This is also in line with our theoretical findings and simulation results, as we expect the effect to become smaller as k increases.

We hence recommend using an odd number of arbiter chains to avoid potential additional attack surface and especially discourage the use of two or four parallel chains. These recommendations also apply whenever (XOR) Arbiter PUFs are used as building blocks for larger PUFs, such as is the case in the Interpose PUF, as bias in intermediate values can result in increased predictability.

The bias distribution also suggests that the input transformation as done by the Lightweight Secure PUF [MKP08] compensates the systematic bias to some extend, which may be a contributing factor to the increased machine learning resistance [RBK10; Wis+19] of the Lightweight Secure PUF. On the other hand, the Lightweight Secure PUF and Permutation XOR Arbiter PUF (4.3) seems to introduce bias for the case k = 3. Such effects should be considered when designing novel input transformations.

Our findings also extend to the Interpose PUF [Ngu+19], which is a combination of two XOR Arbiter PUFs and was designed to be resilient against all state-of-the-art modeling attacks, while being CMOS-compatible. Consisting of two interposed XOR Arbiter PUFs, our simulation shows that the "down" XOR Arbiter PUF plays an important role for the systematic bias, while the "up" XOR Arbiter PUF only has minor influence on it (see Figure 3.3.2). We discuss the design of the Interpose PUF and applicable attacks in Chapter 5.

Given these findings, we provide additional evidence for the original author's advice to use the Interpose PUFs with an odd number of arbiter chains in the lower layer. Furthermore, as our findings are applicable any XOR Arbiter PUF, we extend the parameter recommendation to include the upper layer as well.

#### 3.3.2. Implementation

Several academic works implement the Arbiter PUF using FPGA and/or CMOS technology and studied the resulting reliability, uniqueness, bias, and bit sensitivity metrics.

Lim et al. [Lim+05] examined the uniqueness of CMOS-implemented Arbiter PUFs with respect to PUFs implemented on the same wafer and implemented on different wafers and found no significant difference. Uniqueness values in their study averaged at 40-50%, significantly below the ideal value of 100% (Definition 4). In terms of reliability, they report values between 97% and 100% for a 64-bit Arbiter PUF, depending on operating voltage and temperature. Experiments have been done with 100,000 challenge-response pairs per PUF instance and per environmental condition, with 11 repeated measurements for determination of the reliability.

Maes et al. [Mae+12] report higher uniqueness values of 95% in their CMOS implementation at only slightly decreased reliability of 96% to 100% (again, depending on the temperature). However, their study only considers a relatively small number of 8192 challenge-response pairs.

Utz, Tobisch, and Becker [UTB16] analyzed the metrics of commercially available Arbiter PUFs and found a near-ideal average uniqueness of 99.8% (with narrow variance) based on 51,200 challenge-response pairs collected from 998 PUF tokens, each. They also found a high reliability 96.3%.

The reliability of XOR Arbiter PUFs decreases exponentially with the number of arbiter chains involved. This can be demonstrated using the additive delay model on the XOR Arbiter PUF, and has also been confirmed empirically by Zhou, Parhi, and Kim [ZPK17] on a very large data basis.

The bit sensitivity of Arbiter PUFs was studied by Siddhanti et al. [Sid+19] and is far from ideal. In particular, challenge bits to stages early in the delay lines have little influence on the response, whereas stages later in the delay lines have high influence. Near-optimal influence values of challenge bits are only found around the middle of the delay lines. This has led to the development of the Lightweight Secure PUF (Chapter 4).

Given the results above, the Arbiter PUF can be considered to fulfill fundamental PUF requirements, albeit the achieved reliability can be a concern, in particular in regard with usage in large PUF designs such as the XOR Arbiter PUF.

pypuf (Chapter 9) ships data measured from the Arbiter PUF implementation of Mursi et al. [Mur+20] and Aghaie and Moradi [AM21]. To the best of our knowledge, no other Arbiter PUF data is publicly available.

## 3.4. Logistic Regression Attack

After the successful attacks on the Arbiter PUF using the Perceptron algorithm [Gas+04], it was found that the Logistic Regression algorithm (LR) can model Arbiter PUFs using fewer examples during training [Söl09; Rüh+10]. In contrast to the Perceptron, LR also does not require the data to be linearly separable and can thus be used to model the XOR Arbiter PUF, which originally was suggested to mitigate the Perceptron modeling attack [SD07]. It has been confirmed that LR is also able to create models on data

obtained from real hardware [HMV12; Rüh+13b]. It can be scaled up to very high parameters, while the time and data complexity was observed to grow exponentially [TB15]. An open-source version of the LR attack, implemented in a modern machine learning framework, is available in pypuf (Chapter 9). In addition to differences caused by the new implementation, it also features some detail improvements [Wis+21a], on which we detail below.

For the purpose of the Logistic Regression Attack, we use the noise-free k-XOR Arbiter PUF model as stated in Equation (3.2.1),

$$f(c) = \operatorname{sgn} \prod_{l=1}^{k} \left( \left\langle w^{(l)}, x \right\rangle + b^{(l)} \right),$$

where  $c \in \{-1, 1\}^n$  is the challenge and x the corresponding feature vector.

We assume that the attacker is given the size of the k-XOR Arbiter PUF. The value of n is known as the challenge-interface of the PUF is assumed to be public. Further, the attacker is given N examples of the PUF's challenge-response behavior as training set,  $T = ((c_1, r_1), \ldots)$ , where  $c_i \in \{-1, 1\}^n$ ,  $r_i \in \{-1, 1\}$ . This corresponds to the known message attack definition of Section 2.1.

The supervised learning process starts with a randomly initialized model, i.e. with  $n \cdot k$  values drawn from a Gaussian distribution. We define the model function m as

$$\widehat{m}\left(w^{(1)},\ldots,w^{(k)},c\right) = \prod_{l=1}^{k} \left(\left\langle w^{(l)},x\right\rangle + b^{(l)}\right);$$

$$m\left(w^{(1)},\ldots,w^{(k)},c\right) = \operatorname{sgn}\widehat{m}\left(w^{(1)},\ldots,w^{(k)},c\right).$$

Note that the model explicitly depends on the weights  $w^{(l)}$  for  $1 \le l \le k$ .

The attacker is now faced with the task of finding weights  $w^{(l)}$  such that the resulting model m models the examples in T as accurately as possible. For any given observed challenge c and response r, we define the *likelihood* that the model  $\hat{m}$  predicts the observed behavior correct to be

$$\frac{1}{1 + \exp\left(-r\widehat{m}\left(w^{(1)}, \dots, w^{(k)}, c\right)\right)}$$

While  $r \in \{-1,1\}$ , the model value  $\hat{m}$  can take values in  $\mathbb{R}$ . Whenever we have  $r = \operatorname{sgn} \hat{m} (w^{(1)}, \ldots, w^{(k)}, c)$ , the likelihood is above 1/2 and rapidly approaches 1 with increasing absolute value of  $\hat{m}$ . Likewise, whenever  $r \neq \operatorname{sgn} \hat{m} (w^{(1)}, \ldots, w^{(k)}, c)$ , the likelihood is below 1/2 and rapidly approaches 0 with increasing absolute value of  $\hat{m}$ .

To obtain a value that measures the overall correctness of the model across the training set, we define the *total likelihood* as the product all individual likelihoods, i.e.,

$$\prod_{(c,r)\in T} \frac{1}{1 + \exp\left(-r\widehat{m}\left(w^{(1)}, \dots, w^{(k)}, c\right)\right)}$$

This is motivated by the fact that each correctly predicted response will contribute for this value to converge towards 1, whereas each incorrectly predicted value will contribute for this value to converge towards zero.

The task of finding weights  $w^{(l)}$  that define a well-predicting model can now be reduced to the task of findings weights  $w^{(l)}$  that increase the total likelihood as defined above.

In logistic regression, the weights  $w^{(l)}$  are determined in an iterative manner by conducting a gradient ascent. For the gradient ascent, the derivative of the function to be optimized must be computed, which is difficult due to the large product term. This problem can be circumvented by considering the *log likelihood* instead. By applying the logarithm function, computing the derivative becomes easier, while the maxima of the function remain unchanged due to the monotonicity of the logarithm.

To summarize, the likelihood that the model predicts correctly is maximized when the log-likelihood

$$L\left(w^{(1)}, \dots, w^{(k)}\right) = \ln \prod_{(c,r)\in E} \frac{1}{1 + \exp\left(-r\widehat{m}\left(w^{(1)}, \dots, w^{(k)}, c\right)\right)}$$

$$= \sum_{(c,r)\in E} \ln \frac{1}{1 + \exp\left(-r\widehat{m}\left(w^{(1)}, \dots, w^{(k)}, c\right)\right)}$$

is maximized.

To find such a maximum, the gradient ascent algorithm starts at a random point and then "walks" on the surface defined by the log likelihood function towards the direction of steepest ascent. The stride length of such a step is determined by heuristic algorithms. The direction of the steps is computed using the gradient defined by

grad

$$L\left(w^{(1)},\ldots,w^{(k)}\right) = \left(\frac{\partial L}{\partial w_1^{(1)}},\ldots,\frac{\partial L}{\partial w_n^{(k)}}\right)'$$

where

$$\frac{\partial L}{\partial w_{\nu}^{(\mu)}} = \sum_{(c,r)\in T} \left( \frac{r \cdot \left( \prod_{j\in\{1,\dots,k\}\setminus\{l\}} \left\langle w^{(l)}, x \right\rangle \right) \cdot x_{\nu}^{(\mu)}}{1 + \exp\left( -r \cdot \widehat{m}\left( w^{(1)},\dots,w^{(k)}, c \right) \right)} \right).$$

To summarize, the task of finding weights  $w^{(l)}$  that provide high-accuracy predictions for the given training set T can be reduced to iteratively computing the gradient of the log likelihood function and heuristically adjusting the weights into the direction of the steepest ascent. The process can be terminated when certain (heuristic) criteria are met, e.g. when the stride length becomes small or when the accuracy computed on either the training set or a separate validation set becomes high.

There exists several implementations of the LR algorithm for attacking Arbiter PUFs and XOR Arbiter PUFs. To our knowledge the first implementation was provided by Rührmair et al. [Rüh+10] and is implemented using Python and numpy. In this work, we present an implementation using the Keras machine learning framework.

The LR attack has become an important tool for the security analysis of delay-based PUFs and is used in a large number of different works, including in the recent proposal of the Interpose PUF [Ngu+19] and an attack on it [Wis+20b]. The Keras implementation of the LR attack in this work will serve as a baseline for comparing the performance of LR with various other attacks.

A large-scale study of Tobisch and Becker [TB15] determined training set sizes for the LR attack that yield optimal results, i.e., have the lowest training times, and minimal training set sizes, for which the attack was observed to work at least once, which we confirmed and will use for comparison. To provide for a fair comparison with the neural network attacks shown in Section 3.6, we are using our Keras-based implementation of the LR attack. Differences in run time hence may not only be caused by the usage of different CPUs, but also by optimization differences in the implementations. Nevertheless, we obtain the same number of required CRPs, which indicates that our implementation behaves similar to the one of Tobisch and Becker.

To increase the training performance of the original LR algorithm, we modified some details. First, to reduce the number of epochs required for training, we introduced the usage of mini batches, where the network is updated with the gradient not only after evaluating the complete training data, but several times in each epoch. This allows for convergence using fewer epochs, and thus (except in corner cases), for shorter training time, but one must be careful to not choose the batch size too small. Too small batch sizes can lead to noisy gradient values, which will in turn perform unhelpful updates on the network.

Second, we use Adam optimizer [KB17] instead of the originally used resilient backpropagation, as the latter works poorly together with the use of mini batches.

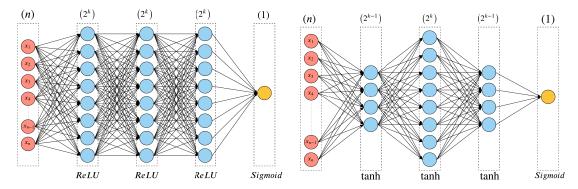

Third, we apply the tanh activation function to each of the k delay values computed by the respective arbiter chains, i.e. we change the model function<sup>3</sup> from

$$c\mapsto \tanh\left(\prod_{l=1}^k\left(\langle W_l,x\rangle+b_l\right)\right)\qquad\text{to}\qquad c\mapsto \tanh\left(\prod_{l=1}^k\tanh\left(\langle W_l,x\rangle+b_l\right)\right).$$

This change was motivated by the observation that in the traditional LR network, a single arbiter chain can have large influence on the absolute value of the final output. However, in the electrical circuit, no analogon to the absolute value exists. Instead, XOR Arbiter PUF model weights can be scaled using positive scalars without affecting the computed function. We speculate that different influences can hamper the training process, as weight updates during backpropagation may be applied predominantly to influential arbiter chains. Applying the tanh function ensures a more equalized influence of all arbiter chains on the final output.

By the introduction of the additional tanh activation function, our attack does not

$$\frac{1}{1+e^{-x}} = \frac{1}{2} + \frac{1}{2} \tanh \frac{x}{2}.$$

<sup>&</sup>lt;sup>3</sup>Note that tanh is implicitly used in the likelihood function above, as

| n  | k  | CRPs          | success<br>rate | duration<br>(max. threads) | mean success<br>accuracy | memory          | [TB15]        |

|----|----|---------------|-----------------|----------------------------|--------------------------|-----------------|---------------|

| 64 | 4  | 30k           | 10/10           | $<1 \min @ 4$              | 95.5%                    |                 | $<1 \min$     |

| 64 | 5  | 260k          | 10/10           | $4 \min @ 4$               | 96.9%                    |                 | $<\!\!1 \min$ |

| 64 | 6  | 2M            | 20/20           | ${<}1$ min @ $4$           | 97.6%                    |                 | $1 \min$      |

| 64 | 7  | 20M           | 10/10           | $3 \min @ 4$               | 98.5%                    |                 | $55 \min$     |

| 64 | 8  | 150M          | 10/10           | $28~\mathrm{min}~@~4$      | 96.4%                    |                 | $391 \min$    |

| 64 | 9  | 500M          | 7/10            | $14~\mathrm{min}~@~40$     | 96.8%                    | $132~{\rm GiB}$ | *2266 min     |

| 64 | 10 | $1\mathrm{B}$ | 6/10            | $41~\mathrm{min}~@~40$     | 95.7%                    | $197~{\rm GiB}$ | -             |

Table 3.1.: Empirical results on learning simulated XOR Arbiter PUFs obtained using our Keras-based implementation of the LR attack. Reference values of Tobisch and Becker [TB15] use up to 16 cores. (\* Result obtained using a different number of CRPs.)

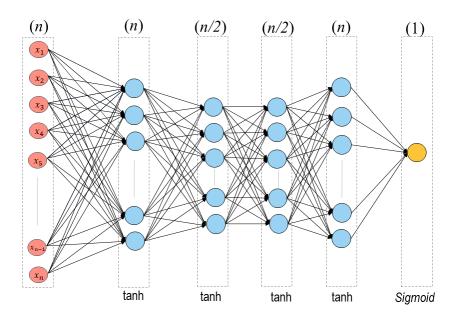

fulfill the definition of logistic regression anymore<sup>4</sup>. In a slight abuse of terminology, we will refer to this version as the *improved LR attack*. A sketch of the network structure used in the attack is displayed in Figure 3.6.4d.

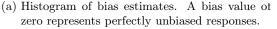

Using our Keras-based implementation together with these improvements, we could increase the performance of the LR algorithm (with respect to wall clock time, i.e., elapsed real-time from beginning to end of the model training procedure), which is summarized in Table 3.1. We found that the largest proportion of the performance gain is due to Keras, which allows for optimized and highly parallel computing, and to a smaller extent due to our improvements. In a comparison of attack performance on 64-bit 5-XOR Arbiter PUFs, we found that our implementation of the original LR attack achieved a success rate of 16/20, while the improved version yielded 18/20 successful, with all other parameters being equal. We did not study in more detail the performance of the two versions depending on the choice of mini batch size, number of CRPs, learning rate, etc.

Similar to the attacks based on neural networks shown in Section 3.6, performance of the improved LR attack crucially depends on the choice of hyperparameters, in particular on a good combination of learning rate and batch size. The number of required epochs is also heavily influenced by any early stopping logic, which may depend on the validation accuracy or loss. We thus expect that the wall-clock performance and the number of required epochs can be further reduced, e.g., by using a systematic approach to find optimal hyperparameters. On the other hand, we expect that for the LR attack, the data complexity cannot significantly be reduced by hyperparameter tuning.

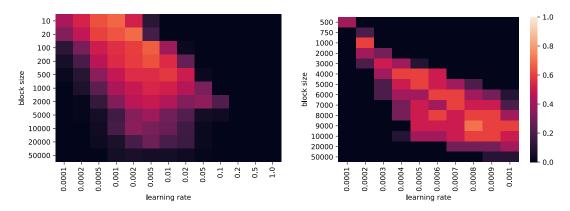

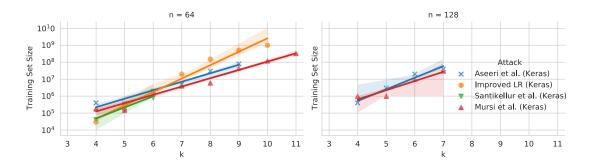

Our numbers confirm once more [Rüh+10; Wis+20b] that the LR attack requires a number of CRPs in the training set that grows exponentially with the number of employed XORs in the target XOR Arbiter PUF. In Fig 3.6.3, we show the required training set size. Based on a fitted function  $k \mapsto \alpha \cdot e^k$  using the least squares method, we predict

<sup>&</sup>lt;sup>4</sup>One can argue that already the LR attack on XOR Arbiter PUF hardly fits the textbook definition of a logistic regression.

the number of required CRPs for k = 10 is 1.3 billion, for k = 11 is 3.6 billion, and for k = 12 is  $10^{12}$ .

The performance of the LR algorithm in the literature [RBK10; Rüh+13b; TB15] and our results show that Arbiter PUF and XOR Arbiter PUF cannot be considered EUF-KMA secure, unless the number of XORs k can be scaled significantly (Section 3.7).

## 3.5. Physical Attacks

For the security analysis of PUFs, as discussed in Section 2.2, the capabilities of attackers with physical access to the PUF must be considered.

To that end, Tajik et al. [Taj+14] analyzed an *n*-bit XOR Arbiter PUF implemented on a Complex Programmable Logic Device (CPLD) and analyzed the photonic emission during operation of the PUF, which is caused by the switching of n-type transistors belonging to the Arbiter PUF stages (realized as multiplexers) in the circuit. The observed measurements allowed the recovery of the delay differences of the Arbiter PUF. After observing the PUF responses for *n* linearly independent challenges, a system of linear equations can be used to recover all internal delays, effectively providing a model to predict the response to any challenge.

In a different attack, Tajik et al. [Taj+15] used a laser to inject a fault into an XOR Arbiter PUF, which lead to the deactivation of parts of the XOR Arbiter PUF and effectively degenerated it into a number of Arbiter PUFs that can be attacked separately using, e.g., the LR attack (Section 3.4). In this attacker model, the advantages provided by the XOR Arbiter PUF over the Arbiter PUF are removed.

Ganji et al. [Gan+15] use a similar approach, but do not require to inject a fault. By using a lattice basis reduction, they can use the information of *how many* Arbiter PUFs return a certain bit value in an XOR Arbiter PUF to reduce the complexity of the modeling attack. This information can be obtained using the photonic emission techniques also used by Tajik et al. [Taj+14].

These attacks demonstrate that the hope that the Arbiter PUF would be temperevident, i.e. change it's behavior when attacked physically, cannot be fulfilled.

To mitigate the attacks to a certain extend, Sahoo et al. [Sah+16] suggested a fault-tolerant implementation of the Arbiter PUF.

Hardware attacks on Arbiter PUFs and XOR Arbiter PUFs are, to some extend, also applicable to PUF designs based on XOR Arbiter PUFs such as the ones discussed in this work.

## 3.6. Neural Network Attacks

This section studies how machine learning modeling attacks that are not restricted to a certain class of model functions can be used to model XOR Arbiter PUFs. This is in contrast to the modeling attack using logistic regression shown in Section 3.4, which is based on the physically motivated model function of the XOR Arbiter PUF (Equation (3.2.1)).

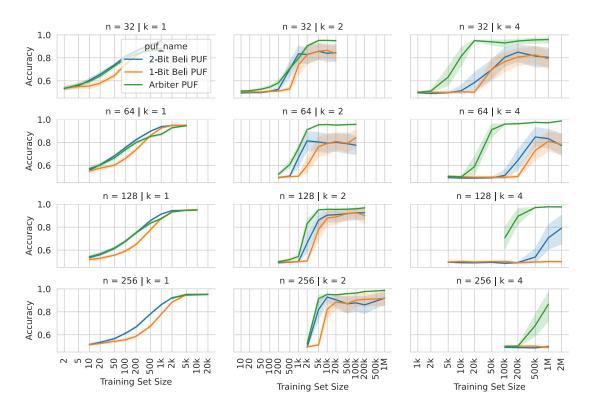

We revisit three neural-network attacks from the literature, replicate and discuss their results. Finally, in Section 3.6.3, we present the best-performing KMA modeling attack to XOR Arbiter PUFs.

The machine learning attacks in this section are all implemented using the Keras framework to provide a fair comparison of their properties and to compare the results to the improved logistic regression attack of Section 3.4. As the attacks run, compared to previous works [Rüh+10; TB15; Wis+19; Wis+20b], relatively fast, we focus our attention on the comparison of the data complexity, i.e., how much training data is required to obtain good modeling predictions.

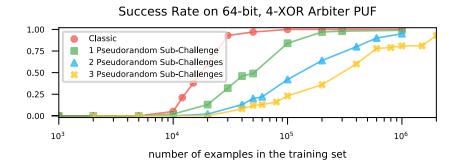

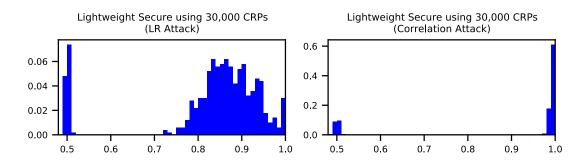

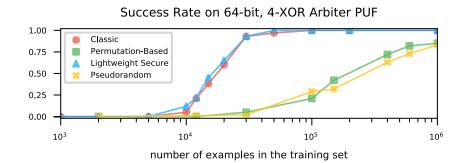

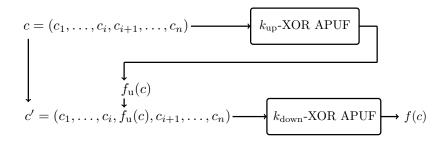

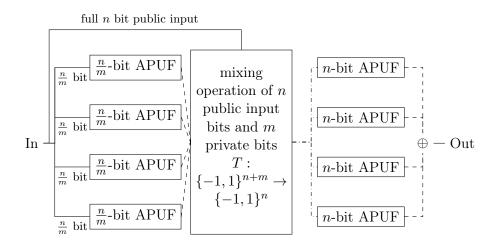

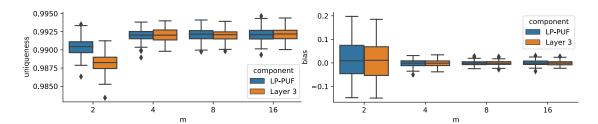

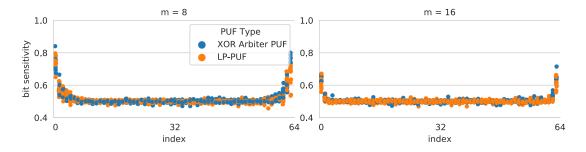

In this work, we do not focus on the exact accuracy metrics of prediction quality for several reasons. First, the attacks that we study do not yield intermediate results when correctly parameterized, i.e., the attacks end either with accuracy 50% or close to 100%. Additionally, we observed that high-accuracy results can be further improved by letting the training continue for a couple more epochs. Second, to impersonate a PUF token, no extremely high accuracy is needed, and any prediction accuracy significantly better than 50% should be considered a security weakness of the PUF design [Del19]. Hence, instead of prediction accuracy, we focus on the attack *success rate*, i.e., the proportion of independently run attacks on independent PUF simulations that yielded prediction accuracy greater than 90%. Given that virtually all successful attacks yielded accuracy 95% or better and virtually all unsuccessful attacks yielded accuracy 55% or below, the success rate is very insensitive to the exact choice of this threshold. Nevertheless, for the sake of completeness, the prediction accuracy of obtained models is given as the average over several attacks on different PUF tokens.

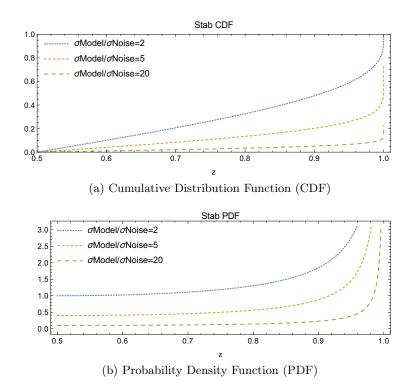

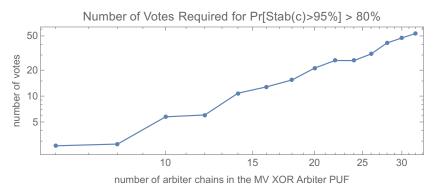

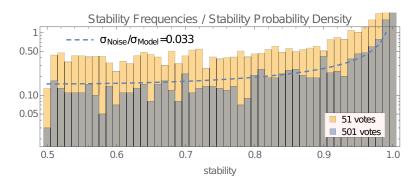

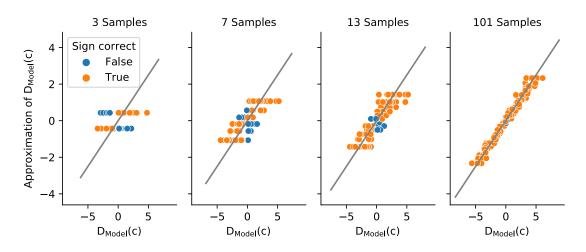

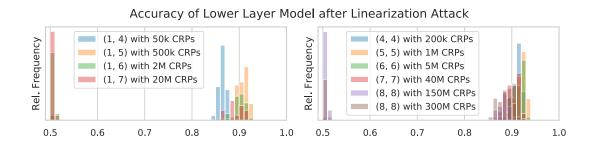

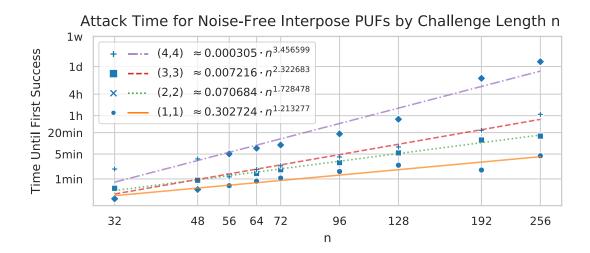

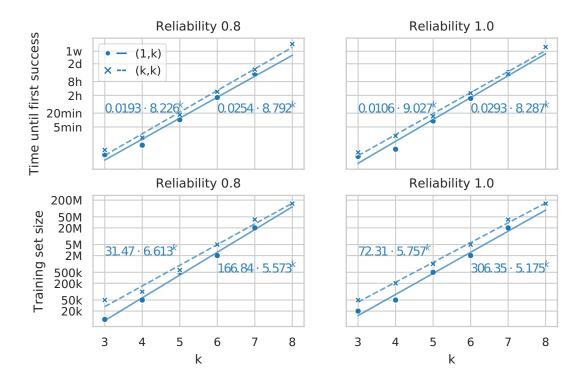

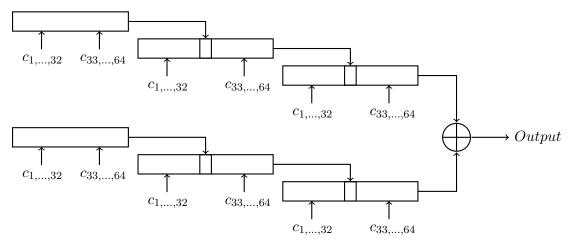

To ensure that all of our results are reproducible in detail, we seed all involved pseudorandom number generators used for generating PUF token simulations, initializations of machine learning models, etc. with defined values.