# Interdigitated Back Contact Silicon Heterojunction Solar Cells

From the Laboratory to Industrial Processes

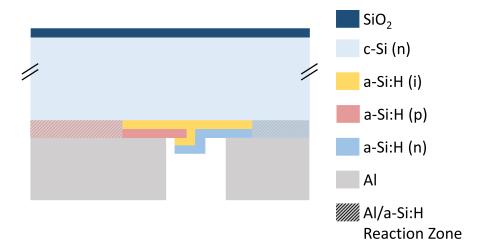

vorgelegt von M.Sc. Johann-Christoph Stang geboren in Berlin

von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften – Dr.-Ing. –

genehmigte Dissertation

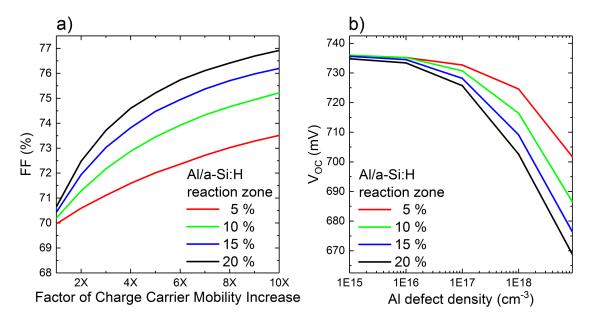

#### Promotionsausschuss:

Vorsitzender: Prof. Dr. Bernd Szyszka Gutachter: Prof. Dr. Bernd Rech

Prof. Dr. Stefan Glunz

Prof. Dr. Isidro Martín García

Tag der wissenschaftlichen Aussprache: 03.07.2018

#### Abstract

This work follows two routes: the first one explores the efficiency potential of IBC SHJ solar cells built with a rather complex process, the second one shows ways to make this efficiency potential actually industrially accessible by developing an appropriate, simplified manufacturing process.

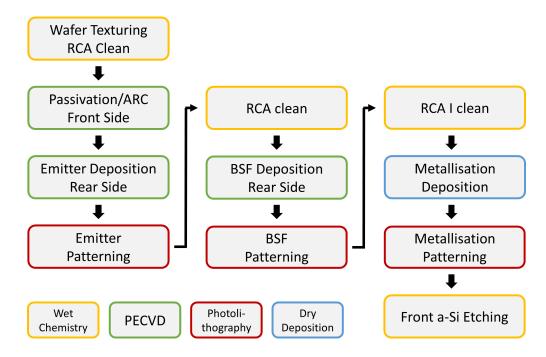

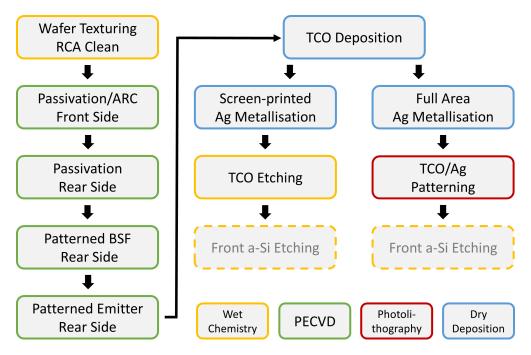

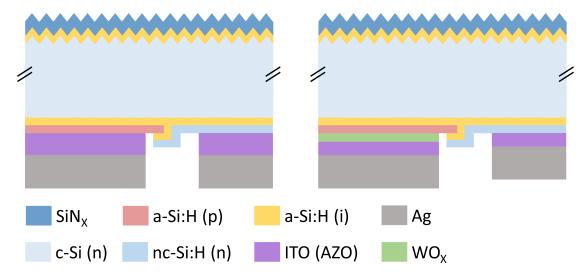

In chapter 4, both manufacturing processes are discussed. In the first part, the established photolithography process is extensively described, emphasising its complexity, and subtle but crucial optimisations to the process are introduced: improved photoresist adhesion, evaporation-based metallisation increasing the reliability of the ITO etch process and, most importantly, the non-destructive protective layer etching.

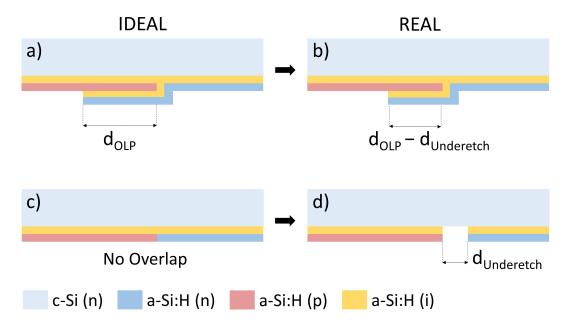

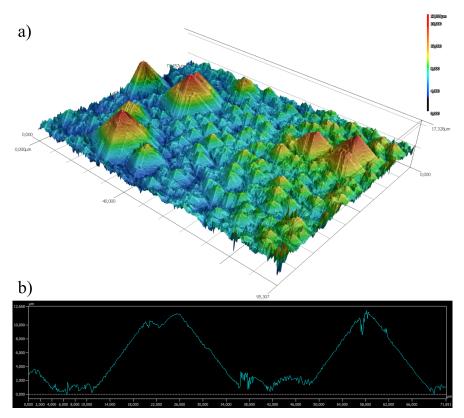

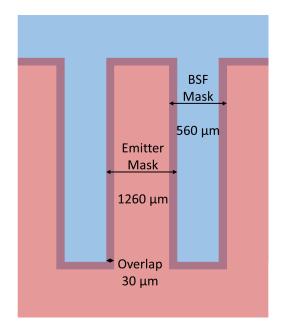

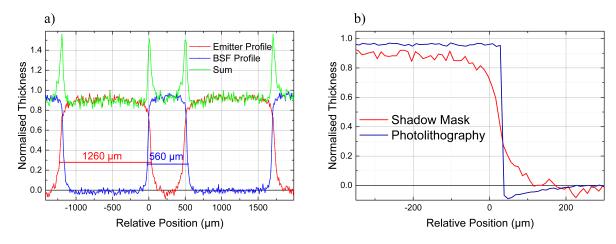

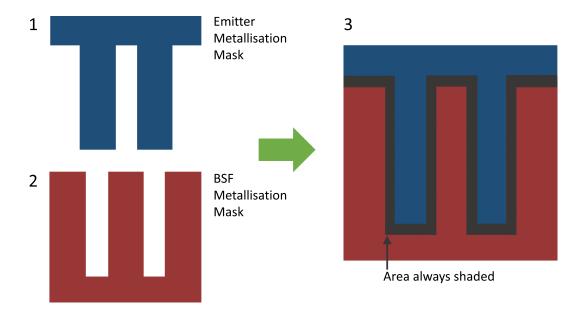

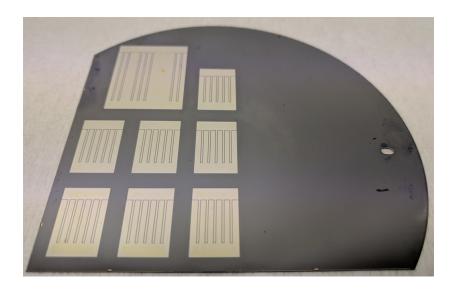

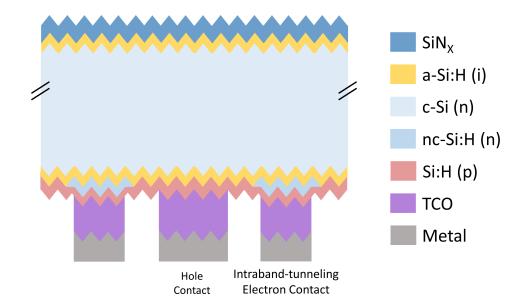

The second part of chapter 4 describes the development of an industrially viable manufacturing process based on structured silicon wafers serving as shadow masks to pattern a-Si:H and nc-Si:H in-situ during the PECVD deposition process. Challenges arising from the laser-ablation based mask manufacturing, the accuracy and fidelity of the patterned layers, and the alignment system are analysed and discussed: tapering effects caused by the surface diffusion of SiH<sub>3</sub> radicals under the masks were found to limit the fidelity of the patterned layers, making adjustments to the cell design with respect to the contact finger widths and metallisation gaps necessary. Furthermore, an alignment system based on laser-drilling holes, matching with the metal pins on a custom-made aluminium carrier, into the respective wafers was developed.

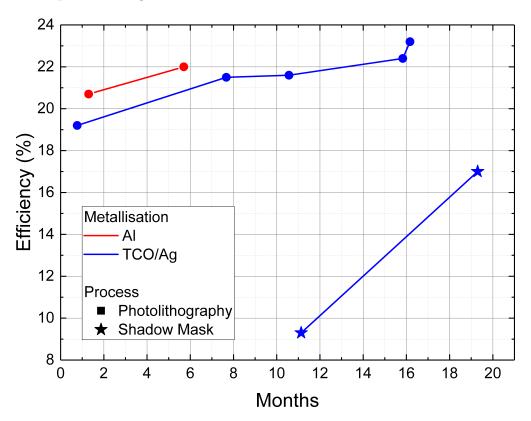

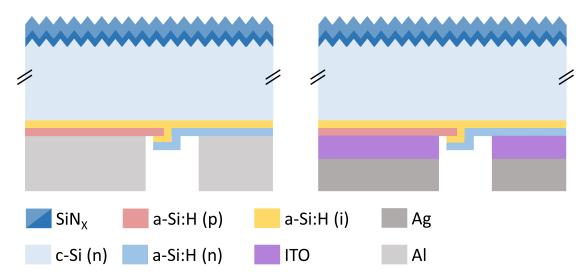

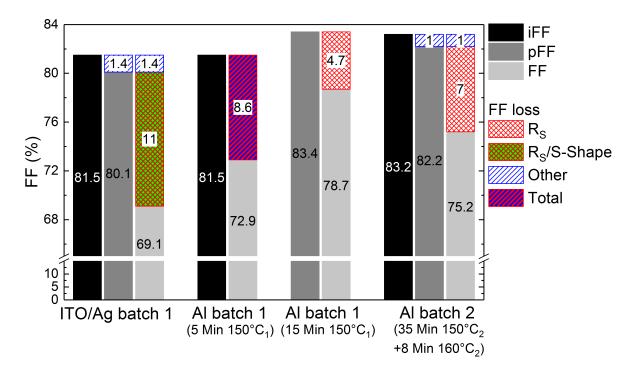

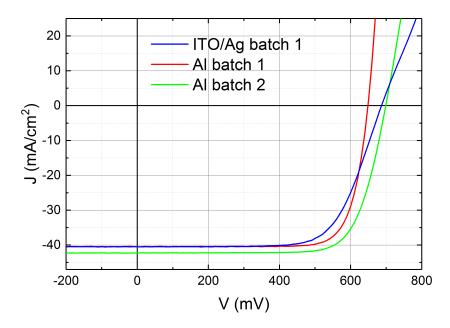

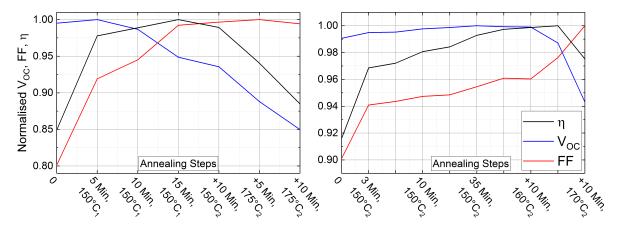

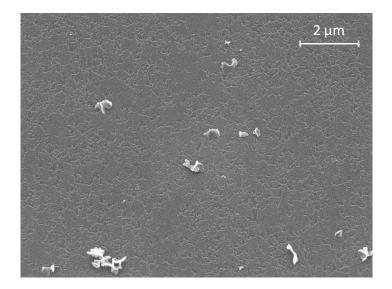

The results of the various IBC-SHJ solar cells built during this work are presented and analysed in chapter 5. Photolithography-based cells with a direct, annealed aluminium metallisation achieve considerably better results than equivalent cells with an ITO/Ag metallisation (efficiency of 20.7 vs. 19.2%). With an improved front side passivation the aluminium-based cells reach efficiencies up 22%. The properties of the Al/a-Si:H contact system strongly depend on the annealing time and temperature. Moderate annealing likely leads to the formation of an intermediate aluminium silicide and initialises the crystallisation of the doped a-Si:H layers, which results in the reduction of the contact resistivity and thus in an increase of the FF. Extended annealing leads to strong interdiffusion between the aluminium and amorphous silicon layers eventually resulting in the disintegration of the latter and thus the deterioration of the passivation quality. In these cases, the consequential  $V_{\rm OC}$  losses cannot be compensated by the increase of the FF.

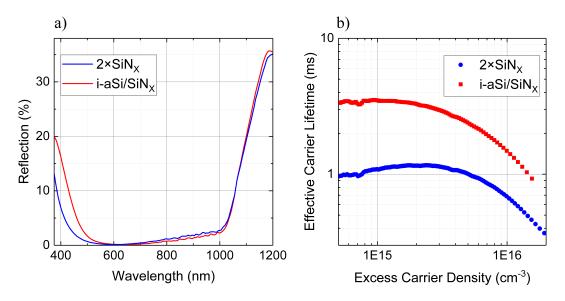

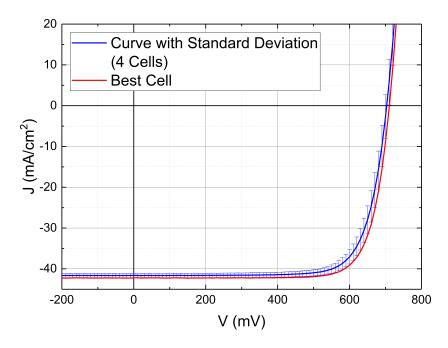

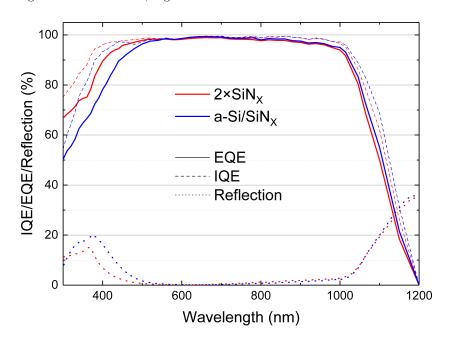

The second part of chapter 5 focuses on the development of photolithography-based solar cells with TCO contacts. Owing to a different front-side layer stack, prioritising passivating over optical properties, as well as optimised a-Si:H deposition processes and film thicknesses, the efficiency of ITO-based IBC SHJ solar cells was increased by

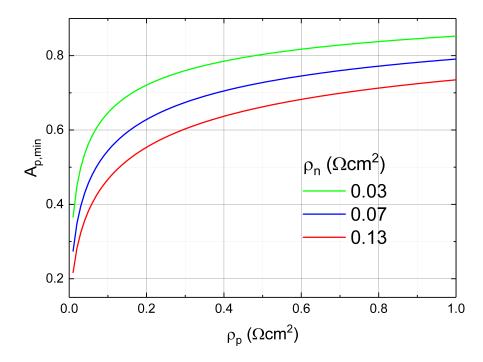

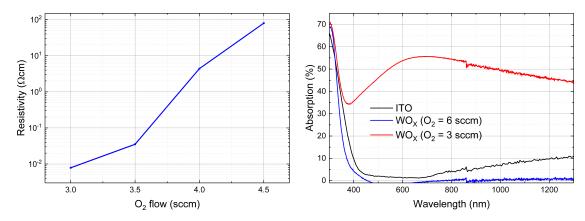

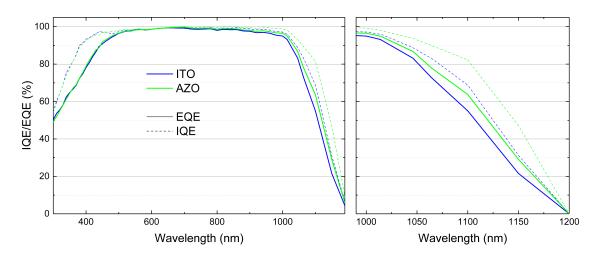

4%abs, from 19.2 to 23.2%. Calculations of the implied FF and Suns- $V_{\rm OC}$  measurements indicate that the solar cells are mainly limited by high series resistances leading to FF values well below 80%. Based on TLM measurements, the contact resistivities, in particular the one of the p-contact stack, were identified to be the main series resistance contributor. Thinning the intrinsic a-Si:H passivation layers and switching to a textured rear side led to substantial improvements of both the contact resistivities and the FF. Additionally, AZO was investigated as an alternative TCO material replacing ITO. The latter was found to form a better contact to the p-type a-Si:H layers, likely related to its higher work function, while the former yielded a better optical response resulting in a higher  $j_{\rm SC}$ . Moreover, initial results of IBC SHJ solar cells with a WO<sub>X</sub> interlayer between the p-type a-Si:H emitter and the TCO (ITO in this case) show slightly lowered p-contact resistivities, indicating the potential of high work function metal oxides as emitter contact materials.

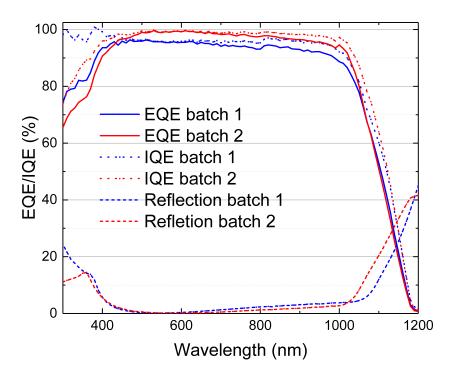

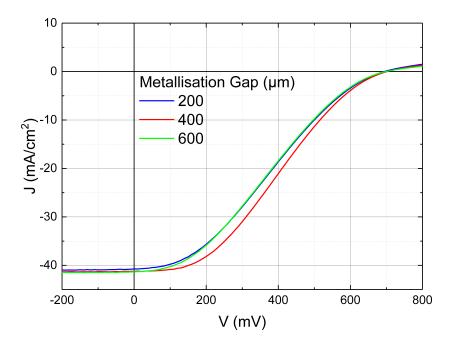

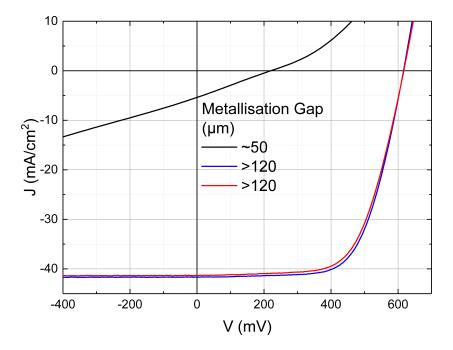

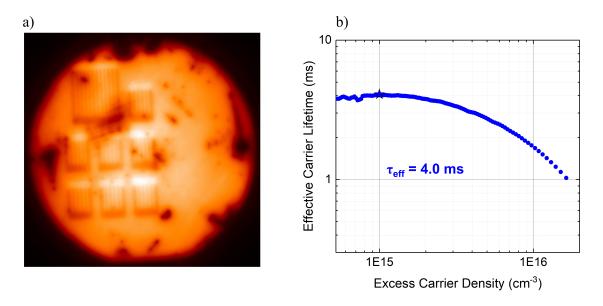

In the last part of the chapter the very first results of IBC SHJ solar cells manufactured with the shadow mask process are presented. Cells with a screen-printed metallisation on an AZO layer reach decent  $V_{\rm OC}$  and  $j_{\rm SC}$  values (41 mA/cm², 700 mV). However, the efficiency does not exceed 10%, as the corresponding jV curves are strongly S-shaped and the jV-derived FF is limited to values around 30%. The latter is most likely related to a malfunctioning emitter/TCO contact or a too thick intrinsic a-Si:H passivation layer. A second batch of solar cells built with a further developed shadow mask process – optimised alignment system, a-Si:H processes identical to the ones used for the best photolithography-based solar cells and a more accurately patterned ITO/Ag metallisation – yielded solar cells with efficiencies up to 17, and FF values up to 66%.  $V_{\rm OC}$  values are particularly low (616 mV), as the emitter passivation degrades during the metallisation.

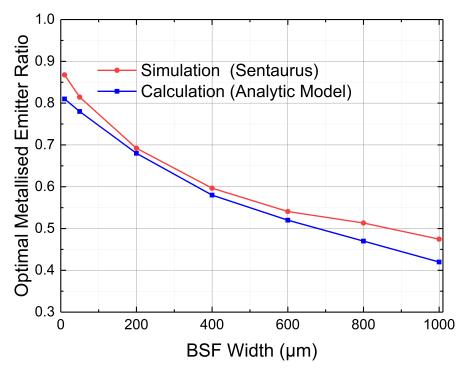

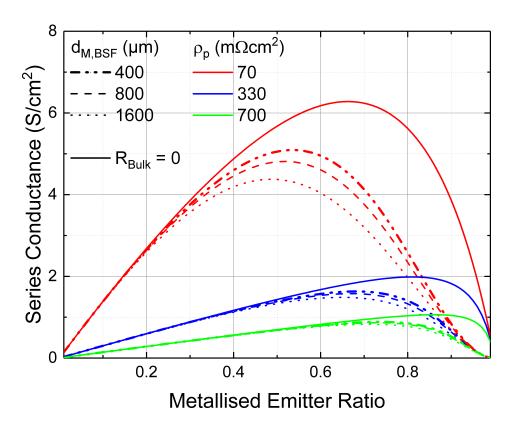

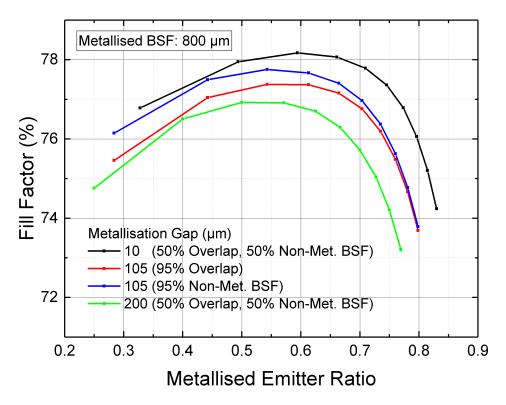

Chapter 6 discusses the prospects of IBC SHJ solar cells with respect to industrial fabrication and marketability. With respect to high-efficiency concepts aiming for cell efficiencies above 25 %, top- and rear-contacted SHJ solar cells are identified to likely be the main competitor for IBC SHJ solar cells. The latter can only succeed if simple manufacturing processes are employed. Based on the state of IBC SHJ research, shadow-mask based processes show the most potential, as the complexity of the manufacturing process does not substantially differ from standard SHJ processes and cell efficiencies close to 24 % have been demonstrated. The implications of a shadow mask process on the contact geometry of IBC SHJ solar cells (larger contact finger widths and metallisation gaps) are also analysed with a simulation study. The results indicate only minor efficiency losses due to process related contact geometry adjustments.

## Zusammenfassung

Einseitig kontaktierte Silizium-Heterostruktursolarzellen (IBC-SHJ) haben das Potential höchste Wirkungsgrade zu erreichen. Diese Arbeit beschäftigt sich mit den Herstellungsprozessen sowie der Optimierung des Kontaktdesigns derartiger Solarzellen. Der Fokus lag hierbei einerseits auf der Weiterentwicklung und Verbesserung des etablierten Photolithographieprozesses sowie andererseits auf der Entwicklung eines alternativen, industriekompatiblen Herstellungsverfahrens, basierend auf der Strukturierung amorpher und nanokristalliner Siliziumschichten in situ mittels geeigneter Schattenmasken während der jeweiligen PECVD-Prozesse (Schattenmaskenprozess).

Die im vierten Kapitel beschriebenen Verbesserungen des Photolithographieprozesses umfassen die Lackhaftung, die Reproduzierbarkeit des ITO-Ätzschrittes und das Vermeiden der Degradation der frontseitigen Antireflexschicht während des Ätzens der darauf befindlichen a-Si-Schutzschicht. Der zweite Teil des vierten Kapitels befasst sich mit der Entwicklung des Schattenmaskenprozesses. Durch Laserstrukturierung wurden hierfür geeignete Masken aus Siliziumwafern hergestellt sowie zwei Alignierverfahren entworfen und hinsichtlich ihrer Genaugikeit und Praktikabilität analysiert. Die Strukturtreue der durch die Masken abgeschiedenen a-Si-Schichten wurde mittels Raman-Profilmessungen analysiert. PECVD-Prozesse, in denen die Schichtdeposition durch die Diffusion der SiH<sub>3</sub>-Radikale hin zur Oberfläche limitiert ist, zeigten diesbezüglich bessere Ergebnisse als Prozesse, in denen SiH<sub>3</sub>-Radikale vermehrt auf der Oberfläche unter die Maske diffundieren können.

Die Eigenschaften der für diese Arbeit hergestellten IBC-SHJ Solarzellen werden im fünften Kapitel vorgestellt. Dabei lag der Fokus im Speziellen auf der Optimierung der Rückkontaktstrukturen der mit dem Photolithographieprozess hergestellten Solarzellen. Solarzellen mit direkten, getemperten Al/a-Si:H-Kontakten erreichten höhere Wirkungsgerade als entsprechende Referenzzellen mit konventionellen ITO/Ag-Kontakten (19,2 zu 20,7%). Durch eine verbesserte Frontseitenpassivierung konnte die Effizienz der aluminiumbasierten Solarzellen auf bis zu 22 % erhöht werden. Die Eigenschaften des Al/a-Si:H-Kontaktes hängen maßgeblich von der Temperatur und Zeitdauer des Temperschrittes ab. Moderates Tempern (T = 150 bis 160 °C, 20 bis 30 Minuten) führt zur Bildung eines Aluminiumsilizides sowie einer partiellen Kristallisation des amorphen Ausgangsmaterials. Beide Effekte verringern den Kontaktwiderstand zwischen der Aluminiummetallisierung und den dotierten a-Si:H-Schichten, wodurch der Füllfaktor steigt. Wird die Temperatur des Temperschrittes weiter erhöht, kommt es verstärkt zu Diffusionsprozessen zwischen den Aluminium- sowie den amorphem Siliziumschichten und in der Folge zu einer teilweisen Auflösung letzterer. Der daraus resultierende Verlust der Oberflächenpassivierung und die folgliche Reduktion der Leerlaufspannung können

in der Regel nicht durch einen weiteren Anstieg des Füllfaktors ausgeglichen werden, sodass die Effizienz der Solarzelle wieder sinkt.

Der zweite Teil des fünften Kapitels beschreibt den Optimierungsprozess von IBC-SHJ-Solarzellen mit TCO-basierten Kontakten. Durch das Einfügen einer amorphen Siliziumschicht wurden die Passivierungseigenschaften des frontseitigen Schichtstapels substantiell verbessert. Des Weiteren wurden die PECVD-Prozesse und die Schichtdicken der rückseitigen a-Si:H-Schichten optimiert. Folglich konnte die Effizienz von Solarzellen mit ITO/Ag-Kontakten um 4 %abs, von 19,2 auf 23,2 % erhöht werden. Mittels einer Füllfaktoranalyse – Vergleich von implizitem und Pseudo-Füllfaktor – wurde der Serienwiderstand als dominanter Verlustmechanismus identifiziert. TLM-Messungen zeigen, dass hohe Serienwiderstände zu einem großen Teil auf einen entsprechend hohen Kontaktwiderstand des p-Kontaktes zurückzuführen sind. Ein Reduktion des letzteren konnte durch eine Verringerung der Schichtdicke der intrinsischen a-Si:H-Passivierschicht erreicht werden, eine Reduktion des gesamten Serienwiderstandes durch den Einsatz einer texturierten anstelle einer planaren Rückseitenoberfläche. Zudem wurde aluminiumdotiertes Zinkoxid (AZO) als alternatives TCO-Material untersucht. Im Vergleich zu ITO weist AZO eine höhere Transparenz im nahen Infrarotbereich auf, wodurch die parasitäre Absorption an der Zellrückseite vermindert wird. Dieser Vorteil wird jedoch durch einen hohen Kontaktwiderstand zum p-dotierten a-Si:H-Emitter kontrastiert. Letzteres führt zu einer Reduktion des Füllfaktors. Des Weiteren wurde Wolframoxid als Emitter-exklusives Kontaktmaterial untersucht. Erste Solarzellen mit einer dünnen Wolframoxidschicht zwischen dem p-dotiertem a-Si:H-Emitter und der TCO-Schicht (ITO) erreichten Effizienzen auf dem Niveau der entsprechenden Referenzzellen (Standardkontakt ITO/Ag), und wiesen darüber hinaus tendenziell niedrigere p-Kontaktwiderstände auf.

Im letzten Teil des fünften Kapitels werden die initialen Ergebnisse von mittels Schattenmaskenprozess hergestellten IBC-SHJ-Solarzellen diskutiert. Zellen mit einer Siebdruckmetallisierung und einem AZO-Schicht als TCO erreichen Leerlaufspannungen von 700 mV und Kurzschlusstromdichten von über  $40\,\mathrm{mA/cm^2}$ . Die Effzienz ist mit  $10\,\%$  jedoch sehr niedrig, da der Füllfaktor lediglich Werte von etwa  $30\,\%$  erreicht – als Folge von stark S-förmigen UI-Kennlinien, potentiell verursacht durch einen unzureichenden Emitter/TCO-Tunnelkontakt oder eine zu dicke intrinsische a-Si:H-Passivierschicht. Mit einem verbesserten Aligniersystem sowie den für die photolithographiebasierten Solarzellen optimierten PECVD-Prozessen konnte die Effizienz auf  $17\,\%$  erhöht werden, die Füllfaktorenwerte gar verdoppelt ( $66\,\%$ ). Die Effizienz dieser Zellen ist maßgeblich durch die niedrige Leerlaufspannung ( $616\,\mathrm{mV}$ ) limitiert, als Folge der Degradation der Emitter-Passivierung während des Metallisierungsprozesses.

Im sechsten Kapitel werden Methoden der industriellen Fertigung von IBC-SHJ-Solarzellen sowie ihre daraus potentiell resultierende Marktfähigkeit diskutiert. Um in der Klasse der Solarzellentechnologien mit einem Effizienzpotential größer als 25 % vor allem gegen beidseitig kontaktierte SHJ-Solarzellen bestehen zu können, müssen drastisch vereinfachte Herstellungsverfahren für IBC-SHJ-Solarzellen entwickeln werden. Diesbezüglich zeigen Verfahren basierend auf Schattenmasken, den aktuellen Forschungsstand betrachtend, das größte Potential, sowohl was die Prozesskomplexität als auch bereits erreichte Effizienzen (bis zu 24 %) betrifft. Mittels einer Simulationsstudie wird des Weiteren gezeigt, dass die für die Applikation eines Schattenmaskenprozesses notwendigen Anpassungen der Kontaktgeometrie (insbesondere breitere Kontaktfinger und Metallisierungsabstände) zu lediglich marginalen Effizienzverlusten führen.

# Contents

| 1         | Intr | oducti  | ion                                     | 1  |

|-----------|------|---------|-----------------------------------------|----|

| <b>2</b>  | Fun  | damen   | ntals                                   | 7  |

|           | 2.1  | Mater   | ials and Interfaces                     | 7  |

|           |      | 2.1.1   | Crystalline Silicon                     | 7  |

|           |      | 2.1.2   | Amorphous Silicon                       | 0  |

|           |      | 2.1.3   | Heterojunction Interfaces               | 11 |

|           |      | 2.1.4   | Contact Materials                       | 11 |

| 2.2 Solar |      |         | Cells                                   | 13 |

|           |      | 2.2.1   | Basic structure                         | 3  |

|           |      | 2.2.2   | Heterojunction Solar Cells              | 4  |

|           |      | 2.2.3   | Interdigitated Back Contact Solar Cells | 5  |

|           |      | 2.2.4   | Basic Parameters and Equivalent Circuit | 6  |

| 3         | Fab  | ricatio | n, Characterisation and Simulation      | 21 |

|           | 3.1  |         | •                                       | 21 |

|           |      | 3.1.1   | Deposition                              | 21 |

|           |      | 3.1.2   | Patterning                              | 22 |

|           | 3.2  | Chara   |                                         | 24 |

|           |      | 3.2.1   | jV measurements                         | 24 |

|           |      | 3.2.2   | TrPCD                                   | 25 |

|           |      | 3.2.3   |                                         | 26 |

|           |      | 3.2.4   | Suns- $V_{\rm OC}$                      | 27 |

|           |      | 3.2.5   | Transfer Length Method                  | 27 |

|           |      | 3.2.6   | Series Resistance Calculation           | 29 |

|           |      | 3.2.7   | Quantum Efficiency                      | 30 |

|           |      | 3.2.8   | •                                       | 31 |

|           |      | 3.2.9   |                                         | 32 |

|           | 9 9  | Cimula  |                                         | า  |

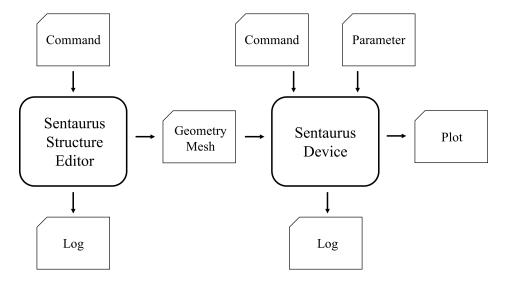

|   |     | 3.3.1   | Sentaurus TCAD                               | 33  |

|---|-----|---------|----------------------------------------------|-----|

|   |     | 3.3.2   | Definition of Device Geometry and Parameters | 35  |

|   |     | 3.3.3   | Device Simulation                            | 37  |

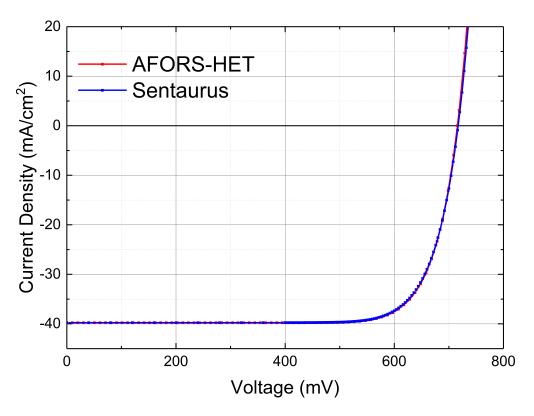

|   |     | 3.3.4   | Validation with AFORS-HET                    | 38  |

| 4 | Pro | cess D  | Development for IBC SHJ Solar Cells          | 41  |

|   | 4.1 | Metho   | ods and Tools                                | 42  |

|   |     | 4.1.1   | PECVD                                        | 42  |

|   |     | 4.1.2   | Deposition of Contact Materials              | 43  |

|   |     | 4.1.3   | Laser Ablation                               | 44  |

|   | 4.2 | Photo   | dithography Process                          | 45  |

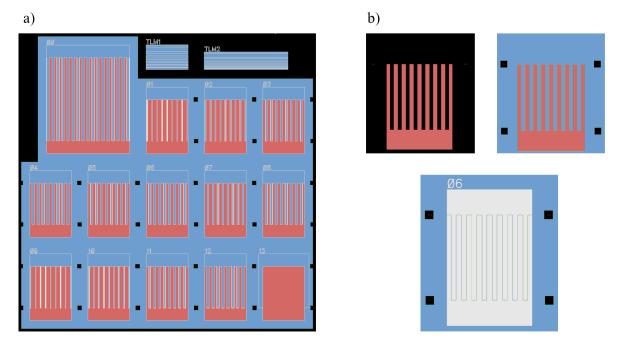

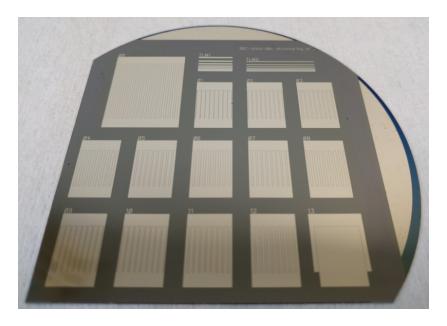

|   |     | 4.2.1   | Cell Layout                                  | 48  |

|   |     | 4.2.2   | Wafer Preparation                            | 49  |

|   |     | 4.2.3   | Layer Deposition and Patterning              | 52  |

|   |     | 4.2.4   | Final Steps                                  | 62  |

|   | 4.3 | Shado   | w Mask Process                               | 62  |

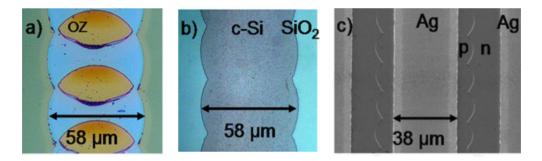

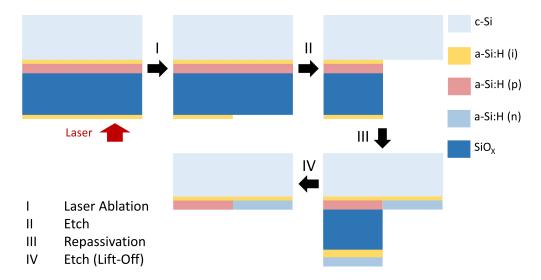

|   |     | 4.3.1   | Laser Ablation of Silicon                    | 65  |

|   |     | 4.3.2   | Mask Layout                                  | 66  |

|   |     | 4.3.3   | Thin Film Analysis                           | 67  |

|   |     | 4.3.4   | Alignment Procedures                         | 71  |

|   |     | 4.3.5   | Contact Formation                            | 76  |

|   |     | 4.3.6   | Final Steps                                  | 80  |

|   | 4.4 | Chapt   | ter Summary                                  | 81  |

| 5 | Dev | vice Op | ptimisation and Analysis                     | 85  |

|   | 5.1 | Introd  | luction                                      | 85  |

|   | 5.2 | Chara   | acterisation Approach                        | 87  |

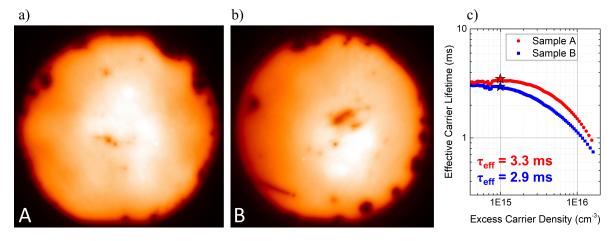

|   |     | 5.2.1   | Absence of Statistical Deviations            | 88  |

|   |     | 5.2.2   | Analysis of the Contact Resistivity          | 89  |

|   |     | 5.2.3   | S-Shapes                                     | 92  |

|   | 5.3 | Cells   | with Direct Aluminium/a-Si:H Contacts        | 94  |

|   |     | 5.3.1   | Illuminated Current-Voltage Measurements     | 95  |

|   |     | 5.3.2   | Aluminium-interacted Silicon Surfaces        | 100 |

|   |     | 5.3.3   | Simulation of Annealed Al/a-Si:H Contacts    | 104 |

|   |     | 5.3.4   | Conclusions                                  | 106 |

|   | 5.4 | Cells   | with TCO/Metal Contacts                      | 107 |

|   |     | 5.4.1   | Variation of TCO Materials                   | 108 |

|   |     | 5.4.2   | a-Si:H Passivated Front Side                 | 110 |

|                                      |                             | 5.4.3  | Emitter/BSF Variation                       |   | 112          |  |

|--------------------------------------|-----------------------------|--------|---------------------------------------------|---|--------------|--|

|                                      |                             | 5.4.4  | Illuminated Current–Voltage Measurements    |   | 113          |  |

|                                      |                             | 5.4.5  | Solar Cells with a Textured Rear Side       |   | 116          |  |

|                                      |                             | 5.4.6  | Optimising Intrinsic a-Si:H Layer Thickness |   | 118          |  |

|                                      |                             | 5.4.7  | Conclusions                                 |   | 119          |  |

| 5.5 Non-Photolithography Solar Cells |                             |        |                                             |   | 120          |  |

|                                      |                             | 5.5.1  | Conclusions                                 |   | 123          |  |

|                                      | 5.6                         | Chapte | er Summary                                  | • | 124          |  |

| 6                                    | Pro                         | spects | of IBC SHJ Solar Cells                      | 1 | 127          |  |

|                                      | 6.1                         | From 1 | Laboratory to Industrial Production         |   | 129          |  |

|                                      |                             | 6.1.1  | In-situ Masking                             |   | 130          |  |

|                                      |                             | 6.1.2  | Laser Ablation                              |   | 132          |  |

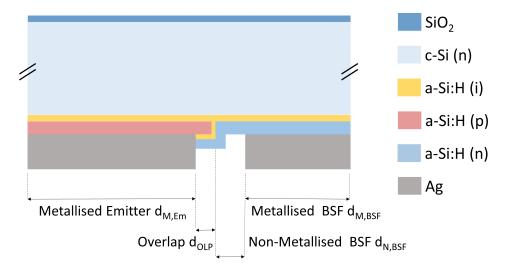

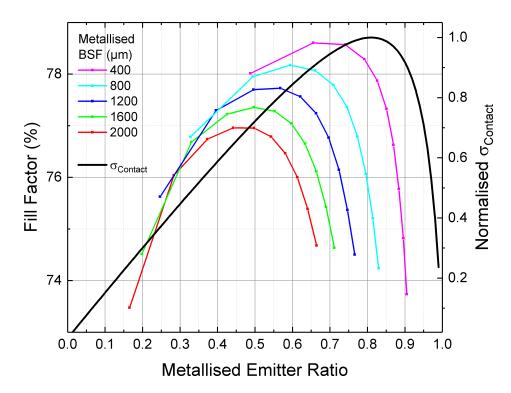

|                                      | 6.2                         | Implic | ations on the Contact Geometry              |   | 135          |  |

|                                      |                             | 6.2.1  | Fill Factor Limitations                     |   | 137          |  |

|                                      | 6.3                         | Conclu | asions                                      |   | 142          |  |

| 7                                    | Con                         | clusio | ns and Outlook                              | 1 | L <b>4</b> 5 |  |

| Aı                                   | ppen                        | dices  |                                             | 1 | 161          |  |

| $\mathbf{A}$                         | A Abbreviations and Symbols |        |                                             |   |              |  |

| В                                    | 3 Simulation Parameters     |        |                                             |   |              |  |

| $\mathbf{C}$                         | C Publications              |        |                                             |   | L69          |  |

| D                                    | D Acknowledgements          |        |                                             |   |              |  |

# Chapter 1

# Introduction

The exploitation of earth's fossil resources in the last two centuries allowed the countries in the Western hemisphere to experience an enormous economical and industrial growth [1]. In the 21<sup>st</sup> century the emerging economies of Asia and Africa are set to follow the same route, with population numbers exceeding the Western example by far. Thus, despite dwindling fossil resources, mankind's increasing demand for energy is not expected to stabilise anytime soon [2]. The fossil fuel based industrialisation has also led to alarming levels of air pollution, destruction of nature, political tensions and to a rapid increase of Earth's average temperature [3–6].

Photovoltaic (PV) technologies are one of the main alternatives to fossil energy, as they use a reliable source of energy, the sun's irradiation, without negatively impacting the environment by  $CO_2$  and other emissions.

Since the first solar cells were built in the 1950s [7], the cumulative installed solar power has steadily increased, with silicon solar cells being the major contributor [8]. At the end of 2016, 320 GWp of PV capacity were installed worldwide, with an increase of roughly 77 GWp compared to 2015, from which 93% relied on solar cells based on crystalline silicon [9].

The semiconductor silicon is a well-understood material, owing to its longtime use in various industries, in particular the transistor and microchip industry, its abundance and its non-toxicity. The power conversion efficiency of silicon-based solar cells has seen consistent improvements throughout the last decades, culminating in Kaneka corporation's recent achievement of a solar cell with an efficiency of 26.7% [10]. This result is very close to the practical limit of 29.4% as calculated for a silicon-based single-junction solar cell [11,12]. The theoretical maximum for such a device amounts to 32%, known as the Shockley-Queisser limit [13].

While in general, silicon solar cells are comparatively simple devices, achieving an efficiency of 20% and higher requires advanced technologies. These technologies

mainly revolve around increasing light absorption, by introducing textured surfaces and anti-reflection coatings [14,15], suppressing the recombination of photogenerated charge carriers, by improving passivation and eliminating material defects [16], and improving charge carrier transport properties, by choosing more conductive materials.

The classic concept for a silicon-based solar cell, featuring a diffused junction (homojunction), inherently lacks passivation. With the addition of dedicated passivation layers between the highly doped emitter and BSF regions in the silicon material and the metallisation, an increase in open circuit voltage ( $V_{\rm OC}$ ) of up to 725 mV is possible [17–19], still falling roughly 35 mV short of the theoretical maximum for silicon [20]. The highest efficiency with diffused junctions was published by the Fraunhofer Institute for Solar Energy Systems in 2017, achieving 25.7% [19]. This also marks the highest efficiency for a two-side contacted silicon-based solar cell.

The heterojunction concept, pioneered by Sanyo in the early 1990s, represents an alternative to the aforementioned homojunction concept [21]. The emitter layer, responsible for collecting the photogenerated minority carriers, is formed by adding a layer of hydrogenated amorphous silicon (a-Si:H) on-top of the crystalline silicon wafer, with the former being doped contrary to the latter. If an intrinsic, hydrogenated amorphous silicon buffer layer between the crystalline wafer and the amorphous emitter is used, outstanding passivation quality and thus  $V_{\rm OC}$  values up to 750 mV are feasible [22].

In order to maximise the light absorption of a solar cell, any losses at the side facing the sun (the cell's front side) should be avoided. In two-side contacted solar cells, the front metal grid inflicts optical losses, as it usually consists of non-transparent materials shadowing part of the front side and thus preventing a significant portion of the incoming light from passing through to the crystalline silicon absorber. These losses are further exacerbated by the underlying emitter, which accounts for further losses due to recombination: in a diffused junction charge carriers created by high-energetic photons are more likely to recombine in the highly doped emitter regions [23]; in a heterojunction the charge carriers generated in the defect-rich a-Si:H emitter rather recombine than contribute to the external current [24].

Both these effects can be avoided, if a back contact (BC) architecture is considered. With both contacts moved to the rear side of the device, the front side can be fully optimised considering only optical and passivating properties, increasing the photogenerated current, usually expressed as the short circuit current density  $j_{SC}$ .

For a long time the company Sunpower has been the most prominent advocate for the BC architecture, commercialising back contacted solar cells with passivated contacts, and achieving cell efficiencies of up to 25% [25,26]. The heterojunction concept and the back contact approach were first combined by Lu in 2007 [27], and since 2014, with

Panasonic achieving an efficiency of 25.6% [28], the connection of these two technologies has held the world record for the most efficient single-junction silicon based solar cell. Panasonic's result was surpassed by the aforementioned Japanese company Kaneka in early 2017, by achieving 26.3% at first and only months later exceeding their own record with 26.6 then 26.7% [10,29,30].

The drawback of any back-contacted architecture is the increase in manufacturing complexity. Having both contacts on the same side of the device necessitates methods to structure the corresponding contact regions. In case of a homojunction approach this means to locally diffuse the p and n<sup>+</sup> regions into the wafer material, while for the heterojunction concept, the additional doped layers need to be structured either after or during their deposition, without harming their properties or those of affected surfaces. Furthermore, practical considerations about the contact geometry must be made. This includes determining the rear side area fraction allocated to one or the other contact, and the area fraction sacrificed for gaps, necessary to separate the contacts. Processing and contact design are not two problems to be solved independently, but are closely interconnected. Oftentimes the structuring method of choice limits the minimum or maximum feature size of certain aspects of the rear side geometry.

#### This Thesis

The work presented in the following illustrates a solar cell optimisation process through the example of silicon wafer based back-contacted heterojunction (BC SHJ) solar cells. The overall aim is to increase the cell efficiency by optimising the back contact geometry of these cells with respect to their passivation quality, contact resistivity, the consequential total series resistance and their optical properties. In addition to that an industrially viable manufacturing process is proposed and analysed with respect to its inherent limitations.

Chapter 2 describes the basic properties of the used materials and the principles of solar cell operation.

In Chapter 3 the technological background with regards to structuring and deposition techniques, the different characterisation methods and the simulation software Sentaurus is introduced and validated. Moreover, the two-dimensional model of an BC SHJ solar cell is outlined. The model serves as a basis for the simulation of BC SHJ solar cells with direct aluminium/a-Si:H contacts and for a simulation study exploring the impact of the rear side contact geometry.

Chapter 4 describes the manufacturing processes of BC SHJ solar cells. At first, the established photolithography process is explained as well as the improvements

introduced during the course of this work. Additionally the development of an alternative, industrially viable process based on shadow masks is outlined.

In Chapter 5 the results of solar cells featuring different contact materials and manufacturing processes are presented and analysed. This incorporates photolithography based BC SHJ solar cells with direct aluminium/a-Si:H contacts or contacts based on transparent conductive oxides (TCO) as well as solar cells built with the shadow mask process.

Chapter 6 discusses the prospects of BC SHJ solar cells, by comparing the technology to other high-efficiency solar cell concepts with respect to potential mass production and marketability. Existing industrially viable approaches to manufacture BC SHJ solar cells are briefly outlined, additionally the impact of wider contact geometries, inherent to these industry-compatible processes, are evaluated by simulation.

The key results of this work can be summarised as follows:

- Annealed direct aluminium/a-Si:H represent a simple and effective option for high-efficiency BC SHJ solar cells, as they exhibit low contact resistivities and thus high fill factor (FF) values. Annealing times and temperatures are critical as extended annealing leads to strong interdiffusion of aluminium and amorphous silicon resulting in the disintegration of the amorphous silicon layers and the destruction of the passivation. With moderate annealing the passivation remains unharmed while the contact resistivity improves drastically, likely owing to the formation of a thin aluminium silicide layer.

- The efficiency of BC SHJ solar cells with indium tin oxide (ITO) contacts was improved by 4%abs (from 19.2 to 23.2%), by optimising the photolithography process, implementing a new front side layer stack and using optimised rear side a-Si:H layers. Additionally alternative TCO materials were evaluated: particularly transparent aluminium-doped zinc oxide (AZO) reduces the parasitic absorption at the rear side and thus increases the  $j_{SC}$  of the respective solar cells, but on the expense of the FF; the FF and the contact resistivity of initial solar cells with a tungsten oxide interlayer between the a-Si:H emitter and the ITO layer are on a par or slightly better than the ones of conventional ITO based solar cells, but parasitic absorption in the WO<sub>X</sub> layer reduces the  $j_{SC}$ . Using textured instead of polished rear sides enhances the optical response of the rear side and improves the solar cell's  $j_{SC}$ . It also increases the effective cell area, leading to a moderate increase of the FF.

• Initial solar cells built with the shadow mask process achieve efficiency values up to 17%, illustrating the general viability of the process. PECVD deposited a-Si:H layers patterned in-situ with shadow masks exhibit tapering and underdeposition effects impairing the fidelity of the patterned layers. The extent of these effects depends on the properties of the respective a-Si:H deposition process. If the latter is limited by the diffusion of SiH<sub>3</sub> radicals to the substrate's surface, the fidelity of the deposited layers is high. As a consequence of the tapering effects, solar cells built with the shadow mask process have to feature wider BSF and emitter widths as well as metallisation gaps. The impact of the wider contact geometry is evaluated with a simulation study: despite the larger contact geometry corresponding losses are small compared to the losses related to the p-contact resistivity.

# Chapter 2

# **Fundamentals**

In this chapter the properties of the relevant materials and the operating principle of solar cells in general are described.

## 2.1 Materials and Interfaces

#### 2.1.1 Crystalline Silicon

In this section, the properties of crystalline silicon are briefly explained, as it represents the core material of the solar cells discussed in this work. For a more in-depth discourse, the reader is referred to [31] and [32].

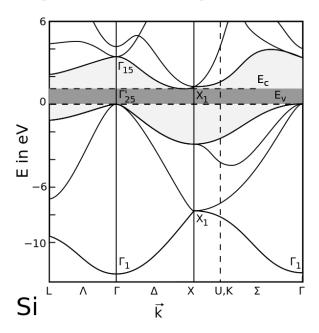

The positive nucleus of a silicon atom is surrounded by its 14 electrons, each occupying a distinct energy level. The silicon atoms are arranged in a diamond type cubic crystal structure that is repeated alongside the entire silicon bulk (crystalline silicon, c-Si). Since the positive nuclei of the atoms are no longer isolated, but positioned in a periodic lattice, the energy levels of the corresponding electrons overlap and form quasi-continuous energy bands. In silicon, such as in every other inorganic semiconductor, an energy gap exists between the highest occupied energy band - valence band  $\mathrm{E}_\mathrm{V}$  - and the lowest unoccupied energy band - conduction band  $E_{\rm C}$ . In silicon, this band qap  $E_{\rm G}$ amounts to a value of 1.12 eV, being the minimum energy that has to be transferred to an electron in the valence band to be excited to the conduction band. A photon therefore can be absorbed by a silicon crystal, if its energy is larger than the aforementioned band gap. However, since silicon is an indirect semiconductor, meaning in the momentum space, or k-space (see Figure 2.1), its valence band maximum and conduction band minimum are not at the same position, an additional amount of momentum is needed to absorb a photon with the minimal energy of 1.12 eV at room temperature (a direct transfer would be possible at an energy of 3.4 eV). This necessary momentum transfer

reduces the probability of absorption and thus lowers silicon's absorption coefficient. As a consequence, comparatively thick layers of crystalline silicon (in the range of 100 to 300 µm) are needed to provide sufficient absorption for solar cell applications.

Figure 2.1: Silicon band structure in k-space, reworked by [33], after [34].

The absorbed photon creates a Wannier-Mott exciton, a weakly bound electron-hole pair. With binding energies in the order of 0.01 eV [35], the exciton is effectively immediately split up, creating an unbound electron in the conduction band and an equivalent hole in the valence band, both able to contribute to charge transfer. Collecting and transferring these photogenerated, free charge carriers to an external circuit is the purpose of a solar cell device.

#### Doping

In a silicon crystal, each silicon atom forms four covalent bonds. It is possible to replace a certain amount of silicon atoms with foreign atoms, whose outer shell contains either less (acceptor material) or more (donor material) electrons. If an element with five outer shell electrons is brought into the silicon crystal lattice, all four silicon bonds will be saturated, leaving one of the donor's bonds open. If the energy level of the donor's outer shell electrons is close to silicon's conduction band, the donor atom is usually ionised at room temperature, releasing its excess electron into the conduction band of the silicon crystal, where it is available for charge transport. This process is called n-doping. Typical elements for n-doping are phosphorus and arsenic.

The reverse process, p-doping, involves an element with three outer shell electrons, whose energy level is close to valence band of silicon. The acceptor atom attracts an

electron from the valence band of silicon, leaving a hole behind. Typical p-doping materials are boron and aluminium.

Doping concentrations are usually in the order of  $10^{15}$  to  $10^{16}$  atoms per cm<sup>3</sup>, with silicon's intrinsic electron and hole densities each being  $10^{10}$  cm<sup>-3</sup> at room temperature. In doped semiconductors one then differentiates between majority and minority charge carriers.

#### Recombination

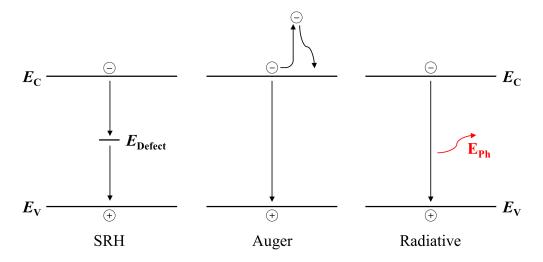

If the silicon crystal is not contacted by an external circuit, meaning that the extraction of the photogenerated charge carriers is not possible, they will eventually recombine. In silicon, three main types of recombination can be identified (see Figure 2.2):

**Shockley-Read-Hall** (SRH) recombination describes the recombination across a defect energetically positioned in the band gap. In the bulk, these defects are caused by impurities or crystal dislocations. At the surface of the silicon crystal, open silicon bonds act as very effective mid-gap recombination centres. The transferred energy is then transformed into lattice vibrations [36, 37].

Auger recombination describes a recombination process that involves three charge carriers: an electron in the conduction band might transfer its energy to another conduction band electron and then recombine with a hole in the valence band. The energy receiving electron is excited to higher energetic position within the conduction band, from which it thermalises back to the conduction band edge. Its energy is lost as heat.

Radiative recombination describes the inverse process to absorption. An electron in the conduction band recombines with a hole in the valence band and emits a photon with an energy corresponding to the band gap of the semiconductor (1.12 eV for silicon). Due to silicon being an indirect semiconductor, radiative recombination is usually not the dominating recombination process.

At low injection levels, meaning that the equilibrium majority charge carriers outnumber the light generated excess carriers, SRH recombination dominates. At high injection, where the excess carriers outnumber the equilibrium majority charge carriers, Auger recombination is predominant.

Each recombination method is attributed with a corresponding recombination rate expressed by an inverse time constant  $\frac{1}{\tau_i}$ . The reciprocal sum of all recombination time

constants constitutes the inverse of the effective lifetime  $\tau_{eff}$ , an important parameter to quantify the passivation quality:

$$\frac{1}{\tau_{\text{eff}}} = \frac{1}{\tau_{\text{rad}}} + \frac{1}{\tau_{\text{Auger}}} + \frac{1}{\tau_{\text{SRH}}} + \frac{1}{\tau_{\text{Surface}}}.$$

(2.1)

Figure 2.2: Modes of recombination in silicon.

#### 2.1.2 Amorphous Silicon

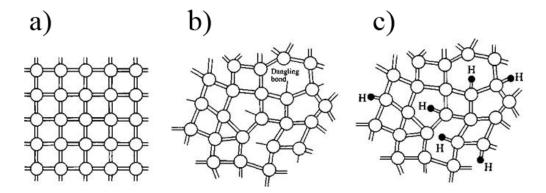

In amorphous silicon (a-Si), the silicon atoms are not bound in a well-ordered crystal lattice, but arranged in sp<sup>3</sup>-hybrid orbitals with the corresponding close range order. In the absence of a long range order, a large number of nanosized voids and unsaturated silicon, so-called dangling bonds lead to a high defect density in the material bulk (see Figure 2.3) [38, 39]. These defects can be passivated by introducing hydrogen into the material (a-Si:H), which fills the nanovoids, saturates open silicon bonds and breaks weak silicon-silicon bonds to replace them with more stable silicon-hydrogen bonds [40–42]. The fundamental differences between amorphous and crystalline silicon with respect to their morphology and composition have a notable impact on their physical properties [43]. Its band gap is greater, with values ranging from 1.5 to 1.9 eV, depending on the hydrogen concentration in the material [44]. It is possible to dope amorphous silicon with the same elements that are used for crystalline silicon, namely phosphorus and boron [45]. However, the doping efficiency is low, because the amorphous network will rather fully integrate the dopant atoms, than allowing them to ionise and contribute a free electron or hole to the conduction or valence band, respectively. Consequently, at similar doping densities, the conductivity of amorphous silicon is orders of magnitude lower than the one of its crystalline counterpart [46].

Figure 2.3: a) Crystalline silicon b) Amorphous silicon with dangling bonds c) Hydrogenated amorphous silicon [47].

#### 2.1.3 Heterojunction Interfaces

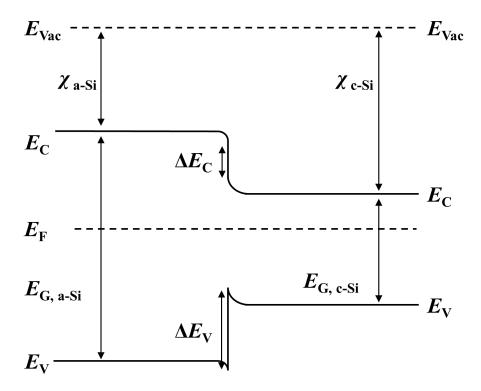

If two semiconductors featuring different band gaps are brought in contact, a heterojunction interface is formed. In equilibrium conditions, the band structures of both materials align with respect to a constant, common Fermi level. Figure 2.4 exemplifies a heterojunction interface between a crystalline and an amorphous silicon layer. Band bending and band offsets depend on the doping levels of the two materials and the amount and charge of interfacial surface states. The conduction band offset for an a-Si:H/c-Si heterojunction was determined to be around 200 meV [48]. Corresponding valence band offsets range between 200 and 450 mV, again depending on the doping of both the a-Si:H and c-Si layer [44,49].

#### 2.1.4 Contact Materials

In the context of this work, the materials that facilitate the extraction of charge carriers from the silicon layers (in this case the doped amorphous or nanocrystalline silicon layers) are denoted as contact materials. These are typically materials with high conductivities, such as metals or materials with metallic properties, e.g. degenerate semiconductors. According to the simple Schottky model, metals and semiconductors form Schottky contacts characterised by the band alignment that arises from the difference between the metal's work function and the semiconductor's electron affinity, resulting in the formation of an accumulation, neutral (flat band), depletion or inversion interface [50]. Ohmic contacts, as desired for solar cells, are ideally free from any barriers, which corresponds to the accumulation case. In reality metal-semiconductor contacts do not obey the simple Schottky model, as acceptor (or donor) surface states capture the metal's excess electrons (or holes) and thus barely affect the Fermi level within the semiconductor. Consequently the barrier height is hardly related to the metal's

Figure 2.4: Not drawn to scale band lineup of an amorphous/crystalline silicon interface, with the vacuum level  $E_{\text{Vac}}$ , the conduction band  $E_{\text{C}}$ , the valence  $E_{\text{V}}$ , the electron affinities  $\chi_{\text{c-Si}}$  and  $\chi_{\text{a-Si}}$ , the band offsets  $\Delta E_{\text{C}}$  and  $\Delta E_{\text{V}}$  and the corresponding band gaps denoted.

work function, but to the amount of surface states pinning the Fermi level. Metal-semiconductor contacts exhibiting ohmic behaviour are therefore achieved by using highly doped semiconductors. In these cases, the space charge region at the interface becomes narrow enough to allow sufficient tunnelling through the barrier as a current transport mechanism [51].

In this work, the following materials were used to contact highly doped p- and n-type a-Si:H layers:

Indium tin oxide (ITO) belongs to the group of transparent conductive oxides (TCO). It is an n-type degenerate semiconductor featuring a wide band gap of around 4 eV. Being transparent in the visible range of the solar spectrum, infrared light can be absorbed due to free carrier absorption, a process that depends heavily on the amount of charge carriers being present in the conduction band [24,52]. Its Fermi level is positioned in the conduction band, hence it exhibits metallic properties. Its work function is usually in the range of 4.4 to 4.8 eV [53].

**Aluminium-doped zinc oxide** (AZO) is a TCO material that exhibits similar properties to ITO. Its conductivity and thus also transparency depends heavily on the

2.2. SOLAR CELLS

amount of aluminium in the material. Given similar conductivity values to ITO, it is usually more transparent, but features lower work function values. [54, 55].

Tungsten oxide  $(WO_X)$  is an n-type semiconductor belonging to the group of transition metal oxides [56]. Depending on the oxygen concentration,  $WO_X$  features a high band gap, and more importantly a high work function above 5.5 eV, making it a promising candidate to form a carrier-selective recombination contact with p-type amorphous silicon [57].

**Silver** and **aluminium** are both metal materials exhibiting high – in case of silver the highest among all metals – values of electrical and thermal conductivity, as well as reflectivity. The work function of silver ranges between 4.3 and 4.7 eV while the one for aluminium is slightly lower with approximately 4.1 eV.

### 2.2 Solar Cells

A solar cell is a device that converts the energy of absorbed photons into electrical charge carriers, that can be driven through an external electric load. Various types of solar cells exist, based on different classes of materials [10]. This chapter solely focuses on solar cells based on crystalline silicon.

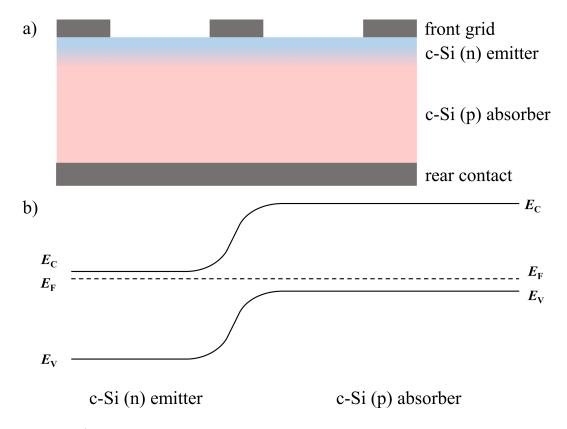

#### 2.2.1 Basic structure

A basic silicon solar cell consists of an either p- or n-doped silicon absorber layer with a thickness typically in the order of 100 to 300 µm, a much thinner emitter layer of the opposite polarity and contact layers, extracting the photogenerated charge carriers [7,58]. Between the absorber and the emitter layer, a pn-junction is formed. Light enters the solar cell through the side that is not fully metallised and is absorbed in the silicon bulk, generating electron-hole pairs. The generated minority charge carriers then diffuse towards the pn-junction where they are swept across the space charge region by the junction's internal electrical field and subsequently extracted through the metal contact. An equivalent amount of majority charge carriers is simultaneously extracted at the n-contact resulting in a net current flow, that can be driven through an external electric load. It is apparent that in an efficient solar cell the recombination of generated minority carriers should be prevented, as otherwise they are not able to contribute to the external current. In the very simple solar cell, shown in Figure 2.5, both the p- and the n-contact are formed by directly contacting a metal with the silicon emitter and the absorber, respectively. This results in poorly passivated surfaces acting as highly

recombination-active zones, thus limiting the open circuit voltage of these cells to values of around  $650 \,\mathrm{mV}$  [23, 59].

Figure 2.5: a) Not drawn to scale structure of a simple silicon solar cell, based on a crystalline p-type absorber, a diffused n-type emitter, and a direct metallisation. b) Band diagram of the simple silicon solar cell (without metallisation, not drawn to scale)

## 2.2.2 Heterojunction Solar Cells

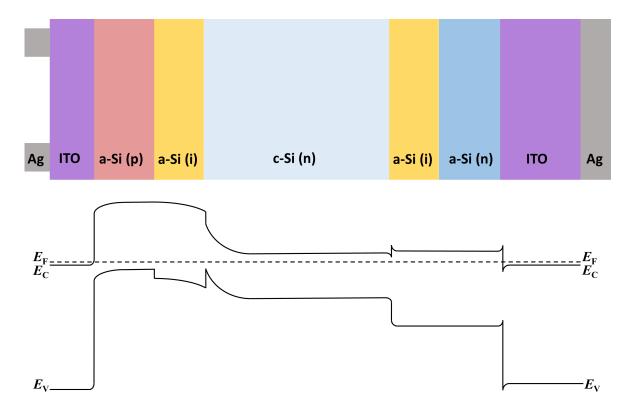

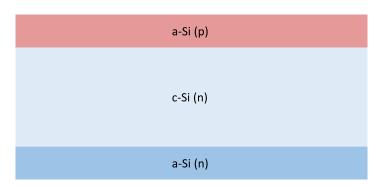

In a heterojunction solar cell the usually n-doped c-Si absorber is passivated on each side by an intrinsic a-Si:H layer, saturating open silicon bonds at the surface of the silicon crystal [16]. The chemical passivation of the absorber's surfaces reduces the recombination within the bulk to a minimum resulting in high minority carrier lifetimes [60]. The addition of an n-doped a-Si:H layer at the n-contact further increases the passivation quality by adding a field-effect, meaning the accumulation of majority and the depletion of minority charge carriers at this interface (back surface field, BSF contact). On the other side a p-doped a-Si:H layer on-top of the intrinsic passivation layer induces a thin inversion layer in the c-Si absorber thus forming the pn-junction needed for efficient charge carrier extraction [61,62]. The band offsets mentioned in subsection 2.1.3 and the band bending induced by the doped layers on either side of the wafer result in the formation of energetic barriers. The large energy barrier in

2.2. SOLAR CELLS

the valence band at the n-contact repels holes, while the energy barrier and the band bending in the conduction band at the p-contact repel electrons. The width of the otherwise counterproductive energetic barriers alongside the extraction direction of either charge carrier (conduction band at the n-contact, valence band at the p-contact) is decreased by the band bending so that the corresponding charge carriers can overcome these barriers either by tunnelling, hopping transport or thermionic emission [46,63–65].

In a front-emitter, mono-facial silicon heterojunction (SHJ) solar cell, light enters the cell through the emitter side, which is therefore contacted with a metal grid. The n-contact metallisation acts as a rear reflector and is thus fully metallised. On both sides a TCO layer is placed in-between the a-Si:H layers and silver electrodes. The TCO layer on the n-side enhances the optical response of the rear reflector by suppressing plasmonic absorption at an otherwise direct silver-silicon interface [52, 66]. At the p-side, the TCO provides the lateral conductivity necessary to allow the minority charge carriers to reach the metal grid fingers, as the p-type a-Si:H layer lacks conductivity. The front TCO also needs to be as transparent as possible to avoid parasitic absorption. Since high conductivity and high transparency are contradicting requirements, the front TCO design always involves a trade-off between these two properties. The situation is further exacerbated as the front-TCO also functions as an anti-reflection layer, thus the layer thickness has a rather small interval (70 to 80 nm in case of ITO) [24].

Figure 2.6 visualises the layer stack and the corresponding band diagram.

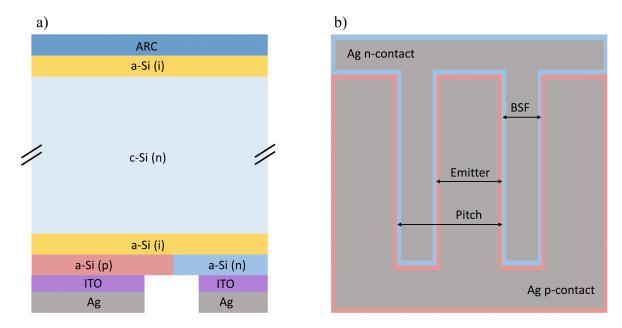

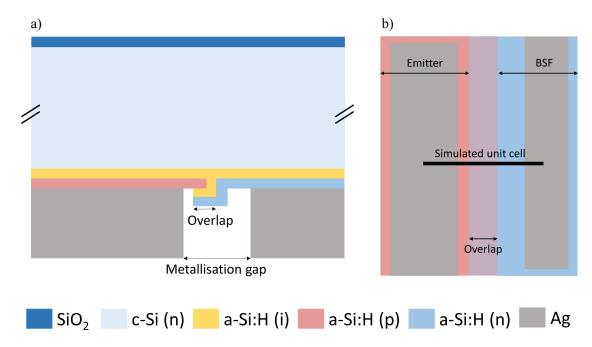

#### 2.2.3 Interdigitated Back Contact Solar Cells

In a back contacted solar cell, both the emitter and the absorber are contacted at the device's rear side, i.e. the side facing away from the illumination. This allows to optimise the front side solely with respect to its optical and passivating properties, which is especially beneficial for SHJ solar cells since the non-ideal, multipurpose front-TCO is omitted [27,67,68]. The absence of a metal grid – inflicting shadowing losses, and emitter or BSF layers – parasitically absorbing part of the incoming light, at the front side leads to an increase in light absorption in the c-Si absorber material.

The two contacts at the rear side of back contacted cells are usually patterned as interdigitated finger structures, with busbars collecting the respective charge carriers at opposite sides of the cell [69]. The interdigitated approach also allows to describe the basic contact geometry with a small set of parameters, namely the pitch as the sum of the widths of both contacts, the emitter coverage as the percentage of the rear-side area that is covered by the emitter contact and the total cell area (in this approach, potential gaps between the contacts and the metallisation coverage of the contact areas are neglected, however these are usually small compared to the overall dimensions

Figure 2.6: Not drawn to scale structure and band diagram of a front-emitter, monofacial silicon heterojunction solar cell. The n-type c-Si absorber is passivated by intrinsic a-Si:H layers. Emitter and BSF contact are formed by p- and n-doped a-Si:H layers, the metallisation in this case consists of an ITO/Ag stack on both sides. In the band diagram the conduction band  $E_{\rm C}$ , the valence band  $E_{\rm V}$  and Fermi level  $E_{\rm F}$  are denoted.

of the finger structures) [70]. Figure 2.7 a shows the schematic of an interdigitated back-contact silicon heterojunction solar cell, Figure 2.7 b illustrates the interdigitated structure and the key parameters.

Point contacts are an alternative option to the interdigitated pattern. However the metallisation is usually more complicated, as the point contacted areas are fully surrounded by the contact area of the other polarity. Hence additional layers have to be added, one to connect the different point contacts and one to isolate this connection layer from the contact area of opposing polarity [71,72].

## 2.2.4 Basic Parameters and Equivalent Circuit

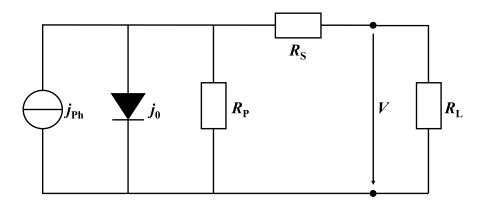

Containing a pn-junction, a solar cell is a particular type of diode. In a simple equivalent circuit, shown in Figure 2.8, this diode is accompanied by an ideal current source, representing the photogenerated current  $j_{\text{Ph}}$  and the series and the parallel resistances  $R_{\text{S}}$  and  $R_{\text{P}}$ , representing the ohmic losses within the device. The following

2.2. SOLAR CELLS 17

Figure 2.7: a) Not drawn to scale layer stack of an interdigitated silicon heterojunction solar cell. The c-Si (n) absorber is still passivated by intrinsic a-Si:H on both sides. The doped a-Si:H layers, forming the emitter and BSF contacts, are placed at the rear side of the device. The metallisation still consists of an ITO/Ag stack for both contacts. b) Rear side view with interdigitated structure: the pitch equals the sum of the emitter and the BSF width – both contacts are almost fully metallised, leaving a small metallisation gap in-between them.

equation describes the current-density-voltage relation of the equivalent circuit in Figure 2.8 [73]:

$$j(V) = j_0 \left( \exp\left(\frac{q(V - jR_S)}{mkT}\right) - 1 \right) + \frac{V - jR_S}{R_P} - j_{Ph}$$

(2.2)

Here k represents the Boltzmann constant, T the temperature, q the elementary charge, V the external voltage, m the ideality factor,  $j_{\rm Ph}$  the external photocurrent, and  $j_0$  the reverse bias saturation current. The latter represents the cumulative recombination within the device in equilibrium conditions and is therefore linked to the diode's or rather solar cell's material quality. The ideality factor m accounts for deviations from the ideal diode equation (m=1), that only considers recombination mechanisms proportional to the charge carrier density product. In reality the recombination in a solar cell is governed by multiple mechanisms that do not necessarily obey this relation, for instance recombination mechanism predominantly occurring at higher injection levels (Auger, SRH recombination incorporating majority carriers). Hence, both  $j_0$  and m need to be adjusted accordingly.

The magnitude of the series resistance  $R_{\rm S}$  depends on the resistance of the different materials conducting the current and the contact resistivity of the respective interfaces. It is thus influenced by the doping level of the bulk, emitter and BSF layers as well as the conductivity of the TCO and metallisation layers.  $R_{\rm P}$  represents current paths bypassing the pn-junctions in the form of shunts between the two contacts. Typical current-density-voltage (jV) characteristics of a solar cell with different values for  $R_{\rm S}$  and  $R_{\rm P}$  are shown in Figure 2.9.

From the jV curve it is possible to extract the solar cell's characteristic parameters:

The **open circuit voltage**  $(V_{\rm OC})$ , at which the internal recombination currents within the solar cell exactly compensate the photogenerated current, resulting in zero external current. The maximum possible  $V_{\rm OC}$  for a silicon solar cell was calculated to be 761 mV, assuming a practically perfect diode (very low  $j_0$ , m=2/3) and taking only Auger recombination as an intrinsic recombination mechanism into account [12].

Figure 2.8: Equivalent circuit of a solar cell, consisting of a diode representing the pn-junction, an ideal current source for the photogenerated current and the resistances  $R_{\rm P}$  and  $R_{\rm S}$ , representing ohmic losses.

The short circuit current density  $(j_{SC})$  describes the current density measured at V=0, at which practically all photogenerated charge carriers recombine over the external shunt. Since the recombination current within the diode at V=0 is usually negligible, the  $j_{SC}$  is basically equal to  $j_{Ph}$  and therefore a good figure of merit for the absorption capabilities of the solar cell. Taking into account silicon's band gap of 1.12 eV and assuming an AM1.5G irradiation, the theoretical maximum  $j_{SC}$  is  $46 \,\mathrm{mA/cm^2}$ , with the practical limit being  $43.3 \,\mathrm{mA/cm^2}$  [12, 13].

The **maximum power point** (MPP) voltage  $V_{\text{mpp}}$  and current density  $j_{\text{mpp}}$  are the voltage or current density values at which the product of V and j maximises. The product of  $V_{\text{mpp}}$  and  $j_{\text{mpp}}$  divided by the power input  $P_{\text{in}}$  (100 mW/cm<sup>2</sup> under AM1.5G conditions) yields the solar cell's **efficiency**  $\eta$ . Although the MPP-values ultimately

2.2. SOLAR CELLS

Figure 2.9: a) Influence of high  $R_{\rm S}$  and low  $R_{\rm P}$  values on an otherwise typical jV curve. b) Visualisation of the characteristic parameters of a jV curve, with the power square dashed.

determine the solar cell's efficiency, they are not very well suited for characterisation and comparison of different solar cells or technologies. In real world operation, the MPP will change over time and outer conditions, therefore the attached power inverters track the MPP of the corresponding modules.

To circumvent the use of MPP-values, the **fill factor** (FF) is introduced as another figure of merit. It is calculated by dividing the MPP-product by the product of the  $V_{\text{OC}}$  and the  $j_{\text{SC}}$ :

$$FF = \frac{V_{\text{mpp}} \cdot j_{\text{mpp}}}{V_{\text{OC}} \cdot j_{\text{SC}}} \tag{2.3}$$

As Figure 2.9 shows, the FF is impacted by both the  $R_{\rm P}$  and the  $R_{\rm S}$ , but also high recombination within the device can have a detrimental effect on the FF. To optimise the FF and analyse contributions to FF losses is one of the major challenges when developing efficient solar cells. Richter *et al.* estimate the maximum achievable fill factor for silicon-based solar cell to 89.3 % [12].

Using the aforementioned parameters it is possible to calculate the solar cell's efficiency  $\eta$  as follows:

$$\eta = \frac{V_{\text{mpp}} \cdot j_{\text{mpp}}}{P_{\text{in}}} = \frac{FF \cdot V_{\text{OC}} \cdot j_{\text{SC}}}{P_{\text{in}}}$$

(2.4)

The latter expression only contains parameters that can either be backtracked to physical properties of the device (optical properties and resulting absorption in the case of the  $j_{SC}$  and semiconductor properties and passivation quality in case of the  $V_{OC}$ ) or, in case of the FF, are at least comparable among different solar cells and solar cell technologies. With the aforementioned maximum values for each parameters, the maximum achievable efficiency for a silicon-based solar cell amounts to 29.4 % [12].

# Chapter 3

# Fabrication, Characterisation and Simulation

In this chapter the technological background with respect to deposition and patterning techniques is outlined. Furthermore, the used characterisation methods are briefly explained. At last, the simulation software Sentaurus TCAD is introduced and validated.

## 3.1 Deposition and Patterning Techniques

For the preparation of interdigitated back contact silicon heterojunction (IBC SHJ) solar cells, it is necessary to deposit and accurately structure thin layers with thicknesses ranging from a few nanometres to a couple of micrometres. In the following, the basics of deposition and patterning techniques relevant for SHJ solar cell manufacturing are described in general. The specific processes that were used to build the solar cells presented in this thesis are discussed extensively in chapter 4.

## 3.1.1 Deposition

This section focuses on deposition techniques that are typical for the manufacturing of SHJ solar cells.

Plasma-enhanced chemical vapour deposition (PECVD) is a technique to deposit solid thin films. A plasma discharge is created between two conductive electrodes, either by applying direct current (DC) or alternating current (AC), with the latter being the more common. The discharge ionises a significant portion of the precursor gas's atoms or molecules. These radicals are then transported towards the substrate's surface, where they are adsorbed and surface diffuse until they react with the surface's

atoms forming a layer. In case of a-Si:H deposition, the precursor gas is usually silane (SiH<sub>4</sub>), with hydrogen (H<sub>2</sub>) being added further hydrogenate the layer [74]. Doped layers can be formed by adding the corresponding precursor gases, e.g. phosphine (PH<sub>3</sub>) for n-doping or diborane (B<sub>2</sub>H<sub>6</sub>) for p-doping.

A PECVD process is characterised by multiple parameters. Small changes in precursor composition, gas pressure, plasma power, substrate temperature, electrode distance and deposition time can have a drastic influence on the deposited layer's properties [75–77]. A carefully optimised PECVD process is therefore a major requirement for a functioning heterojunction solar cell manufacturing process.

Sputter Deposition is part of the group of processes subsumed as physical vapour deposition (PVD) processes, in which a material in a condensed phase is transformed into a vapour phase and subsequently into a condensed phase again. In a sputter process, the initial condensed phase exists in the from of a sputter target. Between the substrate, e.g. a silicon wafer, and the sputter target a plasma is ignited containing an ionised inert gas like argon, either by DC or AC voltage. The ions of the inert gas then impact onto the target's surface ejecting atoms from it. Depending on gas pressure and temperature, the ejected ionised atoms either ballistically fly towards the substrate or collide with the inert gas's atoms and diffuse towards the substrate (and its surroundings). Reactive gases can be added to the sputtering gas in order to influence the composition of the sputtered layer [78]. An indium tin oxide (ITO) layer, for instance, can be sputtered from an indium tin target, with oxygen added to the process gas. Depending on the plasma power, a sputter process is likely to inflict physical damage to the substrate's surface. This has to be taken into account especially when TCO layers are sputtered onto thin a-Si:H passivation layers on silicon wafers [79].

Thermal Evaporation is a PVD process, in which a solid material is evaporated in a vacuum chamber. The evaporated material then travels towards the substrate's surface, where it condenses again. In contrast to sputtering, thermal evaporation will not inflict physical damage to the substrate's surface, however high process temperatures as well as the condensation or crystallisation enthalpy might have an annealing effect on the substrate.

#### 3.1.2 Patterning

In order to manufacture back contacted solar cells, the contacted side needs to be patterned in an appropriate way. Many patterning methods with varying degrees of complexity and accuracy exist, usually the latter depends on the former. Patterning can be done in-situ, combining deposition and patterning in one process, or after the deposition, removing parts of a deposited layer by means of etching. The following sections focus on pattering techniques used to structure layers relevant for the fabrication of SHJ solar cells. These are a-Si:H, TCO and metal films.

Photolithography is a widely used and accurate patterning technique [80]. The layer to be structured is coated with a thin layer of a photoactive resist. Through a mask, the resist is then partly exposed to light and afterwards put into a developer solution. Depending on the type of resist, positive or negative, the parts that were exposed to light are dissolved during the developing or insensitive to the developer solution. In the latter case the unexposed parts of the resist are dissolved. As a result, the structure of the mask (or its negative) is transferred to the resist layer. In a subsequent step, parts not covered by resist are etched, either by using wet chemicals or dry etching methods like reactive ion etching (RIE) [81]. Depending on the masking approach, the mask can be in direct contact with the substrate or projected onto it through a system of lenses, the minimum feature achievable with this method is in the order of a few nanometres (modern computer chips with transistor channel widths in the range of 10 to 20 nm are commercially available [82]). Since for photovoltaic applications the minimal needed dimensions are in the range of a few micrometers, contact masking is sufficient. Owing to the many process steps (usually involving multiple annealing, etching and rinsing steps) photolithography is a lengthy process and thus not regarded as an industrially viable manufacturing method for high volume solar cell fabrication.

Shadow Masking In contrast to photolithography, where the layer is structured after its full-area deposition, the use of shadow masks enables in-situ patterning. To avoid or minimise tapering effects at the structure's edges, the masks should to be as thin as possible. At the same time they have to exhibit a certain amount of mechanical stability. Furthermore, the masks have to withstand the process conditions with regards to elevated temperatures or the presence of a plasma. As the masks will be directly placed onto the substrate, they must not contaminate or alter the surface of the substrate or the conditions in the process chamber. The deposition process itself also has to be compatible with the masking approach. If the film growth on the substrate's surface is governed by surface diffusion processes, which is possible for both PECVD and sputtering processes, undesired deposition under the mask represents a serious issue. If multiple masks in subsequent steps are used, a suitable alignment method is necessary. To maintain the desired simplicity of the process, the masks will be fixed mechanically in most cases, either by clamps or pin holes. This procedure results in several micrometers of alignment inaccuracy.

As a consequence of all these requirements the minimal feature size for a shadow mask based process is more likely to be in the range of hundreds of micrometers.

Laser Ablation The variety of lasers with different characteristics in terms of wavelength, pulse width and power enables many different laser-based patterning techniques. Lasers can be used to directly ablate single a-Si layers from c-Si substrates [83]. However, direct ablation incorporates the risk of damaging the underlying silicon surface so that its repassivation with intrinsic a-Si:H is either more difficult, insufficient or impossible. In most cases, laser ablation is used to structure protective or sacrificial layers that then function as masking layers for subsequent etching processes [84–86].

In theory laser ablation related patterning techniques are less complex compared to a photolithography process. Their industrial viability mostly depends on the complexity of the non-laser process steps, such as the deposition of multiple, potentially intricate sacrificial layers or etching steps still involving wet chemicals.

Screen Printing is a method primarily used to deposit in-situ structured metal layers. A metal paste, usually based on silver or aluminium particles, is pressed onto the substrate through a screen. The screens are made of a fine synthetic mesh, in which the application of a blocking stencil, being impenetrable for the paste, defines the desired structure. A squeegee then presses the paste through the penetrable parts of the screen transferring it onto the substrate. The minimum feature size, in the range of tens of micrometers, is limited by the expansion of the paste during the annealing after printing [87, 88].

Screen printing can also be used to apply etch resists, thus replacing the light exposure and resist developing part of the photolithography process.

#### 3.2Characterisation

The knowledge of the silicon-specific physical limitations allows to determine the solar cell technology's efficiency potential. Loss mechanisms hindering the exploitation of this potential can be identified by various characterisation methods.

In the following, the different methods used to characterise the solar cells presented in this work are briefly described.

#### jV measurements 3.2.1

To determine the solar cell's efficiency by measuring its light jV curve, a solar simulator is used. The class AAA Wacom WXS-156S-L2 simulates the terrestrial solar spectrum using both a tungsten and a xenon lamp [89]. During the measurements, the solar cells are mounted in a water-cooled (maintaining a temperature of 25 °C), custom measuring chuck, masking everything but the cell area. Dark jV curves were measured using the same setup with the entire wafer covered.

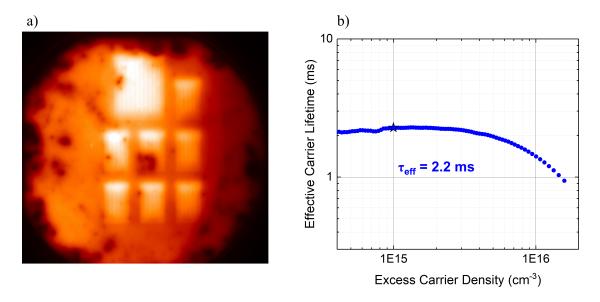

#### 3.2.2 TrPCD

The transient photoconductance decay method (TrPCD) is used to determine the effective minority charge carrier lifetime  $\tau_{\rm eff}$  of a passivated, non-metallised silicon wafer. A flash unit emitting mostly infrared photons generates a certain amount of excess carriers within the device thus leading to an increased conductivity within the wafer, which decays shortly afterwards as the excess carriers recombine. The increase of the wafer's conductivity is detected by the changing inductance of a coil, placed below the wafer. The coil is part of an oscillating circuit, which, as a consequence of the shift in inductance, changes its frequency [90]. The TrPCD measurements were conducted using a WCT-100 wafer-lifetime tool by Sinton Instruments.

Since the wafer's thickness and silicon's charge carrier mobilities are known, the amount of excess carriers  $\Delta n$  can be calculated directly from the measured increase in conductivity. Given minority charge carrier lifetimes far greater than the decay time of the flash, the injection dependant effective charge carrier lifetime is then the result of the division of the measured excess charge carrier density by its temporal gradient [91]:

$$\tau_{\text{eff}}(\Delta n) = \frac{\Delta n}{\left|\frac{\partial \Delta n}{\partial t}\right|} \tag{3.1}$$

#### Implied Fill Factor

The result of the TrPCD measurement  $\tau_{\text{eff}}(\Delta n)$  can be used to calculate an implied jV curve based on the passivation properties of the silicon wafer and an assumed photogenerated current density  $j_{\text{Ph}}$  [92]. The voltage is directly calculated from the excess charge carrier density  $\Delta n$ , as it is, under optimal conditions, equal to the Fermi level separation induced by the photogenerated excess carriers [93]:

$$V = \frac{kT}{q} \ln\left( (n_0 + \Delta n)(p_0 + \Delta n)/n_i^2 \right)$$

(3.2)

Here k is the Boltzmann constant, T the temperature and q the elementary charge. The current is then calculated from the difference between the assumed photogenerated current density and the recombination rate given by effective lifetime measurement:

$$j = j_{\rm Ph} - qd\Delta n/\tau_{\rm eff}(\Delta n) \tag{3.3}$$

Here d represents the wafer's thickness. From the resulting implied jV curve the implied fill factor (iFF) can be determined. The iFF does not include loss mechanisms arising from a potential degradation of the passivation during the subsequent metallisation process or from transport barriers respectively series resistance effects. It therefore represents an upper limit for the achievable FF based on the passivation quality provided by the a-Si:H deposition and patterning processes.

#### 3.2.3 Photoluminescence

In a photoluminescence measurement (PL) a passivated wafer is exposed to a light source emitting photons with an energy greater than the wafer's band gap. Depending on the optical properties of the wafer's surface and its thickness, a certain amount of these photons will be absorbed by the wafer. The absorbed photons generate charge carriers, which eventually recombine, given the fact that the wafer is not contacted. In a wafer with a high charge carrier bulk lifetime and high quality surface passivation, a large portion of the photogenerated charge carriers will recombine radiatively, emitting photons with an energy corresponding to the wafer material's band gap. A photodiode can then detect the emitted photons. The intensity of the emitted light directly relates to the passivation quality of the wafer. If an array of photodiodes (e.g. a camera sensor) is used, the passivation quality of the wafer can be spatially resolved. Well passivated areas on the wafer, where radiative recombination dominates, will appear bright, defect-rich areas, where SRH recombination is predominant, dark.

The setup used for this work is equipped with light emitting diodes emitting light with a wavelength of 650 nm. An optical filter blocking light with wavelengths up to 800 nm is attached to the corresponding camera, ensuring that only radiative recombination is captured. The setup did not allow to differentiate between recombination within the bulk or at the surface. Since only high-quality float-zone silicon wafers were used, dark areas were mainly caused by improper surface passivation. While it is possible to calibrate PL setups in order to gain quantitative information about the passivation quality, for instance an effective lifetime analogue to the aforementioned TrPCD method, PL measurement results in this work were only used for qualitative comparisons among different wafer samples.

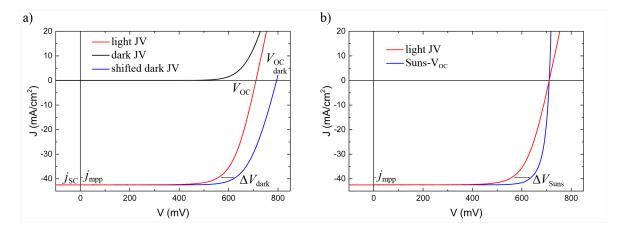

#### 3.2.4 Suns- $V_{\rm OC}$

The  $V_{\rm OC}$  of a solar cell strongly depends on the illumination intensity I. By altering the latter, it is therefore possible to generate an  $I-V_{\rm OC}$  curve. Assuming a linear relation between I and the  $j_{\rm SC}$ , the curve can be transformed into a  $j_{\rm SC}-V_{\rm OC}$  curve, where the  $j_{\rm SC}$  at AM1.5G illumination is set to the expected or measured value for the specific solar cell technology (i.e.,  $41.5\,\mathrm{mA/cm^2}$  for an IBC SHJ solar cell in this work). The fill factor of this pseudo jV curve is called pseudo fill factor (pFF) [94]. Since the Suns- $V_{\rm OC}$  curve is measured entirely under open circuit conditions with no current extracted from the device, the pFF is not influenced by series resistance related losses. Hence the difference between the FF extracted from the normal jV curve and the pFF is a good indicator for series resistance related loss contributions to the FF (if the latter is not limited by S-shapes resulting from non-linear transport barriers). On the other hand, a significant difference between the pFF and the iFF indicates a potential degradation of the passivation during the metallisation process.

Suns- $V_{\rm OC}$  curves were measured using the respective Suns- $V_{\rm OC}$  accessory station to Sinton Instrument's WCT-100 wafer-lifetime tool.

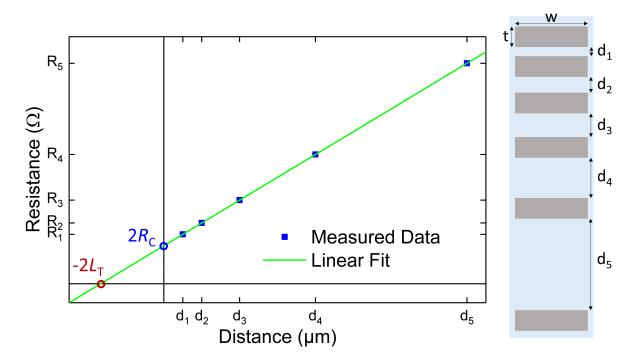

## 3.2.5 Transfer Length Method

The transfer length method (TLM) allows to determine the contact resistivity of a layer stack consisting of two or more layers [95,96]. The layers are structured into multiple, parallel stripes of equal area and shape, but differing in spacing (see Figure 3.1). The resistance of two neighbouring stripes is then plotted over their respective distance. If the contacts between all layers are ohmic, the resulting curve follows a linear trend. By extrapolating the curve the resistance value  $R_{\rm C}$ , representing the resistance for a distance of zero, can be determined as half of the intersection with the ordinate. The half of the absolute value of the intersection with the abscissa gives the so-called transfer length  $L_{\rm T}$  [97]. Taking into account the geometry of the stripes, the contact resistivity  $\rho_{\rm C}$  can be calculated using the following equation [98]:

$$\rho_{\rm C} = R_{\rm C} L_{\rm T} w \frac{1}{\coth(t/L_{\rm T})} \tag{3.4}$$

Here w represents the width of the stripes and t their length. Knowing  $R_{\rm C}$  and  $L_{\rm T}$  it is also possible to determine the sheet resistance  $R_{\square}$  of the material between the stripes:

$$R_{\square} = \frac{R_{\rm C}}{L_{\rm T}} w \tag{3.5}$$

$R_{\square}$  represents the superposition of the sheet resistances of the materials between the two fingers, that contribute to the current transport. In most cases one material features a much lower resistance than the others and thus represents the dominant current path. For instance, in case of silver metal stripes on top of an ITO layer and a silicon wafer substrate, the TLM method will provide the resistivity of the ITO/Ag contact and the sheet resistance of the ITO, as it is usually significantly more conductive than the wafer bulk. If the ITO is structured together with the silver fingers, the contact resistivity extracted by the TLM method will be a superposition of the both contacts, silicon/ITO and ITO/Ag, with the latter likely being orders of magnitude lower than the former. Furthermore, the resistance of the current path within the silicon wafer will be extracted. This value usually correlates to the wafer's nominal resistivity, however in the presence of doped a-Si:H layers on the c-Si wafer, between the TLM stripes, the accumulation of majority charge carriers in the wafer might affect the resistance of the wafer current path.

The jV curves between the respective metal stripes were measured using the 4-point probes method, thus eliminating any resistance contribution arising from the contact resistance between the probes and the metal stripes.

Figure 3.1: Determination of the TLM method's characteristic parameters  $R_{\rm C}$  and  $L_{\rm T}$  based on measured resistance values and linear fitting; the corresponding TLM structure is depicted on the right side.

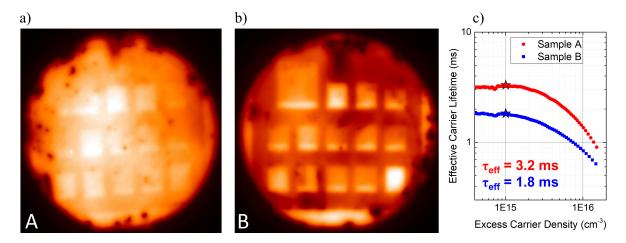

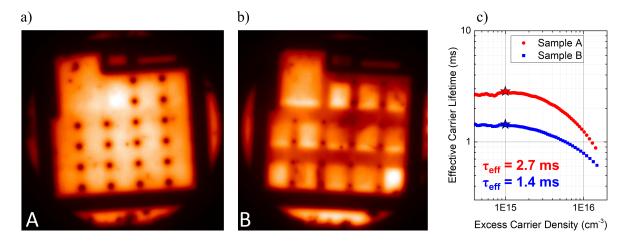

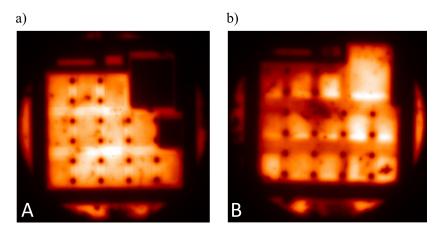

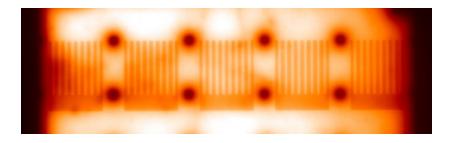

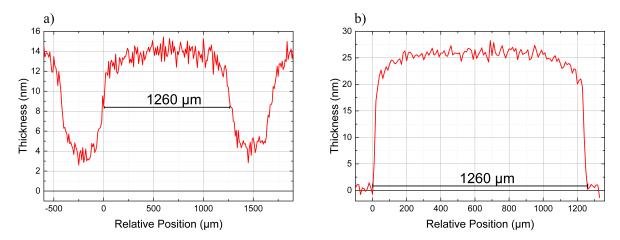

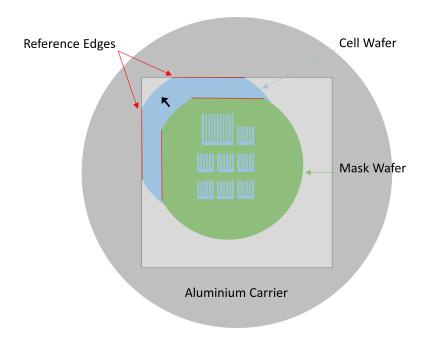

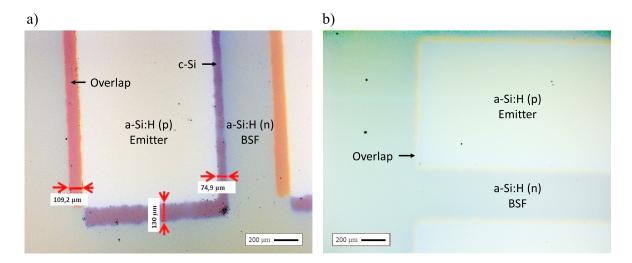

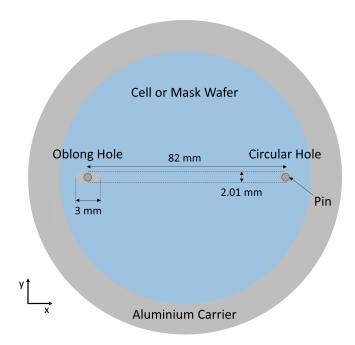

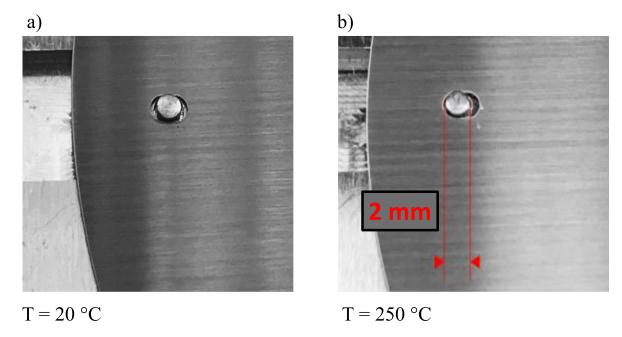

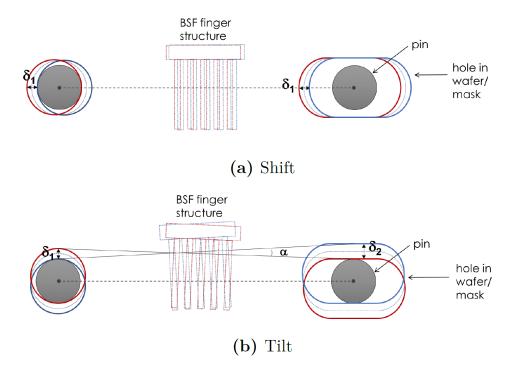

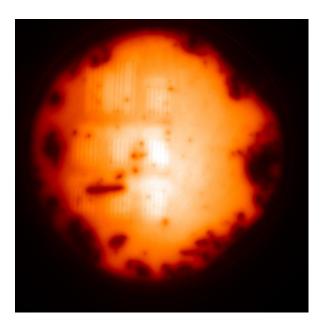

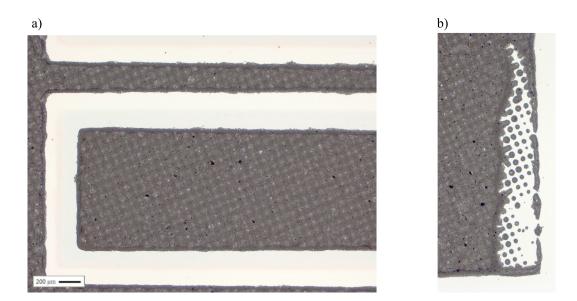

#### 3.2.6 Series Resistance Calculation