## High-Throughput HEVC CABAC Decoding

## vorgelegt von M.Sc. Philipp Habermann

an der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften - Dr.-Ing. -

genehmigte Dissertation

#### Promotionsausschuss:

Vorsitzender: Prof. Giuseppe Caire, Ph.D.

Gutachter: Prof. Dr.-Ing. Thomas Sikora

Gutachter: Prof. Dr.-Ing. Benno Stabernack

Gutachter: Dr.-Ing. Jens Brandenburg

Tag der wissenschaftlichen Aussprache: 02.11.2020

## Abstract

Video applications have emerged in various fields of our everyday life. They have continuously enhanced the user experience in entertainment and communication services. All this would not have been possible without the evolution of video compression standards and computer architectures over the last decades. Modern video codecs employ sophisticated algorithms to transform raw video data to an intermediate representation consisting of syntax elements, which allows enormous compression rates before reconstructing the video with minimal objective quality losses compared to the original video. Modern computer architectures lay the foundation for these computationally intensive tasks. They provide multiple cores and specialized vector architectures to exploit the massive amount of parallelism that can be found in video applications. Customized hardware solutions follow the same principles. Parallel processing is essential to satisfy real-time performance constraints while optimizing energy efficiency, the latter being the most important design goal for mobile devices.

One of the main tasks in modern video compression standards implements a highly sequential algorithm and lacks data-level parallelism in contrast to all other compute-intensive tasks: Context-based Adaptive Binary Arithmetic Coding (CABAC). It is the entropy coding module in the state-of-the-art High Efficiency Video Coding (HEVC) standard and also its successor Versatile Video Coding. Its purpose is the compression and decompression of the intermediate video representation by exploiting statistical properties, thus achieving minimal bitrates. CABAC is one of the main throughput bottlenecks in video coding applications due to the limited parallelization opportunities, especially for high-quality videos. Close-distance control and data dependencies make CABAC even more challenging to implement with modern computer architectures. This thesis addresses the critical CABAC decoding throughput bottleneck by proposing multiple approaches to uncover new parallelization opportunities and to improve the performance with architectural optimizations.

First of all, we quantitatively verify the severity of the CABAC decoding throughput bottleneck by evaluating the HEVC decoding performance for various workloads using a representative selection of state-of-the-art computer architectures. The results show that even the most powerful processors cannot provide real-time performance for several high-quality workloads. The profiling results clearly show that CABAC decoding is the main reason for that in most cases.

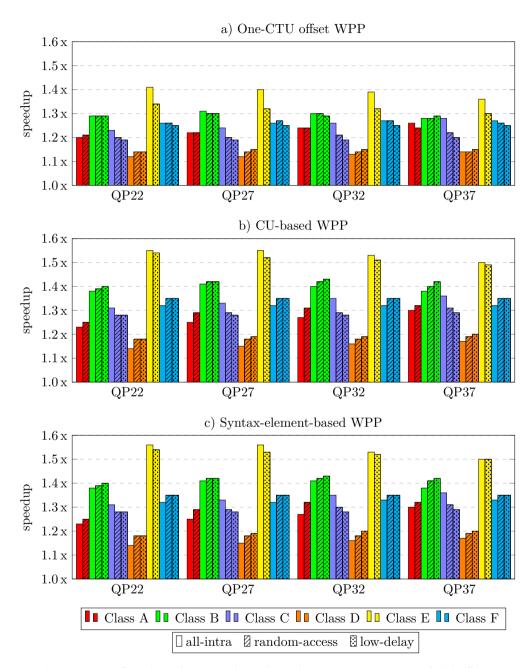

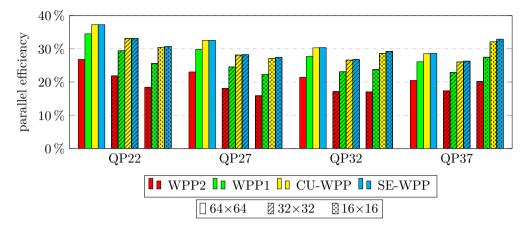

Wavefront Parallel Processing (WPP) is a well-established high-level parallelization technique used in video coding and other applications. It can lead to a high degree of parallelism, however, it suffers from inefficiencies due to the dependencies between consecutive rows in a frame. We present three WPP implementations for HEVC CABAC

decoding with improved parallel efficiency. The WPP versions based on more fine-grained dependency checks allow speed-ups up to  $1.83 \times$  at very low implementation cost.

We also present a bitstream partitioning scheme for future video compression standards. It enables additional parallelism in CABAC decoding by distributing syntax elements among eight bitstream partitions. Besides the parallelization opportunities, this allows specialization of the subdecoders responsible for the processing of their corresponding partitions as they have to process fewer types of syntax elements. This leads to further improvements in clock frequency and significant hardware savings compared to a full replication of the CABAC decoder as it is required for approaches such as WPP. Decoding speedups up to  $8.5\times$  at the cost of only 61.9% extra hardware area and less than 0.7% bitstream overhead for typical Full High Definition videos make this technique a promising candidate for use in future video compression standards.

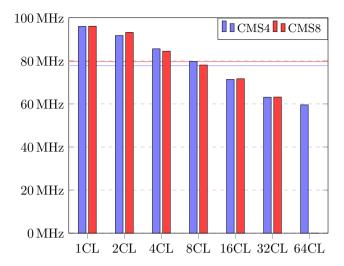

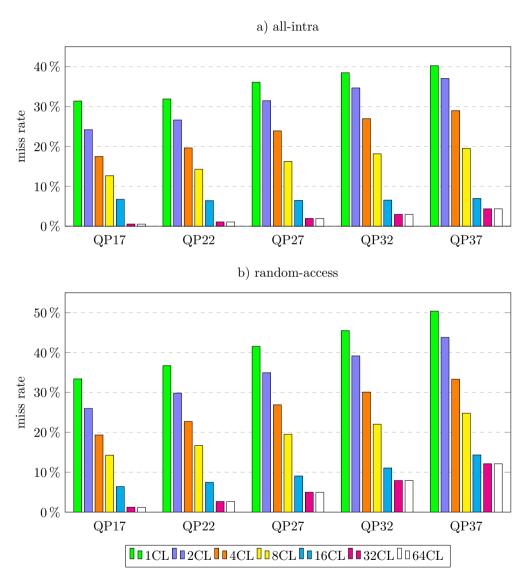

Furthermore, a cache-based architectural optimization is presented. It replaces the context model memory – a critical component in the CABAC decoder pipeline – by a smaller cache, thus increasing the achievable clock frequency. An application-specific adaptive prefetching algorithm is used together with a context model memory layout optimized for spatial and temporal locality. We perform a design space exploration of different cache configurations, finding that a cache of  $2\times 8$  context models provides the best performance. It allows for a 17% increase in clock frequency and miss rates of less than 2%, resulting in performance improvements up to 16.7%.

We also propose techniques for more efficient CABAC decoding on general-purpose processors. Frequent hardly predictable branches lead to very inefficient implementations with these processors. Using more complex but linear arithmetic functions for the parallel decoding of binary symbols provides a speedup of up to  $2.04\times$ . A separate bitstream partition for this type of binary symbol even allows speedups up to  $2.45\times$  at the cost of not more than 0.2% higher bitrate for typical Full High Definition videos.

Finally, we provide recommendations for future video compression standards and computer architectures as well as further research ideas for video coding in general and CABAC in particular. The research conducted in this thesis shows multiple approaches that can substantially improve the performance of CABAC decoding, thereby addressing one of the most critical throughput bottlenecks in modern video coding applications.

## Zusammenfassung

Videoanwendungen haben sich in vielen Bereichen unseres täglichen Lebens etabliert und dabei die Nutzererfahrung in den Bereichen Unterhaltung und Kommunikation zunehmend verbessert. Das wäre ohne die ständige Weiterentwicklung von Videokompressionsstandards und Computerarchitekturen nicht möglich gewesen. Moderne Videocodecs nutzen komplexe Algorithmen, um rohe Videodaten in eine aus Syntaxelementen bestehende Zwischenrepräsentation zu transformieren, was enorme Kompressionsraten erlaubt. Die anschließende Rekonstruktion der Videodaten kann mit minimalen Qualitätsverlusten im Vergleich zum Originalvideo durchgeführt werden. Modern Computerarchitekturen legen die Grundlage für diese rechenintensiven Prozesse. Sie stellen zahlreiche Rechenkerne und spezialisierte Vektorarchitekturen zur Verfügung, welche die zahlreichen Parallelisierungsmöglichkeiten in Videoanwendungen ausnutzen. Die parallele Datenverarbeitung ist essenziell, um die Echtzeitfähigkeit zu gewährleisten und gleichzeitig die Energieeffizienz zu optimieren, was insbesondere für Mobilgeräte eines der wichtigsten Entwicklungsziele darstellt.

Context-based Adaptive Binary Arithmetic Coding (CABAC) ist das Entropiekodierungsverfahren im aktuellen High Efficiency Video Coding (HEVC) Standard, sowie in dessen Nachfolger Versatile Video Coding. CABAC ist für die Kompression und Dekompression der Zwischenrepräsentation eines Videos unter Ausnutzung statistischer Gegebenheiten verantwortlich, wodurch minimale Bitraten erreicht werden können. Dafür wird ein sequentieller Algorithmus verwendet, der CABAC im Vergleich zu allen anderen rechenintensiven Komponenten aktueller Videokompressionsstandards keine Ausnutzung von Datenparallelität ermöglicht. Durch die mangelnden Parallelisierungsmöglichkeiten ist CABAC eine der kritischsten Komponenten, welche die Gesamtleistung eines Videodekoders beschränken. Das gilt insbesondere für Videos mit hoher Qualität und dementsprechend hohen Bitraten. Außerdem stelle eine Vielzahl an Steuerund Datenabhängigkeiten in CABAC moderne Computerarchitekturen vor große Herausforderungen. Das Ziel dieser Doktorarbeit ist die Verbesserung der Leistung des CABAC-Dekoders, da er die Gesamtleistung aktueller Videodekoder maßgeblich beeinflusst. Wir stellen dafür verschiedene Ansätze vor, die einerseits neue Parallelisierungsmöglichkeiten schaffen und andererseits durch architekturelle Optimierungen effizientere Implementierungen ermöglichen.

Zuerst verifizieren wir quantitativ, dass CABAC für den Dekodierungsprozess in HEVC eine kritische Komponente ist. Dafür analysieren wir die Dekodierleistung einer repräsentativen Auswahl aktueller Computersysteme für verschiedene typische Videoanwendungen. Die Ergebnisse zeigen, dass selbst die performantesten Prozessoren nicht für alle Anwendungen echtzeitfähig sind. Weitere Untersuchungen bestätigen deutlich, dass CABAC in den meisten Fällen dafür hauptverantwortlich ist.

Anschließend beschäftigen wir uns mit der Optimierung von Wavefront Parallel Processing (WPP). Dabei handelt es sich um eine weit verbreitete Parallelisierungstechnik, die in der Videokodierung und vielen anderen Anwendungen verwendet wird. WPP erlaubt ein hohes Maß an Parallelisierung, erleidet aber wegen der Abhängigkeiten zwischen benachbarten Bildbereichen Einbußen in seiner Effizienz. Wir stellen drei Implementierungsvarianten vor, die die Effizienz der Parallelisierung mit WPP für CABAC in HEVC deutlich verbessern. Dies wird durch eine feingranularere Prüfung von Abhängigkeiten im Vergleich zu konventionellen WPP-Implementierungen erreicht. So kann die Dekodierung von Videos um einen Faktor von bis zu  $1.83 \times$  beschleunigt werden, während die Implementierung nur unwesentlich komplexer wird.

Dann stellen wir ein Bitstreampartitionierungsschema für zukünftige Videokompressionsstandards vor, welches zusätzliche Parallelisierungsmöglichkeiten schafft. Dies wird durch die Aufteilung aller Syntaxelemente unter Berücksichtigung ihrer Abhängigkeiten auf acht Partitionen erreicht. Zusätzlich ermöglicht dies deutliche Erhöhungen der Taktfrequenz eines Hardwaredekoders, da die spezialisierten Teildekoder für die verschiedenen Partitionen weitaus weniger verschiedene Syntaxelemente bearbeiten müssen. Die reduzierte Komplexität der Teildekoder erlaubt außerdem drastische Hardwareeinsparungen, vor allem im Vergleich zu Techniken wie WPP, die eine vollständige Replikation des CABAC-Dekoders erfordern. Der vorgestellte Dekoder erlaubt eine Beschleunigung um bis zu  $8.5\times$  bei lediglich 61.9% zusätzlichen Hardwarekosten und einer Erhöhung der Bitrate um maximal 0.7% bei typischen Full-HD-Videos.

Außerdem stellen wir einen Cache-basierten CABAC-Dekoder vor. Dieser ersetzt den Context-Model-Speicher durch einen kleineren Cache und ermöglicht somit den Betrieb mit höheren Taktfrequenzen, da der Speicherzugriff den kritischen Pfad beeinflusst. Die auftretenden Fehlzugriffe auf den Cache werden mit einem optimierten Speicherlayout und einem adaptiven Vorhersagealgorithmus effektiv reduziert. Die Untersuchung verschiedener Cache-Architekturen zeigt, dass ein  $2\times 8$  Context-Model-Cache die beste Leistung liefert. Durch die Erhöhung der Taktfrequenz um 17% und eine Fehlzugriffsrate von maximal 2% kann der Durchsatz des Dekoders um bis zu 16.7% erhöht werden.

Die letzte vorgestellte Optimierung behandelt die Software-CABAC-Dekodierung. Der Algorithmus beinhaltet viele schwer vorhersagbare Verzweigungen im Steuerfluss, was für aktuelle Prozessoren eine große Herausforderung darstellt und zu ineffizienten Implementierungen führt. Der Einsatz komplexer arithmetischer Instruktionen zur parallelen Dekodierung führt zu einer Beschleunigung bis zu  $2.04\times$ . Die Nutzung von zwei Bitstreampartitionen für verschiedene Arten von binären Symbolen ermöglicht es sogar, die Dekodierung einer davon ohne Rechenaufwand durchzuführen. Folglich ist eine noch höhere Beschleunigung bis zu  $2.45\times$  bei höchstens 0.2% höherer Bitrate möglich.

Abschließend sprechen wir Empfehlungen für die Entwicklung zukünftiger Videokompressionsstandards und Computerarchitekturen aus. Weitere Forschungsideen für Videokodierung im Allgemeinen und CABAC im Besonderen werden ebenfalls diskutiert. Die dieser Arbeit zugrunde liegende Forschung demonstriert bereits einige vielversprechende Ansätze, welche die Leistung von CABAC und damit des gesamten Dekoders deutlich erhöhen können. Durch die Behandlung dieser kritischen Komponente leisten wir einen wichtigen Beitrag zur Verbesserung vieler aktueller und zukünftiger Videoanwendungen.

## Acknowledgement

This thesis is the result of many years of hard work. It would not have been possible without the help of a couple of people.

First of all, I want to thank my supervisor Prof. Dr. Ben Juurlink for inspiring me as a student which led me to start a research career. I am also very grateful for his scientific guidance during my time as a research assistant in the Embedded Systems Architecture group at TU Berlin.

I also want to thank Dr. Mauricio Alvarez-Mesa and Chi Ching Chi for their support even after they left our group to found their own company. They brought me in touch with video coding which turned out to be a perfect match. Both are experts in this field and guided me to acquire high technical proficiency as well as a high-quality research methodology.

Thank you to all my colleagues in the Embedded Systems Architecture group. It was the nice working atmosphere and the mutual support that enabled our accomplishments and the persistence in our long-term goals. Special thanks go to Angela Pohl and Matthias Göbel with whom I have walked the long road towards a Ph.D. together from the beginning. We went through similar struggles and always supported each other. I am happy and proud that we all made it.

Last and most importantly I want to thank my parents Birgit and Heiko, and my brother Paul for their support during the stressful and frustrating phases while pursuing a Ph.D.. I want to thank my parents for raising me the way they did, for their unconditional love no matter how much I challenged them, and for supporting me in all the things I aspired in life. It is an insufferable loss that my mother unexpectedly passed away not even a year ago and will not be able to witness so many good things in life that she deserves, the completion of this thesis just being one of them. I dedicate this thesis to her to honor her life's work – our family – which made this accomplishment possible in the first place.

# Contents

| 1        | Inti           | oduct  | ion                                        | 1  |

|----------|----------------|--------|--------------------------------------------|----|

|          | 1.1            | Motiv  | ation                                      | 1  |

|          | 1.2            | Objec  | tives                                      | 3  |

|          | 1.3            | Contr  | ibutions                                   | 4  |

|          | 1.4            | Thesis | s Organization                             | 6  |

| <b>2</b> | Bac            | kgrou  | $\operatorname{nd}$                        | 9  |

|          | 2.1            | Video  | Coding                                     | 9  |

|          |                | 2.1.1  | High Efficiency Video Coding               | 10 |

|          |                | 2.1.2  | Other Video Coding Standards               | 15 |

|          |                | 2.1.3  | Parallelism in Video Coding                | 16 |

|          | 2.2            | Perfor | rmance Evaluation                          | 18 |

|          |                | 2.2.1  | Experimental Setup                         | 20 |

|          |                | 2.2.2  | Evaluation                                 | 22 |

|          |                | 2.2.3  | Conclusions and Recommendations            | 26 |

|          | 2.3            | Conte  | xt-based Adaptive Binary Arithmetic Coding | 27 |

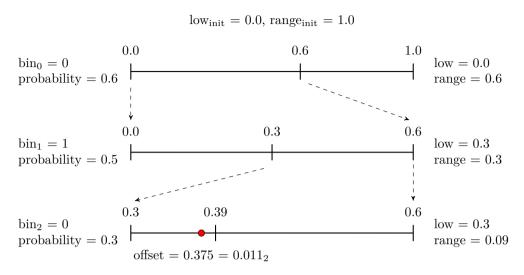

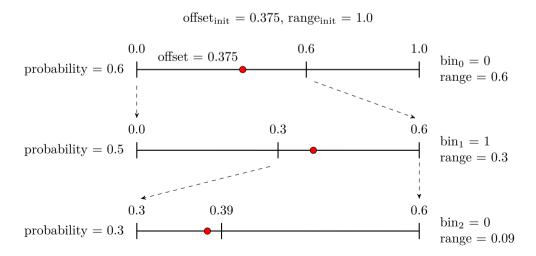

|          |                | 2.3.1  | Binary Arithmetic Coding                   | 27 |

|          |                | 2.3.2  | Context Modeling and Adaptation            | 30 |

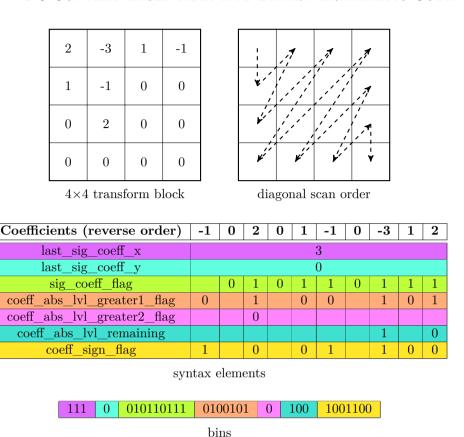

|          |                | 2.3.3  | Binarization                               | 31 |

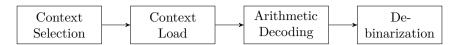

|          |                | 2.3.4  | HEVC CABAC                                 | 32 |

|          |                | 2.3.5  | Other Entropy Coding Methods               | 34 |

| 3        | $\mathbf{Rel}$ | ated V | Vork                                       | 37 |

|          | 3.1            | CTU-   | level Parallelism                          | 37 |

|          | 3.2            | Bin-le | vel Parallelism                            | 39 |

|          | 3.3            | Archit | tectural Optimizations                     | 41 |

|          |                | 3.3.1  | Pipelining                                 | 42 |

|          |                | 3.3.2  | Context Model Cache                        | 43 |

|          |                | 3.3.3  | Data Path Optimizations                    | 43 |

|          | 3.4            | Summ   | nary                                       | 44 |

| 4 | Wa                     | vefront Parallel Processing                 | 45  |

|---|------------------------|---------------------------------------------|-----|

|   | 4.1                    | Dependency Analysis                         | 46  |

|   | 4.2                    | Fine-grained WPP                            | 47  |

|   | 4.3                    | Evaluation                                  | 48  |

|   |                        | 4.3.1 Decoding Speedup                      | 48  |

|   |                        | 4.3.2 Parallel Efficiency                   | 50  |

|   | 4.4                    | Conclusions                                 | 51  |

| 5 | Bin                    | based Bitstream Partitioning                | 53  |

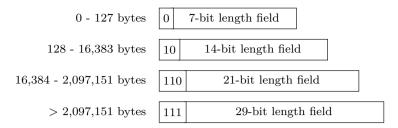

|   | 5.1                    | Bitstream Format                            | 54  |

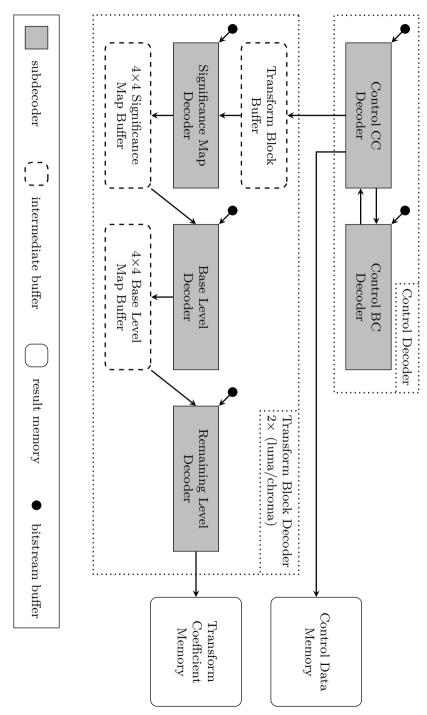

|   | 5.2                    | Parallel Decoder Architecture               | 57  |

|   |                        | 5.2.1 CC Bin Subdecoder                     | 59  |

|   |                        | 5.2.2 BC Bin Subdecoder                     | 59  |

|   |                        | 5.2.3 Improvements over Sequential Decoding | 61  |

|   |                        | 5.2.4 Design Challenges                     | 63  |

|   | 5.3                    | Evaluation                                  | 64  |

|   |                        | 5.3.1 Parallel Decoding Speedup             | 64  |

|   |                        | 5.3.2 Bitstream Overhead                    | 65  |

|   |                        | 5.3.3 Hardware Cost                         | 70  |

|   | 5.4                    | Conclusions                                 | 70  |

| 6 | Cor                    | text Model Cache and Prefetching            | 73  |

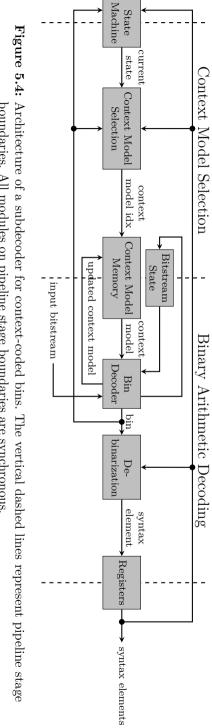

|   | 6.1                    | Decoder Architecture                        | 74  |

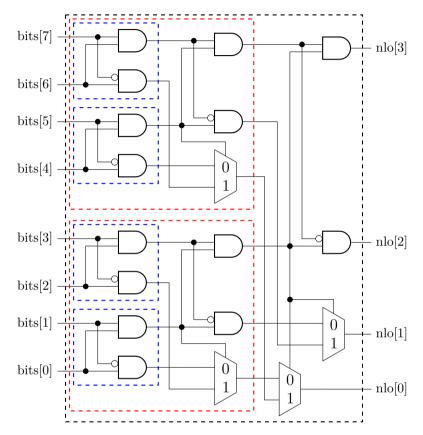

|   |                        | 6.1.1 Context Model Cache and Memory Layout | 74  |

|   |                        | 6.1.2 Adaptive Prefetching                  | 79  |

|   | 6.2                    | Evaluation                                  | 81  |

|   |                        | 6.2.1 Clock Frequency                       | 81  |

|   |                        | 6.2.2 Performance without Prefetching       | 82  |

|   |                        | 6.2.3 Performance with Prefetching          | 85  |

|   |                        | 6.2.4 Real-time Decoding                    | 89  |

|   |                        | 6.2.5 Resource Utilization                  | 91  |

|   |                        | 6.2.6 Energy Efficiency                     | 92  |

|   | 6.3                    | Conclusions                                 | 92  |

| 7 | $\mathbf{C}\mathbf{A}$ | BAC Decoding on GPPs                        | 95  |

|   | 7.1                    | HEVC BC Bin Decoding on GPPs                | 95  |

|   | 7.2                    | Parallel BC Bin Decoding                    | 97  |

|   |                        | 7.2.1 Bypass-Bin Reservoir                  | 98  |

|   |                        | 7.2.2 Division by Inverse Multiplication    | 99  |

|   |                        | 7.2.3 Bitstream Partitioning                | 100 |

|   | 7.3                    | Evaluation                                  | 101 |

|   | 74                     | Conclusions                                 | 102 |

| 8  | Cor    | nclusions                       | 105 |

|----|--------|---------------------------------|-----|

|    | 8.1    | Summary                         | 105 |

|    | 8.2    | Recommendations and Future Work | 108 |

| Li | st of  | Figures                         | 112 |

| Li | st of  | Tables                          | 113 |

| Li | st of  | Listings                        | 115 |

| Li | st of  | Abbreviations                   | 117 |

| Bi | ibliog | graphy                          | 119 |

|    | Pub    | lications                       | 119 |

|    | Star   | ndards, Software, Testsets      | 119 |

|    | Vide   | eo Coding                       | 121 |

|    |        | ropy Coding                     |     |

|    |        | cellaneous                      |     |

# $_{ ext{CHAPTER}}$ 1

## Introduction

Video is widespread in many applications on a variety of computing systems. The emergence of video-on-demand services, IP television, video chatting and conferencing, and others has pervaded many types of digital systems. 75% of all internet traffic has been video data in 2017 according to the Cisco Visual Networking Index and it is predicted to increase up to 82% in 2022 [76]. Video coding standards define a format to represent video data efficiently, such that its storage and transmission over a network becomes feasible. Only five minutes of raw video data can be stored on a 50 GB dual-layer Blu-ray disc when Full High Definition resolution (FHD, 1920×1080 samples), 50 frames per second and a basic color format are used. This is reduced to a few seconds with higher resolutions and color depths. Consequently, video compression becomes inevitable to realize all kinds of entertainment applications. The ever increasing demand for higher video resolutions (4K/8K) and higher quality levels makes video compression a very important research field now and in the future.

#### 1.1 Motivation

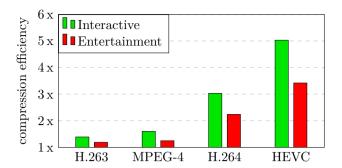

Video coding standards have evolved in the last decades and constantly improved their compression efficiency (see Figure 1.1). High Efficiency Video Coding (HEVC/H.265 [8] [9]) is the latest video coding standard developed by the Joint Collaborative Team on Video Coding (JCT-VC). It provides a 50% decrease in bitrate compared to its predecessor H.264/AVC [14] at the same subjective quality [26]. The potential for another 40% bitrate reduction for HEVC's in-development successor Versatile Video Coding (VVC [17]) was confirmed after the Joint Video Exploration Team studied the performance of new coding tools [36]. Modern video codecs provide compression rates between  $100\times$  and  $1,000\times$  without a noticeable difference in subjective quality compared to the uncompressed video. This is mainly achieved by sophisticated algorithms that remove spatial and temporal redundancies in similar frame areas. It is also exploited that the human visual system is insensitive to specific information, which can be removed without affecting the perceived quality. However, these algorithms have a very high computational complexity and push even modern high-performance computer architectures to their limits. Video coding applications and computer architectures

Figure 1.1: Average improvement in compression efficiency for interactive and entertainment applications of previous video coding standards compared to MPEG-2. Results derived from [26].

have mutually influenced each other during the last decades. Modern video compression standards such as HEVC employ multiple high-level parallelization tools to exploit the capabilities of today's multi- and many-core architectures. It is inevitable to make use of these thread-level parallelism (TLP) opportunities to implement high-performance and energy-efficient video applications. Furthermore, many video compression algorithms are designed to allow high-throughput processing by relaxing some data and control dependencies even though this might introduce small losses in compression efficiency. On the other hand, modern general-purpose processors (GPPs) provide wide vector extensions to efficiently process the massive amount of data-level parallelism (DLP) that can be found in video processing applications. Modern GPPs show real-time decoding capabilities for high-quality 4K video material, however, with poor energy efficiency. Therefore, dedicated video encoding and decoding hardware is used in many computing systems, especially mobile devices, to drastically reduce their energy consumption. These mobile devices heavily rely on maximized energy and compression efficiency while real-time performance is a minimum requirement.

One component in HEVC and also in other video compression standards is often a throughput bottleneck, especially for high-quality videos: context-based adaptive binary arithmetic coding (CABAC [44]). The CABAC decoder extracts syntax elements from the compressed bitstream and controls all other decoder modules with this information. It implements a strictly sequential algorithm with close-distance data and control dependencies which makes optimizations very challenging. In contrast to all prediction, transform and filtering modules in HEVC, it does not contain any DLP. As a result, CABAC can neither benefit from the vector extensions of modern GPPs nor from vectorization approaches in customized hardware. This strictly limits the overall speedup that can be achieved with vectorization. Amdahl's Law suggests that the maximum application speedup is determined by the non-parallelizable fraction [77]. CABAC decoding can easily account for 20% to 40% of the runtime for high-quality videos in a non-vectorized decoder, in extreme cases even more than 80%. Consequently, the overall vectorization speedup is limited to  $5\times$ ,  $2.5\times$  and  $1.25\times$  respectively, although much higher improvements can be reached for the other components.

The performance of video decoding is more critical than video encoding in most applications. Especially in video-on-demand services, playback from Blu-ray discs, etc., a video needs to be encoded only a few times while decoding can easily be done billions of times. The performance of the encoding process does not matter too much as it can be done offline. On the other hand, real-time performance is essential on the decoder side and energy efficiency is also of utmost importance considering that the number of mobile devices used for video playback is rapidly increasing. Applications with realtime encoding requirements, such as digital cameras and video communication, can always aim for a lower compression rate to reduce the performance requirements. This tradeoff makes insufficient encoder performance less critical than at the decoder side. Furthermore, the inefficient compression increases the workload for the decoder. As a matter of fact, the efficient implementation of CABAC is more challenging in the decoder in general as the currently decoded syntax element determines which one needs to be decoded next. Compared to that, the next syntax elements are always known in the CABAC encoder which allows more efficient pipelining strategies. This thesis is focused on addressing the critical CABAC decoding throughput bottleneck that limits the performance of many video applications.

## 1.2 Objectives

In this thesis, we develop and evaluate different optimization strategies for HEVC CABAC decoding. We also propose modifications in the HEVC standard that allow more efficient CABAC decoding in future video coding standards.

#### Objective 1: Identify main performance bottlenecks in video decoding.

The performance of the overall video decoder determines the quality of experience in video-based applications. Therefore, an analysis of the work distribution between the different decoder modules is essential to identify bottlenecks that need to be addressed. Video coding applications are especially challenging in this regard as the work distribution highly depends on the video content, characteristics and quality.

Objective 2: Improve the performance and efficiency of CABAC decoding. Based on the results of *Objective 1*, CABAC decoding has been identified as the main performance bottleneck for high-quality video decoding. Consequently, we will focus on optimizing CABAC decoding as high-quality video decoding is most challenging for modern computer architectures. We aim at implementing the existing HEVC CABAC algorithm as efficiently as possible on a variety of today's computing systems.

Objective 3: Enable new parallelization opportunities in CABAC decoding. CABAC decoding implements a sequential arithmetic coding algorithm which, unlike all other major decoder modules, does not allow the use of DLP techniques for performance improvement. While modern computer architectures – especially graphics

#### 1 Introduction

4

processing units (GPUs) and GPPs – constantly improve their support for exploiting DLP, CABAC is the only module in state-of-the-art video codecs that does not benefit from this development. Finding alternative parallelization opportunities is essential to compensate for the lack of DLP. Modifications in the HEVC standard might be necessary to achieve this goal. Therefore, the developed techniques can be seen as proposals for future video coding standards.

By addressing the CABAC decoding throughput bottleneck, the data-parallel capabilities of modern computer architectures become also more effective as the sequential fraction in the video decoding process is reduced.

#### 1.3 Contributions

The research conducted in this thesis is supposed to improve the performance and efficiency of modern video decoders in hardware and software implementations. Due to the versatility of video coding applications, we provide a comprehensive performance analysis of the HEVC decoder. The CABAC decoder is identified as the main performance bottleneck for high-quality videos in this analysis. Consequently, we develop and evaluate strategies to optimize the CABAC decoding process on different levels, e.g. frame, block and symbol level. Furthermore, we aim at enabling new parallelization opportunities for use in future video coding standards. The main contributions are as follows:

- We provide a quantitative performance evaluation of the HEVC software decoder. Therefore, we employ multiple processors to represent a wide range of computing devices, from smartphones to high-performance desktop computers. We also use testsets that are typical for different video coding applications and evaluate them in a broad range of quality levels. Based on this analysis, the main decoder bottlenecks and architectural limitations can be identified. We further provide recommendations for future video coding standards and computer architectures to better match the capabilities and requirements of each other.

- Wavefront Parallel Processing (WPP) is an established tool to exploit intra-frame parallelism by processing consecutive rows of pixel blocks, however, it suffers from parallel inefficiencies. When analyzing the dependencies that lead to the common horizontal offset between consecutive rows, it can be found that they are most relaxed for CABAC. To exploit that, we propose three methods that improve the parallel efficiency of WPP for CABAC decoding when it is decoupled from the reconstruction process. The methods differ in the granularity at which dependency checks are performed.

- We propose a modified bitstream format for future video coding standards that enables additional parallelization opportunities and substantial speedups for CABAC decoding. A common HEVC bitstream is divided into eight partitions that can be

processed simultaneously with few dependencies. The fixed partitioning scheme works best for high-quality videos when CABAC throughput is most critical. Furthermore, the bitstream overhead and hardware cost are much smaller than with the existing high-level parallelization tools in HEVC.

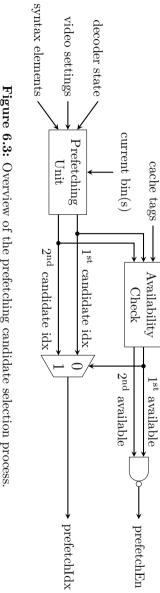

- Architectural improvements for CABAC hardware decoding result in higher achievable clock frequencies and consequently higher throughput. We present a context model cache architecture with an application-specific memory layout. An adaptive prefetching algorithm is used to reduce the miss rate to a negligible level. The use of this cache architecture leads to improvements in performance and energy efficiency with low hardware overhead.

- Although many devices have dedicated video coding hardware, software is often

used as a fallback solution, e.g. when advanced video features are used. We present

an improved technique for parallel bypass-bin decoding on GPPs. Although it

is based on simple integer arithmetic, common CABAC decoding is inefficient

on GPPs due to frequent hardly predictable branches. We achieve substantial

decoding speedups by replacing such code by a branch-free version based on more

complex arithmetic instructions.

The contributions of this thesis are based on previous works that have been published as follows:

- 1. P. Habermann, "Design and Implementation of a High-Throughput CABAC Hardware Accelerator for the HEVC Decoder, Lecture Notes in Informatics Seminars, Informatiktage 2014, pp. 213-216, Potsdam, Germany, March 2014

- P. Habermann, C. C. Chi, M. Alvarez-Mesa and B. Juurlink, "Optimizing HEVC CABAC Decoding with a Context Model Cache and Application-specific Prefetching", Proceedings of the 11th IEEE International Symposium on Multimedia (ISM 2015), pp. 429-434, Miami, FL, USA, December 2015, Best Student Paper Award

- 3. P. Habermann, C. C. Chi, M. Alvarez-Mesa and B. Juurlink, "Application-Specific Cache and Prefetching for HEVC CABAC Decoding", IEEE Multimedia, volume 24, issue 1, pp. 72-85, January 2017

- 4. **P. Habermann**, C. C. Chi, M. Alvarez-Mesa and B. Juurlink, "Syntax Element Partitioning for high-throughput HEVC CABAC Decoding", Proceedings of the 42nd IEEE International Conference on Acoustics, Speech and Signal Processing (ICASSP 2017), pp. 1308-1312, New Orleans, LA, USA, March 2017

- P. Habermann, C. C. Chi, M. Alvarez-Mesa and B. Juurlink, "Improved Wave-front Parallel Processing for HEVC Decoding", Proceedings of the 13th International Summer School on Advanced Computer Architecture and Compilation for High-Performance and Embedded Systems (ACACES 2017), pp. 253-256, Fiuggi, Italy, July 2017

- P. Habermann, C. C. Chi, M. Alvarez-Mesa and B. Juurlink, "A Bin-Based Bitstream Partitioning Approach for Parallel CABAC Decoding in Next Generation Video Coding", Proceedings of the 33rd IEEE International Parallel and Distributed Processing Symposium (IPDPS 2019), pp. 1053-1062, Rio de Janeiro, Brazil, May 2019

- 7. **P. Habermann**, C. C. Chi, M. Alvarez-Mesa and B. Juurlink, "Efficient Wavefront Parallel Processing for HEVC CABAC Decoding", Proceedings of the 28th Euromicro International Conference on Parallel, Distributed and Network-based Processing (PDP 2020), pp. 339-343, Västerås, Sweden, March 2020

The author of this thesis developed the research ideas of all publications. He performed the implementation work, designed and executed the evaluations, and wrote the papers. The co-authors assisted in technical discussions, by providing software that was used as a starting point for the implementation (publications 1-3), and by performing reviews.

## 1.4 Thesis Organization

Chapter 2 provides a brief overview of the fundamentals of video coding with a focus on the HEVC standard. We also present the results of the conducted performance evaluation to identify the main throughput bottlenecks in the HEVC decoder. Finally, we provide a more detailed description of CABAC as it is the main decoder module covered in this thesis. Related work is discussed in Chapter 3. The analysis of existing work is divided into multiple parts that cover parallelization approaches on different levels, as well as architectural optimizations. Based on the results of the analysis we propose multiple optimizations which are covered in the following chapters.

Three WPP implementations for CABAC decoding are presented in Chapter 4. They perform more fine-grained dependency checks and improve the parallel efficiency compared to conventional WPP. The proposed techniques yield best results for low-delay applications which also benefit the most from the improved parallel efficiency within a frame. Afterwards, we propose a bitstream partitioning approach in Chapter 5 that enables additional parallelism and significantly improves the performance of CABAC decoding for future video coding standards. At the same time, the hardware cost and bitstream overhead are substantially smaller than for the HEVC high-level parallelization approaches because these metrics have been specifically targeted in the design process of the bitstream partitioning scheme. Chapter 6 shows architectural enhancements with an application-specific context model cache architecture, the corresponding adaptive prefetching algorithm, and an optimized context model memory layout. A design space exploration has been performed to find the best cache configuration in terms of performance, energy efficiency and hardware cost. Different techniques for improved CABAC decoding on GPPs are presented in Chapter 7. The replacement of frequent hardly predictable branches by more complex but branch-free arithmetic instructions leads to substantial speedups when exploiting the bypass-bin grouping in HEVC.

Finally, the thesis is concluded and promising future work is discussed in Chapter 8. We also provide recommendations for developers of video compression standards and computer architectures based on the findings in this thesis.

# $_{\scriptscriptstyle ext{CHAPTER}}2$

## Background

This chapter provides the background information to which we will refer in the thesis. Section 2.1 covers information about video coding, especially the HEVC standard. Furthermore, the results of a performance analysis of the HEVC decoder are presented in Section 2.2 to quantitatively motivate the need for further optimizations in CABAC decoding. Finally, a more detailed description of HEVC CABAC is provided in Section 2.3 as it is the main topic of this thesis.

## 2.1 Video Coding

Most modern video coding standards employ a hybrid approach with prediction techniques and a transformed residual signal. Intra- and inter-picture prediction are used to remove spatial and temporal redundancies in similar frame areas. As these predictions do not yield perfect results, a transformed and quantized version of the difference between the real frame area and its prediction is also transmitted. In this way, video data can be reconstructed based on previously decoded information. The post-processing with image filters and the compression of the prediction and residual information with an entropy coding method complete the majority of state-of-the-art video coding standards.

Sampling is applied to videos to transform them into a time-discrete fixed spatial resolution. The time-discrete sampling determines the number of frames per second (fps) a video consists of. 20 to 60 fps are typically used in most applications to allow smooth transitions between frames. The spatial resolution determines the amount of details that can be observed in video data. Full High Definition (FHD,  $1920 \times 1080$  samples) is a widespread resolution that is used in many entertainment applications. Table 2.1 shows more video resolutions that are typically used.

Video data is commonly represented in the YCbCr color scheme. It consists of luminance information (luma, Y) and two chrominance (chroma) components that represent the deviation from gray towards blue (Cb) and red (Cr). This decorrelation of the color components is beneficial for the compression efficiency. Furthermore, chroma subsampling is often applied to reduce the amount of required data, exploiting that the human visual system is more sensitive to luminance than to chrominance. Only one Cb and

| 4    | :3        | 16    | 6:9       | 17:9 |                    |  |

|------|-----------|-------|-----------|------|--------------------|--|

| VGA  | 640×480   | HD    | 1280×720  |      |                    |  |

| SVGA | 800×600   | FHD   | 1920×1080 | 2K   | 2048×1080          |  |

| UXGA | 1600×1200 | UHD-1 | 3840×2160 | 4K   | $4096 \times 2160$ |  |

| QXGA | 2048×1536 | UHD-2 | 7680×4320 | 8K   | 8192×4320          |  |

**Table 2.1:** Common video resolutions for different aspect ratios (4:3, 16:9, 17:9).

**Table 2.2:** Chroma subsampling modes with chroma resolutions relative to an  $N \times N$  luma block.

| Mode                             | 4:2:0                            | 4:4:4                   | 4:2:2                  | 4:0:0 |

|----------------------------------|----------------------------------|-------------------------|------------------------|-------|

| Chroma resolution                | $\frac{N}{2} \times \frac{N}{2}$ | $N \times N$            | $N \sim N$             |       |

| $({ m width} 	imes { m height})$ | ${2} \times {2}$                 | 1 <b>V</b> × 1 <b>V</b> | $\frac{1}{2} \times N$ | _     |

Cr sample are used together with a block of 2×2 Y samples in the most common 4:2:0 mode, which is equivalent to half the horizontal and vertical resolution for Cb and Cr compared to Y. A list of common chroma subsampling modes can be seen in Table 2.2.

#### 2.1.1 High Efficiency Video Coding

The HEVC standard has been released in 2013. Since then, it has been updated to the current version of November 2019 [9]. Multiple extensions have been specified to extend its applicability to more areas, e.g. range extensions [11], scalable video coding [12], as well as multiview and 3D extensions [13]. The HEVC Test Model (HM [10]) is the corresponding reference software that provides an implementation of the encoder and decoder. The following description of the HEVC standard is based on the work of Sullivan et al. [8].

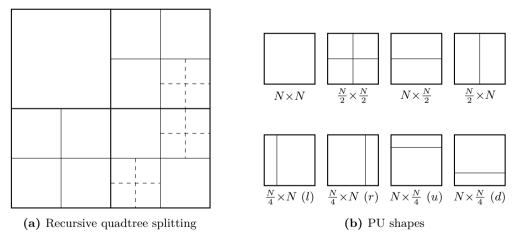

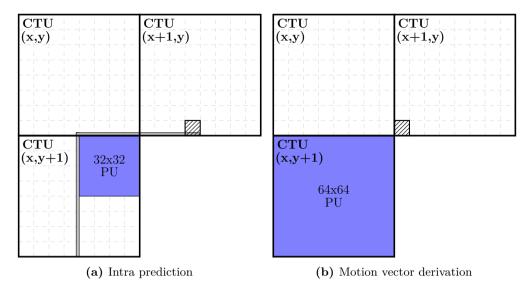

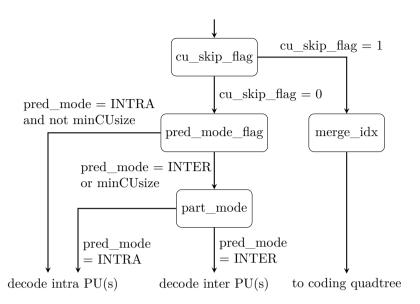

Each frame is divided into coding tree units (CTUs) in the HEVC standard (see Figure 2.1). CTUs are square blocks of  $64\times64$ ,  $32\times32$  or  $16\times16$  samples. The CTU size is fixed for a video and can be selected to allow the best compression efficiency ( $64\times64$ ) or lowest processing latency ( $16\times16$ ). A coding quadtree per CTU can recursively divide the area into square coding units (CUs) (see Figure 2.2a). The largest possible CU size is equal to the CTU size while the smallest size is  $8\times8$  samples. The decision about the prediction mode (intra- or inter-picture) is made on the CU level. Every CU is associated with one, two or four prediction units (PUs) and a (potentially empty) transform tree. The area of a CU can be divided into PUs with a variety of shapes (see Figure 2.2b) to better match the structure of the corresponding frame content and allow more efficient prediction. While only square shapes are available for intrapicture prediction, all shapes can be used for inter-picture prediction as long as the resulting PUs have at least a size of  $4\times8/8\times4$  samples. The transform tree represents the residual signal, i.e. the difference between the real block and the predicted block.

**Figure 2.1:** Partitioning of a frame into  $64 \times 64$  CTUs. (Cactus test sequence from JCT-VC common test conditions [23])

Figure 2.2: Block partitioning in HEVC.

The transform tree can also be recursively divided into square transform units (TUs) with a minimum size of  $4\times4$  samples. TUs consist of multiple transform blocks (TBs) for the color components Y, Cb and Cr.

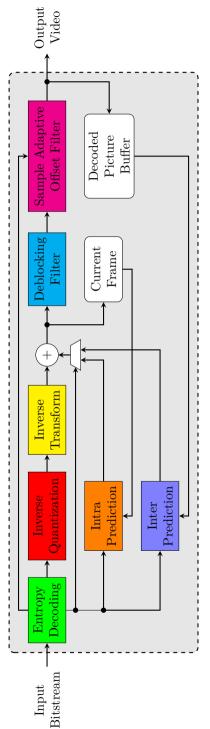

An overview of the most important modules in the HEVC decoder is presented in Figure 2.3. First, the entropy coding module extracts syntax elements – a non-sample-based representation of a frame – from the compressed input bitstream. HEVC uses CABAC as the only entropy coding method. The extracted syntax elements are then used to control other decoding steps, such as prediction and filters. Intra prediction exploits spatial similarities of neighboring blocks within a frame to remove redundant data and decrease the required data rate. Inter prediction targets the same goal by exploiting temporal similarities of blocks in consecutive frames. In the encoder, the residual is transformed to the frequency domain and quantized before compression. Inverse quantization and inverse transforms are applied to the transform coefficient syntax elements in the decoder to restore the residual data which is added to the predicted block before filters are applied. The deblocking filter (DBF) is used to reduce compression artifacts that arise due to the block-wise processing of video data. Afterwards, the sample adaptive offset (SAO) filter reduces sample distortion by adding specific offsets to different sample categories. The main components are described in more detail in the following.

CABAC is the only entropy coding method in HEVC. It employs binary arithmetic coding which is known to provide high compression performance at high computational complexity. Context modeling is used to compress binary symbols (bins) efficiently and to enable an adaptive entropy coding method that can work well with very different video characteristics. A more detailed description of CABAC will be provided in Section 2.3.4 as it is the main decoder component discussed in this thesis.

Intra Prediction predicts the signal of a block based on the adjacent pixels in the top-left, top, top-right, left and bottom-left blocks. It is predominantly used to exploit spatial similarities in regular structures and homogeneous regions in a frame. HEVC intra prediction supports a DC mode, a planar mode, and 33 directional modes for prediction. Neighboring samples are extrapolated in the respective prediction direction when a directional mode is used. The DC mode fills the whole predicted block with an average value of all neighboring samples. The planar mode creates a gradient that provides a smooth transition from the adjacent samples to the predicted area. Intra prediction is performed on  $4\times4$ ,  $8\times8$ ,  $16\times16$  or  $32\times32$  blocks.

Inter Prediction exploits temporal similarities in different frames to predict a block of samples from previously decoded frames. This method is particularly effective as consecutive frames in a video are most often very similar. As a result, inter prediction is one of the most important techniques being responsible for the very high compression rates in modern video compression standards. A motion vector is signaled to indicate the location of the reference block in a previous frame compared to the predicted block. Motion vectors compensate for the movement of objects or the camera in consecutive frames. Further information is coded to identify the reference frame that should be used. An eight-tap interpolation filter is used for luma inter prediction (four-tap for chroma) to achieve quarter-pixel (eighth-pixel for chroma) accuracy. Bi-prediction is used to perform a weighted interpolation between two different reference frames.

Figure 2.3: Block diagram of the HEVC decoder.

**Inverse Quantization** is applied to undo the quantization in the encoder. The quantization process divides the transformed residual signal by a specific value to reduce the amount of data that has to be coded. There are losses in precision when undoing the quantization step due to the use of integer arithmetic. The quantization parameter (QP) determines the extent of data loss.

Inverse Transform is performed after the inverse quantization process. Discrete cosine transforms and discrete sine transforms are applied to the residual signal in the encoder to transform it into the frequency domain. As the human visual system is less sensitive to specific parts of the frequency spectrum, they can be removed without affecting the noticeable quality. The inverse process is performed in the decoder to restore the initial residual signal, however, it might be inaccurate due to the quantization that was performed in between. HEVC specifies  $4\times4$ ,  $8\times8$ ,  $16\times16$  and  $32\times32$  discrete cosine transforms and a  $4\times4$  discrete sine transform.

The **DBF** is applied after the residual signal was added to the predicted block. The main purpose of the filter is the reduction of artifacts that arise due to the block-based coding. The DBF is only applied to PU and TU boundaries on an 8×8 grid. Different filter strengths are used. The strongest is applied if at least one of the involved blocks is intra-predicted. A weak filter is applied when either of the blocks has non-zero transform coefficients or when the inter prediction data differs from each other.

The SAO Filter is the final step in the decoder pipeline. It can enhance the video quality in smooth areas and around edges by providing two modes that conditionally manipulate all samples based on parameters that are encoded in the compressed bitstream. The band offset mode adds specific offsets to all samples whose values are within a specific range while the edge offset mode manipulates samples if their horizontal, vertical or diagonal neighbors fulfill certain requirements that make the samples local minima/maxima or edge samples.

The work distribution among the described decoder modules depends on the frame content and especially on the video quality. The QP is the most important parameter to determine the quality of the residual signal and, consequently, also the quality of the reconstructed video. Lower QPs result in higher video quality and higher bitrates. Typical QPs for low quality are 32 and 37, while 22 and 27 are used for high-quality videos. QPs of 12 and 17 are used for very high video quality in special applications.

Different modes are commonly used in video coding. All-intra (AI) does not use inter prediction, thereby removing dependencies between frames at the cost of much higher bitrates. Random-access (RA) makes use of the effective inter prediction for better compression efficiency. Intra frames are typically used every second to provide access points. This is the common mode for most applications. Low-delay (LD) makes use of inter prediction but limits the maximum decoding delay by restricting the available reference frames.

#### 2.1.2 Other Video Coding Standards

HEVC is by far not the only existing video coding standard. In this section, we will briefly describe the main differences to HEVC's predecessor H.264 and its in-development successor VVC. We further provide an overview of the emerging AV1 standard.

H.264/AVC [14] [15] was released in 2003 and has been the widely established standard before the introduction of HEVC. It requires about twice the bitrate as HEVC for compressing videos at the same subjective quality. A major reason for that is HEVC's support of 64×64 CTUs. This allows a much more efficient compression than with the 16×16 macroblocks in H.264. Furthermore, HEVC intra prediction supports 33 instead of eight directional modes in H.264, thereby allowing a much more fine-grained directional prediction. The inter prediction interpolation precision was improved with seven- and eight-tap filters compared to a six-tap filter in H.264. The H.264 DBF was applied on a 4×4 grid. The simplified filter decision on an 8×8 block granularity in HEVC makes the filter easier to parallelize. The SAO filter did not exist at all in H.264. Finally, H.264 supported two entropy coding methods. In addition to CABAC, context-based adaptive variable length coding (CAVLC) could also be selected. It has a lower computational complexity but does not reach the coding efficiency of CABAC. Furthermore, the CABAC design has been significantly improved to allow higher throughput.

VVC [17] aims to reduce the bitrate by another 50% in comparison to HEVC. The Joint Video Experts Team (JVET) is currently supervising the development process and the release is planned for 2020. An important step in this direction is the increase of the CTU size to  $256 \times 256$  samples. The nesting of a multi-type tree into the coding quadtree allows a better mapping of coding blocks to objects in a frame by also allowing binary and ternary splits. The number of directional intra modes was increased from 33 to 65 for more fine-grained prediction. Transform sizes have been increased from  $32 \times 32$  up to  $128 \times 128$ . Another new feature is the introduction of the adaptive loop filter (ALF) which was also part of HEVC but was removed before its release. It applies a Wiener filter to minimize the mean square errors between original samples and reconstructed samples from SAO and thereby allows significant bitrate reductions at the same quality level. While the CABAC implementation is very similar as in HEVC, some refinements have been applied, e.g. adaptive context model initialization and multi-hypothesis probability estimation. The VVC Test Model [18] is the corresponding reference software.

AV1 (AOMedia Video 1, [19]) is an open-source video coding standard developed by the Alliance for Open Media. It has been released in 2018 [20] and succeeds Google's VP9 standard [21] [22]. Both aimed at providing a royalty-free alternative to H.264 and HEVC video coding standards and implement the same hybrid approach, however, there are many differences in the coding tools. AV1 specifies  $128 \times 128$  superblocks compared to the  $64 \times 64$  CTUs in HEVC. The partitioning of the coding quadtree is more flexible and allows smaller block sizes. 56 directional modes are available for intra prediction and an intra block copy allows to fully reuse previously decoded blocks in the same frame. Interesting techniques in AV1 inter prediction include overlapped block motion compensation, warped motion compensation, and advanced compound

prediction. Besides the DBF, a constrained directional enhancement filter is applied for deringing and one of two loop restoration filters can be used. AV1 supports frame super-resolution which offers coding gains at low bitrates by processing a frame at a lower resolution and upscaling it afterwards. AV1 employs a multi-symbol entropy coding scheme compared to the binary arithmetic coder in HEVC. 15-bit precision is used for the probabilities of all potential symbols to enable improved accuracy, especially for infrequent symbols.

A comparison of the coding efficiency of HEVC, H.264 and AV1 has been provided by Grois et al. [37]. They found 32.8% and 38.4% bitrate reductions of HEVC compared to H.264 and AV1 respectively. The results have been partly confirmed by Laude et al. [38] who measured the same bitrate increase of AV1 compared to HEVC. Furthermore, they have shown an average 27.7% and 44.6% bitrate reduction in the RA configuration of VVC over HEVC and AV1 respectively. They also found a  $9.7\times$  and  $32.6\times$  increase in encoding time of VVC and AV1 over HEVC. This might limit the applicability of the new standards in applications with timing constraints or lead to performance reductions due to necessary tradeoffs between runtime and coding efficiency. In general, the performance comparison between different video codecs is a challenging task. The results vary significantly depending on the encoder configuration, the evaluated metrics (objective/subjective) and especially the employed testsets. An established metric for the comparison of the compression performance of different encoders at the same objective quality is described in [40].

#### 2.1.3 Parallelism in Video Coding

Video coding applications contain a massive amount of parallelism on different levels. High-quality real-time video applications can only be efficiently implemented by exploiting these parallelization opportunities.

Frame-level Parallelism refers to the simultaneous processing of multiple frames. This is generally possible in HEVC as every frame is coded in a separate slice, however, some inter-frame dependencies need to be considered. Slices are data structures that allow independent processing of the corresponding frames or frame areas. A frame consists of at least one slice and can contain multiple slices, which also enables parallel processing within a frame. HEVC supports I-, P- and B-frames. I-frames use only intra-prediction and consequently do not depend on other frames. That is why they are mainly used as access points in a video. P-frames can be inter-predicted from previously decoded frames. B-frames can make use of bi-prediction to be reconstructed from two other frames. Both P- and B-frames can also use intra-prediction. The decision for the prediction mode is made at CU granularity.

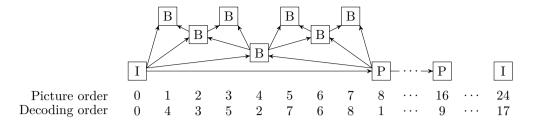

Figure 2.4 shows a typical structure of a group of pictures (GOP) and the dependencies between them. The dependencies and the resulting decoding order are chosen to make the best use of the effective bi-prediction. Every video sequence starts with an I-frame (index 0). Afterwards, a P-frame (index 8) can be predicted from the I-frame. The B-frame at index 4 can be decoded as soon as both the I- and the P-frame are decoded.

Figure 2.4: GOP structure with one I-frame every 24 frames.

The first frame-level parallelization opportunities within a group of nine frames arise when frames 2 and 6 can be decoded in parallel. After that, even four frames can be processed simultaneously (1, 3, 5, 7). In addition to the parallelism inside a group of nine frames, multiple of these groups can also be processed at the same time, i.e the I-frame at index 24 (and all other multiples of 24) in parallel with the I-frame at index 0, and the P-frame at index 16 in parallel with the B-frame at index 4. Overall, many frames can be processed in parallel, however, due to delay constraints and limitations in computational and memory resources, the number of parallel frames is very limited in practice.

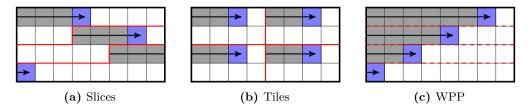

Block-level Parallelism refers to the parallel processing of multiple blocks within a frame. These are most commonly CTUs, however, the approach can also be applied to PUs, TUs, and even smaller blocks of samples, especially when performing operations for the different color components. Three high-level parallelization techniques for parallel CTU processing are specified in the HEVC standard: Slices [33], Tiles [34] and WPP [35]. A frame can consist of multiple slices whose corresponding areas can be processed independently (see Figure 2.5a). Slices contain a set of CTUs which are processed row by row. A frame can also be divided into rectangular tiles for independent parallel processing (see Figure 2.5b). The frame partitioning approaches prevent some prediction opportunities at tile boundaries and thereby reduce the compression efficiency. WPP allows the parallel processing of multiple rows of CTUs (see Figure 2.5c). The decoding of a CTU row can be started as soon as the second CTU in the above row has been processed because the CABAC context information needs to be forwarded. These dependencies lead to a wavefront-like progression of multiple threads over the frame. WPP can also lead to a reduced compression efficiency compared to sequential decoding as the CABAC learning process is interrupted. Furthermore, a ramp-up and -down in the number of active parallel threads limits the efficiency of WPP within a single frame, however, this problem becomes negligible as soon as multiple frames can be processed in parallel. Slices, Tiles and WPP depend on even load balancing for best parallel scalability. Unfortunately, the load is most often concentrated in specific frame areas. Differently-sized slices and tiles can adapt to the load-intensive areas and reach a better work distribution.

An analysis of the parallel scalability and efficiency of HEVC parallelization approaches has been provided by Chi et al. [30]. One of the main contributions of this work is a technique called Overlapped Wavefront (OWF) which extends WPP to multiple frames.

Figure 2.5: High-level parallelization tools in HEVC.

This three-dimensional parallelization approach substantially improves the scalability and efficiency of WPP.

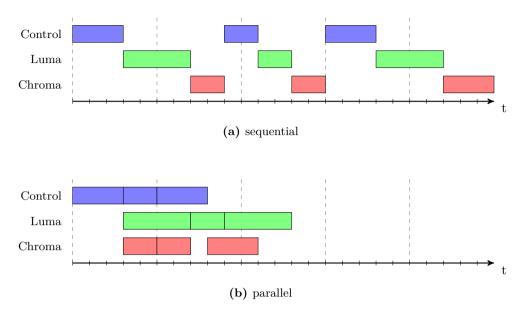

Task pipelining is also an effective technique at the CTU level. Instead of performing entropy decoding, inverse transform and quantization, prediction, and filtering for a CTU after each other before processing the next CTU, these steps can be pipelined. A single thread can perform the entropy decoding for CTU N. When the work is done, it can directly proceed with the entropy decoding for CTU N+1. At the same time, another thread can execute all inverse transform and quantization operations for CTU N while a third thread performs the prediction for CTU N-1 and a fourth thread executes the DBF and SAO filter for CTU N-2. Load balancing is also the main limiting factor for performance improvements, as with Slices, Tiles and WPP. Task pipelining can also be applied at the frame-level, however, it induces immense memory requirements as information for multiple frames needs to be stored for the next thread. This is also not optimal in terms of data locality.

Sample-level Parallelism can be found in all prediction, transform and filtering tasks in the HEVC decoder. The same operations are most often applied to all samples in a block. The vector extensions of modern processors can be used to process many of these samples in parallel and with reduced overhead for instruction fetch, decode, etc.. The same vectorization approaches can also be implemented in customized hardware. Vectorization is greatly responsible for the existence of high-performance and energy-efficient real-time video coding applications as it provides significant speedups up to  $5\times$  for the entire HEVC decoder [31]. This work by Chi et al. provides an overview of the vectorization techniques applied to all components of the HEVC decoder that contain significant DLP. The evaluation covers many different processors with a variety of vector extensions. It has also been shown that the improvements in energy-efficiency grow very similar to the speedup achieved by vectorization [32].

#### 2.2 Performance Evaluation

The HEVC decoder is a complex application consisting of multiple components (see Figure 2.3) that differ in their computational and memory requirements. The performance of the whole decoder is limited if only one component does not deliver the required throughput for real-time decoding. It is necessary to identify these bottlenecks and

address them with specific optimizations to improve the overall decoder performance in the most efficient way. Therefore, we perform an analysis of the HEVC software decoder providing useful general insights that also apply to hardware decoding as the same operations are possible in hardware, however, most often more efficiently. The resulting higher computational performance in dedicated hardware might bring new bottlenecks to light, especially limitations of the memory system. Nevertheless, this can also be mitigated with application-specific cache architectures or customized data layouts for improved data reuse.

An overview of complexity-related aspects in the HEVC standardization process has been provided by Bossen et al. [27] shortly before the publication of the standard in 2013. Although the main focus is a comparison to H.264, the performance results can be used as a reference. An optimized HEVC software decoder has been used for the evaluation that evolved from the one used in [29]. Intel SSE 4.1 and ARM Neon vector extensions are used to exploit the significant amount of DLP. The authors evaluated single-threaded decoding performance in RA mode with QPs of 27 and 32. An Intel Core i7-3720QM mobile CPU (central processing unit) can process all JCT-VC class B testsequences (1920×1080 samples) while an embedded 1 GHz ARM Cortex-A9 CPU can process all JCT-VC class C testsequences (832×480 samples) in real-time. The most time-consuming decoding tasks in this configuration are motion compensation (43%/49%), entropy decoding (24%/21%) and loop filters (21%/18%).

Ultra High Definition (UHD,  $3840 \times 2160$  samples) real-time decoding capabilities have been demonstrated by Bross et al. [28] using a 3.1 GHz eight-core server processor (Intel Xeon E5-2687W) and the Fraunhofer HHI HEVC software decoder in 2013. Although only achieved for lower quality levels, the general feasibility of UHD real-time decoding is shown.

Chi et al. provided a more exhaustive performance evaluation of a fully vectorized HEVC software decoder on multiple AMD, Intel and ARM processors in 2015 [31]. In addition to the existing evaluation by Bossen et al., the effect of multiple vector extensions is investigated. They demonstrate a substantial speedup due to the newer AVX2 vector extension which doubles the vector register size compared to SSE 4.1 and AVX. Further optimizations such as chroma interleaving have been applied to achieve a better utilization of the vector registers. Furthermore, UHD video material has been used for performance measurements as it is one of the emerging use cases of HEVC. The authors also used a wider spectrum of video quality levels (QP 24, 28, 32, 36). Multithreading has also been added to the evaluation. A WPP approach has been extended to multiple frames [30] to efficiently exploit TLP and get the most out of modern multi-core architectures. The evaluation shows that multithreaded real-time software decoding of 1080p videos is easily achievable for all architectures except an ARM Cortex-A9. Some of the more powerful processors can even decode 10-bit 2160p videos in real-time.

Real-time decoding capabilities have been demonstrated for many types of video coding applications since the introduction of HEVC. However, as computer architectures and video coding use cases have evolved in the last years, we provide an up-to-date evaluation. It is necessary to identify the main throughput bottlenecks so that the optimization

work leads to the largest speedup for the overall decoder. The main contributions compared to existing works are:

- An analysis of real-time decoding capabilities and performance bottlenecks that need to be addressed in future standards such as VVC.

- Multiple state-of-the-art processor architectures that represent different computing devices.

- A testset of commonly used video coding applications.

- Evaluation of the latest 512-bit vector extensions (AVX-512).

In the following, we describe the experimental setup and show performance and profiling results for different applications on a variety of processors. Furthermore, we draw main conclusions from the performance analysis.

#### 2.2.1 Experimental Setup

One of the main goals of the performance analysis is to provide an overview of the realtime decoding capabilities of modern GPPs for typical video coding applications. Four different platforms are used for evaluation to cover a wide range of computing systems. Each of the selected processors is representative of a class of devices: smartphones, mobile computers, desktop computers and high-performance desktop computers. An overview of the selected platforms can be seen in Table 2.3. The Kirin 970 is a commonly used smartphone processor that consists of four high-performance ARM Cortex-A73 cores and four low-power ARM Cortex-A53 cores. We further employ the Intel Core i7-8550U ultrabook CPU and the Intel Core i7-7700K desktop CPU for evaluation. Although all these three CPUs have four main processor cores, their performance is very different. The ultrabook processor and especially the smartphone processor are designed to be very energy-efficient. Therefore, they operate at a lower clock frequency and have a different cache architecture. Besides the smaller vector register size, the Kirin 970 also lacks simultaneous multithreading, i.e. the ability to execute two threads on the same core at the same time while sharing functional units. The high-performance desktop processor (Intel Core i9-7960X) has 16 cores which makes it much more powerful, even with the slightly reduced clock frequency. Furthermore, the doubled vector register width in comparison to the conventional desktop and ultrabook CPU is expected to allow a better exploitation of the available DLP in video coding applications. We use an optimized HEVC decoder developed by Spin Digital Video Technologies GmbH [78]. A previous version of it has already been used in [31]. We employ WPP with one thread per core for the smartphone processor and two threads per core for all others for the evaluation.

Video coding is used in very different fields and the corresponding applications have different requirements regarding video resolution, frame rate, color format and depth, quality and bitrate. In the following, we list six typical applications that will be used for the evaluation in this work.

Table 2.3: Architectural parameters of the evaluation platforms. I\$: instruction cache, D\$: data cache

|                                    | Smartphone                                         | Ultrabook                             | Desktop                               | HP Desktop                          |

|------------------------------------|----------------------------------------------------|---------------------------------------|---------------------------------------|-------------------------------------|

| Processor                          | HiSilicon Kirin 970                                | Intel Core i7-8550U                   | Intel Core i7-7700K                   | Intel Core i9-7960X                 |

| Cores                              | 4 Cortex-A73 + 4 Cortex-A53                        | 4                                     | 4                                     | 16                                  |

| Base Frequency                     | $2.36/1.80~\mathrm{GHz}$                           | 1.80 GHz                              | 4.20 GHz                              | $2.80~\mathrm{GHz}$                 |

| Turbo Frequency (all cores active) | n.a.                                               | 3.70 GHz                              | 4.40 GHz                              | $3.60~\mathrm{GHz}$                 |

| Simultaneous<br>Multithreading     | ×                                                  | `                                     | `                                     | `                                   |

| Vector<br>Extension                | Neon (128 bit)                                     | AVX2 (256 bit)                        | AVX2 (256 bit)                        | AVX-512 (512 bit)                   |

| $\mathbf{R}\mathbf{A}\mathbf{M}$   | 6 GB                                               | 16 GB                                 | 32 GB                                 | 64 GB                               |

| Cache (per core)                   | 64 KiB L1 I\$/D\$ (A73)<br>32 KiB L1 I\$/D\$ (A53) | 32 KiB L1 I\$/D\$<br>256 KiB L2 Cache | 32 KiB L1 I\$/D\$<br>256 KiB L2 Cache | 32 KiB L1 I\$/D\$<br>1 MiB L2 Cache |

| Cache (shared)                     | 2/1  MiB L2 Cache $(A73/A53)$                      | 8 MiB L3 Cache                        | 8 MiB L3 Cache                        | 22 MiB L3 Cache                     |

|                     | Video Class                             | #Videos | Mode | $\mathbf{QPs}$ | $rac{ m Bitrate}{ m (MBit/s)}$ |

|---------------------|-----------------------------------------|---------|------|----------------|---------------------------------|

| Low-delay           | Common testset<br>Class E               | 3       | LD   | 22, 27, 32, 37 | 0.1 - 0.4<br>0.4 - 2.2          |

| Screen content      | Range Extensions<br>YCbCr 444 SC        | 6       | RA   | 22, 27, 32, 37 | 0.2 - 1.8<br>0.5 - 6.6          |

| Animation           | Range Extensions<br>YCbCr 444 Animation | 3       | RA   | 22, 27, 32, 37 | 0.3 - 1.9<br>1.8 - 7.3          |

| FHD<br>playback     | Common testset<br>Class B               | 5       | RA   | 22, 27, 32, 37 | 0.4 - 2.4<br>1.7 - 33.1         |

| Video<br>production | Range Extensions<br>RGB 444             | 8       | AI   | 12, 17, 22, 27 | 27.9 - 548.1<br>74.0 - 1117.1   |

| UHD<br>playback     | EBU UHD-1                               | 4       | RA   | 12, 17, 22, 27 | 5.1 - 87.1<br>135.9 - 793.6     |

**Table 2.4:** Video coding applications. Separate bitrate ranges are shown for the lower and higher quality levels.

- Low-delay applications, e.g. video conferencing and video chatting in LD mode.

- Screen content, e.g. presentation slides and web browsing videos.

- **Animation** as found in animated movies.

- FHD playback of videos that are streamed over the internet or stored on media such as DVDs.

- Video production in AI mode with high quality and color depth.

- UHD playback of videos as in FHD playblack, but typically at higher quality levels.

An overview of the testsets is provided in Table 2.4. More details about the testsets can be found in [23] [24] [25]. We use the same modules as seen in Figure 2.3 for the profiling of the video decoder components, however, there are two exceptions. First, inverse quantization is merged with inverse transform (IQ/IT) because they are often processed together. Second, there is a category for remaining tasks that do not belong to any of the existing categories, e.g. writing reconstructed frames to memory (Others).

#### 2.2.2 Evaluation

Table 2.5 shows the real-time decoding capabilities of all platforms for the selected testsets. We use the average decoding performance for evaluation. However, it should be noted that the complexity of different frames can vary significantly. Consequently, higher performance might be necessary for judder-free playback. All platforms deliver sufficient performance for the basic low-delay, screen content, animation and FHD applications. On the other hand, only the HP desktop can process the high-bitrate video production testset as well as the high-resolution UHD testset in real-time. In the

**Table 2.5:** Performance overview showing the worst-case performance of any video of the corresponding testset compared to the required real-time performance.

|                  | Smart-<br>phone | Ultra-<br>book | Desktop | HP<br>Desktop  |

|------------------|-----------------|----------------|---------|----------------|

| Low-delay        | $5.35 \times$   | 11.75×         | 23.93×  | $22.45 \times$ |

| Screen content   | 2.40×           | $10.47 \times$ | 18.50×  | $30.49 \times$ |

| Animation        | 1.96×           | 6.11×          | 12.23×  | 23.51×         |

| FHD playback     | 1.22×           | $2.67 \times$  | 5.15×   | 11.76×         |

| Video production | 0.15×           | 0.24×          | 0.49×   | 1.30×          |

| UHD playback     | 0.12×           | 0.22×          | 0.31×   | 1.12×          |

Table 2.6: Detailed performance results of selected testsets in fps.

| a) Smartphone<br>FHD (1920×1080), RA | QP22   | QP27   | QP32   | QP37   |

|--------------------------------------|--------|--------|--------|--------|

| BasketballDrive 50 fps               | 96.14  | 121.60 | 142.87 | 157.18 |

| BQTerrace 60 fps                     | 73.45  | 132.05 | 156.68 | 169.36 |

| Cactus 50 fps                        | 100.09 | 135.74 | 153.75 | 162.87 |

| Kimono1 24 fps                       | 107.83 | 126.02 | 140.00 | 157.18 |

| ParkScene 24 fps                     | 95.03  | 121.31 | 138.63 | 160.14 |

| b) HP Desktop<br>Video Prod. $(1920 \times 1080)^*$ , AI | QP12   | QP17   | QP22   | QP27   |

|----------------------------------------------------------|--------|--------|--------|--------|

| DucksAndLegs 30 fps                                      | 89.20  | 93.60  | 101.22 | 124.43 |

| EBULupoCandlelight 50 fps                                | 108.56 | 184.28 | 349.50 | 538.31 |

| EBURainFruits 50 fps                                     | 114.18 | 175.58 | 254.40 | 362.29 |

| Kimono1 24 fps                                           | 79.49  | 105.46 | 202.58 | 368.25 |

| OldTownCross 50 fps                                      | 64.83  | 75.60  | 97.41  | 168.28 |

| ParkScene 24 fps                                         | 65.90  | 83.65  | 122.02 | 192.28 |

| <b>Traffic</b> 2560x1600, 30 fps                         | 46.27  | 61.36  | 84.39  | 123.66 |

| VenueVu 30 fps                                           | 162.82 | 270.85 | 378.11 | 490.16 |

| c) HP Desktop<br>UHD (3840×2160), RA | QP12  | QP17   | QP22   | QP27   |

|--------------------------------------|-------|--------|--------|--------|

| EBULupoCandlelight 50 fps            | 62.94 | 109.66 | 244.84 | 322.95 |

| EBULupoConfetti 50 fps               | 71.28 | 176.07 | 312.37 | 365.96 |

| EBURainFruits 50 fps                 | 56.09 | 112.65 | 210.54 | 288.36 |

| EBUWaterfallPan 50 fps               | 62.28 | 128.29 | 207.46 | 272.76 |

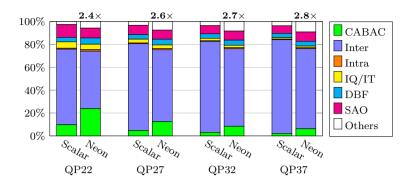

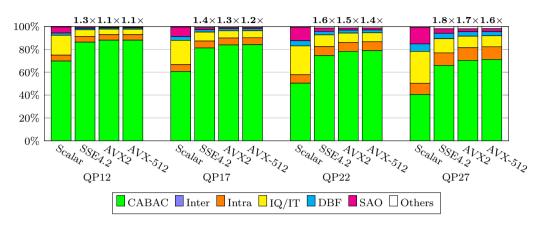

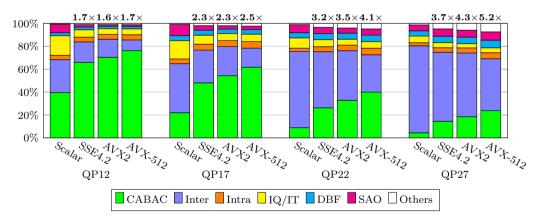

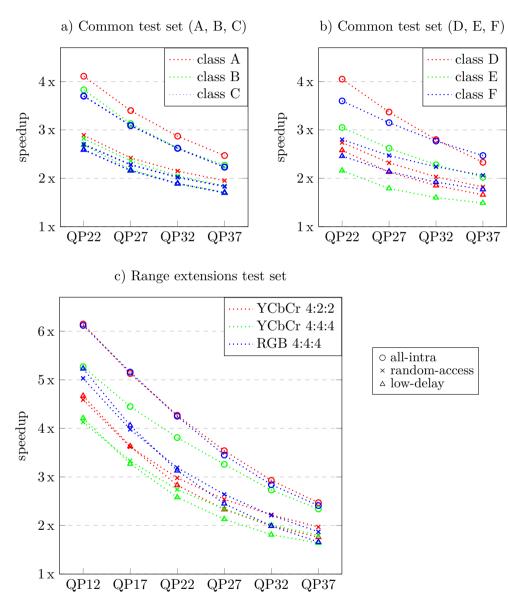

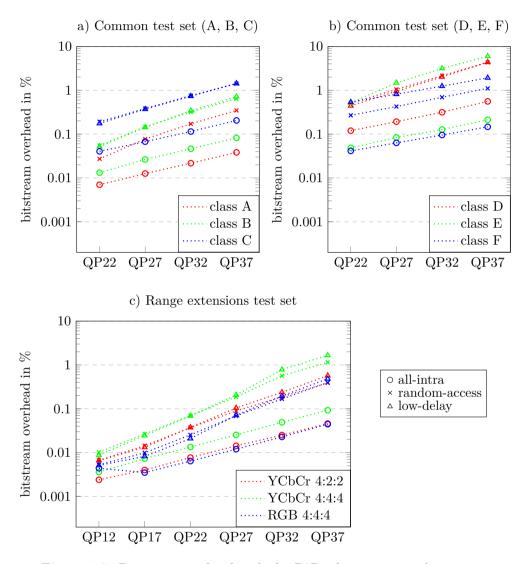

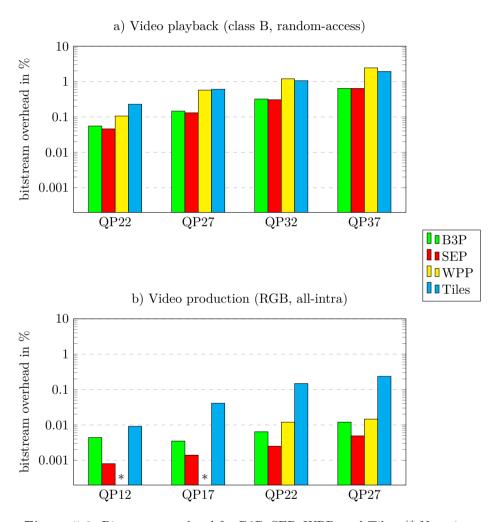

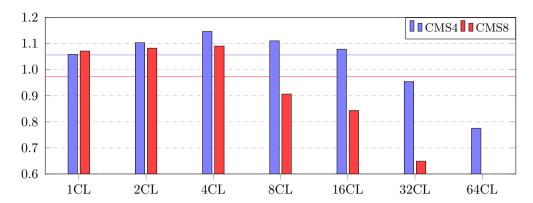

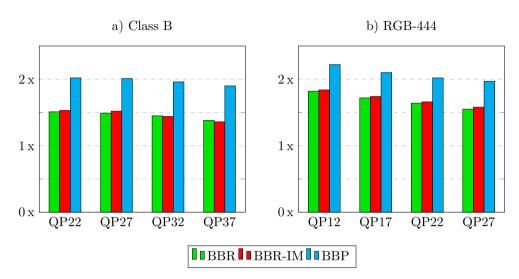

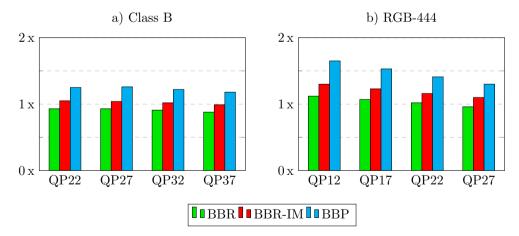

**Figure 2.6:** Smartphone + FHD testset profiling with Neon vectorization. Speedup over Scalar shown on top.

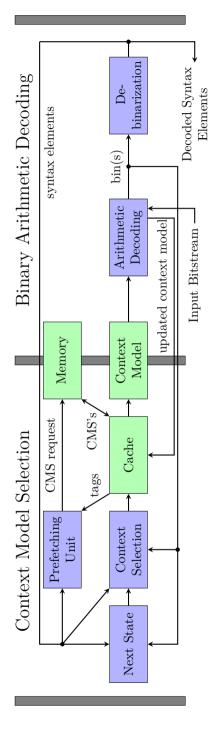

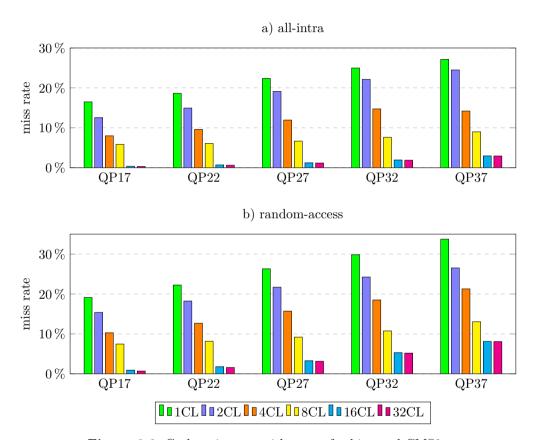

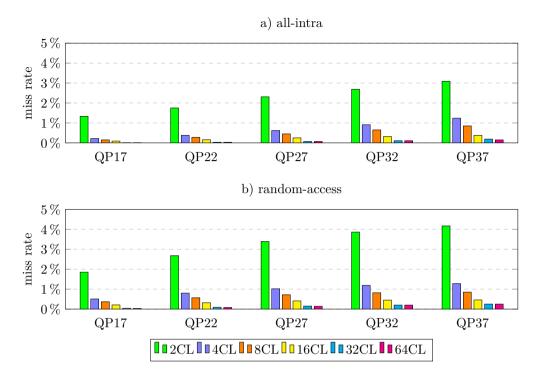

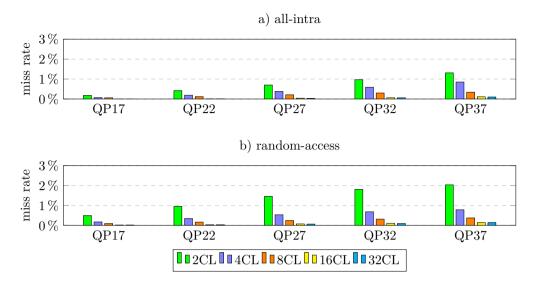

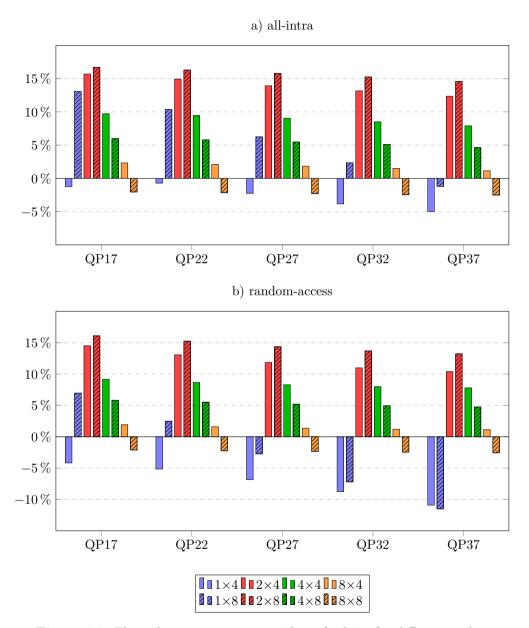

following, we take a more detailed look at the performance measurements for specific testsets (Table 2.6). We further aim to identify performance bottlenecks by analyzing the decoding time that is spent on specific tasks in the single-threaded HEVC decoder (Figures 2.6, 2.7, 2.8).