# **MEMTRACE:**

# A Memory, Performance and Energy Profiler Targeting RISC-Based Embedded Systems for Data-Intensive Applications

von

Diplom-Ingenieur

Heiko Hübert

Von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften – Dr.-Ing. –

genehmigte Dissertation

## Promotionsausschuss:

Vorsitzende: Frau Prof. Dr. rer. nat. Sabine Glesner Berichter: Herr Prof. Dr.-Ing. Hans-Ulrich Post Berichter: Herr Prof. Dr.-Ing. Holger Blume

Tag der wissenschaftlichen Aussprache: 19. Mai 2009

Berlin 2009

# Acknowledgements

The research described in this thesis has been carried out at the Fraunhofer Institute for Tele-communications, Heinrich Hertz Institute (HHI) in Berlin. My work within the Embedded System Group (ESG) of the Image Processing Department laid the foundations and provided inspiration for this dissertation.

First of all I would like to thank Professor Hans-Ulrich Post, who immediately agreed to supervise this thesis. He provided me with valuable comments on scientific and structural concerns. I am also very grateful to Professor Holger Blume for being the co-referee and for all our discussions, which were inspiring and valuable to me.

A very special and extended thank you goes to my supervisor at HHI, Dr. Benno Stabernack, who conducted me through all these years. I appreciate his advice on so many matters and the countless hours he invested in discussions and just chatting. I am also grateful to Dr. Ralf Schäfer, the head of the Image Processing Department, for giving me the opportunity to accomplish this work. My gratitude also goes to my colleagues at HHI for all the fruitful discussions and for helping me to expand my knowledge in many ways.

Special thanks go to Ella Ornstein, who helped this work to lose a bit of its German accent and make it nicer for the native speaker's ears. Also, Joshua Becker and my colleagues at HHI spent many hours of their spare time proof-reading. Many thanks.

Finally, I want to express my deepest appreciation to my family and friends. They provided moral support and always managed to encourage me whenever the goal seemed out of reach.

# **Abstract**

The design of embedded hardware/software systems is often subject to strict requirements concerning various aspects, including real time performance, energy consumption and die area. Especially for data-intensive applications, such as multimedia systems, the number of memory accesses is a dominant factor for these aspects. In order to meet the requirements and design a well-adapted system, it is necessary both to optimize the software and to design an adequate hardware architecture. For complex applications, this design space exploration can be difficult and requires in-depth analysis of the application and its implementation alternatives. This calls for profiling tools, which aid the designer in the design, optimization and scheduling of hardware and software.

Numerous tools exist for this purpose, and performance profiling solutions especially have been available for decades. Memory and energy profiling for embedded systems have become major issues within the last 10 years. However, the existing tools either cover only parts of the required profiling results or the statistics are not at the required level of detail. Some of the tools provide results only for the entire application and not at a source-code function level. This restricts the optimization potential, as the cause of a performance loss cannot be localized. Other tools suffer from a restricted level of accuracy. Results are based on generic processor architectures or taken with a low sample rate, or the tools apply source code instrumentation. Available profiling mechanisms with high accuracy suffer from long simulation times. This makes a comprehensive system analysis unfeasible.

This work presents a novel profiling methodology, which combines fast, accurate and comprehensive profiling in order to overcome the restrictions of the aforementioned techniques. The work describes the developed technique and its implementation as the MEMTRACE profiling tool. The trade-off between a decent simulation time and a sufficient level of accuracy is reached by using a tracing-based profiling approach that applies cycle-accurate simulators. In order to target a broad range of processors, a well-defined interface is established for interconnection with the processor simulator. Thus any cycle-accurate model can be used, as long as it provides access to basic runtime information such as the program counter, cycle counter and memory busses. The profiler is independent of the application's source code, which leads to higher accuracy as compared to instrumentation-based tools.

METRACE delivers cycle-accurate profiling results on a C function or even source code line level. The results include clock cycles, various memory access statistics and energy consumption estimates for embedded RISC-based processors. In addition to these results, the tool generates numerous statistics tailored to the specific optimization techniques that have been developed in this work. A focus is placed on memory access optimization, since for data-intensive applications, this aspect offers a high potential for increasing system efficiency.

Additionally to software analysis, the profiler supports an examination of bus-based systems, for example those composed of a processor, memory devices and coprocessors. For this purpose the coprocessors are represented by abstract but cycle-accurate models and MEMTRACE has been extended by detailed bus analysis features.

An instruction-accurate power consumption model has been developed for a sample processor and incorporated into the profiler for energy estimation. Two case studies are presented, which show how the applicability of the profiler and the optimization techniques has been proven in the design of hardware/software systems for data-intensive applications.

# Zusammenfassung

Der Entwurf eingebetteter Hardware/Software-Systeme unterliegt häufig strengen Anforderungen hinsichtlich verschiedener Kriterien wie z.B. Echtzeitfähigkeit, Energieverbrauch und Chipfläche. Insbesondere bei datenintensiven Anwendungen, beispielsweise in Multimediasystemen, spielt die Anzahl von Speicherzugriffen eine dominierende Rolle. Um diesen Kriterien beim Entwurf gerecht zu werden, muss sowohl die Software optimiert als auch eine adäquate Hardwarearchitektur entwickelt werden. Für komplexe Anwendungen kann diese Entwurfsraum-Exploration aufwändig sein und setzt eine detaillierte Analyse der Anwendung und ihrer Implementierungsalternativen voraus. Um den Entwickler bei Entwurf, Optimierung und Scheduling zu unterstützen, werden deshalb Analysewerkzeuge (Profiler) benötigt.

Zahlreiche Programme wurden bereits zu diesem Zweck entwickelt, insbesondere Leistungsanalyse analysewerkzeuge existieren seit langem. Die Speicherzugriffs- und Verlustleistungsanalyse gewannen gerade in den letzten zehn Jahren an Relevanz. Die gegenwärtigen Profiler decken jedoch entweder nur einen Teil dieser Analysen ab oder sie können nicht den benötigten Detaillierungsgrad liefern. Beispielsweise können einige der Werkzeuge die Ergebnisse nicht den Quellcodefunktionen zuordnen. Dies verringert das Optimierungspotential, da die Ursache einer Leistungseinbuße nicht genau lokalisiert werden kann. Andere Profiler liefern hingegen eine eingeschränkte Genauigkeit aufgrund generischer Prozessormodelle, niedriger Abtastfrequenz oder Quellcodemodifikationen (Instrumentation). Analysemethoden mit hoher Genauigkeit benötigen oft lange Simulationszeiten, die eine umfassende Systemanalyse verhindern.

In dieser Arbeit wird eine neue Profilingmethode vorgestellt, die sowohl eine genaue, schnelle als auch umfangreiche Analyse ermöglicht und damit die Schwächen der erwähnten Methoden überwindet. Die Arbeit beschreibt die Methodik und deren Umsetzung als MEMTRACE Profiler. Durch einen tracingbasierten Ansatz, der einen zyklengenauen Simulator verwendet, können sowohl eine adäquate Simulationszeit als auch eine ausreichende Genauigkeit erreicht werden. Um einen breiten Bereich an Prozessoren abdecken zu können, wurde eine wohldefinierte Schnittstelle zwischen Profiler und Simulator geschaffen. Dadurch kann jedes zyklengenaue Modell verwendet werden, das einen Zugang zu grundlegenden Prozessorressourcen erlaubt, wie z.B. dem Befehlszähler, Zyklenzähler und den Speicherbussen. Außerdem ist der Profiler vom Quellcode der zu untersuchenden Applikation unabhängig, was zu einer höheren Genauigkeit gegenüber den Ergebnissen instrumentationsbasierter Ansätze führt.

MEMTRACE liefert zyklengenaue Analyseergebnisse auf Funktions- bzw. Zeilenebene des C-Quellcodes. Die Ergebnisse umfassen Taktzyklen, zahlreiche Speicherzugriffsstatistiken und Energieverbrauchsabschätzungen für eingebettete RISC Prozessoren. Neben diesen Ergebnissen werden zahlreiche weitere Analyseergebnisse generiert, die auf spezielle Optimierungen zugeschnitten sind, welche im Rahmen dieser Arbeit entwickelt wurden. Dabei wird ein Fokus auf Speicherzugriffe gelegt, da deren Optimierung bei datenintensiven Anwendungen ein hohes Potential zur Steigerung der Systemeffizienz mit sich bringt.

Zusätzlich zur Softwareanalyse wird durch den Profiler auch eine Untersuchung bus-basierter Systeme ermöglicht, z.B. bestehend aus einem Prozessor, Speichern und Coprozessoren. Dazu werden die Coprozessoren durch abstrakte, aber zyklengenaue Modelle abgebildet sowie MEMTRACE um detaillierte Busanalysefunktionen erweitert.

Um eine Abschätzung der Verlustleistung zu unterstützen, wurde exemplarisch ein instruktionsgenaues Verlustleistungsmodell entwickelt und in den Profiler integriert. Anhand zweier Fallstudien wird gezeigt, wie der Profiler erfolgreich innerhalb des Entwurfs von Hardware/Software Systemen für datenintensive Applikationen Anwendung finden konnte.

# **Table of Contents**

| A | CKNOW          | LEDGEMENTS                                                               | III |

|---|----------------|--------------------------------------------------------------------------|-----|

| A | BSTRAC         | T                                                                        | V   |

| Z | USAMM          | ENFASSUNG                                                                | VII |

| T | ABLE O         | F CONTENTS                                                               | IX  |

|   |                | ATIONS                                                                   |     |

| 1 |                | RODUCTION                                                                |     |

| • | 1.1            | BACKGROUND                                                               |     |

|   | 1.2            | CONTRIBUTIONS                                                            |     |

|   | 1.3            | OUTLINE                                                                  |     |

| 2 | STA            | TE OF THE ART                                                            | 3   |

|   | 2.1            | EMBEDDED SYSTEMS                                                         | 3   |

|   | 2.1.1          | Design Flow                                                              |     |

|   | 2.1.2          | Processors                                                               |     |

|   | 2.1.3          | The ARM Architecture                                                     |     |

|   | 2.1.4          | The AMBA Architecture                                                    |     |

|   | 2.2            | PROCESSOR SIMULATORS                                                     |     |

|   | 2.2.1<br>2.2.2 | ARMulator – The ARM Instruction Set Simulator                            |     |

|   | 2.2.2          | Automatic Simulator Generation – The Verilator                           |     |

|   | 2.3.1          | ARM Software Development Toolchain                                       |     |

|   | 2.3.2          | Cycle Profiling Tools                                                    |     |

|   | 2.3.3          | The ATOMIUM Memory Profiler                                              |     |

|   | 2.3.4          | Power Estimation Tools                                                   |     |

| 3 | THE            | ORETICAL BACKGROUND                                                      | 27  |

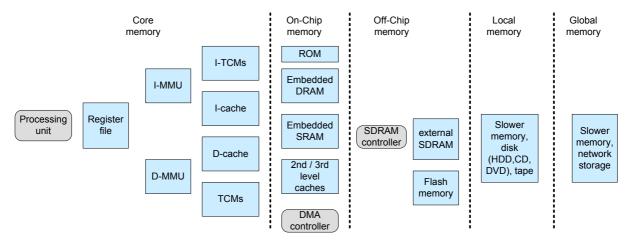

|   | 3.1            | EMBEDDED SYSTEM COMPONENTS                                               | 27  |

|   | 3.1.1          | Processor Architectures                                                  |     |

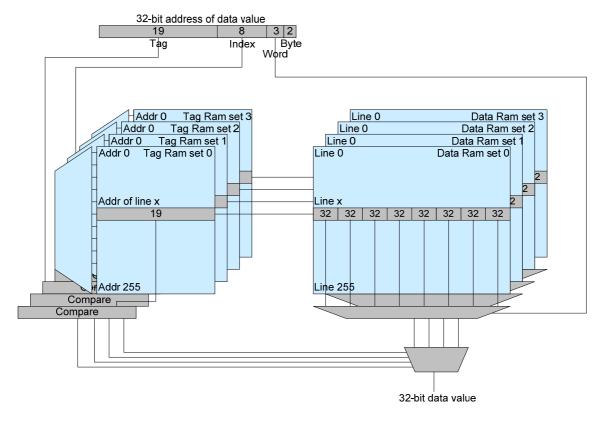

|   | 3.1.2          | Memory Architectures                                                     | 29  |

|   | 3.1.3          | Interconnection Architectures                                            |     |

|   | 3.2            | SIMULATION MODELS                                                        |     |

|   | 3.2.1          | Processor Models                                                         |     |

|   | 3.2.2<br>3.3   | Memory ModelsProfiling                                                   |     |

|   | 3.3.1          | Profiling Results                                                        |     |

|   | 3.3.2          | Profiling Methods                                                        |     |

|   | 3.4            | DATA-INTENSIVE APPLICATIONS AND THEIR IMPLEMENTATION FOR RISC PROCESSORS |     |

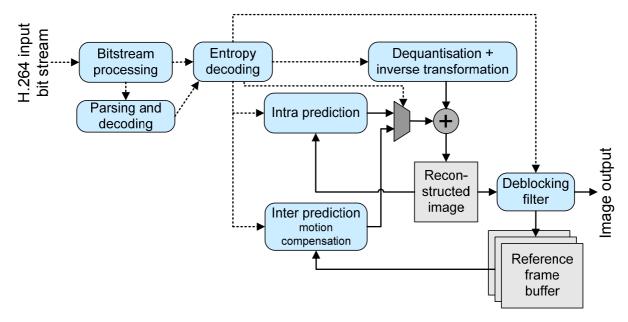

|   | 3.4.1          | The H.264/AVC Video Coding Standard                                      |     |

| 4 | COM            | IPREHENSIVE PROFILING OF EMBEDDED PROCESSORS                             | 48  |

|   | 4.1            | EXTENSIVE PROFILING METHODOLOGY                                          | 48  |

|   | 4.1.1          | Program Information Acquisition                                          |     |

|   | 4.1.2          | Runtime Data Acquisition                                                 | 52  |

|   | 4.1.3          | Representation of the Statistical Analysis Data                          |     |

|   | 4.2            | MEMORY PROFILING WITHIN THE DESIGN FLOW                                  |     |

|   | 4.2.1          | Hardware/Software Partitioning and Design Space Exploration              |     |

|   | 4.2.2<br>4.2.3 | Software Profiling and Optimization                                      | 33  |

|   | 4.2.3<br>4.2.4 | Coprocessors                                                             |     |

|   | 4.2.5          | Scheduling                                                               |     |

|   | 4.2.6          | HDL Simulation                                                           |     |

|   |                |                                                                          |     |

|   | 4.3            | PROFILING-BASED SOFTWARE OPTIMIZATIONS                      |     |

|---|----------------|-------------------------------------------------------------|-----|

|   | 4.3.1          | Pinpointing Code Locations with Inefficient Memory Accesses |     |

|   | 4.3.2          | Using Caches and Non-Cacheable Areas                        |     |

|   | 4.3.3          | Page Miss Reduction in DRAMs                                |     |

|   | 4.3.4          | Speedup Estimation before Implementation                    |     |

|   | 4.3.5          | Data Access Visualization                                   |     |

|   | 4.3.6          | Efficient Register Usage                                    |     |

|   | 4.4            | PROFILING-BASED HARDWARE OPTIMIZATION                       |     |

|   | 4.4.1          | Instruction Set                                             |     |

|   | 4.4.2          | Address Modes                                               |     |

|   | 4.4.3          | Data Partitioning between Fast and Slow Memory              |     |

|   | 4.5            | POWER MODEL OF AN EMBEDDED PROCESSOR                        |     |

|   | 4.5.1          | CMOS Power Consumption                                      |     |

|   | 4.5.2          | Power Measurement Methods                                   |     |

|   | 4.5.3          | Instruction Sequences for Power Evaluation                  |     |

|   | 4.5.4          | Power Model of an SoC                                       |     |

| 5 | IMP            | LEMENTATION                                                 | 80  |

|   | 5.1            | Workflow                                                    |     |

|   | 5.1.1          | Initialization                                              |     |

|   | 5.1.2          | Analysis                                                    |     |

|   | 5.1.3          | Postprocessing of the Analysis Results                      |     |

|   | 5.2            | TOOL ARCHITECTURE                                           |     |

|   | 5.2.1          | MEMTRACE Base                                               |     |

|   | 5.2.2          | MEMTRACE Dynamic Link Library (Backend)                     |     |

|   | 5.3            | GRAPHICAL USER INTERFACE                                    |     |

|   | 5.4            | SPREADSHEET FORMAT DESCRIPTION                              |     |

|   | 5.5            | THE CONFIGURATION FILE                                      |     |

|   | 5.5.1          | File Format                                                 |     |

|   | 5.5.2          | List of Functions                                           |     |

|   | 5.5.3<br>5.5.4 | List of Variables                                           |     |

|   |                | Global Settings                                             |     |

|   | 5.6<br>5.6.1   | Hardware/Software Cosimulation Interface                    |     |

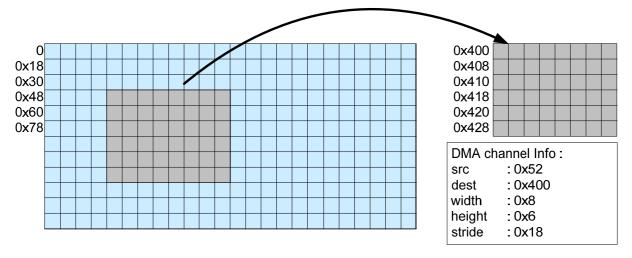

|   | 5.6.2          | DMA Controller                                              |     |

|   | 5.7            | RETARGETING TO OTHER EMBEDDED PROCESSORS                    |     |

|   | 5.7.1          | Toolflow for Profiling LISA and Verilog Processor Models    |     |

|   | 5.8            | POWER MEASUREMENT SETUP                                     |     |

|   | 5.8.1          | Calibration of the Measurement Setup                        |     |

|   | 5.8.2          | Software Test Suite                                         |     |

| 6 | A PP           | JICATION OF THE PROFILER                                    |     |

| · | 6.1            | H.264/AVC Decoder Profiling                                 |     |

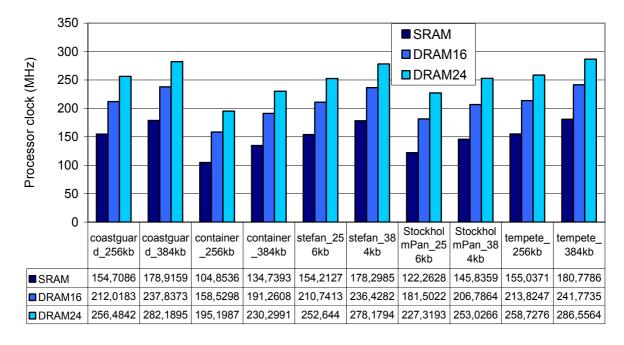

|   | 6.1.1          | Description of the Test Scenario                            |     |

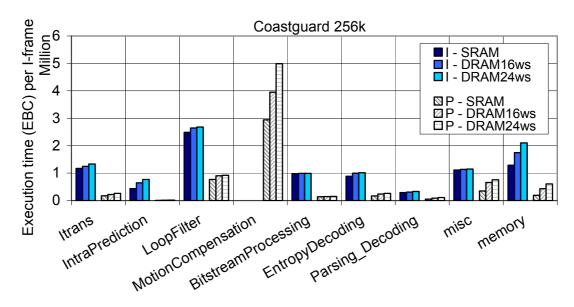

|   | 6.1.2          | Profiling Results                                           |     |

|   | 6.1.3          | Profiling-Based Software Optimization Potential             | 108 |

|   | 6.1.4          | Summary of Profiling and Software Implementation Results    | 100 |

|   | 6.1.5          | Hardware/Software System Architecture                       |     |

|   | 6.2            | GESTAVATAR – GESTURE DETECTION FOR AVATAR CONTROL           |     |

|   | 6.2.1          | Results                                                     |     |

| 7 | SUM            | MARY & PROSPECTS                                            | 122 |

| • | 7.1            | COMPARISON WITH EXISTING TOOLS                              |     |

|   | 7.1            | PROSPECTS                                                   |     |

| 0 |                | ENDIX                                                       |     |

| 8 |                |                                                             |     |

|   | 8.1            | DETAILED AND COMPREHENSIVE PROFILING RESULTS                |     |

|   | 8.1.1          | H.264/AVC Encoder/Decoder                                   |     |

|   | 8.1.2          | Function Group Analysis for I- and P-Frames                 |     |

|   | 8.1.3          | Cycles per Frame Analysis                                   | 133 |

| 8.1.4   | Usage of ARM11 SIMD Instructions            |     |

|---------|---------------------------------------------|-----|

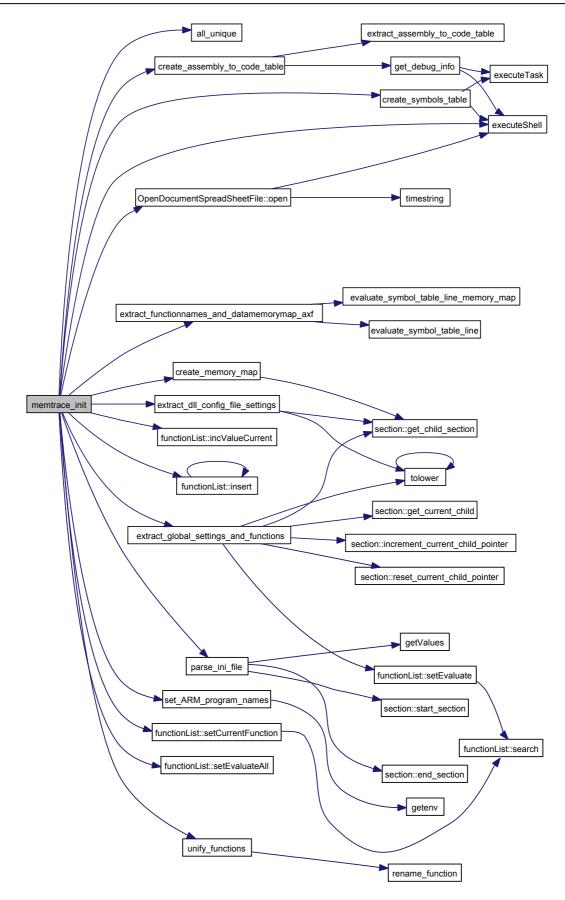

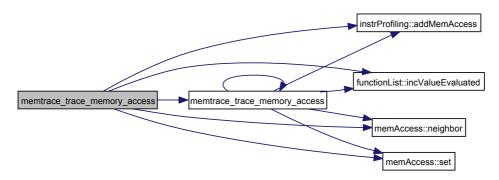

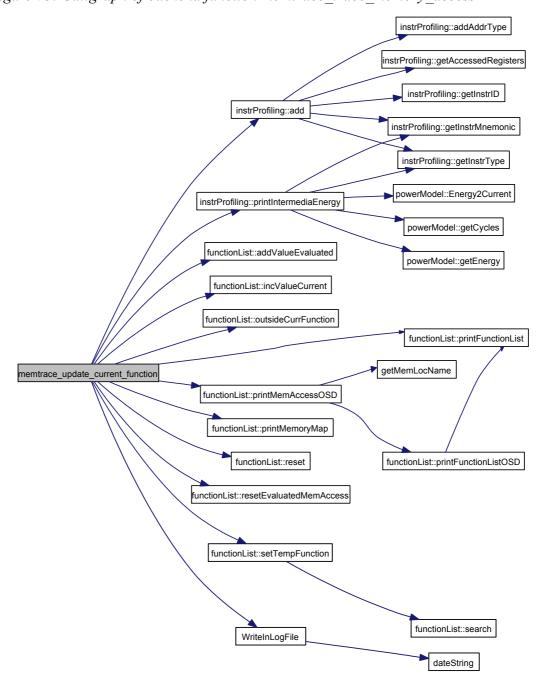

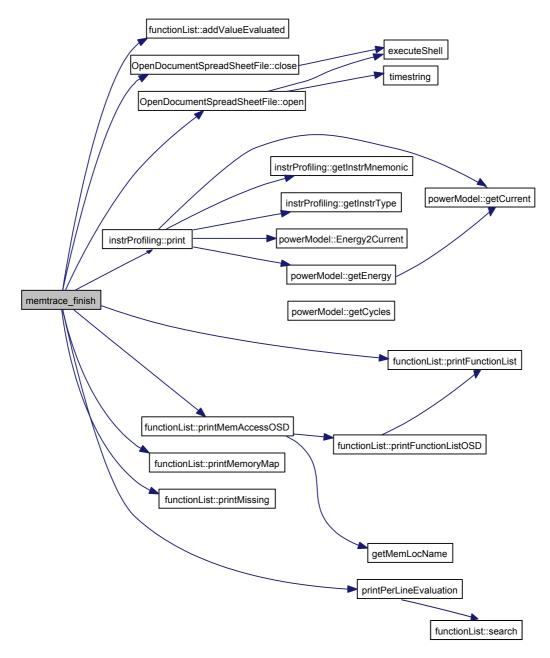

|         | MEMTRACE IMPLEMENTATION DETAILS.            |     |

| 8.2.1   | Block Diagrams of MEMTRACE Internals        |     |

| 8.2.2   | Screenshots of the Graphical User Interface |     |

| 8.2.3   |                                             |     |

| 8.2.4   | The Configuration File                      |     |

| 8.2.5   | List of Source Code Files                   |     |

|         | Full Description of the Command-line Syntax |     |

| REFEREN | NCES                                        | 151 |

# **Abbreviations**

AHB Advanced High-performance Bus

ALU Arithmetic Logic Unit

AMBA Advanced Microcontroller Bus Architecture

API Application Programming Interface

ASIC Application Specific Integrated Circuit

ASIP Application Specific Instruction Set Processor

AXF ARM Executable Format

AXI Advanced eXtensible Interface

CIF Common Intermediate Format

CISC Complex Instruction Set Computer

CLI Command-line Interface

CMOS Complementary Metal Oxide Semiconductor

CPU Central Processing Unit

DDR Double-Data-Rate

DLL Dynamic Link Library

DMA Direct Memory Access

DIVIA Direct Memory Access

DRAM Dynamic Random Access Memory

DSP Digital Signal Processor

DVB-H Digital Video Broadcasting – Handheld

EBC External Bus Cycles

ELF Executable and Linking Format FPGA Field-Programmable Gate Arrays

FIFO First In – First Out

FLI Foreign Language Interface

FLPA Functional-Level Power Analysis

GUI Graphical User Interface

HDL Hardware Description Language

ILPA Instruction-Level Power Analysis

IO Input/Output

IP Intellectual Property

IPC Instruction Per Cycle

ISO International Organization for Standardization

ISA Instruction Set Architecture

ISS Instruction Set Simulator

ISSM Instruction Set System Model

ITU International Telecommunication Union

MMU Memory Management Unit

MPEG Moving Pictures Experts Group

NoC Networks-on-Chip

OS Operating System

PCB Printed Circuit Board

PDA Personal Digital Assistant

Pel Picture Element (Pixel)

PLI Programming Language Interface

QVGA Quarter Video Graphics Array

RAM Random Access Memory

RISC Reduced Instruction Set Computer

ROM Read Only Memory

RTL Register Transfer Level

RTSM Real Time System Model

RW Read-Write

SIMD Single Instruction Multiple Data

SPICE Simulation Program with Integrated Circuit Emphasis

SoC System-on-Chip

SDRAM Synchronous Dynamic Random Access Memory

SI International System of Units

SRAM Static Random Access Memory

TCM Tightly Coupled Memory

TLB Translation Lookaside Buffer

VHDL Very High Speed Integrated Circuit Hardware Description Language

VLC Variable Length Coding

VLIW Very Long Instruction Word

ZI Zero Initialized

# 1 Introduction

# 1.1 Background

The design of an embedded system often starts from a software description of the system in the C language. For example, the designer writes an executable specification based on a reference implementation of the application, e.g. from standardization organizations or the open-source community. This software code is often not optimized in any way, because it mainly serves the purpose of functional and conformance testing. Therefore it has to be transformed into an efficient system, including hardware and software components. The design of the system requires the following steps:

- system architecture design

- hardware/software partitioning

- software optimization

- design of hardware accelerators

- system scheduling

All these steps require detailed information about the performance of the different parts of the application. Besides the arithmetical demands of the application, memory accesses can have a huge influence on performance and power consumption. This is especially the case for data-intensive applications such as multimedia systems, due to the huge amount of data being transferred in these applications. This problem increases if the given data bandwidth is not used efficiently.

In order to reduce overall data traffic, those parts of the code which require a high amount of data transfer have to be identified and optimized. The above-mentioned applications contain up to 100,000 lines of source code. Therefore tools are required that help the designer to identify the critical parts of the software. Several analysis tools exist, for example gprof [42] or VTune [57] provide timing analysis. Memory access analysis is part of the ATOMIUM [25] tool suite. However, all these tools provide only approximate results for either timing or memory accesses. A highly accurate memory analysis can be done with a hardware (HDL) simulator, if an HDL model of the processor is available. However, such an analysis requires a long simulation time.

This thesis targets these issues and covers the performance, memory and power consumption profiling of embedded systems, as well as the usability of the profiling results within the design flow. In order to achieve a fast and accurate solution, a specialized profiler has been developed, called MEMTRACE, for obtaining performance, memory access and power consumption statistics. The profiling is tailored to embedded system architectures containing a single RISC processor, a single memory bus with memory-mapped components – such as memory or coprocessors – and a direct memory access (DMA) controller. This thesis will show how the provided profiling results can be used during the design and optimization of embedded hardware/software systems. Among other case studies, MEMTRACE has been applied during the efficient design of a mixed hardware/software system for H.264/AVC video decoding. Starting from a software implementation, this thesis shows how the software is optimized, an efficient hardware architecture developed and the system tasks scheduled based on the profiling results.

## 1.2 Contributions

The contributions of this work can be summarized as:

- presentation of an overview of existing profiling tools

- overview of embedded system architecture components

- design and implementation of a profiling tool suite

- development of several profiling analysis methods for memory-centric software and hardware optimization

- design and implementation of a hardware/software co-profiling environment

- creation of a simple processor power model for energy profiling

- integration of the profiler in an embedded system design flow

- application of the profiler for analysis of several software projects

- application of the profiler during the design of a system architecture for a multimedia SoC

This profiling and optimization methodology has been applied within several industrial and research projects. The profiling tool developed in this work has been used for evaluating and optimizing the performance of software targeting embedded devices. In-depth profiling has been performed, combined with system architecture exploration of memory and coprocessors.

The profiling methodology and the tool implementation have been presented to the research community in several publications and presentations at workshops and symposiums as well as in a book chapter [46, 47, 48, 92, 49]. Furthermore, the application of the tool within the design of embedded systems is described in technical journals and proceedings of international conferences [88, 89, 91, 87, 86]

## 1.3 Outline

Chapter 2 gives an overview of the state of the art in profiling and related subjects. A general overview of current embedded system design flows and existing tools for CPU, memory and power profiling is presented.

In Chapter 3 the theoretical background of the different aspects is surveyed. The components of processor-centric embedded systems and the corresponding simulation models are presented. Since the focus of this work is data-intensive applications, an example of such applications and implementation issues for embedded systems are given. The different aspects of profiling are highlighted and existing methods for hardware/software optimizations are presented.

Chapter 4 shows the contribution of this work to the field of profiling embedded processor systems. The profiling method and a variety of analysis results are presented. There is also a focus on power measurement and model creation for a sample processor. Furthermore, this thesis presents the application of the profiling results within the design flow for hardware- and software-centric optimizations.

The implementation and the workflow of the profiling tool as well as its integration with an existing instruction set simulator are described in Chapter 5. The profiling tool has been used within a number of projects for software analysis and optimization as well as for hardware architecture design. Some examples are presented in Chapter 6. Chapter 7 summarizes the work and points out unresolved issues and areas for future work.

# 2 State of the Art

This chapter presents the state of the art of profiling of embedded systems. As the term "embedded systems" is quite fuzzy, a review of the different definitions found in literature is provided and summarized. The major component of an embedded system is the processor, which controls the system and executes the software part of the application. An overview of the most common embedded processors is given. For profiling the software a simulation model of the processor is required, therefore Section 2.2 describes a processor simulator and a simulator generator. The following section gives an overview of the tools required in profiling process, including an example development toolchain and existing tools for performance, memory and power analysis.

# 2.1 Embedded Systems

Many definitions can be found for the term "Embedded System". Marvedel gives a pragmatic definition in his book of "Embedded System Design" [66], which covers a wide range of application fields:

"Embedded systems can be defined as information processing systems embedded into enclosing products, such as cars, telecommunication or fabrications equipments"

Most definitions slightly differ from each other, but a statement which can be found very often is that there is no fixed definition for this term. This fact was stated already a decade ago [39] and a fuzziness within the definition is still common today [66]. The most plausible reason is the enormous growth of the application field for embedded systems. Whereas an early application for embedded system could be found in banking transaction systems [100] and was implemented on mainframes. Over the decades their application field has grown to cover industrial control systems, networking devices, household appliances, automotive and consumer and many other products. Such systems can be found in portable as well as stationary devices. The following attributes can be found in most descriptions of embedded systems, e.g. in [66, 39, 72]:

- embedded in an enclosing device

- tailored to a specific application

- subject to real-time constraints and efficiency requirements

- interaction with external devices, such as sensors, regulators, input and output devices

- programmability is a common feature

- consists of hardware and software components

- often used in consumer products, control applications

Another way of identifying and defining embedded systems can be done by distinguishing the term from related devices or systems. ASICs, which are also tailored to a specific application, define devices usually composed of fixed hardware components. ASIPs come closer to embedded systems, or can be part of such, as they also offer programmability besides their restricted application area. However, ASIP only refer to the programmable part of a system. The definition of SoC comes closest to the one of embedded systems, as system-on-chips combine different components to form an entire system. An inherent characteristic of SoCs is that the parts are combined on a single chip, whereas embedded systems might be (and often are) constructed of multiple devices.

For clarifying the term, many people distinguish between embedded systems and general-purpose computer, such as a PC. The difference can be stated by a PC not being dedicated to a specific application and as such it can be programmed freely [21, 72]. On the other hand, the computing task of the embedded systems is invisible to the user [66]. Edwards et al. [32] state in 1997:

"Such systems, which use a computer to perform a specific function, but are neither used nor perceived as a computer, are generically known as embedded systems"

The program code controlling the programmable parts of an embedded system is often stored in ROM, such as a flash memory and is usually referred to as firmware, contrary to the term software used in PCs.

Considering the two parts of the term, "embedded" indicates that the unit is part of a larger device and not stand-alone. And the word "system" reflects that it consists of several units, most often a processor, coprocessors and input/output units for interacting with the device.

# 2.1.1 Design Flow

The implementation of embedded hardware/software systems incorporates many design and optimization steps. The targeted application and requirements have to be mapped on a combination of hardware and software components. The mapping decision is influenced by several factors, mainly by the application requirements and the available hardware and software resources. For finding a suitable system architecture, usually a design space exploration is performed based on more or less detailed profiling [22].

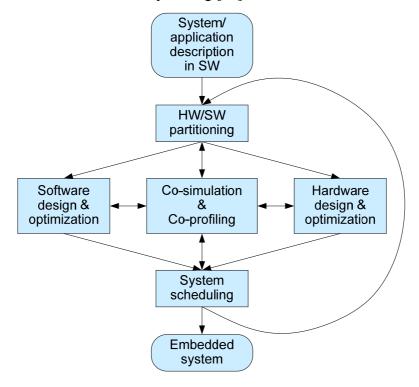

Figure 1: Typical embedded system design flow

Figure 1 shows a typical design flow for embedded hardware/software systems. Initially a system is defined in a textual form describing its functionality, requirements and constraints. The description of the functionality is then transferred to an executable form in order to prove its correctness. After functionally verifying this executable system description, often in C or

C++, a performance evaluation needs to be made in order to find an appropriate hardware/software architecture. Starting with a pure software implementation and an initial architecture specification, profiling can be used to measure the performance and reveal if the (real-time) requirements are met. If not, an iterative cycle of software and hardware partitioning, optimization and scheduling starts. During this process a continuous co-verification of the system is required. This includes on one hand a cosimulation [50] for ensuring the functional correctness of the system. On the other hand detailed profiling results are crucial for monitoring the influence of design steps on the performance.

## 2.1.2 Processors

Table 1 gives an overview of the most popular embedded RISC processors. Most processors feature a five- to seven-stage pipeline, as it offers a reasonable trade-off between maximum clock-frequency and instruction delay. A common number of registers is 32, with a major exception being the ARM processors, which only feature 16 registers. Section 2.1.3 describes the ARM processor family in more detail.

Most RISC processors are built as Harvard architecture with separated instruction and data caches. Typically, these caches are two- to four-way set associative and have a size of 32 to 64 kB. Since caches are very area and energy consuming, second-level caches are not very common in embedded system design and can only be found in high performance architectures, such as the ARM Cortex-A9 [8] SoCs. Some of the processors are extensible in their execution unit. The LEON [38] and the ARM processors use a coprocessor interface for this purpose. Before the calculation can be executed data needs to be transferred from the register file to the coprocessors by special instructions. Tensilica [94] and ARC [6] allow a customization of the instructions set. The execution unit can be placed beside the main ALU and incorporated in the pipeline path, which allows direct access to the register file. Besides the presented processors, numerous embedded architectures exist, which combine a RISC-Core with a DSP, e.g. Blackfin [5] from Analog Devices or TriCore [52] from Infineon. Such architectures have proven to be a good choice for combining control-flow and data processing needs of multimedia applications.

#### 2.1.3 The ARM Architecture

The ARM processor architecture [37] has evolved over the years from a simple 3-stage pipelined RISC core to a 13-stage-pipelined multi-core SoC architecture. Initially, it had been developed only as a processor for personal computers, but the architecture has been found to be very efficient in terms of performance and power consumption. This makes the ARM processors a good candidate for embedded systems, e.g. for controlling tasks and the newer architecture types also for data processing. The ARM core architecture is a typical RISC processor however with a small register file of only 16 registers, which can lead to performance restrictions for data-intensive applications. Data transfer between register file and memory is only possible with load and store instructions. Newer core types also support more CISC-like load and store instructions for transferring multiple registers with a single instruction. These, instruction are often used for saving registers to the stack or for copying data from one memory location to another. Besides decreasing the instruction count it speeds up transfers by using the burst mode of the AHB.

Table 1: Embedded RISC processors

| Processor                | Pipeline | Custom instr. | Registers | Instr./data<br>cache<br>(in bytes) | Instr./data<br>TCM<br>(in bytes) | Special fea-<br>tures                                      |

|--------------------------|----------|---------------|-----------|------------------------------------|----------------------------------|------------------------------------------------------------|

| ARM7TDMI                 | 3        | -             | 16        | 8k unified                         | -/-                              | Von Neumann architecture                                   |

| ARM9E                    | 5        | -             | 16        | 128k/128k                          | +/+                              | Coprocessor interface                                      |

| StrongARM<br>SA-1110     | 5        | -             | 16        | 16k/8k                             | -/512                            | 32 set-associative caches, coprocessor interface           |

| XScale PXA27x            | 7-8      | -             | 16        | 32k/32k                            | -/2k                             | SIMD, coprocessor interface,<br>256kB SRAM                 |

| ARM11                    | 8        | -             | 16        | 64k/64k                            | +/+                              | SIMD, branch prediction, 64-bit bus, coprocessor interface |

| ARC600                   | 5        | +             | 32(-60)   | 32k/32k                            | 512k/16k                         | Branch prediction, register file extendable                |

| ARC700                   | 7        | +             | 32(-60)   | 64k/64k                            | 512k/256k                        | Branch prediction, 64-bit bus, register file extendable    |

| Tensilica<br>Xtensa7     | 5        | +             | >=64      | 32k/32k                            | 256k/256k                        | Up to 128-bit bus, windowed registers                      |

| Tensilica<br>Diamond232L | 5        | -             | 32        | 16k/16k                            | -/-                              | Windowed registers                                         |

| LatticeMicro32           | 6        | -             | 32        | 32k/32k                            | -/-                              |                                                            |

| Altera NIOS II           | 5-6      | +             | 32        | 64k/64k                            | +/+                              | Direct-mapped cache                                        |

| Xilinx<br>MicroBlaze v5  | 5        | -             | 32        | 64k/64k                            | +/+                              | Direct-mapped cache, coprocessor interface                 |

| MIPS 4KE                 | 5        | -             | 32        | 64k/64k                            | +/+                              | Coprocessor interface                                      |

| openRISC<br>OR1200       | 5        | +             | 32        | 64k/64k                            | -/-                              | Direct-mapped cache, open source                           |

| LEON3                    | 7        | -             | 520       | 1M/1M                              | +/+                              | Coprocessor interface, windowed registers, open            |

| SuperH SH-4/5            | 5        | -             | 16        | yes/yes                            | -/-                              | source<br>16-bit fixed length based,<br>superscalar        |

An exceptional feature of the ARM architecture is a barrel-shifter within the execution stage of the pipeline. The shifter is placed between the register file and the ALU. It can be used within data processing and also for extending the range of immediate value as well as for address offset manipulation.

Two major versions of the ARM instruction set exist, a full 32-bit version and a reduced 16-bit, also called Thumb instruction set. The 32-bit instructions support conditional execution, i.e. each instruction can be coded so that it only executes at a specific status of the CPU flags. The instruction set has grown with every new architecture version and has become very dense and irregular. Custom instructions are not allowed but custom functionality can be provided

via the coprocessor interface. Up to 15 coprocessors can be attached to a core where one coprocessor is already defined as system control coprocessor, e.g. for controlling the MMU and the caches. Specific instructions are available, which allow data transfer between coprocessor, external memory and core register file and furthermore for initiating data processing operations on the coprocessor. For most of the ARM processors support both, little and big endian data arrangement, thus depending on the application field the appropriate setup can be chosen.

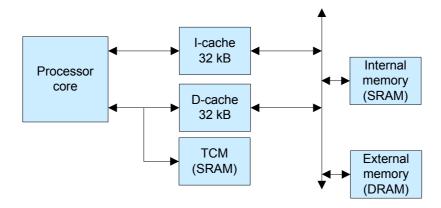

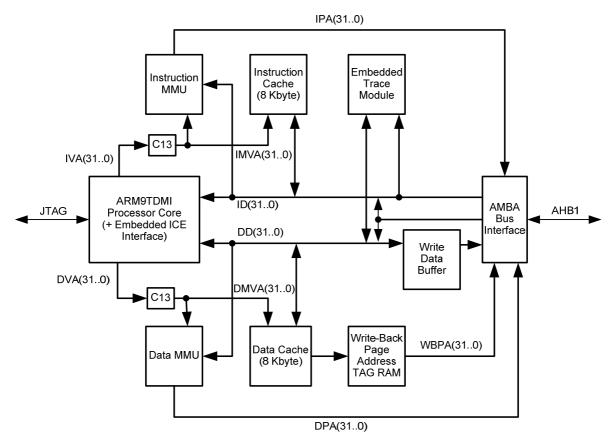

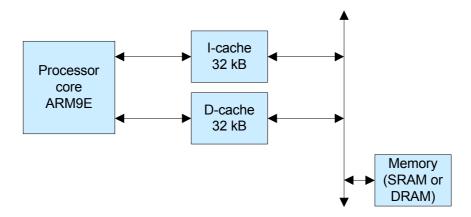

ARM Ltd. licenses the processors as intellectual property and it comes in many different flavors. The oldest architecture available is the ARM7 family. These processors have a simple 3-stage pipeline and a von-Neumann architecture, i.e. using a shared data and instruction bus. The simplest version, the ARM7TDMI, only contains the core without a cache or MMU. This is a very small implementation of a RISC core with a low power implementation. Starting with the ARM9 family, a Harvard architecture is used, with separate caches for instructions and data. The pipeline is extended to five stages and an optional floating point unit is available. A write buffer is introduced for accelerating store operations to external memory and a memory management unit (MMU) for operating system support. The ARM9E family makes the caches customizable and adds tightly coupled memory (TCM) devices, which can be used for fast data and instruction access. The instruction set is extended with DSP instructions, such as a single-cycle multiply-accumulate instruction and saturating arithmetic. The processor used in most studies of this work, the ARM946E-S, is a member of this processor family.

processor family. The ARM 11 family, which was introduced in 2002, extends the pipeline to eight stages and splits it into a data execution and load/store pipeline. Branch prediction is used to decrease the need for flushes of the long pipeline. The instruction set is supplemented by SIMD instructions for use in data-intensive applications, e.g. video or data coding, and a built-in coprocessor for floating point arithmetic. Data transfers have been accelerated by a DMA controller for the TCMs, a wider memory interface of 64-bit and unaligned memory accesses.

The latest processor family is called Cortex and offers several core types targeting different application fields. The most powerful is the Cortex-A family, which provides a dual-issue 13-stage pipeline, extends the SIMD instruction set and width (128-bit) and adds a second-level cache. This family is not covered in this work, because a cycle-accurate instruction set simulator is not available within the software design suite (Real View Development Suite [14]).

Two further families based on the ARM architecture are the StrongARM [53] and the XScale [56] processors. In cooperation with Digital Equipment Corporation (DEC) ARM developed the StrongARM processors in 1995. This core is a predecessor of the ARM9 architecture and offers comparable hardware features, a 5-stage pipeline combined with a Harvard architecture with separate caches and MMUs. Remarkably, the caches, which had an initial size of 16 kB each (in later processor version the D-cache was reduced to 8 kB) are 32-way set-associative. From the programmers perspective it is more similar to the ARM7, the instructions set (ARMv4) provides only 32-bit instructions, without the Thumb or DSP extensions. When Intel took over the processor development from DEC, the StrongARM was improved and became the XScale processor. The XScale is compatible to the ARMv5TE instruction set, which is also supported by the ARM9E family. The pipeline is extended to 7-8 stages and the caches have a size of 32 kB each. Furthermore branch prediction is available and starting with the PXA270, the Wireless MMX extension provides SIMD instructions and an on-chip SRAM of 256 kB is incorporated.

Both, the StrongARM and the XScale are system-on-chip architectures, which provide power management features and numerous auxiliary components, such as DMA controller and inter-

faces to LC displays and serial data communication. They became very popular as processors for portable devices, e.g. PDAs or navigation systems.

#### 2.1.4 The AMBA Architecture

Many system-on-chip architectures use busses that are compliant to the Advanced Microcontroller Bus Architecture (AMBA) [10] standard. AMBA is a royalty-free standard developed by ARM Ltd. and was first released in 1995. The standard defines a range of busses for different needs, starting from simple low-bandwidth busses for I/O purposes up to multi-channel pipelined busses for multi-core architectures. All AMBA busses are synchronous and have separate data and address busses.

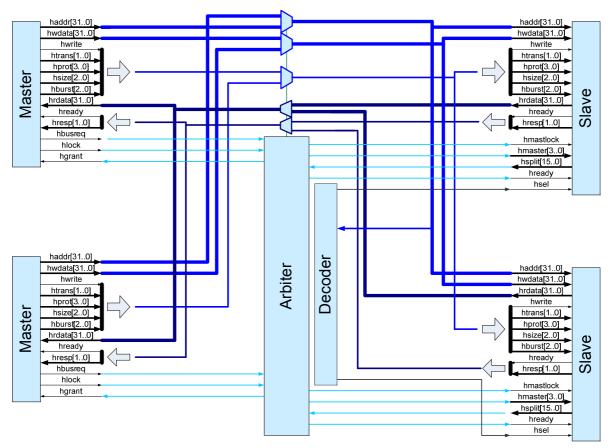

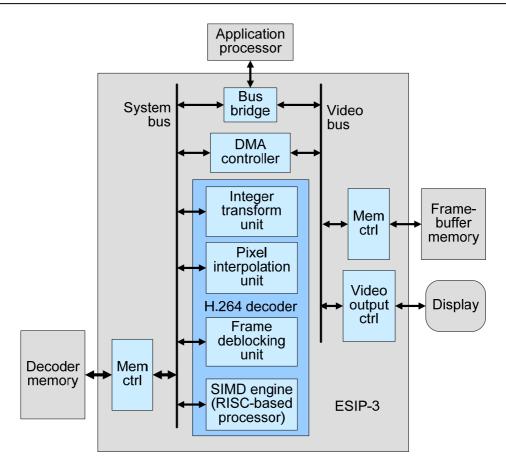

The Advanced Peripheral Bus (APB) of the AMBA specification is optimized for low-bandwidth requirements, easy implementation and low power consumption and especially suitable for slow I/O components, such as timers and serial interfaces. The only master device allowed on the bus is the bridge to a higher order bus and the bus protocol is simple. Advanced features such as pipeline or burst transfer are not supported, and the bus width is restricted to 32 bit. In order to reduce the required chip area, a tristate implementation of the data bus is allowed. For faster system components such as the CPU, memory and DMA controller, the AMBA specification defines the Advanced High-performance Bus (AHB) architecture. The AHB interface is the standard bus connection for all ARM processors up to the ARM10 family, and is also the bus interface simulated in the ARMulator, and therefore used within this work. It is a multi-master compatible bus system and features separate read and write busses. An example system is shown in Figure 2, containing two bus masters and two slaves, the bus arbiter and the decoder.

Figure 2: AHB-based system with two masters and two slaves

Any transaction is initiated by a master, which need to request access to the bus from the arbiter. According to a prioritization scheme, which is not specified in the standard, the arbiter grants access to the bus master with the highest priority. Once the access is granted, the arbiter sets the multiplexers giving the master access to all control, address and data busses, enabling it to reach the slaves. Although all slaves receive the signals, the actual addressed slave is selected by the decoder, which evaluates the address bus according to a specified memory map. In addition the multiplexers in charge of connecting the slave output signals, i.e. reading data and response signals, are set according to the memory map. The address and data signals are driven in a pipelined fashion, i.e. for one clock cycle the master provides the address and control signals, and in the next cycle the data values are expected on the bus. During the data phase of one access the master can issue the address for the next transaction. If the slave cannot serve the data signal in the next cycle, it prolongs the data phase by issuing a wait signal. If the slave expects the waiting time to be long, it can indicate this to arbiter, which may grant bus access to other masters, until the slave can serve the request. This so-called split transaction is especially useful when accessing slow-response slaves, such as an SDRAM controller during a page miss, in order to reduce idle time of the bus.

Besides single data transfer, the AHB protocol specifies burst transfer, which allows the transfer of multiple data values at consecutive addresses within one transaction. Similar to the single data transfer, it starts with an address phase, but features a multi-cycle data phase, where within each clock cycle (if not extended with wait states) one data transfer is issued. Burst transfers are very suitable for burst-oriented components, such as SDRAM, which require a long initialization (addressing) time for each access, but once addressed, can serve data very fast, in order to overcome a long delay time of single transfers.

The AHB protocol allows bursts of fixed sizes or undefined lengths. If another master is requesting the bus during a long burst operation, this leads to a long latency time for this master, and may reduce the system speed significantly. Therefore, a feature called early burst termination is available, which allows the arbiter to decide to interrupt the burst and grant the bus to other waiting masters. For performance increase of the AHB, the simple multiplexer structure shown in Figure 2 can be replaced by a more complex interconnect matrix, which creates a multi-layered bus architecture for parallel data transfer.

The new bus standard within the AMBA specification is the **Advanced eXtensible Interface** (**AXI**) Protocol [11]. It targets even higher bandwidth requirements, especially by separating address and data busses and allow multiple data busses to exist in the system. Thus, multiple transactions can be issued on the address bus and served independently on the data busses. Furthermore, separate read and write data and address busses are defined, which allows concurrent read and write transactions. Each transaction can be labeled with a transfer ID for allowing out-of-order completion. If some transactions have higher latency responses than others, the out-of-order handling leads to less idle time on the busses. The AXI-based busses are the standard interface of never ARM processors and are used in ARM11 and Cortex cores.

## 2.2 Processor Simulators

For testing and analyzing software for a specific processor, the processor needs to be available as a hardware device or simulator, whereas simulators usually offer a more elaborate view of the processor internals. Simulators exist for most processors, differing in their accuracy, sometimes even multiple models on different accuracy levels exist for a processor [81]. As an example of a typical model, an instruction set simulator (ISS) for the ARM architecture is described in more detail. Usually processors, as any digital hardware component, are de-

scribed in a hardware description language. If no other processor model on a higher abstraction level is available, these models can be used for simulation. Being very fine grained they lead to long simulation times. In Section 2.2.2 a tool is presented, allowing a transformation of such models to a higher level of abstraction for faster simulation.

# 2.2.1 ARMulator – The ARM Instruction Set Simulator

The ARMulator [15] is the ISS for processors based on the ARM architecture. In conjunction with a debugger it can be used for code evaluation and performance analysis. Besides the processor core including the pipeline and the register file, the ARMulator simulates other architectural features such as caches, a memory management unit (MMU) and a memory sub system and peripheral devices. The ARMulator is implemented as DLL and works together with the RealView Debugger, the AXF debugger and the command-line debugger armsd, which are all part of the RealView Development Suite, see Section 2.3.1.

The ARMulator simulates the processors in a nearly cycle-accurate manner. Restrictions on the accuracy apply concerning the cache simulation and advanced memory bus (AHB) architectures. The simulator supports a wide range of processors based on the ARM architecture, including a basic support for StrongARM and XScale processors from Intel. See Section 2.1.3 for more details on the ARM processor architecture. As the ARM cores are available as hardware IPs, many features of the cores are adjustable. The simulator allows adjusting these features, which include:

- cache sizes and organization

- tightly coupled memory size

- · processor speed

- divider between processor and bus cycle length

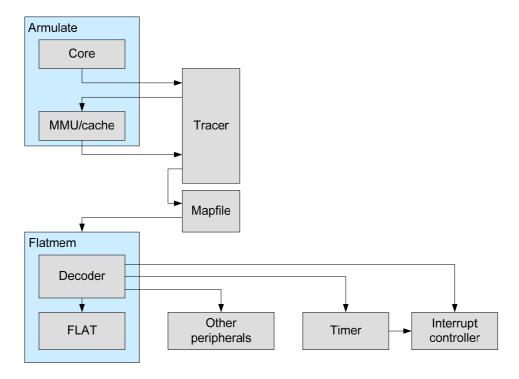

The external memory bus architecture is an abstract model of the AMBA AHB standard, which defines a multiplexer-based on-chip bus. The multi-master capable bus has separate address and data busses and a typical data bus width of 32-bit. The simulator can be extended by modules, which can be used for gathering inside information of the simulator or for the simulation of hardware components surrounding the processor. Such hardware extensions can either be memory-mapped devices or connected via the coprocessor interface, thus creating an entire system architecture. Some examples for extension modules are already provided with the ARMulator, such as a profiler and a tracer module for analysis purposes as well as memory module for simulation of a memory sub system. Figure 3 shows an example connection of modules to the ARMulator.

The ARMulator is extended with the tracer module, tracing all accesses to the caches and from the caches to the external bus. The Mapfile models the timing behavior of each address region defined by a memory map file. Every bus access is then passed to a bus model (Flatmem), which performs the address decoding, and parses the access either to a simple memory model or to memory-mapped peripherals, such as a timer component or an interrupt controller.

Figure 3: ARMulator extended with modules [15]

Modules need to be written in C or C++ and are connected to the ARMulator as DLLs. An API is defined for the interconnection and the ARMulator extension kit provides the required header files, libraries and makefiles. The API consists of numerous functions to access inside variables of the simulator. This includes:

- read or write of a register or coprocessor value

- assert or read signals, e.g. interrupt signal

- set or get events, e.g. from the CPU/MMU or other modules, such as cache miss or address undefined instruction

- access any memory location (without interfering the actual bus simulation)

- control and access to the simulator internals, such as reading the cycle counter or adding other counters

- accessing the debugger, e.g. for printing messages on the debugger screen

The API also defines a number of auxiliary functions, helpful during the design of modules. For example, for every instruction set a disassembly API function exists, providing the disassembled line for a binary instruction code word. For actively including modules into the simulation process, callback functions can be registered in the simulator. The functions can be called at any of the following occasion:

- each instruction: for instruction tracing

- bus cycle: for inspecting bus behavior

- event: with installing event handler, this event can be caught within a module and perform a particular action in the module

- after a specific time (from now): e.g. to imitate delay behavior of real hardware

Bus modules can be considered as leafs of the memory architecture tree generated by the Flatmem module. They are called as soon as a memory access to their address range occurs.

The address range needs to be registered by the API function <code>ARMulif\_ReadBusRange()</code> and the module function, which serves the memory access within the module is registered with the API function <code>bus\_registerPeripFunc()</code>. Section 2.2.1.2 describes the definition of a generic bus module for memory-mapped devices.

Memory modules, such as the tracer module, are instanced by being linked into the memory chain. Starting from the core, every memory access is passed from one link in the memory chain to the next. Two memory busses are accessible to modules, the core memory bus and the external memory bus. The former is the connection between the core and the caches. The latter connects the caches with the memory subsystem if caches are available, otherwise memory and core bus are identical. Memory modules can link to both busses. The API functions ARMulif\_QueryMemInterface() provides a handle to a bus, which is required for connecting to the bus and for retrieving information about the bus type. The function AR-Mul\_InsertMemInterface() is then applied to insert the module into the memory chain and provided the simulator with the appropriate callback functions. The following section about the Tracer module gives an example of a memory module.

The ARMulator, as well as the modules, can be controlled by configuration files. These files specify module parameters or allow disabling a module, which might be required for speeding-up the simulation. Alternatively these parameters can be overwritten with values passed from the debugger, e.g. with command-line parameters of the debugger in order to modify the behavior of a module for the current simulation run.

For new processors, starting with the Cortex family, the ARMulator has been replaced with the Instruction Set System Models (ISSMs) [8], which no longer provide cycle-accuracy. Instead, in 2007 ARM presented the SOC Designer tool suite, which provides cycle-accurate processor and system models. In 2008 ARM discontinued the SOC Designer development and the tool was acquired by Carbon Design Systems. Thereafter ARM focuses on hardware-based profiling instead, which is supported by ARM RealView Profiler, see Section 2.3.2.3.

#### 2.2.1.1 The Tracer Module

The Tracer module is an extension for tracing numerous processor activities, such as instructions, memory accesses, register changes, and events, such as cache misses, and writes them to file. An example trace file is given in Listing 1.

| MSW4  | 0001A190  | 23C06023 |         |                   |

|-------|-----------|----------|---------|-------------------|

| BNR40 | 000080C0  | 28B00030 |         |                   |

| MNR40 | 000080C0  | 28B00030 |         |                   |

| IT    | 000080B8  | 8afffffb | BHI     | 0x80ac            |

| R     | r1=0001a1 | 194      |         |                   |

| BNR40 | 000080AC  | E2522010 |         |                   |

| MNR40 | 000080AC  | E2522010 |         |                   |

| BSR40 | 000080B0  | 28B01070 |         |                   |

| MSR40 | 000080B0  | 28B01070 |         |                   |

| BSR40 | 000080B4  | 28A11070 |         |                   |

| MSR40 | 000080B4  | 28A11070 |         |                   |

| IT    | 000080AC  | e2522010 | SUBS    | r2,r2,#0x10       |

| BSR40 | 000080B8  | 8AFFFFFB |         |                   |

| MSR40 | 000080B8  | 8AFFFFFB |         |                   |

| IT    | 000080B0  | 28b01070 | LDMCSIA | r0!, {r4-r6, r12} |

| R     | r2=000000 | 018      |         |                   |

| BNR4  | 00019FA0  | C023C184 |         |                   |

Listing 1: Example tracer file

The first letter of each line indicates the information type; the "M" stands for memory access on the core memory bus, "B" lines indicate an access on the external memory bus. The accessed address and data are supplied. Lines starting with an "I" indicate the executed instruction including the disassembly, the suffix "T" indicates that the instruction was taken. "R" shows changes in registers. Usually, for more complex software millions of cycles need to simulated, thus the trace files can become enormously large, in the range of gigabytes. Therefore, tracing a whole software execution with full trace information is not feasible. The tracer allows disabling specific trace information, limiting the address range for memory tracing and sub-sampling the tracing, i.e. only every n-th tracing sample will be written to the trace file. The trace file source code is part of the RealView environment.

The tracer module connects to the ARMulator with four interfaces. It installs itself as bus module on the core bus, for tracing every access to the instruction and the data cache. Furthermore it links into the external bus chain, for tracing cache and write buffer accesses to the external memory and other bus components, as shown in Figure 3. Instruction usage is analyzed by installing a so-called hourglass callback function, which is called each time a new instruction is decoded. The disassembly functions are used to produce the disassembly string depending on the current instruction mode. And finally, a callback function tracing various events is installed.

## 2.2.1.2 The Mapfile Module

The Mapfile module defines a timing behavior for bus devices. The timing is provided in wait states in terms of bus clock cycles. The Mapfile differentiates between read and write access times as well as between sequential and non-sequential accesses. The specific timing for sequential accesses can be used to emulate for example burst modes on the bus or page hits in DRAMs. Although this timing does not reflect the real behavior, at least it allows an approximation. For more detailed timing a DRAM timing module would be required. The Mapfile imitates the AMBA bus behavior in a simple manner.

| ;; start | size     | name  | width | access | read-times | write-times |

|----------|----------|-------|-------|--------|------------|-------------|

| 0000000  | 00010000 | ROM   | 2     | r      | 8/8        | 0/0         |

| 00010000 | 000F0000 | NOMEM | 4     | _      | 0/0        | 0/0         |

| 00100000 | 00100000 | SRAM  | 4     | rw     | 16/16      | 16/16       |

| 00200000 | 0080000  | DRAM  | 4     | rw     | 208/8      | 200/8       |

| 00A0000  | FF600000 | NOMEM | 4     | _      | 0/0        | 0/0         |

Listing 2: Timing definition for the Mapfile module

The timing parameters are defined in a file, a typical example of an embedded system architecture is given in Listing 2. The mapping defines a ROM with a size of 16 kB (0x10000 bytes) starting at address 0x0. The data width of the ROM is 16 bits (2 bytes) and the sequential and non-sequential read access times are 8 ns each. An SRAM resides at address 0x10000 with a size of 1 MB and read and write times of 16 ns.

The non-sequential access times (208 ns and 200 ns) of the DRAM component are much slower than the sequential times. This reflects the page architecture of DRAMs [45]. DRAMs are organized in pages of memory cells, which are activated at the same time. Pages have a size of typically 0.5 to 4 kB, and accesses within a page are served very fast. An access to another page results in a page miss. For accessing this new page a pre-charge is required, leading to a longer access time. Furthermore, if sequential accesses within a page occur, a burst mode can be used, decreasing the access time even further. This results in the short access times (8 ns) for sequential accesses to the DRAM.

Depending on memory bus speed the Mapfile calculates the resulting wait states. For example the 208 ns for a non-sequential read access to the DRAM lead to 25 wait states on a bus running at 125 MHz. Every access to a memory location from the processor simulator passes through the Mapfile module. The Mapfile evaluates the timing behavior for this access, and either passes the access to the memory, if no wait states occur, or triggers the wait signal on the bus.

#### **2.2.2** Automatic Simulator Generation – The Verilator

If simulators are not available for an existing processor or if the processor is a self-developed design, a model of the processor needs to be created. One choice is writing a model of the processor in software, for example in C. It is tricky to guarantee the consistency of the real hardware processor and the software model, as they are developed independently. This task becomes even more complicated if the processor design changes during development, for example the pipeline structure is rearranged or new instructions are added. One solution is to use the hardware description of the processor, if available, which is usually written in a hardware description language, such as Verilog or VHDL. Simulation tools exist for executing the hardware model, and a connection to the profiler can be established via specific external interfaces, for example via the so-called foreign or programming language interface (FLI, PLI). However, hardware simulation is usually performed on a nanosecond-accurate level. This implies long simulation time and delivers an accuracy, which is not required for the profiling. Another choice is to convert the HDL model to a faster and more abstract cycle-accurate model. Different tools exists to convert HDL models to SystemC or C, e.g. V2SC [68], Verilator [85], or VHDL-to-SystemC [98]. Within this work the Verilator tool is applied for automatic generation of a processor model. The tool takes a set of synthesizable Verilog code files and creates a C++ model of this code including a simulator environment. The result is a C++ class containing the top level module of the Verilog design and all lower level modules. The input and output ports of the top level module are converted to variables with the same name. In addition ports and signals of lower level modules are still visible.

The Verilator environment allows an easy testbench creation for the generated processor. Listing 3 shows the testbench for a C++ processor model called "Vtop". Similar to the HDL model the processor is operated with the reset signal and a toggling clock signal. The simulator is instructed to evaluate the input signal and generate the internal and output signals by calling the eval() function. Furthermore a tracing module is provided, which can be used to generate waveform of signals.

```

#include <verilated.h>

// Defines common routines

#include "Vtop.h"

// From Verilating "top.v"

// Instantiation of module

Vtop *top;

int main() {

top = new Vtop; // Create instance

top->reset 1 = 0; // Set some inputs

while (!Verilated::gotFinish()) {

if (main time > 10) {

top->reset l = 1; // Deassert reset

if ((main time % 10) == 1) {

top->clk = 1; // Toggle clock

if ((main time % 10) == 6) {

top->clk = 0;

```

```

}

top->eval(); // Evaluate model

cout << top->out << endl; // Read a output

main_time++; // Time passes...

}

top->final(); // Done simulating

}

```

Listing 3: Example code of a C++ testbench for a Verilator processor simulator [85]

## 2.3 Tools

This section presents tools for the design and profiling of embedded software. As an example of a software development suite, the RealView Developer Suite [14] for ARM processors is presented. It contains tools for compiling and building applications from source or assembly code targeted to a specific processor architecture. Development suites for other processors provide similar features and tools, for example the GNU Compiler Collection [36]. In the following sections a survey of existing profiling tools is given, which cover the analysis of performance, memory accesses and power consumption.

# 2.3.1 ARM Software Development Toolchain

ARM provides a toolchain for software development targeted to their processors, which is called RealView Developer Suite [14]. The development suite includes all tools required for software development, including compiler, linker, debugger and ISS.

Armcc [13] and armasm are the compiler and assembler for creating object files from software source code files. The tools support the compilation of ISO C, ISO C++ or ARM assembly code, respectively and are equipped with the standard library sets for C and C++ including file input/output and the Standard Template Library (STL). The code generation of the tools can be controlled with command-line options for creating code optimized for specific processor types and instruction sets, floating-point implementations and different optimizations targets, i.e. small code size or fast execution. Floating-Point operations can be either coded as assembly instructions or as calls to library functions. The former requires that the processor is equipped with a floating-point unit or an emulator. The tools can be instructed to include debug information, e.g. for use in a debugger, in order to map assembly code lines to C source code lines.

The object files created by armcc or armasm can either be first combined to a library with the armar achiever tool, or directly linked to an executable file with the linker utility (armlink). The linker creates an executable files from object and library files in the ARM Executable and Linking Format (ARM ELF). The linker defines the placement of the code and data segments of the input files in memory. Normally, code and data are partitioned in three regions:

- ER RO: read-only region for program code and constant data

- ER RW: read-write region for global variables

- ER ZI: zero-initialized region for data, which need to initialized with a zero value

The regions are usually placed consecutively in memory followed by the heap. As stack and heap grow toward each other, the stack is usually placed at a high address, in order to avoid a stack-heap collision. The placement of the regions can be controlled by command-line options of the linker, e.g. the start address and the grouping of regions. For a more comprehensive

definition of the memory map a so-called scatter-loading can be applied. Within a scatter file, the exact placement can be specified, see Listing 4.

```

ROM LOAD 0x0 {

ROM EXEC 0x0 {

vectors.o (Vect, +First)

* (+RO)

DRAM RW +0 {

.ANY (+RW)

}

DRAM ZI +0 {

.ANY (+ZI)

HEAP +0 UNINIT {

heap.o (+ZI)

TCM 0x04000000 0x2F40 {

tcm vars.o (+RO, +RW, +ZI)

}

STACKS 0x28080000 UNINIT {

stack.o (+ZI)

}

}

```

Listing 4: Example scatter file

The interrupt vectors and the startup code, defined in the file vectors of are placed in at address 0x0 followed by the RW and ZI region and the heap. A number of variables, defined in tcm\_vars.o, are placed in a fast tightly coupled memory (TCM), which is memory-mapped at location 0x04000000 with a size of 0x2F40. Finally, the stack is placed at address 0x28080000.

The executable files created by the linker can be preprocesses and examined by any ELF compatible tool. The RealView suite includes a tool called fromelf, which can be used for converting the executable into another format, e.g. binary format. Additionally it displays the content of an ELF file, including code disassembly, debug information, and symbol tables. In Section 4.1.1 it is shown, how the tool can be used for extracting function and variable names of the executable.

The tool suite provides two GUI-based debuggers and a command-line-based debugger called armsd for evaluating and debugging the code. The debuggers can either be used for observing code execution on real processor hardware or on a simulator. The connection to the execution unit is established via a DLL interface. For simulation the debugger connect to the ARMulator, which is described in Section 2.2.1 The ARMulator can be extended for simulating the behavior of surrounding memory-mapped hardware, e.g. memory, coprocessors or DMA controllers.

# 2.3.2 Cycle Profiling Tools

Profiling is a part of the software development process and describes the procedure of analyzing the execution behavior of software concerning different metrics. Table 2 gives an overview of existing profiling tools. They differ in the delivered analysis results, accuracy and supported processor architectures. The tools are explained in more detail in the following sections.

Table 2: Profiling tools

|                            | Cycles | Memory accesses | Power | Per function | Per line | Callgraph results | Instrumentation/<br>source code required | Accuracy                      | Embedded<br>processors |

|----------------------------|--------|-----------------|-------|--------------|----------|-------------------|------------------------------------------|-------------------------------|------------------------|

| Gprof                      | +      | -               | -     | +            | +        | +                 | +                                        | Sampling (10 ms)              |                        |

| Armprof                    | +      | -               | -     | +            | -        | +                 | -                                        |                               | ARM CPUs               |

| ARM RealView<br>Profiler   | +      | +               | -     | +            | +        | +                 | -                                        | Sampling (µs/ns) & estimation | ARM CPUs               |

| ATOMIUM                    | +      | +               | -     | +            | -        | +                 | +                                        |                               | Abstract model         |

| PowerEscape <sup>1</sup>   | +      | +               | +     | +            | -        | +                 | +                                        |                               | Abstract model         |

| VTune                      | +      | +               | -     | +            | +        | $+^2$             | -                                        | Sampling                      | Xscale, Intel x86      |

| HDL Profiling <sup>3</sup> | +      | +               | +     | -            | -        | -                 | -                                        | Ns                            | If HDL model available |

| Valgrind /<br>Callgrind    | +      | +               | -     | +            | +        | +                 | -                                        | Simulated CPU                 | Only x86/PPC           |

| SimpleScalar               | +      | +               | +     | -            | $+^4$    | -                 | -                                        | Simulated CPU                 | Synthetic model        |

| MEMTRACE                   | +      | +               | +     | +            | +        | -                 | -                                        | Cycle                         | if ISS available       |

<sup>&</sup>lt;sup>1</sup>no longer available

## 2.3.2.1 **Gprof**

Gprof [42] is a callgraph profiler, which was developed in the early 1980's at the University of Berkeley. It is based on the UNIX profiling tool prof [19] and became part of the BSD-UNIX system. With some enhancements gprof also became part of the binutils package [35] and is therefore available on all GNU/Linux systems. Thus, gprof became a widely-used profiling tool for software analysis and optimization.

Gprof is based on instrumentation of the source code. This process is performed by the compiler and needs to be enabled by designer manually, i.e. the gcc compiler provides the "-pg" option for this purpose. During instrumentation, see Section 3.3.2.1 for more details, the source code is enhanced with code fragments, which are responsible for generating profiling data during execution of the program. After finishing the program execution, the collected profiling information is written to a file, which can be further processed by the profiler. Gprof basically provides two different profiles, a flat profile as depicted in Listing 5 and a callgraph profiling shown in Listing 6.

```

Each sample counts as 0.01 seconds.

용

cumulative

self

self

total

time

seconds

seconds

calls

us/call

us/call

name

65.84

15.60

15.60

20000

780.22

883.96

b

```

<sup>&</sup>lt;sup>2</sup>not for embedded processors

<sup>&</sup>lt;sup>3</sup>very slow

<sup>&</sup>lt;sup>4</sup>per assembly address

| 17.51 | 19.75 | 4.15 | 40000 | 103.74 | 103.74 | С |

|-------|-------|------|-------|--------|--------|---|

| 17.13 | 23.81 | 4.06 | 20000 | 202.97 | 306.71 | а |

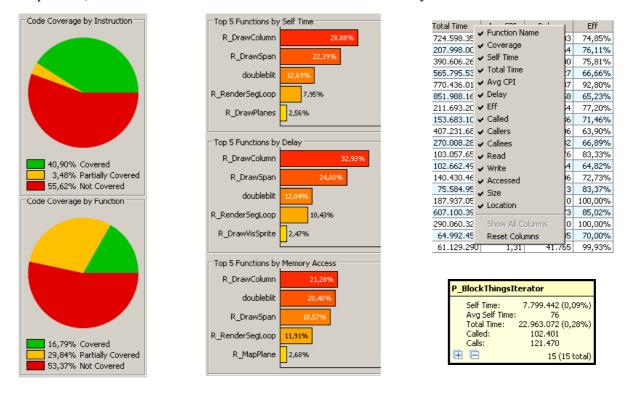

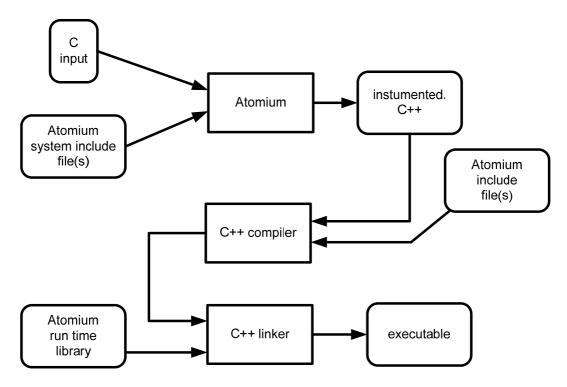

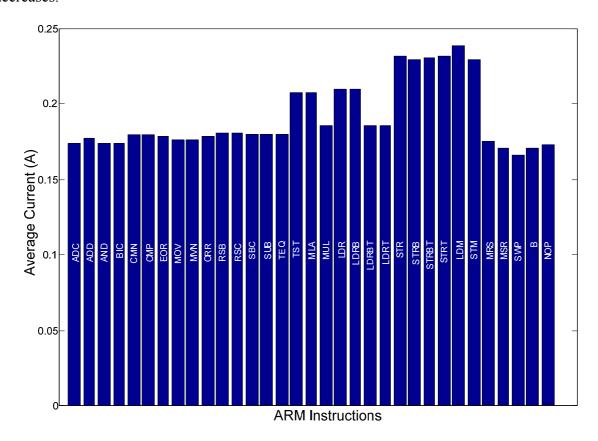

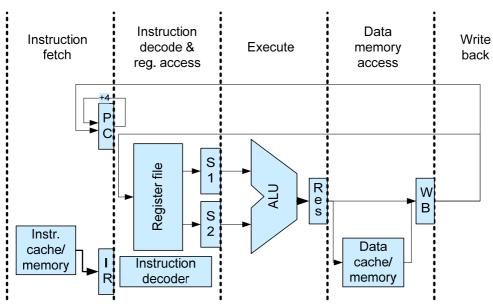

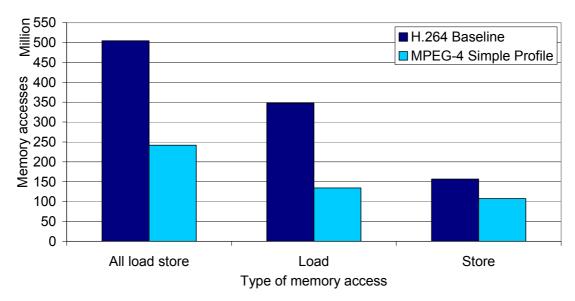

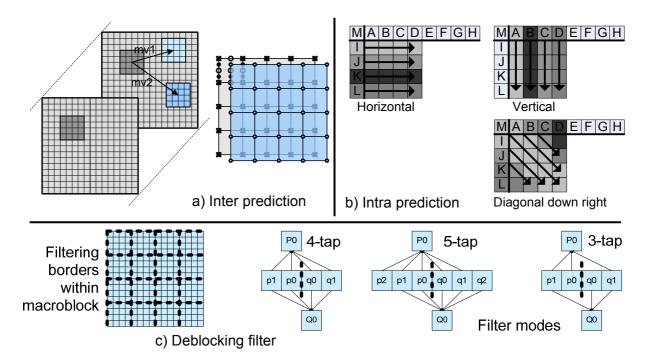

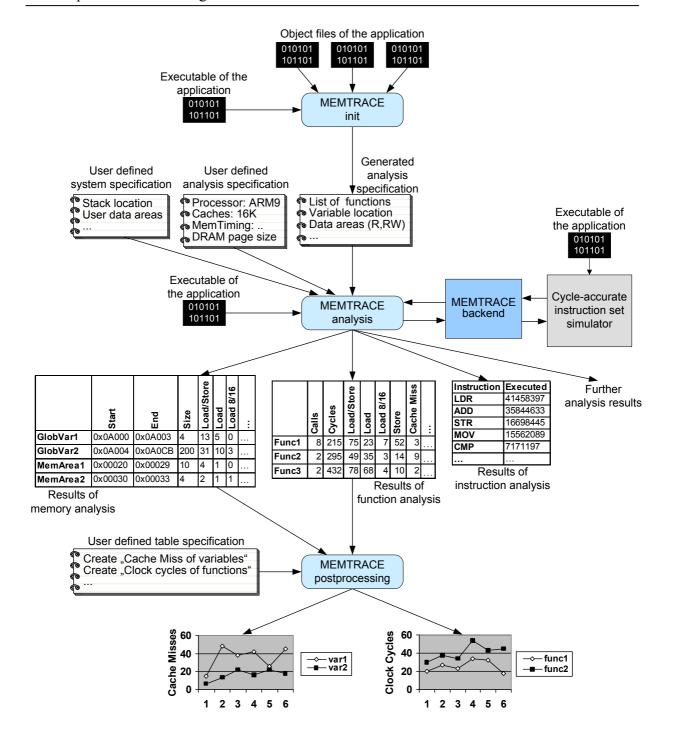

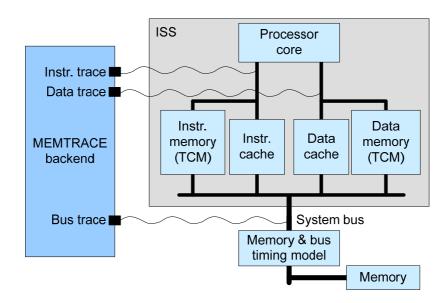

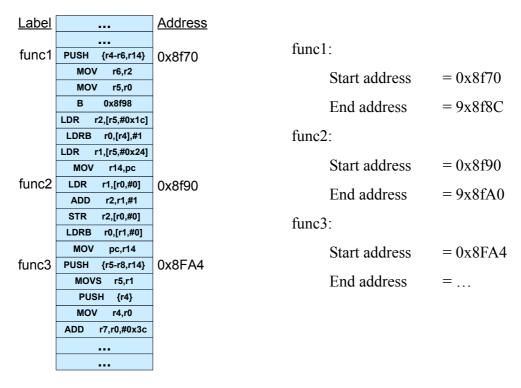

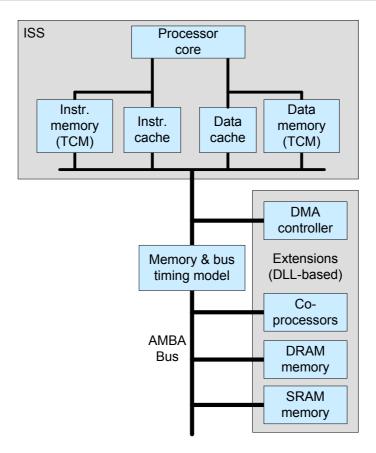

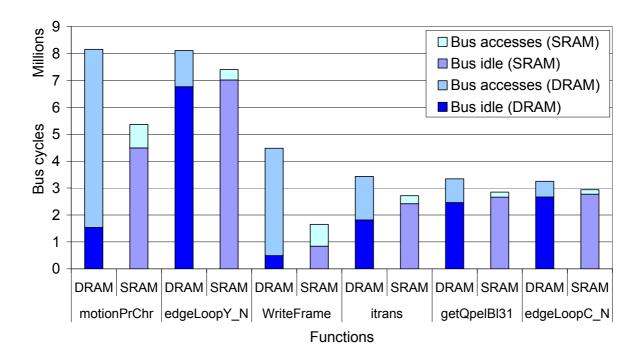

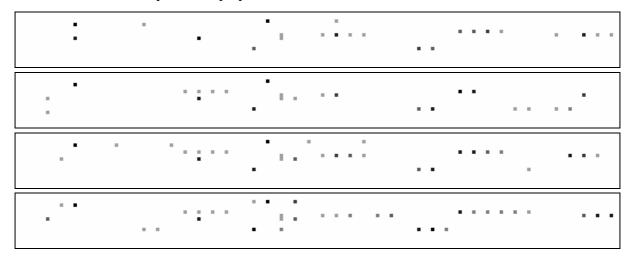

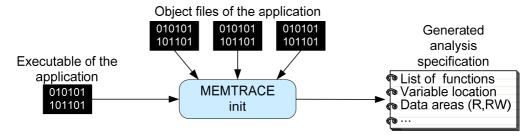

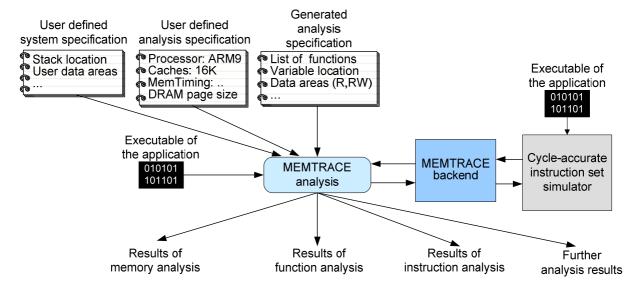

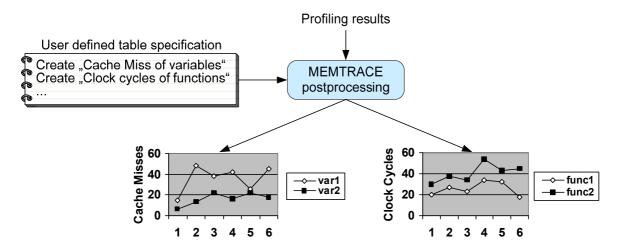

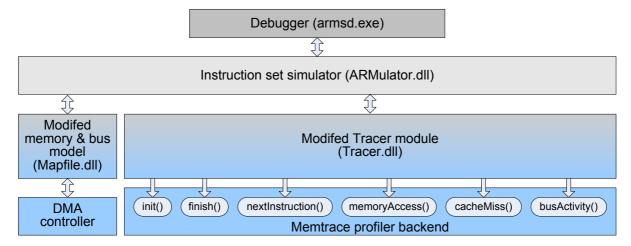

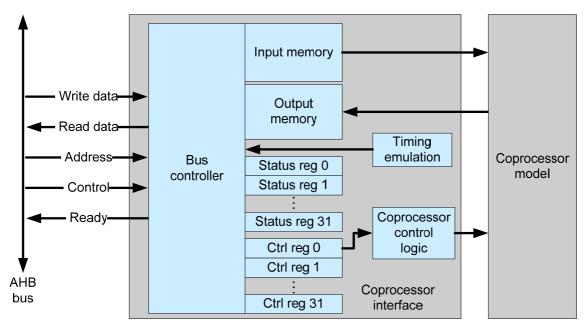

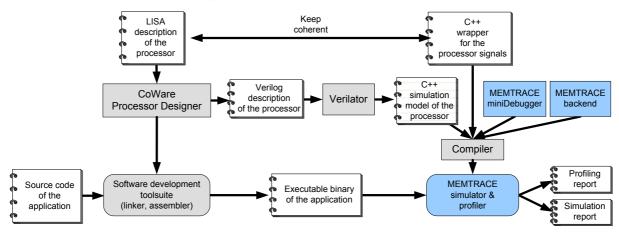

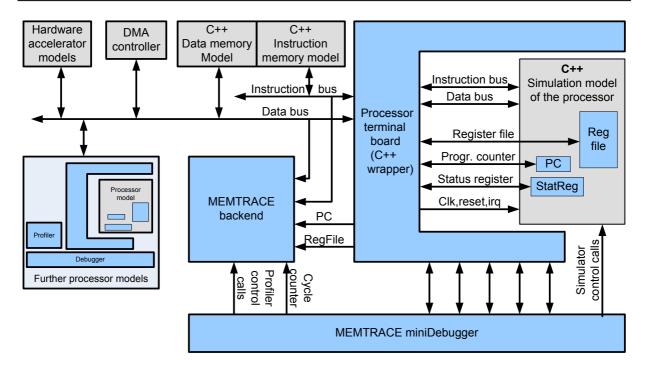

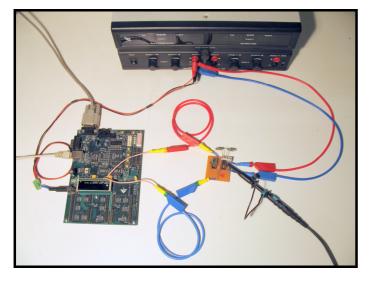

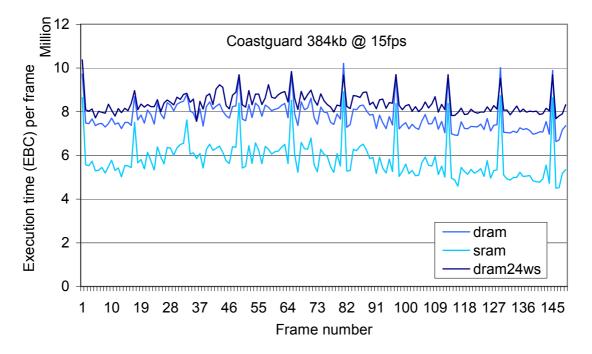

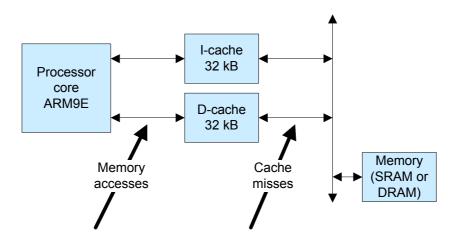

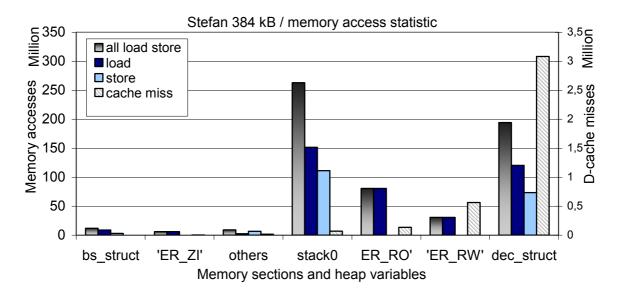

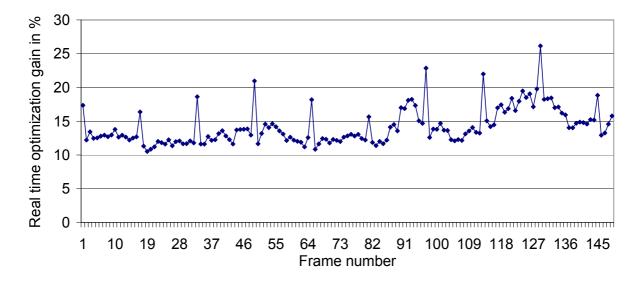

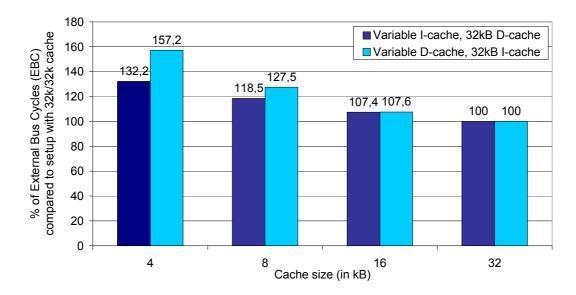

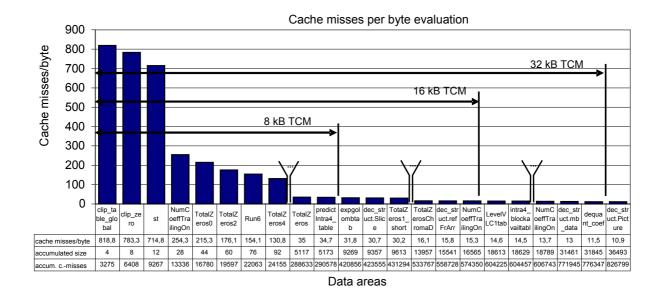

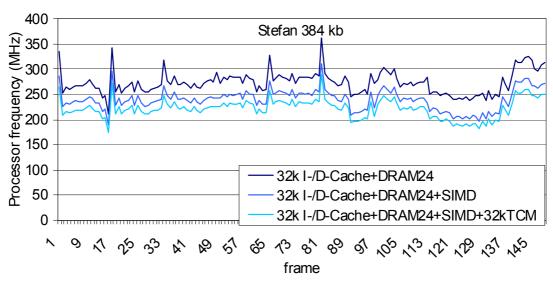

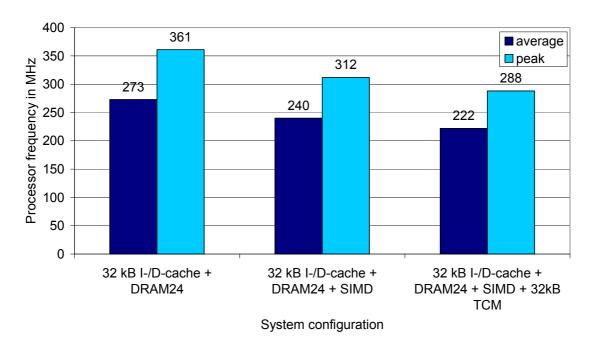

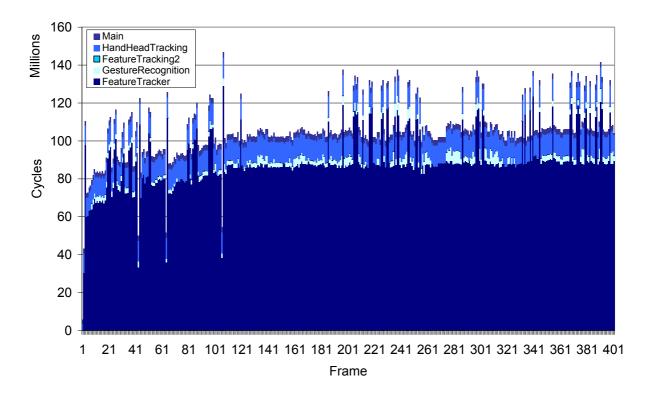

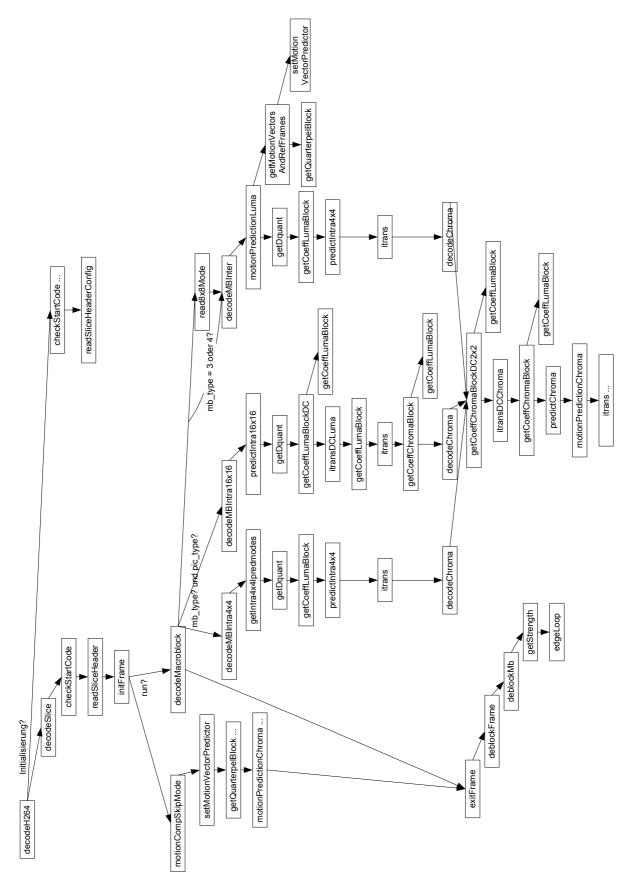

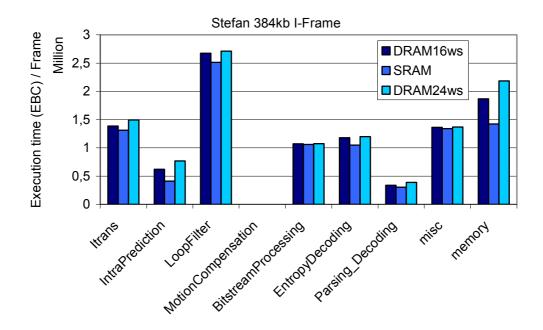

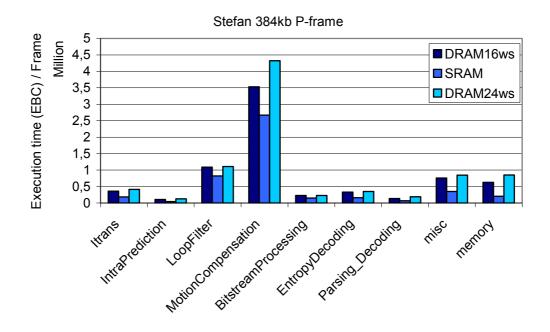

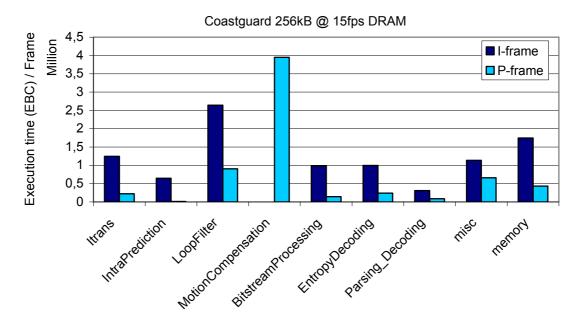

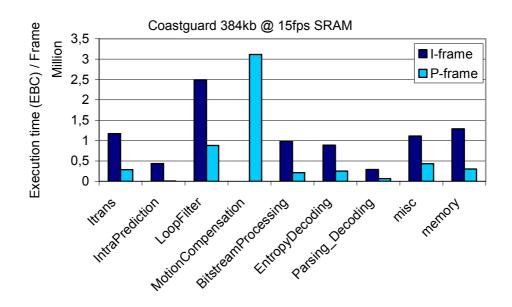

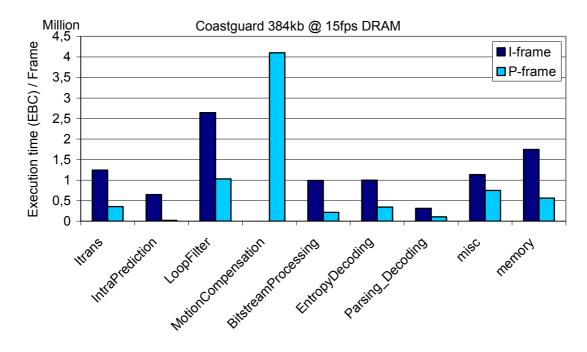

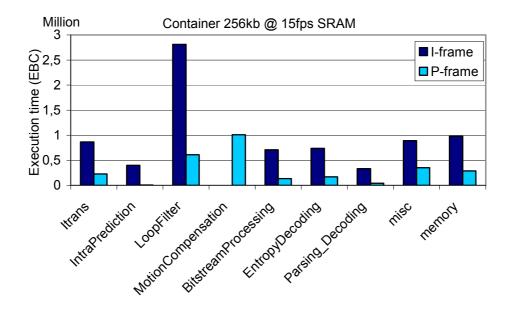

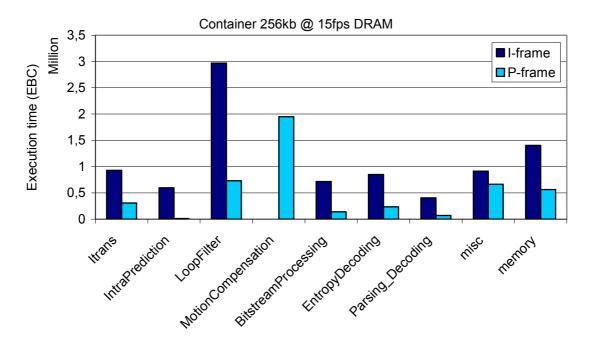

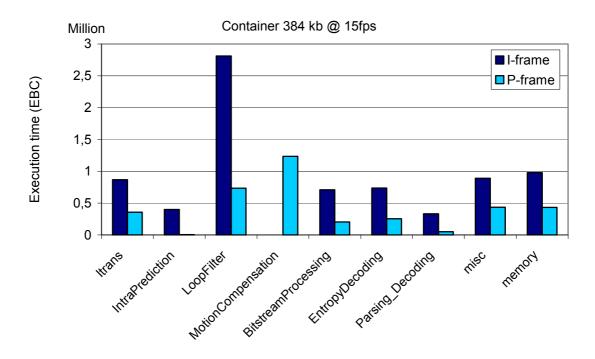

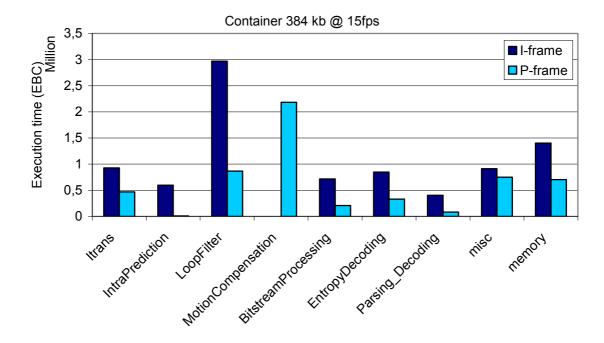

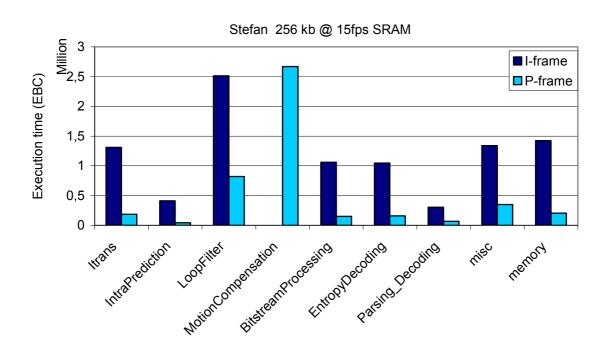

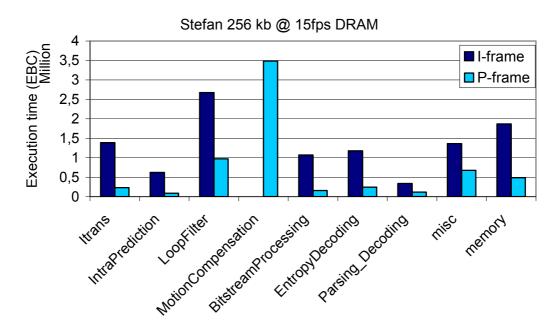

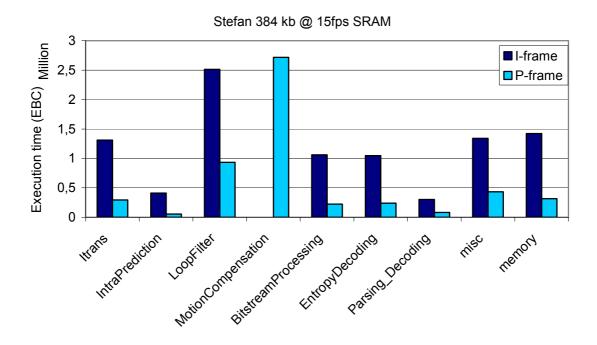

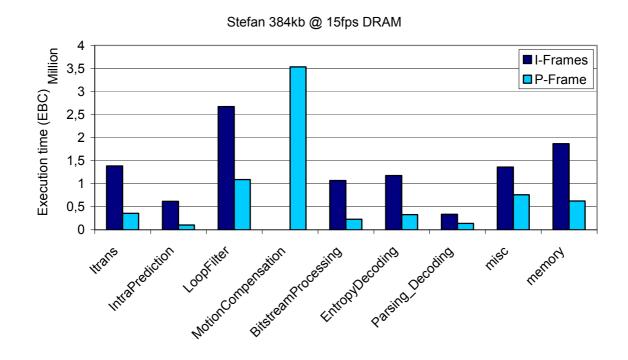

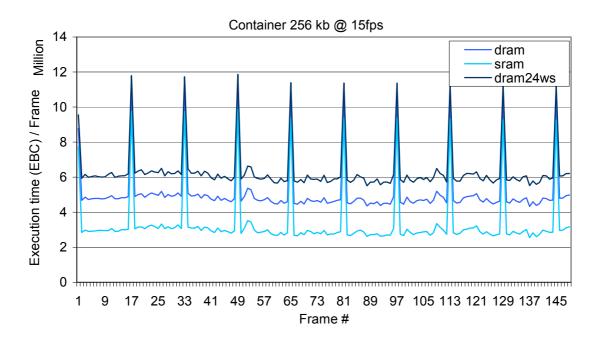

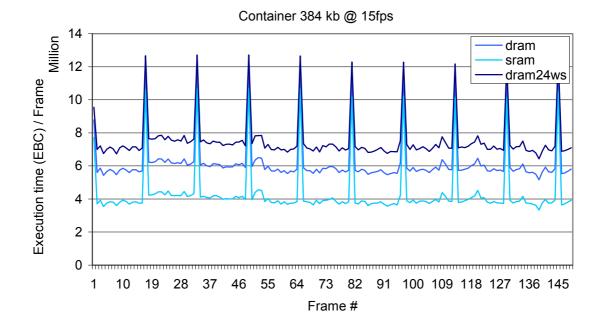

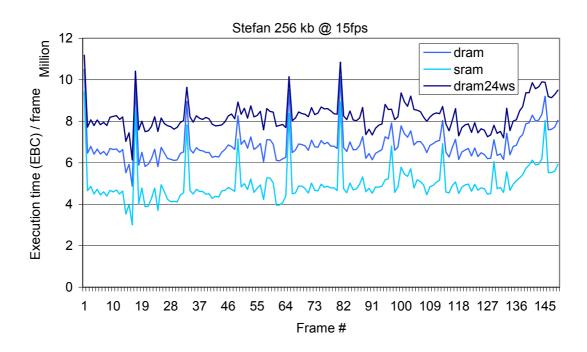

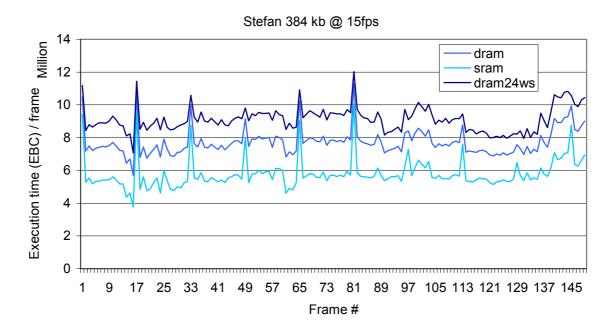

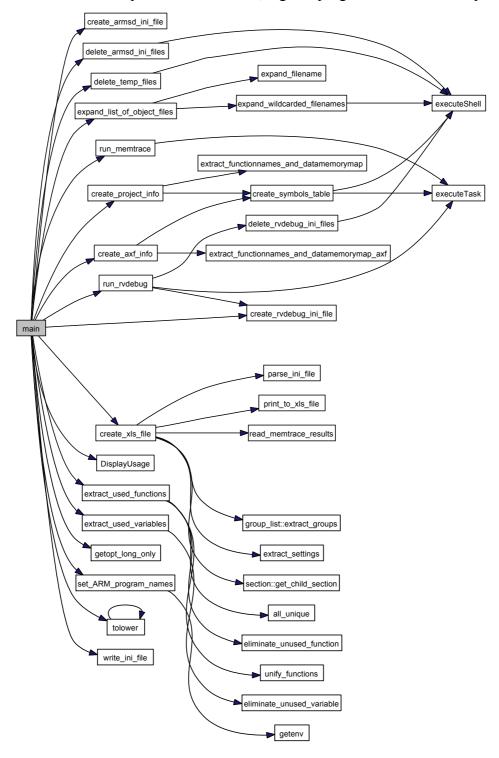

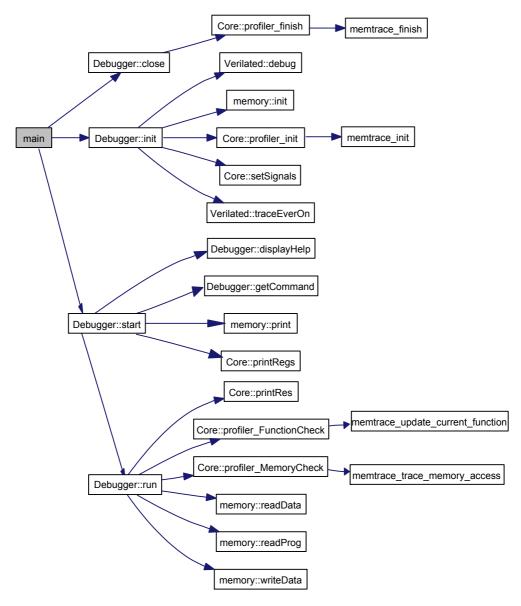

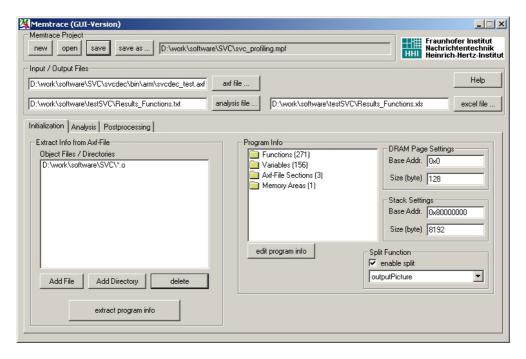

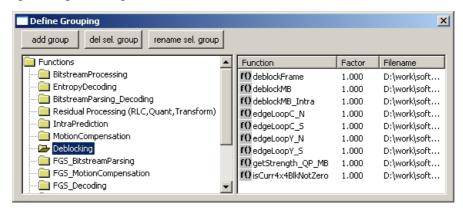

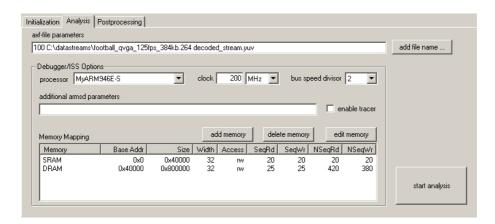

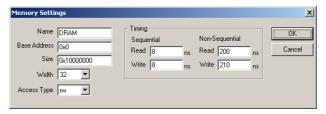

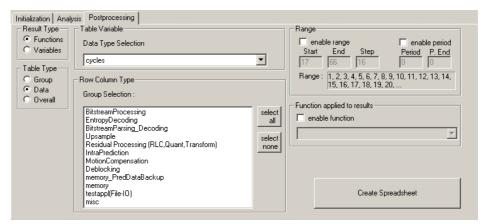

Listing 5: Gprof flat profile