## AlGaN/GaN HEMTs Reliability: Degradation Modes and Analysis

vorgelegt von

Master of Physics

Ponky Ivo

aus Jakarta

von der Fakultät IV - Elektrotechnik und Informatik der Technische Universität Berlin zur Erlangung des akademischen Grades

Doktor der Naturwissenschaften -Dr.rer.nat.-

genehmigte Dissertation

#### Promotionsausschuss:

Vorsitzender: Prof. Dr.-Ing. W. Heinrich

Berichter: Prof. Dr. G. Tränkle Berichter: Prof. Dr.-Ing. C. Boit Berichter: Prof. Dr. M. Kuball

Tag der wissenschaftliche Aussprache: 24. Mai 2012

Berlin 2012 D 83

## Acknowledgments

I would like to thank Professor Dr. Günther Tränkle for giving me the chance to work at Ferdinand-Braun-Institut für Höchstfrequenztechnik (FBH). His guidance through discussions not only encourage me to work and dig more GaN reliability studies, but also build up my knowlegde and broaden my horizon.

A respectful thank I would like to address to Dr. Joachim Würfl for fruitful discussions and his willingness to share his broad knowledge and long experience in GaN areas. I highly apreciate his hardworking attitude and nurture skills which are very good examples for me professionally and personally.

I am very grateful to Dr. Richard Lossy to whom I can ask a lot of questions regarding GaN process technology and reliability problems.

My learning process in Germany would not be possible without DAAD funding. I am grateful to Fr. Kasperek and Mbak Endah for their assistance and guidance prior to my departure from Jakarta as well as my stay in Berlin.

During my PhD work, there were some collaborations on GaN reliability studies. Therefore, I would to express my gratitude to Professor Christian Boit group at Technische Universität (TU) Berlin, Professor Martin Kuball and Dr. James Pomoroy at University of Bristol, Professor Gaudio Meneghesso at University of Padova, and Dr. Tim and Fr. Sandy Schaaf at Max Born Institute.

Special thanks to Dr. Arkadiuzs Glowacki at TU Berlin for teaching me how to use PEM machine. Thank you very much for your trust and sharing your lab skills. I would like to thank to Dr. Ute Zeimer for her assistance in analyzing the samples and discussing the results of EDX, CL and FIB. Thanks also to Fr. Lawrenz for FIB-ing assistance. And to Dr. Anna Mogilatenko and Dr. Holm Kirmse at Humboldt University, I thank for their corporation and fruitful discussions concerning FIB, lamella transfer, EDX and TEM investigations. Special thanks to Anna for her valuable corrections for my thesis.

Thanks to ex-Büro colleagues: Reza, Paul, Tomas and Mathias. Special

thanks to Nidhi for her useful tips for academic matters and for living in Germany happilly. Eldad Bahat-Treidel, thank you for wafers supply and simulations (you surprised me with Indonesian greeting in the first day I worked!). And Kotara, many thanks for your efforts in FIB and discussions. Thanks for inputs and discussions to other GaN group members. To Melanie, thanks for your willingness to share your feedbacks, findings and feelings as well.

My four year work cannot be accomplished without help from wonderful measurement guys: Lars who is always cooperative and very helpful, Stephan and Steffen who nearly don't mind their DIVA measurements to be interrupted, Hai Bang and Marko who almost do *Aufbau* work quickly for me. Also thanks to Armin, for your assistance and sharing your long experience. It is also good to work with nice persons in bending measurements so I thank Hr. Roos, Ben and Irene.

I would like also to address my sincere gratitude to Claudia, du bist ein Schutzengel. Thanks to Ngoc for her companion working in the weekend. I thank other Ladies Night (LN) members of FBH. Thanks to Sabir, Aga, Olof and Thomas for free advices which most of them make me laugh: D.

I am indebted to friends who are always there for me for good and bad times in DE especially: Ican, Yuni and Rere, Jeung Lyza and Mas Ken, Eva, Ratri, Riska. Special thanks to friends who always support me no matter how far we are: Rientha, Lina, Yayah, Rosie, Mutiara and Yenni for their patience in listening to my stories. To Alex and Bernt, thanks for your understanding during my stressful time. Thanks also to my friends in Groningen: Uyung, Puri, Amel and Iging for sharing our desperado period during PhD and supporting each other. Thanks to Mesjid Al-Falah (IWKZ) where I can satisfy needs of my soul and stomach. Thanks to DIBVM where I enjoy playing badminton every saturday and to DAAD 2007 members for sharing our experience and support. Special thanks to Bang Aji for his important contribution which brightens my life in Berlin.

My study far away from home would not be blessed without my parents' prayers. I thank Allah, The Almighty, for giving me wonderful parents and a warm big family. Thank you very much for your endless support, love and encouragements.

Berlin, February 2012

## Abstract

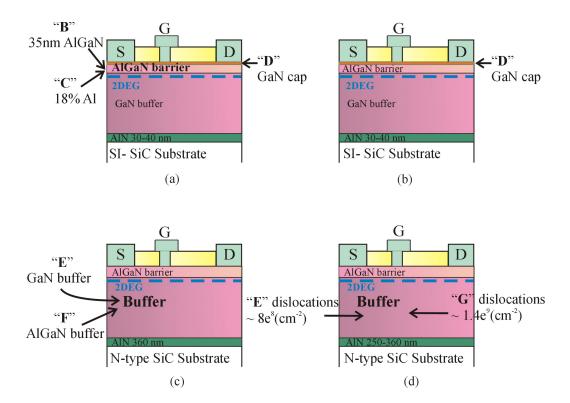

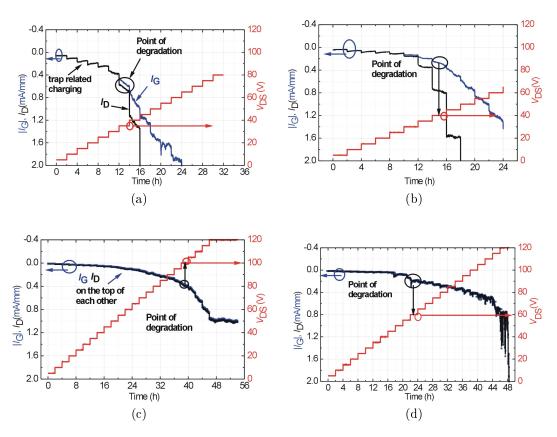

AlGaN/GaN HEMTs reliability and stability issues were investigated in dependence on epitaxial design and process modification. DC-Step-Stress-Tests have been performed on wafers as a fast device robustness screening method. As a criterion of robustness they deliver a critical source-drain voltage for the onset of degradation. Several degradation modes were observed which depend on epi design, epi quality and process technology. Electrical and optical characterizations together with electric field simulations were performed to get insight into respective degradation modes. It has been found that Al-GaN/GaN HEMT devices with GaN cap show higher critical source-drain voltages as compared to non-capped devices. Devices with low Al concentration in the AlGaN barrier layer also show higher critical source-drain voltages. Superior stability and robustness performance have been achieved from devices with AlGaN backbarrier epi design grown on n-type SiC substrate. For the onset on any degradation modes the presence of high electrical fields is most decisive for on- and off-state operation conditions. Therefore careful epi design to reduce high electric field is mandatory. It is also shown that epi buffer quality and growth process have a great impact on device robustness. Defects such as point defects and dislocations are assumed to be created initially during stressing and accumulated to larger defect clusters during device stressing. Electroluminescence (EL) measurements were performed to detect early degradation. Extended localized defects are resulting as bright spots at OFF-state conditions in conjunction with a gate leakage increase.

## Zusammenfassung

$AlGaN/GaN\ HEMTs\ mit\ unterschiedlichen\ epitaktischen\ Designs\ und\ Prozess$ modifikationen wurden auf ihre Zuverlässigkeit und Stabilität untersucht. DC-Stufenstresstests wurden als Screeningmethode für die Bauelementrobustheit durchgeführt. Mit dieser Methode erhält man eine kritische Source-Drain-Spannung, die den Beginn der Degradation kennzeichnet. Verschiedene Degradationsmodi wurden beobachtet, die vom epitaxialem Design, der epitaxialen Qualität und der Prozesstechnologie abhängen. Elektrische und optische Messungen zusammen mit elektrischen Feldsimulationen wurden durchgeführt, um Einblick in das Degradationsverhalten zu bekommen. Es hat sich gezeigt, dass AlGaN/GaN HEMTs mit einer GaN Cap-Schicht eine höhere kritische Drain-Source-Spannung zeigen als Transistoren ohne diese Schicht. HEMTs mit niedriger Aluminiumkonzentration in der AlGaN-Barriere zeigen ebenfalls eine höhere kritische Drain-Source-Spannung. Transistoren mit AlGaN-Backbarrier, die auf n-Typ SiC-Substraten gewachsen wurden, zeigen eine besonders hohe Stabilität und Robustheit. Für den Betrieb im On-State als auch im Off-State ist ein hohes elektrisches Feld entscheidend für den Beginn der Degradation. Daher sind epitaxiale Designs, die das elektrische Feld so weit wie möglich reduzieren, von großer Wichtigkeit. Es wird gezeigt, dass die Qualität der Bufferschicht und der Wachstumsprozess der epitaxierten Schichten großen Einfluß auf die Robustheit der Bauelemente haben. Zu Beginn des Stressprozesses werden Punktdefekte und Versetzungen erzeugt, die im weiteren Verlauf des Stresstests zu Agglomeration von Defektclustern führen. Der Beginn der Degradation wurde mit Hilfe der Elektrolumineszenz untersucht. Im Off-State werden ausgedehnte lokalisierte Defekte als stark leuchtende Flecken detektiert, wobei gleichzeitig ein Anstieg der Leckströme zu beobachten ist.

## Author's Declaration

This thesis is submitted to Technische Universität Berlin in support of an application for admission to the degree of Dr. rer. nat. I hereby declare that this thesis is my own work and effort and that it has not been submitted anywhere for any award. Where other sources of information have been used, they have been acknowledged. The work was carried out between September 2007 and February 2012, under supervision of Professor Günther Tränkle.

Ponky Ivo February 2012

## Contents

| A            | ckno  | wledgments                                                   | iii          |

|--------------|-------|--------------------------------------------------------------|--------------|

| $\mathbf{A}$ | bstra | nct                                                          | $\mathbf{v}$ |

| Zι           | usam  | menfassung                                                   | vii          |

| A            | utho  | r's Declaration                                              | ix           |

| 1            | Inti  | roduction                                                    | 1            |

|              | 1.1   | A short story of GaN                                         | 1            |

|              | 1.2   | GaN structure                                                | 2            |

|              | 1.3   | Substrate options                                            | 2            |

|              | 1.4   | ${\rm AlGaN/GaN}$ high electron mobility transistors (HEMTs) | 5            |

|              | 1.5   | The status of GaN reliability                                | 8            |

|              |       | 1.5.1 Heckmann diagram: crystal properties relations         | 11           |

|              | 1.6   | Structures of this thesis                                    | 12           |

| 2            | Alc   | GaN/GaN HEMT device fabrication                              | 13           |

|              | 2.1   | Motivation                                                   | 13           |

|              | 2.2   | Epitaxy                                                      | 13           |

|              | 2.3   | Process Technology                                           | 16           |

|              | 2.4   | Defects                                                      | 18           |

| 3            | Dev   | vice stressing and characterizations                         | 25           |

|              | 3.1   | Robustness tests                                             | 26           |

|              | 3.2   | Long term lifetime tests                                     | 26           |

|              | 3.3   | Electrical characterizations                                 | 28           |

|              | 3.4   | Optical characterizations                                    | 32           |

|              | 3.5   | Localized structural analysis                                | 35           |

| 4            | Des   | sign of experiments                                          | 39           |

|              |       | Motivation                                                   | 39           |

| 5  | Res          | ults                                                           | 4            | 3              |

|----|--------------|----------------------------------------------------------------|--------------|----------------|

|    | 5.1          | GaN HEMTs critical voltage determination by DC-Step-Stres      | $\mathbf{S}$ |                |

|    |              | tests                                                          |              | 4              |

|    |              | 5.1.1 Strain in AlGaN layer                                    | 4            | 18             |

|    |              | 5.1.2 Gate Technology and Substrate type                       |              | 0              |

|    |              | 5.1.3 Summary                                                  |              | 60             |

|    | 5.2          | Influence of GaN cap on robustness of AlGaN/GaN HEMTs          |              | 1              |

|    |              | 5.2.1 Electroluminescence                                      |              | 64             |

|    |              | 5.2.2 Electric Field simulation                                |              | 57             |

|    |              | 5.2.3 Summary                                                  |              | 68             |

|    | 5.3          | Comparative study of AlGaN/GaN HEMTs robustness versu          |              |                |

|    |              | buffer design variations                                       |              | 68             |

|    |              | 5.3.1 Characterization by Electroluminescence                  |              | 3              |

|    |              | 5.3.2 Simulations of band diagrams and internal electric field |              |                |

|    |              | distribution                                                   |              | 66             |

|    |              | 5.3.3 Summary                                                  |              | 8              |

|    | 5.4          | Degradation mechanisms of GaN HEMTs in dependence of           |              |                |

|    |              | buffer quality and gate technology                             |              | 9              |

|    |              | 5.4.1 Electroluminescence                                      |              | $\overline{2}$ |

|    |              | 5.4.2 Summary                                                  |              | 7              |

| 6  | Gal          | N reliability interpretations                                  | 8            | 1              |

|    | 6.1          | Nature of leakage during pinched-off stress                    | 8            | 2              |

|    | 6.2          | Electroluminescence at ON- and OFF-state                       |              | 5              |

|    |              | 6.2.1 Electroluminescence at OFF-state                         | 8            | 6              |

|    |              | 6.2.2 Electroluminescence at ON-state                          |              | 6              |

|    | 6.3          | TEM investigations of dislocations                             | 9            | 1              |

| 7  | Cor          | nclusions and Outlook                                          | 9            | 3              |

| Li | ${ m st}$ of | Publications/Conferences                                       | 9            | 7              |

|    |              | ranhv                                                          | 9            | 9              |

## Chapter 1

## Introduction

#### 1.1 A short story of GaN

The first gallium nitride (GaN) compounds were prepared by reacting ammonia gas with metallic gallium at high temperatures in 1932 by Johnsonn etal. [1]. Their work showed its remarkable stability toward heat, solutions of acids and bases. Almost four decades later Maruska et al. [2] and Pankove et al. [3] characterized the optical properties of GaN and determined the direct band gap to 3.36 - 3.39 eV at room temperature. A few years later the GaN bandstructure and its reflectivity were computed by the empirical pseudopotential method [4]. Bloom et al. predicted GaN as a promising material for luminescence devices and laser applications due to its wide direct band energy. In the following years, Ilegems and Montgomery [5] suggested that the n-type conductivity of GaN semiconductor behaviour is due to native defects. Their conclusions were widely debated. The question was whether n-type conductivity was due to native defects or impurities. Several groups continued their work intensively on point defects and most comprehensive point defects studies are contributed by Neugebauer and Van de Waal [6]. They proposed that unintentional donor impurities and gallium vacancies are responsible for n-type conductivity of GaN rather than the long believednitrogen vacancy [7]. Other noticable work on charged point defects which control numerous defect properties of semiconductors have been published by Seebauer and Kratzer [8].

In early 90's, the first p-n junction LED GaN fabrication was reported by a Japanese group [9]. Earlier reports of improving crystalline quality of GaN by inserting a thin AlN nucleation layer to accommodate lattice constant mismatch of sapphire substrate was reported by Yoshida *et al.* and Akasaki *et al.* [10, 11]. In early 90's Khan *et al.* for the first time observed a 2-dimensional electron gas (2DEG) at the interface between AlGaN and GaN layers [12]. Since then, research of AlGaN/GaN high electron mobility transistors (HEMTs) towards improving technology for improved performance and novel application was intensively pursued by numbers of groups [13, 14, 15, 16, 17]- to mention a few.

Mishra's recent overview provided impressive data of RF performance of GaN HEMTs stand: 13.7 W/mm at 30 GHz, 10.5 W/mm at 40 GHz, and 2.4 W/mm at 60 GHz and the fastest GaN devices today at a cut-off frequency of 220 GHz and a maximum oscillation frequency of 400 GHz [18]. However, GaN-based devices have shown short-term instabilities including collapse of DC IV-characteristics, and high leakage currents. This urges comprehensive reliability studies which are the main purpose of this thesis. It is important to investigate the main cause of GaN HEMTs degradation i.e. temperature and/or electric field dependencies through detailed investigations from material growth to process technology.

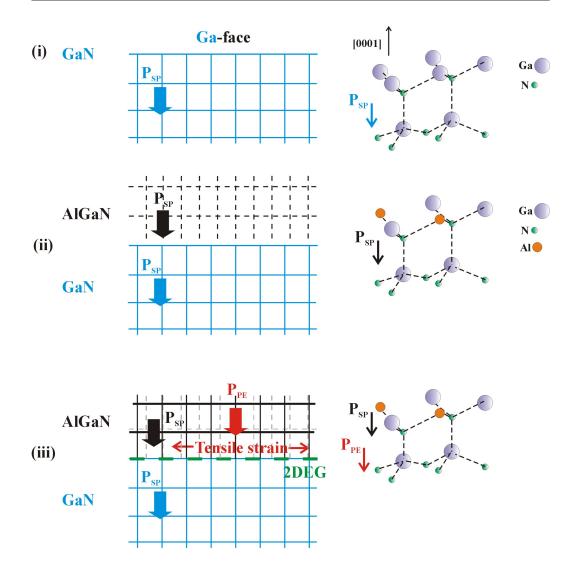

#### 1.2 GaN structure

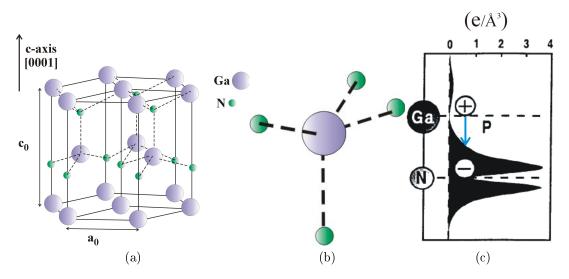

Group III-nitrides can crystallize in three possible crystal structures: the wurzite (WZ) structure, the zinc-blende structure and the the rocksalt structure. The GaN WZ structure has a hexagonal unit cell and is thermodynamically more stable than other structures such as zinc blende or rocksalt structures [19]. The wurtzite (WZ) structure is non-centrosymetric (i.e. it lacks of inversion symmetry) and displays piezoelectric effect. The asymmetry of Ga-N bonding between the longer bond and the shortest bond in a tetrahedral atom arrangement leads to a permanent dipole along the c-axis (see Fig. 1.1b). Ga-N bond is highly polarized with the electrons located mostly near the nitrogen atom [20] (see Fig. 1.1c). The spontaneous polarization of GaN crystal by convention is along [0001] direction [21] (see Fig. 1.2). Any stress accommodated during the heteroepitaxial GaN growth changes the lattice parameter along the c-axis, leading to an additional piezoelectric polarization. Piezoelectric constant of AlN, GaN and InN with WZ structure have are up to ten times larger than those of conventional III-V and II-VI semiconductor compound [22].

#### 1.3 Substrate options

The successful growth of GaN epitaxial layer on foreign substrates has to consider several aspects: lattice mismatch, thermal conductivity and price.

Figure 1.1 GaN (a) wurtzite structure, (b) tetrahedral configuration, and (c) charge distribution of valence electrons.

Figure 1.2 Ga-polarity and N-polarity crystals with each polarization direction (blue arrow)[13].

Historically, sapphire (Al<sub>2</sub>O<sub>3</sub>) was the first substrate for GaN-based devices, but it is not that favorable for RF and high power device applications due to its poor thermal conductivity (0.2-0.5 W/cm K). Moreover, GaN growth on sapphire has big lattice mismatch 13-16 % [23, 24]. The most favorable GaN substrate for microwave applications is SiC which is good in terms of thermal conductivity of 5 W/cm K, less expensive and provides a comparable low

lattice mismatch  $\sim 3.4$  % [25]. Growing GaN-based device on SiC substrate with AlN nucleation layer, the strain can be smaller  $\sim 0.5$  % [26].

Another option are Si substrates which are cheaper than SiC substrates and have a thermal conductivity of 1.5 W/cm K. Disadvantage is the higher lattice mismatch about 16.9 % [27] which causes strong tensile strain. The best substrate to grow GaN-based device is a freestanding GaN substrate with advantages, of course, no lattice mismatch and good thermal conductivity (1.3 W/cm K). Recently, it was reported a very low thermal impedance of AlGaN/GaN HEMTs on diamond substrate is 4.1 K mm/W due to high diamond thermal conductivity of 22 W/cm K) [28]. However, GaN growth on diamond has large lattice mismatch which causes severe strain and wafer bowing [29] (see Table 1.1).

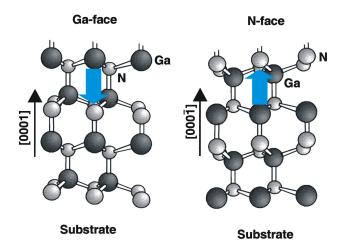

Fig. 1.3 shows estimations of the annual wafer production for each substrate type. For large volume production the Si substrate is the most attractive option for power electronics applications. Fre standing GaN substrates are good for optoelectronic applications since they are very sensitive to vertical dislocations. For microelectronic applications, still SiC substrate is favorable.

Figure 1.3 Substrate cost per square centimeter estimation in annual wafer production [30].

| Substrate | $\operatorname{Advantage}$                                | Disadvantage                     |  |  |

|-----------|-----------------------------------------------------------|----------------------------------|--|--|

| GaN       | lower relative defect density,                            | difficult to produce large-      |  |  |

|           | lower leakage current, higher de-                         | diameter single-crystal GaN      |  |  |

|           | vice yield, good for optoelec-                            | substrate, expensive             |  |  |

|           | tronic applications                                       |                                  |  |  |

| Diamond   | high thermal conductivity,                                | large lattice mimatch causes se- |  |  |

|           | higher operating power density                            | vere strain and bowing, not easy |  |  |

|           | and temperature capabilities                              | to deposit GaN                   |  |  |

| Si        | offers integration with Si IC lower thermal conductivity, |                                  |  |  |

|           | technologies, large diameter sub-                         | ogies, large diameter sub-       |  |  |

|           | strate                                                    |                                  |  |  |

Table 1.1 Summary of alternative to SiC substrate for GaN-based device [29]

## 1.4 AlGaN/GaN high electron mobility transistors (HEMTs)

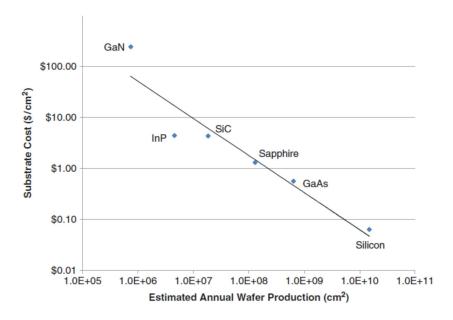

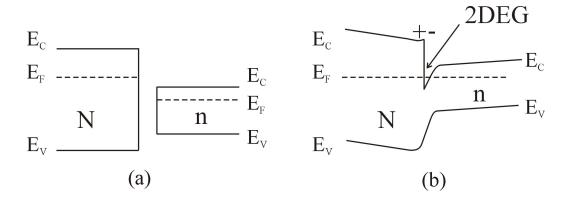

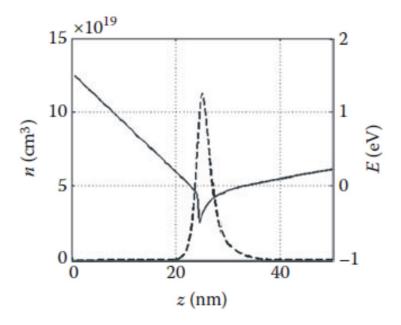

AlGaN/GaN HEMTs are fabricated at FBH by metal organic vapour phase epitaxy (MOVPE) in crystal direction (0001) with gallium face surface. On the top of the GaN buffer layer, a thin AlGaN layer is deposited. At the interface of this heterostructure, a 2DEG is formed (see Fig. 1.4). When two different semiconductors are in contact in the absence of an external bias voltage, the equilibrium is reached by lining up the Fermi level and bending the band diagram accordingly. This can create triangully shaped quantum well structure at the interface. The necessary band bending is a consequent to the transfer of electrons from semiconductor with larger band gap (i.e. AlGaN) to lower band gap (i.e. GaN). The transfer of electrons to occupy lower energy states continues until the Fermi level is the same on both sides of heterostructures [31, 32]. The electrons occupy energy states in the triangular potential well the so called 2DEG such that electrons have quantized energy and are free to move in a two dimensional plane parallel to the interface.

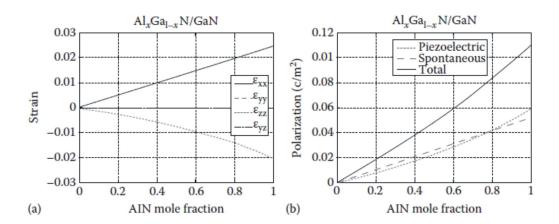

The AlGaN crystal has a smaller lattice constant than GaN crystal because the Ga atom in GaN crystal is replaced by smaller sized Al atom. Consequently, the AlGaN a-axis lattice spacing must stretch to match to the underlying GaN lattice (see Fig. 1.5). This causes the c-axis of the AlGaN layer to contract and the lattice is unrelaxed and an additional piezoelectric polarization  $P_{PE}$  in AlGaN layer occurs. The total polarization field of both spontaneous polarization  $P_{SP}$  and piezoelectric polarization  $P_{PE}$  induces charges in 2DEG at the AlGaN/GaN interface with a high sheet charge density of  $\sim 10^{13}$  cm<sup>-2</sup>. It was shown that there is a minimum AlGaN thickness necessarily to induce charges in 2DEG [33] and that the Al concentration in

Figure 1.4 Schematic formation of 2DEG in the interface of heterostructure semiconductors due to the conduction band discontinuity in the interface (a) before contact, and (b) in contact reaching the equilibrium by lining up Fermi level. Electrons transfer from larger band gap semiconductor (N) to lower band gap semiconductor (n) results a positive donor space charge in larger band gap semiconductor.

AlGaN layer determines the charge sheet density in the 2DEG channel [34]. Fig. 1.6 depicts the composition-dependent strain and the total polarization for a thin  $Al_xGa_{1x}N$  layer on a relaxed GaN layer.

The charge carriers in 2DEG channel due to total polarization ( $P = P_{SP} + P_{PE}$ ) is described by Poisson equation as the following [29],

$$egin{aligned}

abla \cdot D &=

abla \cdot (arepsilon \ E + P) =

ho \\

abla \cdot [arepsilon( -

abla arphi)] +

abla \cdot P &=

ho \\

abla arepsilon \rightarrow 0, ext{ then} \\

abla^2 arphi &= -rac{

ho}{arepsilon} + rac{1}{arepsilon} \left[

abla \cdot P \right], \end{aligned}$$

At the interface between AlGaN and GaN, the polarization results in a fixed polarization charge  $\rho^{Pol}$

$$abla^2arphi=$$

-  $rac{

ho}{arepsilon}$  -  $rac{

ho^{Pol}}{arepsilon}$

The charge  $\rho$  in the semiconductor covers holes p, electrons n, ionized donors  $N_D^+$ , and ionized acceptors  $N_A^-$ ; and possibly the donor-acceptor traps. Thus a complete description of charged carried in semiconductor due to the response of a potential field as the following,

Figure 1.5 Schematic explanation of polarization induced charge creation (i) GaN growth with Ga-face has spontaneous polarization field  $P_{SP}$  along c-axis represented by a blue arrow (ii) before intimate contact- AlGaN layer with smaller lattice constant (dashed black lines) than GaN lattice constant due to smaller size of Al atom (iii) deposition of AlGaN layer on the top of GaN layer creates tensile strain along a-axis to match GaN lattice constant and consequently the lattice constant of AlGaN in c-axis is stretched. This creates piezoelectric polarization  $P_{PE}$  in AlGaN layer.

Figure 1.6 (a) Elastic strain calculation in  $Al_xGa_{1-x}N$  layer as a function of Al concentration on a relaxed GaN crystal, and (b) total polarization from piezoelectric and spontaneous polarizations as a function of Al concentration [29].

$$abla^2 arphi =$$

-  $rac{q}{arepsilon}$  [  ${

m N}_D^+$  -  ${

m N}_A^-$  + p - n ] -  $rac{

ho^{Pol}}{arepsilon}$

Fig. 1.7 describes high concentration of charged carries in 2DEG as a response to the potential field. The standard AlGaN/GaN HEMTs is characterized by a high sheet charge density of electrons at the interface even without any intentional doping. Depending on specific design the sheet charge density can be almost one order of magnitude higher than standard AlGaAs/GaAs HEMTs.

#### 1.5 The status of GaN reliability

Literature of GaN device reliability has some decisive questions: what is the real cause of GaN degradation? Is it due to material intrinsic properties, substrate and/or GaN growth quality, process related effects or a combination of all of them? The most important question is: what is physics behind it?

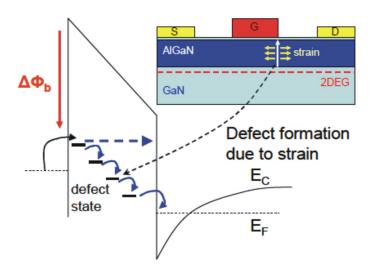

Presently, there are two main streams of degradation mechanism explanations: hot electron [35, 36] and inverse piezoelectric effect [37]. Hot electrons by definition are electrons with higher energy than the lattice thermal energy. They can get kinetic energy from high electric field when the device in turned on. These "hot" electrons can get injected into the AlGaN barrier layer and might be trapped or create interface states or bulk traps [35]. Defect creation by hot electrons in GaN and other similar materials is controlled

Figure 1.7 Charged carriers (dashed line) concentration in 2DEG channel of standard conduction band (solid line) AlGaN/GaN HEMTs as a response to the potential field [29].

by local kinetic considerations, and not by the defect formation energy. Hot electrons can possibly provide sufficient energy to cause a pre-existing defect to convert into a metastable configuration or cause migration of pre-existing defects. In addition, hot electrons may release a hydrogen atom from a pre-existing passivated defect. Hydrogen release (possibly from annealing) from defects has been known to cause device degradation in Si [38, 39]. Ref. [40] provided the model of an H atom that could be trapped in screw dislocations by some diffusion in high temperature growth condition. Besides, hydrogenation lowers the formation energies of point defects including the vacancy and antisite defects [39].

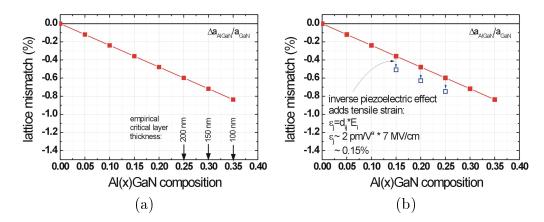

Inverse piezoelectric effect is a result of applied high electric field which adds tensile strain in AlGaN barrier layer due to the lattice mismatch between the AlGaN barrier layer and the GaN buffer. The total strain can exceed beyond crystal elasticity, and consequently crystallographic defects can be created [37]. One simulation of electromechanical stress under the gate at the drain side showed that the maximum electric field opens the possibility for electron injection and inverse piezoelectric effect [41].

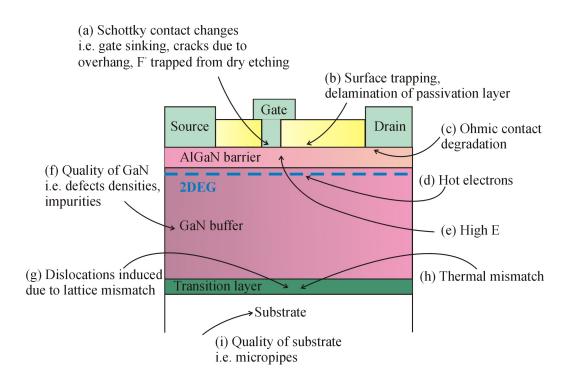

Figure 1.8 AlGaN/GaN HEMTs schematic cross-section, identifying critical areas for device degradation (summarized from Ref. [36, 42]).

Fig. 1.8 depicts critical areas in AlGaN/GaN HEMTs which are related to epitaxial growth quality and process as well. There are possibilities that Schottky and ohmic contacts degrade and imperfect passivation layer are responsible for parasitic charging effects which cause dispersion and lagging effects (see (a), (b), and (c) in Fig. 1.8). One should design carefully Al-GaN/GaN HEMT device concerning the high electric field ( $\sim 6 \text{ MV/cm}$ ) under the gate at the drain side which can cause degradation due to inverse piezoelectric effect and generate hot electrons (see (d) and (e) in Fig. 1.8). This can lead to crystallographic defects where pre-existing defects (i.e. vacancies, dislocations, impurites) can aggravate. These defect clusters can trap electrons or can become electrically conductive and thus reduce device performance. Localized native defects due to material growth condition, and dislocations mostly due to lattice mismatch between substrate and GaN buffer (see (f) and (g) in Fig. 1.8) can act as degradation points. During cooling down after material growth, the wafer may bend which indicates large tensile strain. In a worse case, when thermal mismatch between GaN and substrate is large, even cracks can occur (see (h) in Fig. 1.8). During

gate process using plasma etching employing reactive fluorine components, fluorine can be incorporated in the semiconductor and create instabilities there. This step can create crystallographic defects which act as traps under the gate (see (a) in Fig. 1.8). In addition, substrate quality needs careful inspection. This is due to the fact that defects such as micropipes in the substrate can penetrate to the surface and influence the electrical properties of the device (see (i) in Fig. 1.8). Therefore, it is important to discuss both epitaxial growth and device fabrication including defects formation that I will explain in chapter 2.

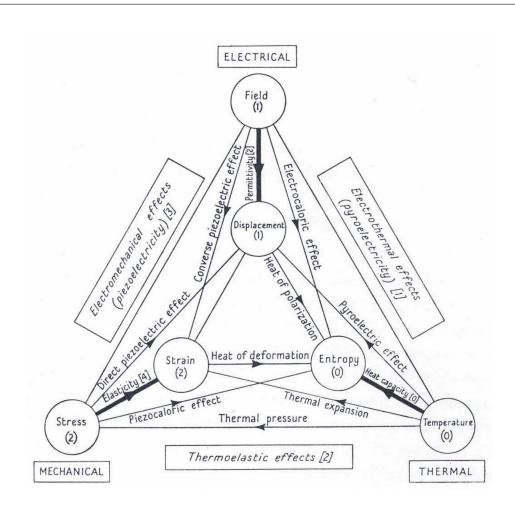

#### 1.5.1 Heckmann diagram: crystal properties relations

It is necessary to discuss the intrinsic property of GaN as a centrosymmetric crystal. Mechanical, electrical and thermal parameters of centrosymmetric crystal are described by the Heckmann diagram (see Fig. 1.9). There are three "forces" applied to the crystal in the three outer corners: temperature T, electric field E, and mechanical stress  $\sigma$ . Each of these "forces" has direct results: entropy per unit volume S, electric displacement D, and strain  $\epsilon$  respectively. The three principal effects regarding these pairs (depicted in the thick arrows) [43]:

- In a reversible change, and considering unit volume, an increase of temperature produces a change of entropy dS = (C/T) dT, where C is the heat capacity per unit volume, and T is the absolute temperature.

- a small change of electric field dE produces a change of electric displacement  $dD = \epsilon dE$ , where  $\epsilon$  is the permittivity tensor.

- a small change of stress  $\sigma$  produces a change of strain  $de = s \ d\sigma$ , where s is the elastic compliances.

The three properties, thermal, mechanical and electrical, are correlated to each other such as channel temperature when GaN device is switch on is related to electric field and current distribution. By performing electroluminescence (EL) measurements, Shikegawa et al. observed that the EL intensity reveals peaks around the edge of the channel where the electron temperature is high [44]. Theoretically, strain modifies the bandstructure because strain changes the relative positions of atoms in a material and change selection rules for optical transitions [45]. Recently, Ref. [46] showed a correlation between tensile stress and strong luminescence intensity where device under high tensile stress cause a redshift of the peak of photoluminescence intensty.

Figure 1.9 Heckmann diagram [43].

#### 1.6 Structures of this thesis

This thesis introduces AlGaN/GaN HEMTs, basic understanding and a brief of reliability issues in chapter 1. Chapter 2 explains AlGaN/GaN HEMTs fabrication from material growth and process technology together with a discussion of potential defect creation. The stressing methods and characterizations including electrical, physical and localized characterizations are discussed in chapter 3. Then, we designed experiments to investigate GaN reliability issues in chapter 4. Results and discussions would be shown in chapter 5 followed by our interpretations of the results in chapter 6. The last chapter provides the conclusions and outlook of AlGaN/GaN HEMTs reliability.

## Chapter 2

# AlGaN/GaN HEMT device fabrication

#### 2.1 Motivation

AlGaN/GaN HEMTs reliability issues as mentioned in chapter 1 need to be examined carefully concerning the whole technological process chain. Good understanding of device fabrication is crucial to narrow down the degradation problems. The damage that is detected in degraded devices is often due to multiple degradation effects being the consequence of one initial degradation mechanisms. It is therefore very important to stress devices in such a way that the initial degradation effect can be observed without fully damaging the device as a consequence of this effect. This premature degradation detection is not only necessary for interpreting degradation modes and failure analysis but also important to give fast feedback to device technology improvement. In this chapter, I will explain the fabrication of AlGaN/GaN HEMTs in Ferdinand-Braun-Institut (FBH). After all, it is also essential to discuss defects which can occur during material growth, during process, from the difference material intrinsic properties such as lattice and thermal mismatch, and/or combination of these factors.

#### 2.2 Epitaxy

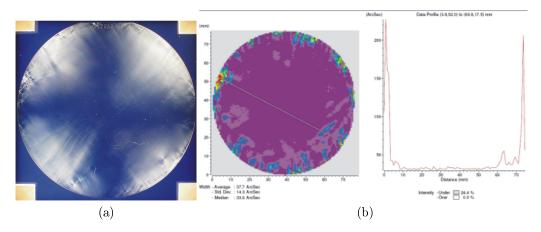

In this work, the following single crystal line substrates used are: semi insulating (SI) or n-type SiC substrates with 2- and 3-inch diameter. Regular substrate inspections to check defect and mechanical strain distribution across the wafer were performed by cross polarization light microscope (see Fig. 2.1a). Fig. 2.1b shows the X-ray diffraction mapping of the full width

Figure 2.1 Substrate routine check: (a) polarized-photo and (b) X-ray mapping.

half maximum of a diffraction peak that characterizes the quality of the crystalline SiC substrate. It can be seen that the crystalline quality of the substrate is much better in the wafer centre whereas at the wafer periphery the crystalline is clearly compromised. To a certain extend this finding also correlated with the crossed polarization imaging of Fig. 2.1a.

Metalorganic vapour phase epitaxy (MOVPE) is the dominant GaN epitaxial growth technique at FBH. It uses metal organic compounds such triethyl or trimethyl-gallium (TEG or TMG) as gallium source and NH<sub>3</sub> as nitrogen source, respectively. The simplified chemical reaction for the GaN growth is the following,

$$Ga(CH_3)_3 + NH_3 = GaN + 3CH_4 + H_2$$

From the equation above, hydrogen involves in GaN deposition. But most of the hydrogen is not coming from this reaction. Hydrogen is the carrier gas for TEG and TMG. Noted that  $CH_4$  at high temperature ( $\sim 1000$  °C) can be decompose. As mentioned before, hydrogenation lowers the formation energies of point defects including the vacancy and antisite defects [39]. Additionally, hydrogenation could passivate acceptors.

To accommodate the lattice mismatch between SiC substrate and GaN, a thin AlN nucleation layer can be used. The use of an AlN initial layer not only reduces the lattice mismatch between AlN and GaN ( $\sim 2.4$  %) but also promotes surface wetting [47]. The AlN nucleation layer thickness has range of 30-300 nm. The nucleation layer growth conditions influence the GaN nucleation and consequently grain coalescence which then determines GaN dislocation densities, and stress incorporation [47, 48]. Ref. [48] showed that high temperature AlN growth provides a low number of dislocation density

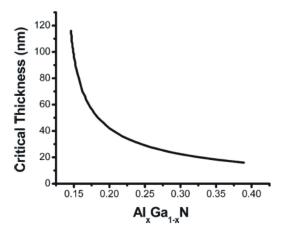

Figure 2.2 Calculation of AlGaN critical thickness on relaxed GaN layer with Fisher model Peierls barrier (dislocation density 10<sup>10</sup> cm<sup>-2</sup>) [49].

in GaN buffer layer. AlN thickness study comparison (25 nm vs. 150 nm) showed an order of magnitude of threading dislocations (TDs) difference ( $\sim 1 \times 10^9$  cm<sup>-2</sup> vs.  $\sim 2 \times 10^8$  cm<sup>-2</sup>) [47].

Thickness of the AlGaN barrier layer on the top of GaN buffer is  $\sim 25\text{-}35$  nm as it basically accomodates the lattice constant of the GaN buffer layer. Underneath this layer is heavily tensile strained. This is due to the fact that the Al atoms sit in Ga place which make lattice constant smaller, and the GaN buffer layer forces the system to a GaN lattice constant. Strain in AlGaN increases along with Al concentration. At certain thickness of the AlGaN layer, the elasticity of the AlGaN layer is not strong enough to withstand the tensile stress, and the material starts to relax and to form microscopic cracks. Simulation from Ref. [49] shows that the critical thickness of AlGaN is a function of Al concentration in AlGaN layer (see Fig. 2.2).

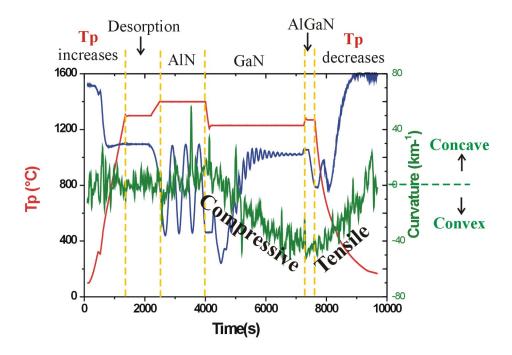

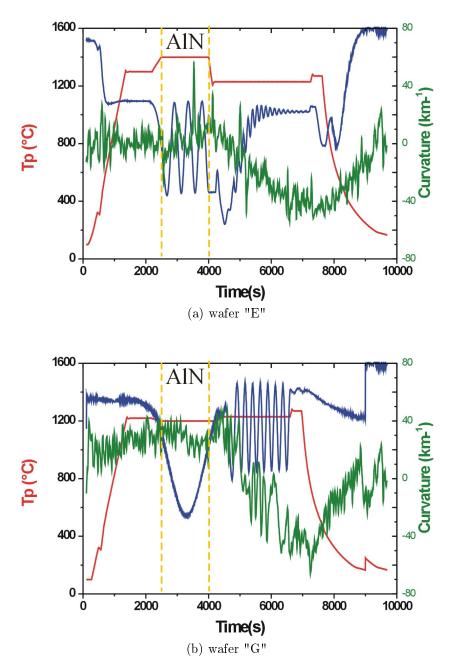

A typical epitaxial growth process for HFET structure accompanied by the in-situ monitoring of growth temperature and wafer curvature is shown in Fig. 2.3. It shows that wafer acquaintances thermal stress (red line) during epitaxial growth which determines wafer bow curvature (green line). The growth process temperature  $T_P$  is measured at the backside of a SiC susceptor. The emissivity corrected the surface temperature of a SiC susceptor  $T_{true}$  is measured by a pyrometer with wavelength 950 nm to calculate the growth rate. The in-situ surface reflectance data is measured with wavelength 405 nm which is very sensitive to the GaN surface in terms of the coalescence process.

Figure 2.3 Wafer curvature and surface reflectance were monitored during growth using an EpiCurveTT-AR sensor. Red line is the growth process temperature  $T_P$ , blue line is the reflectance measured by a pyrometer (450 nm), and green line is the wafer bow curvature. Yellow dashed-lines are marks for temperature changes during epi growth.

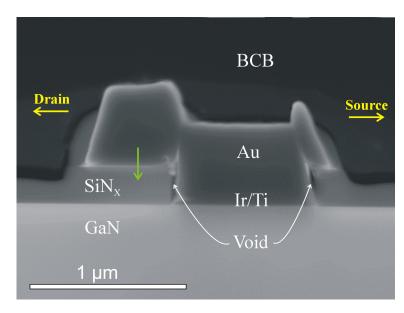

#### 2.3 Process Technology

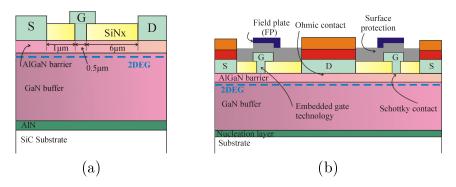

Concerning AlGaN/GaN HEMT device performance and reliability, some optimizations of technology in critical areas are developed as depicted in Fig. 2.4.b. T-gate structures with a longer wing at the drain side acting as a field plate (FP) [50, 51] are applied to reduce high electric field under the gate at the drain side. A new embedded gate technology has been developed in which the nitride is deposited at an early stage of processing and gates are defined by nitride etching and subsequent metallic gate definition. Low resistance ohmic contacts  $R_C$  (< 0.5 Ohm cm) are essential for efficient high power electronic device operation. The metal diffusion because thermal annealing leads to rough surface morphology and difficult to make good line edge definition of ohmic contacts. The rough surface morphology can be a problem for homogeneous issue of active areas (will be shown in electroluminescence measurements in chapter 5). The problem of good line edge definition does

not facilitate low S-G distance for high speed device operation, and hence it deteriotes the performance of high speed HEMTs [52].

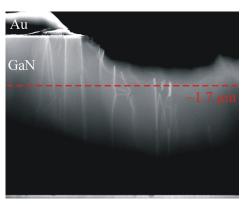

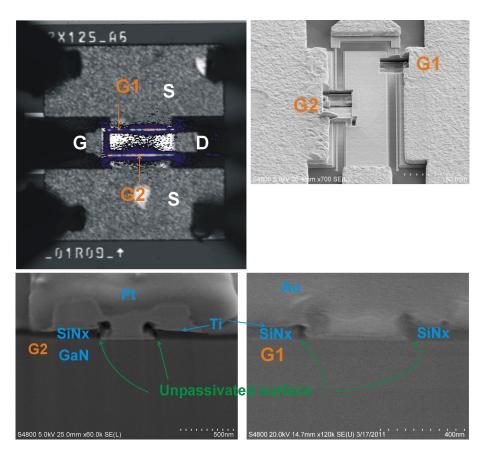

Figure 2.4 AlGaN/GaN HEMT (a) cross-sectional dimension of 2x125  $\mu$ m device used for reliability measurements, and (b) optimizations of process technology for critical areas.

Typical metallic compositions for ohmic contacts are: Ti/Al/Ni/Au, or Ti/Al/Mo/Au or  $Ti/Al/Ti/Au/WSiN_x$ . The ohmic metal contacts are formed by rapid thermal annealing (RTA) around 800 °C. If ohmic contacts are formed in n-GaN laver, during annealing, Ti reacts with GaN and forms TiN. This reaction extracts N from GaN and generates N-vacancies in GaN layer. Additionally Ga is dissolved in Mo and Au which leads to further intermetallic compound/semiconductor interaction and thus helps to form a good ohmic contact. These vacancies acts as n-type dopant and create a highly doped region in the vicinity of the interface, and generates the foundation for tunneling contact mechanism. If ohmic contacts are formed in AlGaN layer, it has been observed that the contact resistivities of Ti/Al metalizations on AlGaN/GaN increased with an increasing Al concentration (due to an increase of band gap of AlGaN) and with an increasing AlGaN thickness due to the increasing tunneling depth. However it has been observed that TiN protrusions which are formed along dislocations, penetrate through the AlGaN barrier layer, and hence may directly contact the 2DEG [53].

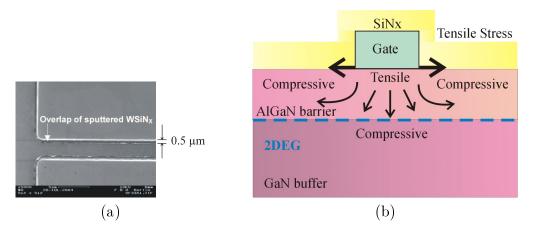

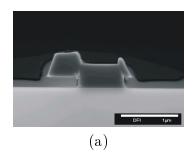

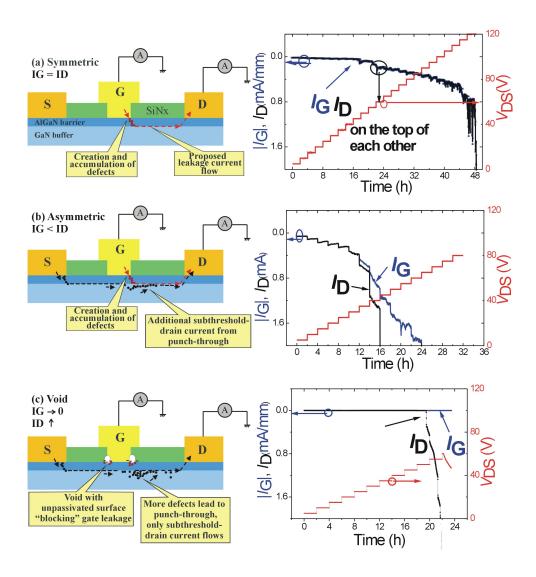

Regularly checked with visual inspection such SEM as depicted in Fig. 2.5. (a) reveals the edge delineation problem which causes a problem to place gate closer to source than 0.5  $\mu$ m (might create short circuit), and fence-like WSiN structures that might compromise yields. Surface passivation is intended to reduce surface traps and avoid current collapse. However, non-continous surface passivation i.e. a trench opening to form the gate and subsequent  $SiN_X$  passivation above the metallic gate introduces very complex compressive and tensile stress situations in the gate area which may give rise to premature degradation effects in these areas (see Fig. 2.5. (b)). Ref.

[54] observed other optimization such as second passivation and different encapsulation of passivation have an impact to gate leakage.

Figure 2.5 Examples of process problems (a) SEM picture of  $Ti/Al/Ti/Au/WSiN_x$  ohmic contact with edge delineation [52], and (b) schematic of area below the gate of AlGaN/GaN HEMT with a non-uniform  $SiN_x$  passivation layer induces compressive and tensile stress [49].

#### 2.4 Defects

It is very crucial to discuss defects in this chapter because they strongly determine electrical, optical and thermal properties of semiconductors It has been suggested for the first time by Ilegems and Montgomery that native defects dominate the transport properties of bulk GaN [5] explaining the n-type conductivity of bulk GaN. In this section, I discuss types of defects which affect AlGaN/GaN HEMT device performances and reliability.

#### Types of defects

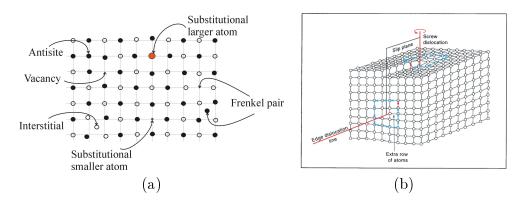

Based on dimension, defects in solids can be categorized as the following (see Fig. 2.6):

- 0D: point defects, i.e. vacancies, self-interstitial atoms, substitutional impurity atoms, interstitial impurity atoms and antisite defects.

- 1D: dislocations, i.e. edge and screw dislocations.

- 2D: grain boundaries i.e. tilt- and twist-type, stacking faults, and external surface.

Figure 2.6 Some examples of defects (a) point defects (grid lines are a guide for eye) (b) edge and screw dislocations [55]

• 3D: bulk or volume defects, i.e. voids, cracks and foreign inclusions.

#### **Defects formation**

The formation probability of crystal line defects depend on:

- Crystal structure and unit cell atoms. GaN has a relatively low atomic packing fraction of 0.42 [56]. This represents a moderate degree of openness in the unit cell but also depicts a large differences in radii (Ga has a large and N has a small covalent radii). This makes the formation of interstitial and antisite defects unfavorable; only vacancies have formation energies that are low enough. This fact is important in interpreting degradation mechanisms.

- Lack of stoichiometry. This influences the formation energies of defects in the growth process, such as Ga-rich growth condition leads to a smoother surface. A reduced growth temperature leads to C-incorporation in the grown layers (in this case C stems from the metalorganic precursors).

- Growth conditions. Defects can enter a material along with the diffusion of wanted, or unwanted, impurity atoms such as hydrogen during crystal growth which can lower the energy formation of point defects [39]. These unwanted materials are dependent on growth conditions [57].

- Mechanical property. Defects can also be introduced into materials by the processes of plastic deformation. This mechanical property is

related to temperature, lattice mismatch, thermal expansion mismatch and strain incorporated by processing such as for example passivation or metallization.

• High energetic particles interaction with lattice. For example, plasma etching and hot electrons can cause displacement damage [35, 36, 58].

#### Point defects

Among GaN native point defects, vacancies have the lowest fomation energies [7]. Under p-type conditions the nitrogen vacancy is dominant, and under n-type conditions the gallium vacancy is dominant [59, 60]. Source of unitentional n-conductivity of GaN are oxygen- and silicon incorporated for certain reactor types [7]. The defects are not independent from each other: they are coupled via the condition of charge neutrality. The total sum of electrons in the conduction band, holes in the valence band and charges trapped in the defects must be zero. Consequently, when a potential difference is applied in GaN-based devices (nonequilibrium condition i.e. OFF-state), charges trapped in the defects can be released and may degrade the device.

A low certain formation energy is required to create defects in larger concentration under conditions of thermodynamic equilibrium. For all growth temperatures the gallium vacancies are those point defects with the highest concentration even at high temperature of 1300 K (growth temperature) [59].

Point defects i.e.  $V_{Ga}$  and its complexes with one or more  $O_N$  have very low formation energies at different positions near the threading-edge dislocations [61]. If the point defects in are mobile, a number of reactions can occur i.e. an interstitial can annihilate with its own or another vacancy. Interstitials or vacancies can cluster, agglomerate and trap impurity atoms. Mobile point defects are known in other semiconductors i.e. two types of mobile point defects in Ge surface were observed by STM at temperatures below 80 °C [62]. Ref. [63] pointed out that the mobile defects can be trapped by impurity atoms, thus forming impurity-related complexes. Limpijumnong and Van de Walle investigated the diffusion of relevant native point defects in wurtzite GaN crystals. Gallium interstitials  $Ga_i$  migrate via an interstitial cy mechanism with an unexpectedly low barrier of 0.9 eV. They are mobile at temperature slightly below room temperature. The migration barrier for gallium vacancy  $V_{Ga}$  is significantly low of 1.9 eV. For all these defects the lowest-energy migration path results in motion both parallel and perpendicular to the c-axis [64]. This should be noted for the interpretation of lifetime effects.

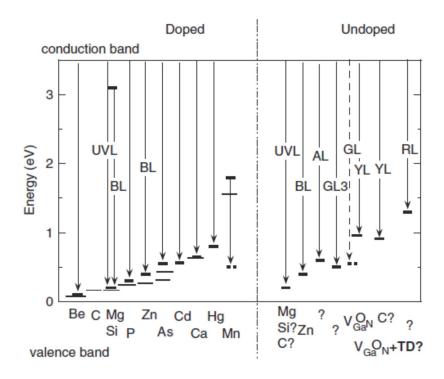

Luminescence is a powerful method to detect point defects. Reschchikov

and Morkoc studied luminescence of point defects for different states in energy band gap in doped and undoped GaN [60, 65] (see Fig. 2.7). As several other authors, they also pointed out that  $V_{Ga}-O_N$  defect complexes i.e.  $V_{Ga}-O_N$  contribute to well known broad band yellow luminescence (YL) besides other defects i.e. dislocations at low-angle grain boundaries [66].

Figure 2.7 Radiative transitions associated with major doping impurities [65].

#### **Dislocations**

Abundant studies of dislocations in GaN are available. It is well known that heteroepitaxial growth of GaN results in formation of high threading dislocation (TD) densities. The lowest reported TD densities in GaN are  $\sim 10^6$  cm<sup>2</sup>. TDs are problematic: they can be sources of nonradiative recombination [67, 68, 69] and modify crystal potentials creating localized electrostatic and strain fields [69, 70, 71, 72, 73]. TDs also scatter carriers and reduce the carrier mobility [74] as well act as pathways for current leakage [75, 76, 77] and therefore can lower the breakdown voltage  $V_{BR}$  [78]. Consequently, the

fabrication of GaN layers with low TD density remains one of the most important challenges in the GaN epitaxy. The lowest threading dislocation (TD) densities are reported to be in the range of  $\sim 10^6$  cm<sup>-2</sup> [79]. Screw and mixed dislocations dominantly contribute to nonradiative recombination compared to edge dislocations [68, 80]. They create states in GaN band gap which can accept or donate electrons, and may become charged in doped material [40]. The stress field produced by the dislocations can accumulate electrically active impurities and point defects near the dislocations [69]. Ref. [81] correlated dislocations to the existence of the bright spot during electroluminescence measurements at OFF-state. Meanwhile Ref. [82] associated bright spots during electroluminescence measurements at OFF-state with electron release from traps of defect complexes (i.e.  $V_{Ga}$ -O<sub>N</sub>).

#### Surface defects

As mentioned previously, lattice mismatch between the substrate and the GaN buffer layer results in dislocation formation in GaN layer. These, so-called threading dislocations can penetrate through the whole GaN/AlGaN layer stack. They can be observed as pits on the (Al)GaN surface by AFM measurements. These pits are the terminations of dislocation lines and contribute to the surface roughness. Heying at al. found the GaN surfaces to be dominated by three dislocation mediated structures: pinned steps, spiral hillocks and surface depressions [83]. Ref. [84, 85] pointed out that the origin of the hillocks on N-polar c-plane and m-plane are screw dislocations. The association of hillocks to dislocations was directly shown by AFM measurements that reveals the spiral pattern of atomic steps [86].

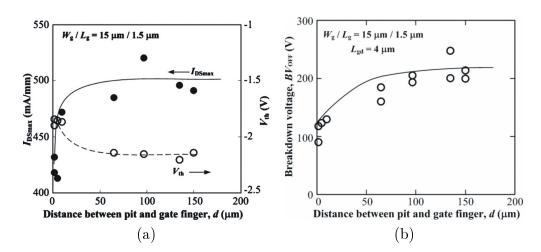

Defects originating from SiC substrate micropipes can run through the buffer and up to the surface of AlGaN buffer which influence device characteristics such as IV-output, transfer and gate leakage [87]. Bang et al. correlated wafer yield to various size and densities of the hollow of these structures. It is known that they introduce free carrier densities close to the active region and therefore influence 2DEG. Similar effects are applicable to Si substrates [88], defects in any case influence the AlGaN/GaN HEMTs device performance. Depending on distance from active area, deep pits may influence pinch-off voltage  $V_{TH}$ , maximum drain current  $I_{Dmax}$  and breakdown voltage  $V_{BR}$  [89] (see Fig. 2.8). These pits are originating from the substrate and are present until the top of AlGaN surface layer irrespective of buffer technology. Deep pits can be the original sources of high leakage current through the buffer and substrate which yield devices with low  $V_{BR}$ . The prevention and control of deep pits largely depends on the epitaxial growth technology [90].

Those defects discussed before may also affect GaN optical properties

Figure 2.8 AlGaN/GaN HEMTs electrical characteristics in dependence from pit distance from gate finger (a)  $I_{Dmax}$  and pinch-off voltage  $V_{TH}$ , and (b) breakdown voltage  $V_{BR}$  [89].

which can be observed at certain wavelenghts such as yellow luminescence; however, usually a large amount of damage is needed for detection. In contrast, electrical properties are usually affected already by small quantities of defects which introduce levels in the forbidden gap. The electrical properties include carrier concentration is usually sensitive to lattice defects. Ref. [74] examined 2DEG transport in the AlGaN/GaN HEMTs is mostly dominated by dislocation scattering with a typical dislocation density above  $5 \times 10^7$  cm<sup>-2</sup> for Al contents ranging from 8-35 %. They predicted the mobility of the 2DEG to exceed 2000 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> as the dislocation density falls below  $\sim 5 \times 10^7$  cm<sup>-2</sup>.

### Chapter 3

# Device stressing and characterizations

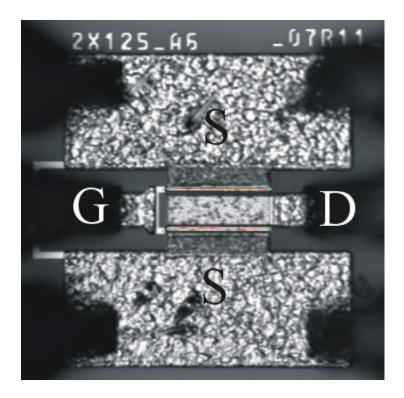

For systematic investigations of AlGaN/GaN HEMTs reliability problems. one should refer to basic properties of nonsymmetric materials as described in Heckmann diagram (see subsection 1.5.1). It relates electrical, mechanical and thermal properties to each other and is therefore well suited for a formal description of the dependencies that might occur during device stressing. It could for example relate thermal, mechanical, electrical and optical properties to each other and thus provide the basis for a more detailed understanding of degradation effects. In this work we have concentrated on detecting degradation thresholds, which mean that we have to monitor the device behavior once a degradation of instability effect occurs. Therefore, we have established DC-Step-Stress test to find out degradation thresholds which are also intended to provide a short term information on the principal robustness of the devices. Indeed, these stresses deliver meaningful fingerprints and are able to detect characteristic properties in dependence on device material properties, technology and device layout. The stressings are accompanied by characterizations such as IV-measurements, electroluminescence and localized characterizations. Localized characterizations include cross-sectioning by focused ion beam (FIB) and mechanical grinding for transmission electron microscopy (TEM) and energy dispersive x-ray spectroscopy (EDX) investigations. The devices under test have size of  $2x125 \mu m$  with FBH standard source-gate space  $L_{SG} = 1 \mu m$ , gate-drain space  $L_{GD} = 6 \mu m$ , gate length  $L_G = 0.5 \mu m$ , unless otherwise specified.

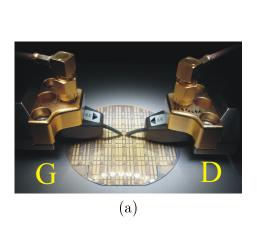

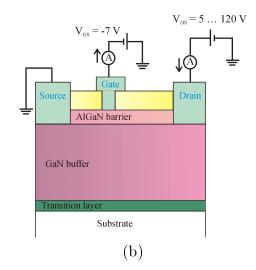

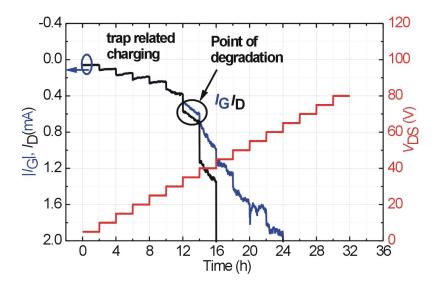

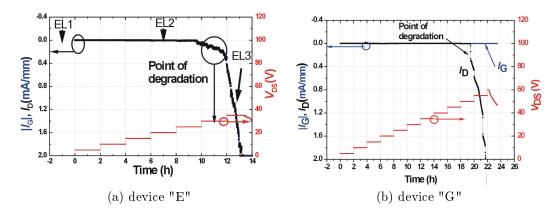

#### 3.1 Robustness tests

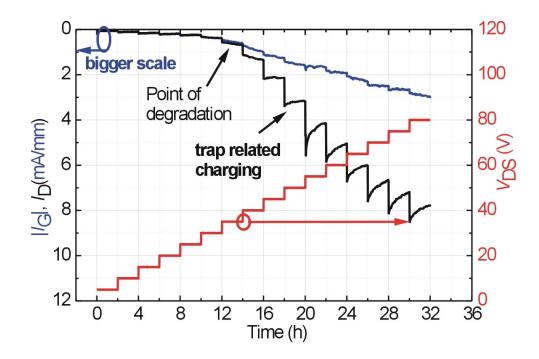

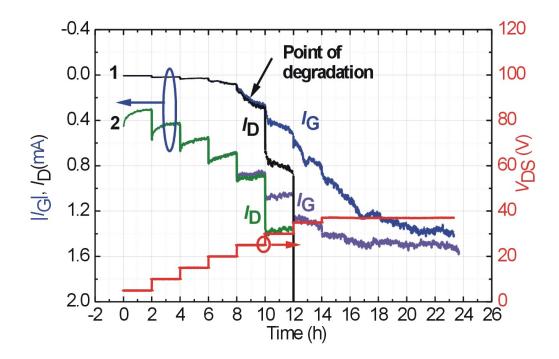

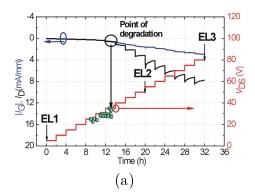

DC-Step-Stress tests consist of 5 V step ramping of drain-source voltage  $V_{DS}$  every two hours on pinch-off transistors ( $V_{GS} = -7$  V). They are performed at room temperature in darkness (see Fig. 3.1). Since this electrical stressing is performed at OFF-state, one can see the effect of applying high electric field without thermal stress (channel is not open). The irreversible evolution of one or both, gate leakage current  $I_G$  and subthreshold drain current  $I_D$  are observed during stressing and have been taken as a criterion for the onset of device degradation so called critical voltage  $V_{CR}$  when one or both of those currents increase (see Fig. 3.2). In the several steps before the point of degradation, trap related chargings are observed. The number of devices for our screening standard DC-stressing on wafer is a minimum five devices across the wafer: one from the centre, two from the edge and two from midcentre. This insures a certain statistical relevance.

Definitely, one cannot compare the degradation mechanism at OFF-state with degradation mechanism at ON-state when the channel is open. It is likely, that the degradation mechanisms are different between OFF- and ON-states [35]. DC-stressing at OFF-state pronounces the impact of high electric field on devices meanwhile at ON-state. It is therefore a good method to separate this from current assisted degradation effects. However, one should consider the piezoelectric effect for both ON- and OFF-state stress conditions.

Another test so called the high temperature reverse bias (HTRB) applies both, thermal and electrical stressings simultaneously to the device. HTRB is triggering field assisted and thermally activated degradation mechanism simultaneously. Therefore, one should carefully interest the results because it is not easy to distinguish how each stress type affects the device performance; temperature or high electric field and/or which one is the trigger to the other.

### 3.2 Long term lifetime tests

Typical wear-out times of semiconductor devices are in the order of  $1x10^6h$  ( $\sim 100$  years or more) hence accelerated testing conditions are needed. Many chemical processes associated to device failure progress exponentially with temperature i.e. diffusion and metal migration. Commonly, an accelerating test by applying thermally activated stress on a number of devices is a standard procedure to predict median time to failure (MTTF). The Arrhenius model for lifetime prediction is possible if degradation mechanisms follow an exponential law with temperature

$$MTTF = A \exp (E_a/kT)$$

Figure 3.1 DC-Step-Stress Test on wafer with (a) two coplanar probes connected to gate voltage source (G) and drain voltage source (D). The probe has three fingers where the middle finger is connected to gate or drain voltage source (signal), and the two fingers are connected to source (ground), and (b) schema of electrical circuit for DC-Step-Stress Testing.

where  $E_a$  is the activation energy associated to the particular failure mechanism, T is the device temperature, k is Boltzmann's constant and A is a constant.

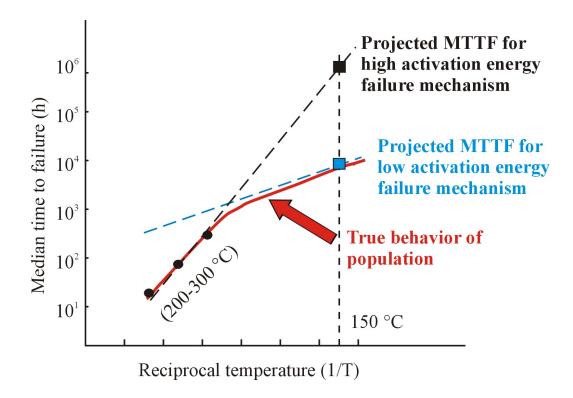

Common model to analyse the life test data which involves fitting the failure rate at a particular temperature is Weibull distribution. MTTF is measured by extrapolating a number temperature points taken at high temperature to the temperature of device application. The number of data points at each temperature should be in good confidence level which increases with an increasing number of samples. A lognormal plot of the failure times that would be used to originate MTTF graph based on Arrhenius formula, ideally lines up the data points in a straight line. Lifetime prediction to a specific operation temperature is possible be extrapolating the resulting straight line to the given temperature. This is possible only if the following are fulfilled: 1) the failure mechanisms are identical at all high temperature test points, and 2) the failure mechanism at high temperature is the same at the device application temperature [29], and 3) the failure mechanisms exponentially depend on temperature. If the slope at each temperature is similar, a single failure mechanism (assumption 1) can be considered. One should be careful with assumption 2 since the accelerated high temperature tests do not detect the existence of a low activation energy failure mechanisms which may lead to highly overestimated MTTF values (see Fig. 3.3). Failure mechanisms

Figure 3.2 An example of DC-Step-Stress test result. The gate leakage, subthreshold drain current and drain-source voltage  $V_{DS}$  are represented by blue, black and red lines, respectively. Trap related chargings are observed during single steps before gate leakage and/or subthreshold drain current finally start to degrade irreversibly. Critical voltage  $V_{CR}$  of this device is determined to 35 V. This is the drain voltage  $V_{DS}$  where degradation effects are clearly seen for the first time.

which are or only weakly activated by temperature are possible i.e. high electric field causes inverse piezoelectric effect [37].

The channel temperature used for MTTF measurements has been determined by several methods as shown in Table 3.1 with each advantage and limitation.

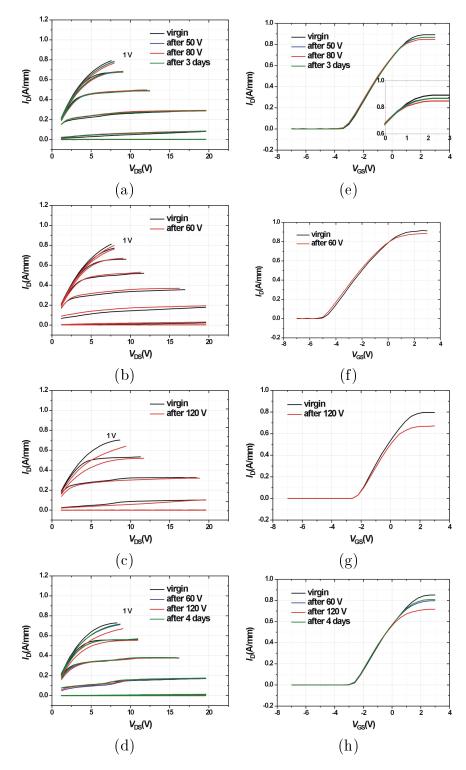

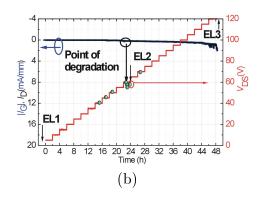

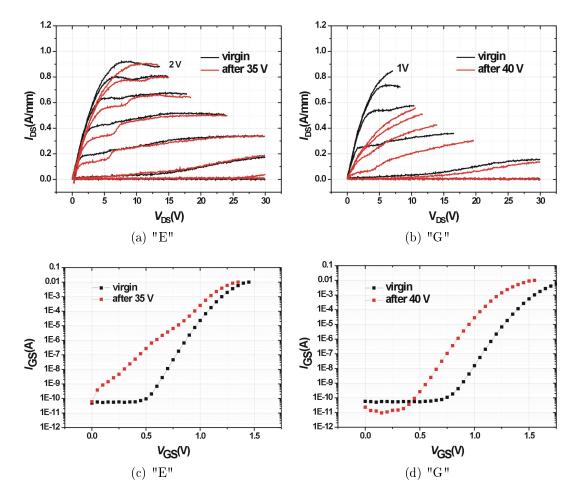

#### 3.3 Electrical characterizations

Static and dynamic IV-characterizations were performed on AlGaN/GaN HEMTs before and after DC-stress at base temperature 16 °C altogether with output transfer and diode characteristics. In this study, generally static IV-characteristics are measured by increasing drain voltage  $V_{DS}$  (from 0 to 30 V) for each value of gate voltage  $V_{GS}$  (from -7 V to +1 V) with a specific power dissipation limit  $P_{diss}$  (3 W/mm). Transfer curve characteristics are measured at drain voltage  $V_{DS} = 10$  V from gate voltage  $V_{GS}$  -7 V to

Figure 3.3 MTTF estimation illustration of overestimated MTTF at high accelerated high temperature test conditions to the actual device application temperature [29].

+1 V. Diode characteristics are measured in positive direction from gate to drain and to source  $V_G = 0$  to 2 V with maximum current of 10 mA/mm. And for negative direction, they are measured from source and drain to gate contact with negative voltage from -1 to -10 V with negative current limit of 1 mA/mm.

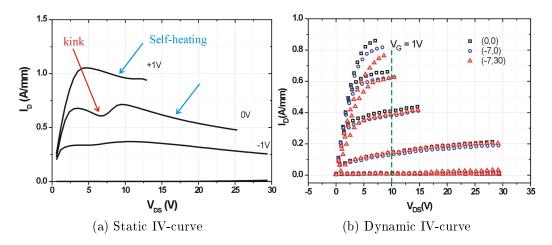

When the static IV-output characteristics are performed at comparably long scan times in such a long dwell time for example 1 V/s from 0 to 30 V of  $V_{DS}$ , these conditions may give enough time for electrons to change trapping states in the surface or AlGaN/GaN buffer interface. This trapping effect is observed as kinks at knee voltage usually below 10 V  $V_{DS}$  (see red arrow in Fig. 3.4a). In this figure also self heating of the device can be observed by a decay of drain current at high power dissipation levels. This is due to a reduced charge mobility in the channel due to phonon scattering. This causes a drop of saturated current (pointed by blue arrows in Fig. 3.4a).

Dynamic IV-characteristics are performed on a device by pulsing from

Table 3.1 Methods to measure channel temperature device [29]

|                          |                             | •                           |                             |  |

|--------------------------|-----------------------------|-----------------------------|-----------------------------|--|

| Method                   | Technique                   | Limitations                 | $\operatorname{Advantages}$ |  |

| IR imag-                 | using IR detector to deter- | resolution $\sim 35$        | Fast, cover large ar-       |  |

| ing                      | mine surface temperature    | $\mu\mathrm{m}$             | eas, die-attach in-         |  |

|                          | which requires calibration  |                             | tegrity                     |  |

|                          | of surface emissivity       |                             |                             |  |

| Liquid                   | coating liquid crystal,     | invasive and                | No calibration re-          |  |

| $\operatorname{crystal}$ | power up slowly and         | range of tran-              | quired                      |  |

|                          | observe transition tem-     | sition tempera-             |                             |  |

|                          | perature                    | ture is limited             |                             |  |

| Electrical               | applying constant current   | indirect mea-               | in situ monitor of          |  |

|                          | to calibrate forward-       | surement                    | circuit temperature         |  |

|                          | biased diode. tempera-      |                             |                             |  |

|                          | ture is proportional to     |                             |                             |  |

|                          | forward voltage             |                             |                             |  |

| Raman                    | observing the raman spec-   | slow and for                | need a model to             |  |

| spec-                    | ${ m trum\ shift}$          | best resolution             | determine peak              |  |

| troscopy                 |                             | $_{ m needs}$ $_{ m large}$ | channel tem-                |  |

|                          |                             | integration time            | perature, high              |  |

|                          |                             | -                           | resolution                  |  |

Figure 3.4 An example of (a) static IV-curve with kink at knee voltage due to trapping effect, and drop of saturated drain currents due to self-heating, and (b) pulsed IV-curve with each bias point (0,0), (-7,0) and (-7,30) are represented by open black squares, blue circles, and red triangles respectively.

a static quiescent point to the necessary locations throughout the IV plane (see an example of pulsed IV-curve in Fig. 3.4b). The pulse length is short enough to provide an IV-measurements isothermal (quiescent thermal) and isodynamic (quiescent trapping) conditions [91]. Pulsed I/V measurements are especially suitable to characterize the influence of trapping effects on the electrical performance of devices at well defined bias point conditions. These measurements rely on the fact that trap states usually have large time constants. If a device is then constantly biased at a certain point and the IV characteristics is measured starting from and returning back to this bias point within very short times (less than 1  $\mu$ s) and residing at the bias point relatively long (large duty cicle) the trap situation at this point can be considered as constant- the trap are not able to respond to the short measurement pulses. Hence the IV characteristics measured exactly reflects the internal charging situation of the device in this particular bias point.

To characterize device trapping effects the following three bias points are particular interest:

- If the device is biased at both, drain and gate voltage equal to 0 V, practically no internal electrical fields are present in the device. Thus this situation practically reflects the situation of a non trapped device.

- If the device is biased at zero drain voltage and at pinch-off gate conditions, electrical fields are dominating in the gate area only. Hence traps related to a limited volume around the gate are affected. This condition is referred to as "gate lag".

- If the device is biased OFF-state, however at a higher drain voltage, the gate high field region extends more and more towards the drain and to the buffer which means, that now traps in these regions are additionally affected. This condition is referred to as "drain lag".

As a consequence, pulsed I/V measurements prove informations on the basic location of trap states within the device. In this study, the pulse duration is 200 ns with a separation time of 0.5 ms and the quiescent points are  $(V_{GS}, V_{DS})$ : (0,0), (-7,0) and (-7,30). A gate lagging factor  $z_G$  is defined which rates the nearly trap free pulse measurement at zero bias conditions to the actual measurement at a given bias point. The  $z_G$  is defined as

```

\begin{split} \mathbf{z}_G &= \left(\mathbf{I}_{D(-7,0)} - \mathbf{I}_{D(0,0)}\right) / \mathbf{I}_{D(0,0)} \\ \text{for gate lag and} \\ \mathbf{z}_D &= \left(\mathbf{I}_{D(-7,30)} - \mathbf{I}_{D(0,0)}\right) / \mathbf{I}_{D(0,0)} \end{split}

```

for drain lag conditions where  $I_{D(0,0)}$ ,  $I_{D(-7,0)}$  and  $I_{D(-7,30)}$  are the drain current at (0,0), (-7,0) and (-7,30) respectively. The values are usually taken

at constant drain bias  $V_{DS}$  of 10 V and a gate bias  $V_{GS}$  of +1V to ensure comparability (see green dashed line in Fig. 3.4b).

### 3.4 Optical characterizations

Early GaN luminescence measurements were performed by electron-beam and optical excitation [3, 92]. Any spontaneous light emission from an excited state to a lower state is called luminescence. The main requirement for emission is that the system is brought out of equilibrium conditions which needs some form of excitation. Excitation by an electric current triggers electroluminescence (EL), by optical excitation produces photoluminescence (PL), and by an electron beam causes cathodoluminescence (CL) [93]. Luminescence is a very strong tool for detection and identification of point defects in semiconductors, especially in wide-band-gap varieties [60]. It is also a non-destructive test and a sensitive measurement. PL and CL measurements are commonly used to characterize GaN after epitaxy growth.

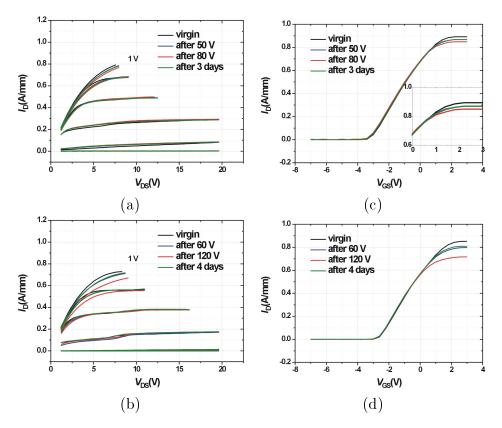

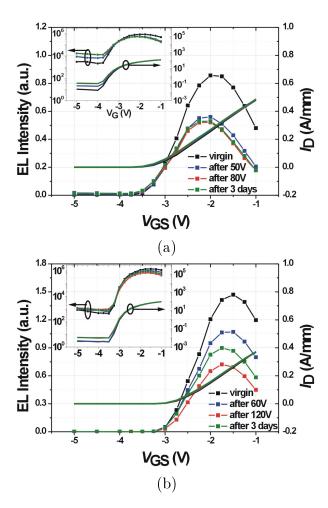

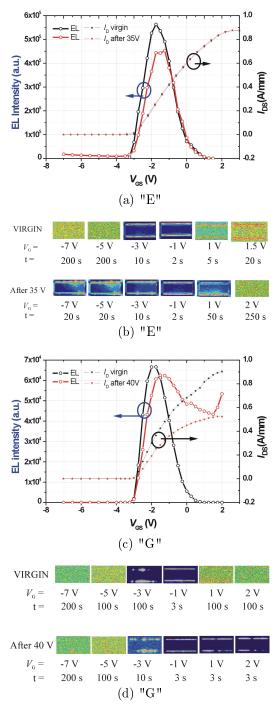

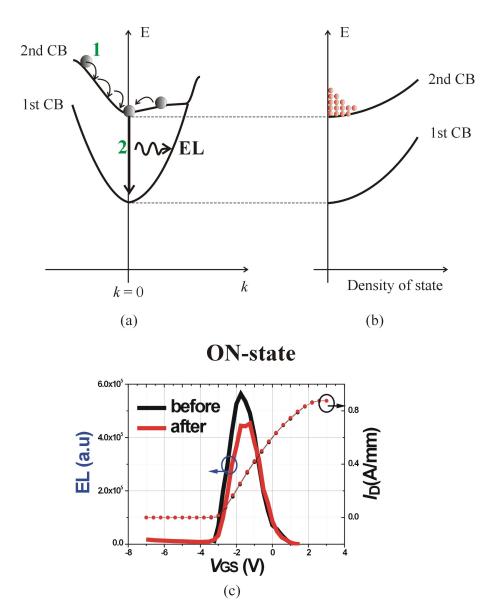

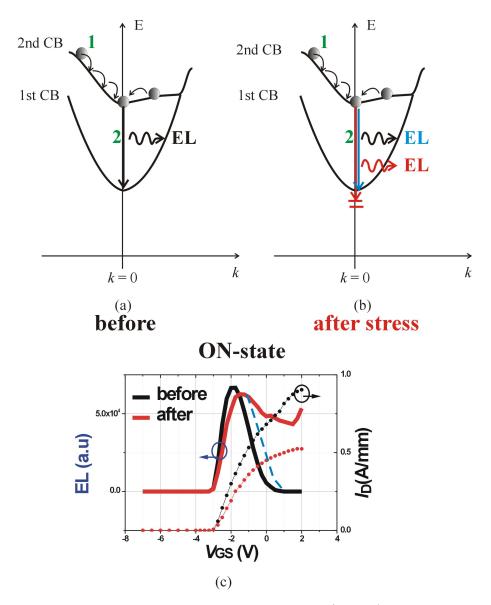

Electroluminescence (EL) measurements are known as a useful tool to localize potentially defective regions in the device topology [36]. Electroluminescent emission has initially been studied in GaAs and InP based heterostructure field effect transistors (HFETs) in order to investigate hot electron induced breakdown [94], impact ionization [95] and the conduction-to-conduction band (intra-band) transition of electrons [96]. In AlGaN/GaN HFETs technology EL has also been claimed as a valuable tool to provide a deeper insight in electronic properties of devices. It has been pointed out that the EL is possibly due to hot electron [36, 97] and intra-band transitions [98]. EL emission has therefore been proposed as a way to probe the regions of high electric field in a device.

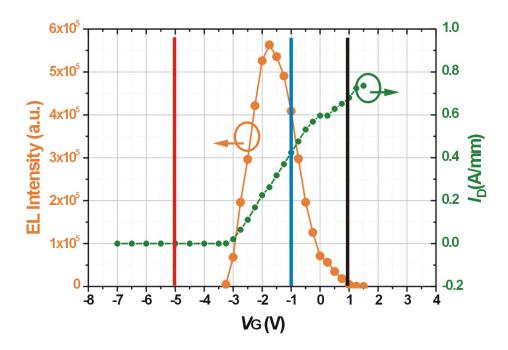

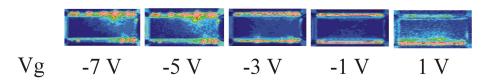

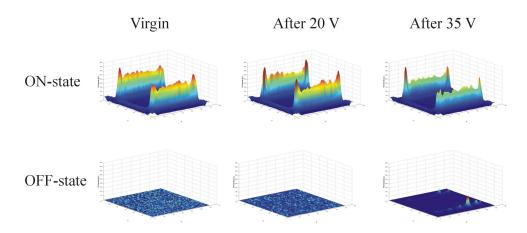

A typical EL image at  $V_{DS}=10~V$  and  $V_{GS}=-1~V$  (ON-state) with integration time is 1 s is shown in Fig. 3.5. EL emission at ON-state condition is generated in the active areas between gate-drain contacts and relatively homogeneous.

Typical normalized EL intensity of AlGaN/GaN HEMTs vs. transfer characteristics is shown in Fig. 3.6. The EL intensity curve starts when the 2DEG channel begins to open and increases abruptly. The peak of EL intensity is located at about a quarter of maximum drain current. With respect to the spectral distribtuion of the EL light, Ref. [98] observed a broad peak at around 670 nm ( $\sim 1.85 \; \text{eV}$ ) of AlGaN/GaN HEMTs EL spectrum. This EL spectrum is different from unbiased PL spectra, however impact ionization is unlikely the source of EL in AlGaN/GaN HEMTs.

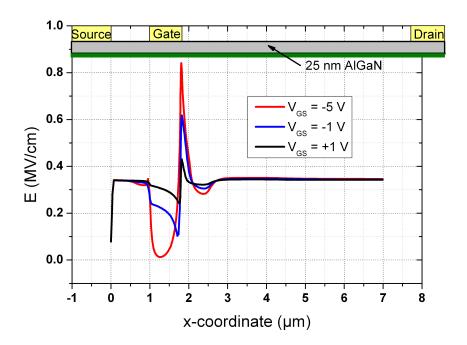

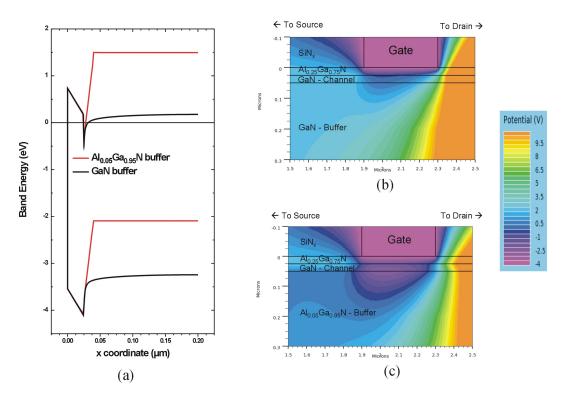

Fig. 3.7 shows our simulation of electric fields of AlGaN/GaN HEMT

Figure 3.5 Superimposed emission and optical image of AlGaN/GaN HEMT 2x125  $\mu$ m device at  $V_{DS}=10$  V and  $V_{GS}=-1$  V (ON-state).

device in the channel during transfer characteristics at three  $V_{GS}$  bias points (marked in Fig. 3.6). This electric field simulation explains the EL intensity evolution vs. transfer characteristics in Fig. 3.6 as the following: when 2DEG channel is pinched-off ( $V_{GS}=-5$  V), the electric peak reachs the maximum value of 0.85 MV/cm under the gate in the drain side. The electric field decreases slightly ( $\sim 0.6$  MV/cm) when the 2DEG channel is open and drops further about 0.4 MV/cm when gate voltage increases ( $V_{GS}=+1$  V). Kolnik et al. calculated the threshold of electric field for electrons to occupy the second conduction band in  $\Gamma$  direction of wurtzite GaN bulk is to 0.3 MV/cm [99]. The electric field simulation results in an electric field intensity of typically of 0.6 MV/cm at ON-state which more than enough to excite electrons in the channel occupying the second conduction band in  $\Gamma$  direction.

When the gate-source voltage  $V_{GS}$  further increases i.e.  $V_{GS} = +1 \text{ V}$ , the drain current  $I_D$  increases as well. This results in a more homogeneous distribution of the potential along the channel hence the electric field peak

Figure 3.6 The typical EL intensity vs. transfer characteristics at  $V_{DS}=10~V$  shows a bell-shaped curve EL with its peak around a quarter of the maximum drain current  $I_D$ . The red, light blue and black lines are electric field simulation points in the 2DEG channel at  $V_{GS}=-5~V$ , -1 V and +1 V respectively (see to Fig. 3.7).

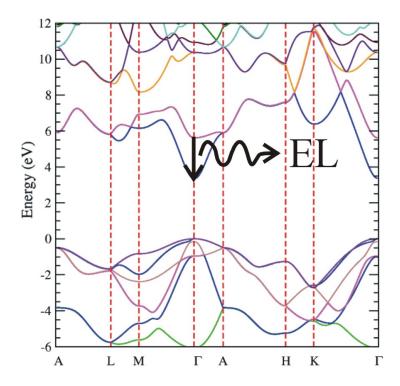

at the drain edge of the gate is reduced. This is described as electric field decrease, and explains drop of the EL intensity at high gate-source voltage i.e.  $V_{GS} = +1$  V. Ref. [99] calculated the difference between first and second conduction band in WZ GaN bulk at  $\Gamma$  direction is about 2.2 eV. Therefore, it is plausible to explain the peak of the EL spectrum at 670 nm as intra-band transition [98] as depicted in Fig. 3.8.

We have frequently performed EL measurements to characterize GaN devices before and after stressing. EL measurements in this work have been performed at the Technical University Berlin using a Hamamatsu Photon Emission Microscope (Phemos 1000) in the darkness. The system is equipped with a liquid nitrogen cooled Si-CCD detector (- 50 °C) with spectral sensitivity in the visible and near infrared regime. The EL measurements were performed along the transfer characteristics. The total EL intensity is counted from emission distribution over the two finger devices.

Figure 3.7 Simulation of absolute intensity of electric field of AlGaN/GaN HEMT device with 25 nm thickness of AlGaN layer and 0.7  $\mu$ m gate length. The electric fields are calculated in the channel (26 nm depth from the surface along the green line) with bias conditions:  $V_{DS}=10~V$  and  $V_{GS}=-5~V$  (red line), -1 V (blue line) and +1 V (black line) [Courtesy of E. Bahat-Treidel].

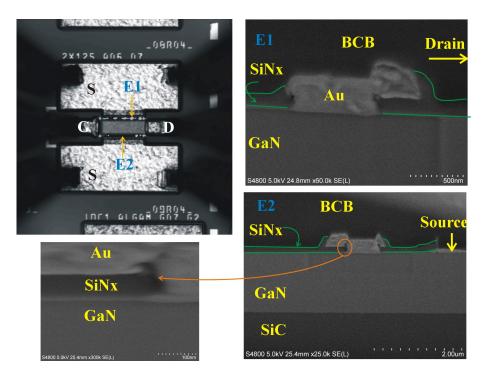

### 3.5 Localized structural analysis

Cross-sectioning methods are required to investigate the structural built-up and possible structural and compositional changes in devices. We applied two commonly used methods to obtain a device cross-section: mechanical grinding followed by ion milling and focused ion beam (FIB) technique. The obtained samples were subsequently analysed using transmission electron microscopy (TEM). Compared to FIB preparation the mechanical grinding method is extremely time consuming. Furthermore, using this conventional preparation method it is often impossible to prepare strongly localized small device areas. On the other hand this method introduces a less number of artifacts into the prepared cross-section, whereas FIB preparation uses bombarding by Ga<sup>+</sup> ions and often results in Ga ion implantation, strong surface amorphization and even formation of liquid Ga droplets on the lamellae sur-

Figure 3.8 Schematic of EL explanation from intra-band transition [98]. Electrons are being excited by high electric field and occupying the second conduction band in  $\Gamma$  direction. These electrons can emit photon during transition to the first conduction band. WZ GaN energy band structure is after [100].

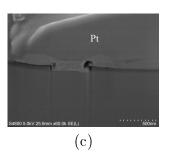

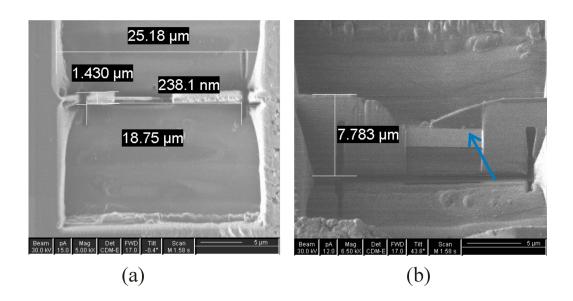

face. However, FIB preparation has a good advantage that it can be used to cut a localized area of interest to see the cross-section of device structures. To minimize the unintentional damage caused by the FIB preparation, one should protect the localized areas of interest using e.g.Pt coating (see the difference of FIB cross-sectioning with and without Pt coating in Fig. 3.9).

FIB preparation conditions for lamella:

- 2  $\mu$ m thick Pt stripe deposition of area 25  $\mu$ m x 2  $\mu$ m, the current is 1000 pA, filled box with dwell time of 0.2 s was performed in 3 min.

- Regular cross section (RCS) for area of 25  $\mu$ m x 15  $\mu$ m, the current is 2700 pA, dwell time of 1 s, was performed in 40 min. Estimated depth is about 8  $\mu$ m.

- Cleaning cross section (CCS) for area of 25  $\mu$ m x 1.4  $\mu$ m, the current is 1000 pA, dwell time of 1 s, was performed 20 min. The sample

Figure 3.9 Cross-section of gate area of AlGaN/GaN HEMT devices obtained by (a) mechanical grinding (notice T-gate wings are not symmetric), (b) by FIB without Pt coating and (c) by FIB with the protecting Pt coating. Without Pt Ga ion used in FIB cause a roughening of the gate metal wall (b). Note: (b) and (c) are the cross-sectioned T-gate in the same device [Courtesy of P. Kotara].

is rotated by  $180^\circ$ , then RCS and CCS were performed with the same conditions above. The lamella thickness is about 700 nm. Then sample was tilted by  $45^\circ$  for U-cut.

- Filled box was determined for area of 18  $\mu$ m x 0.7 mm, the current is 350 pA in 15 min. The sample is rotated again by 180°.

- Filled box was determined for area of 18  $\mu$ m x 0.7 mm, the current is 350 pA in 15 min. The sample is tilted back for window cut.

- CCS for area of 7  $\mu$ m x 0.6  $\mu$ m with the current of 350 pA, dwell time of 1 s, was performed in 2 min.

- CCS for area of 7  $\mu$ m x 0.4  $\mu$ m with the current of 150 pA, dwell time of 1 s, was performed in 2 min. The sample is rotated by 180°.

- CCS for area of 7  $\mu$ m x 0.6  $\mu$ m with the current of 350 pA, dwell time of 1 s, was performed in 2 min.

- CCS for area of 7  $\mu$ m x 0.4 $\mu$ m with the current of 150 pA, dwell time of 1 s, was performed in 2 min. The sample is tilted by 45°, to free the cutting.

- Filled box was determined with the current of 150 pA in 2 min.

Images of window thinning and U-cut of lamella prepared by FIB is shown in Fig. 3.10.

It is important to notice that in order to achieve a good electron transparency for TEM, the lamellae thickness should be in the range of about 100

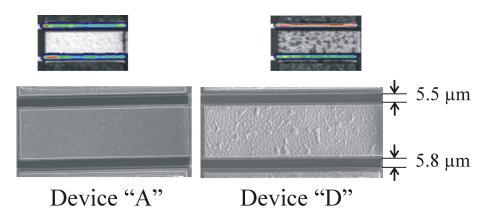

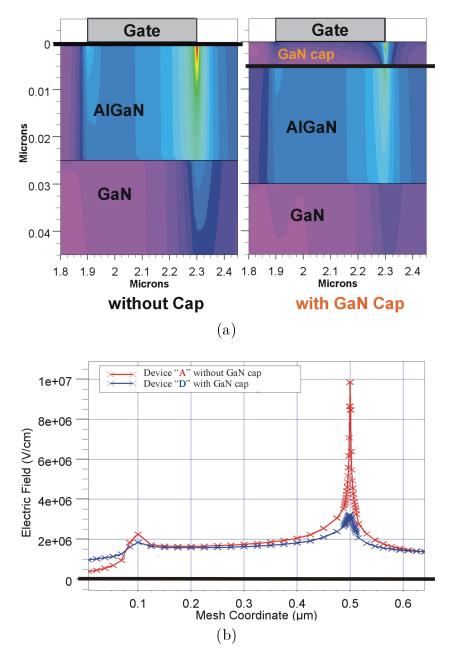

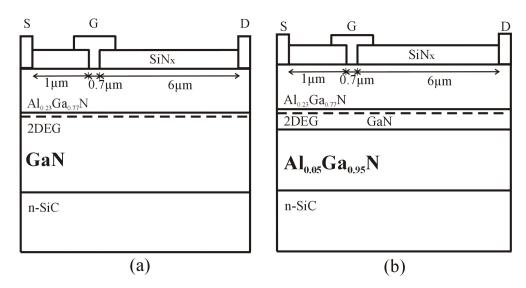

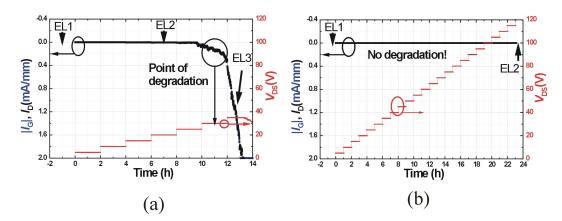

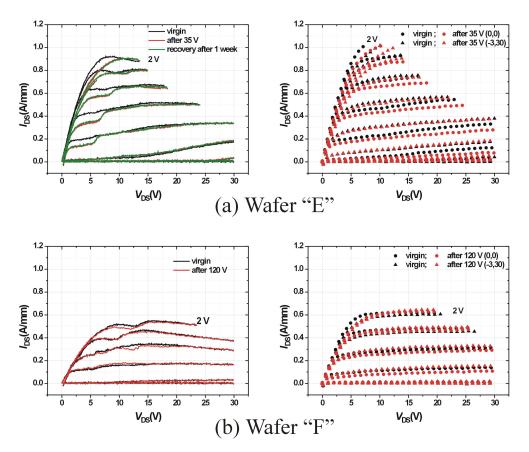

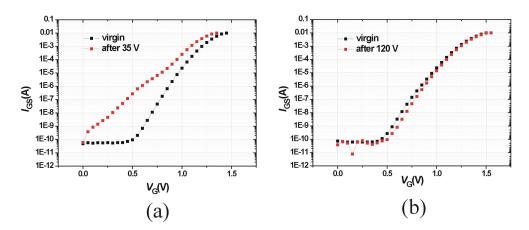

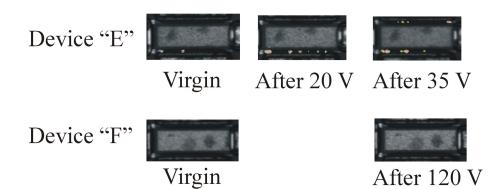

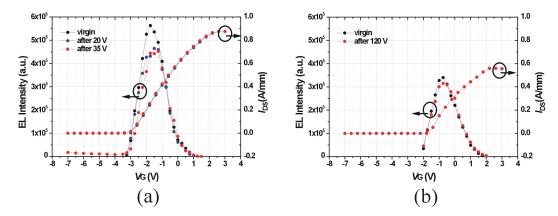

Figure 3.10 Lamella preparation by FIB shows window thinning of the area of interest from (a) top view and (b) side view. U-cuts are shown at both sides of window. A blue arrow points the gate position [Courtesy of U. Zeimer].