### Reliability Study of Stud Bump Bonding Flip Chip Assemblies on Molded Interconnect Devices

vorgelegt von Dipl.-Ing. Marc Dreßler aus Stuttgart

Von der Fakultät IV – Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften Dr.-Ing.

genehmigte Dissertation

Promotionsausschuss:

| Vorsitzender: | Prof. DrIng. H. Klar            |

|---------------|---------------------------------|

| Berichter:    | Prof. DrIng. Dr. E.h. H. Reichl |

| Berichter:    | Prof. DrIng. B. Wunderle        |

Tag der wissenschaftlichen Aussprache: 5. Februar 2010

Berlin 2010 D83 So eine Arbeit wird eigentlich nie fertig, man muß sie für fertig erklären, wenn man nach Zeit und Umständen das mögliche getan hat.

> Johann Wolfgang von Goethe Italienische Reise, 1787

#### Summary

The Stud Bump Bonding (SBB) flip chip technology on Molded Interconnect Devices (MID) is a highly promising solution to the increasing demand for reliable interconnection technology at high temperatures, a miniaturized assembly and a reduction of costs and parts.

The reliability and potential failure mechanism of the flip chip technology on organic boards, such as FR4, invoking the solder bump technology is widely studied, whereas the failure mechanism and therefore the criteria to optimize a SBB flip chip interconnection on MID was still largely unknown.

Carrying out thermal cycling, this work shows for the first time that the SBB flip chip technology used in combination with Printed Wiring Boards based on the MID technology is a highly reliable packaging technology. Using requirements set by the automotive industry, such as exposing the assembled flip chip interconnections to thermal cycles between 150  $^{\circ}$ C and -40  $^{\circ}$ C, no single electrical failure is detected; it was tested until 3000 thermal cycles.

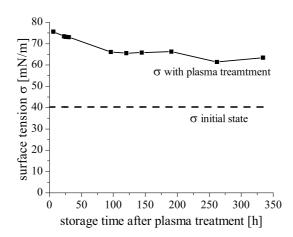

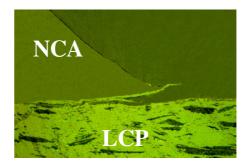

In order to consider a greater technology variety, two different kinds of SBB flip chip technologies were studied: isotropic conductive adhesive (ICA) in combination with capillary underfill (UF), as well as no-flow underfill such as non-conductive adhesive (NCA). Moreover, for both technologies, two different underfill respectively NCA materials were used, which further support the analysis. Additionally, two different chip sizes and board thicknesses were used. The influence of oxygen plasma treatment of the surface of the LCP board was investigated, which strongly influences the wetting angle between substrate and underfill.

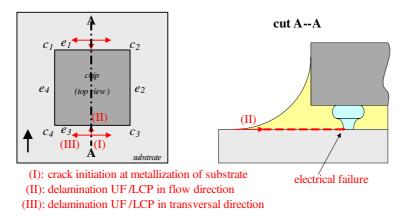

This work proves that in thermal cycling of this kind of packaging technology, two failure mechanisms are dominant. A systematic and detailed investigation of potential failure mechanism by means of a complete literature study followed by Finite Element (FE) Analysis of the interconnection were performed. Two potential failure mechanisms were initially theoretically proposed: bulk fillet cracking and delamination between board and underfill. Then, experimental reliability analysis of the SBB flip chip technology on MID boards was carried out and univocally verified the theoretically proposed failure mechanisms, proving that the failure mechanisms can occur simultaneously. Failure originating from the bump area was not detected.

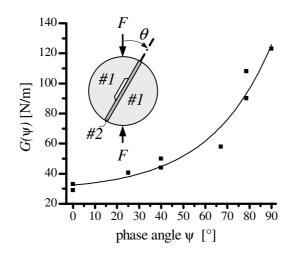

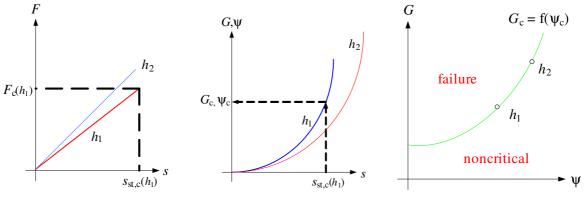

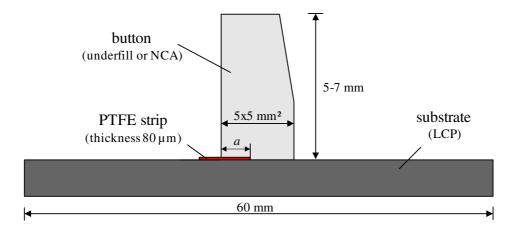

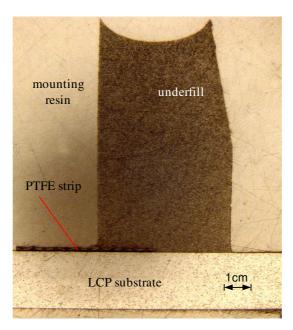

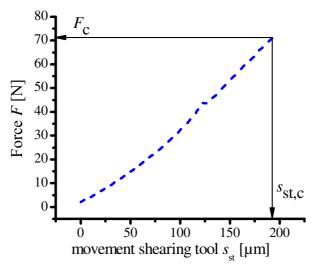

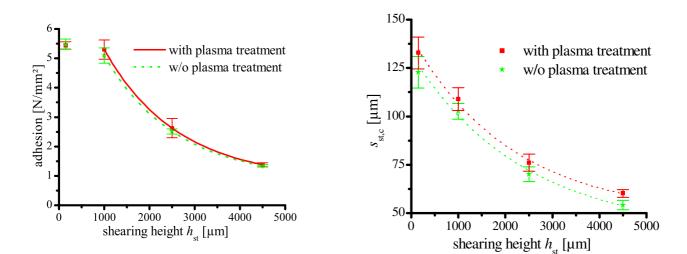

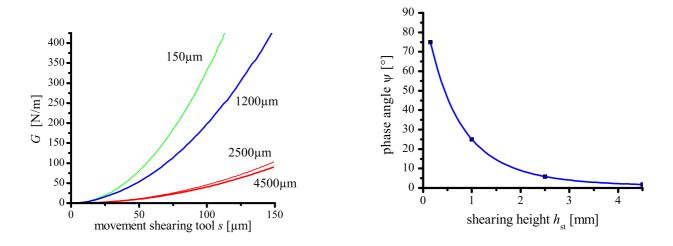

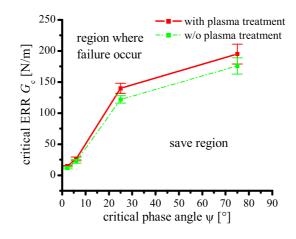

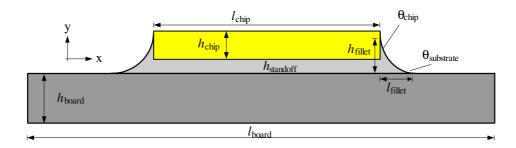

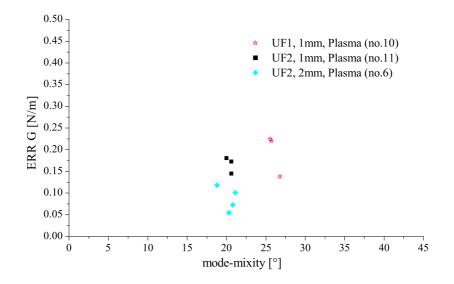

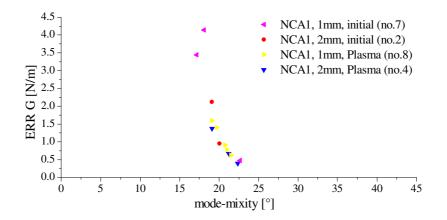

For investigating the delamination risk, a highly innovative enhancement, suitable for industrial use, of the button-shear-test for measuring the interfacial toughness of an underfill/substrate interface was developed. Since adhesion depends strongly on the ratio between shearing and tension loading of the interface, it is necessary to measure the toughness at different phase angles. With the enhanced button-shear-test, which is based on correlation of FE analysis and experimental testing, the phase angle can be widely varied using a single test specimen and different shearing heights. The obtained dependence conforms with values from the literature, which are mostly obtained from cumbersome testing on various test setups. The failure for the tested structure appeared in the upper layer of the thermoplastic board material LCP. Therefore, plasma treatment of the LCP did not show great improvement of the adhesion.

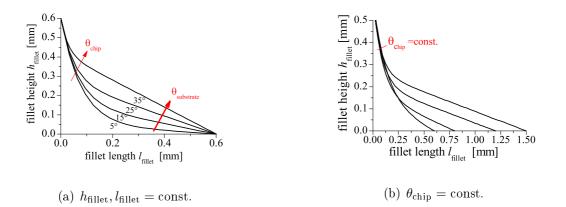

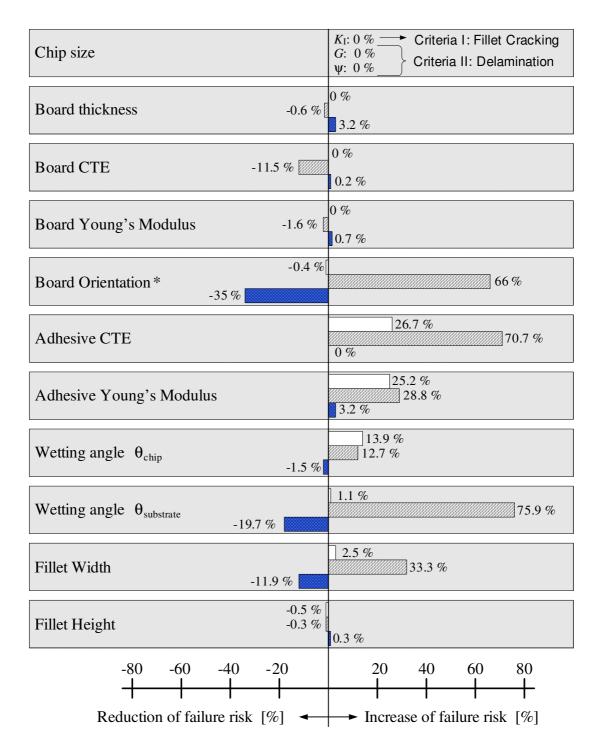

The proposed failure mechanisms were used to create a guideline to optimize SBB flip chip interconnections. The general conclusion can be drawn that the two failure mechanisms were strongly influenced by local parameters. Parameters which influence the global behavior of the flip chip interconnection such as the chip size and the thickness of the board show negligible influences on the failure mechanisms. A higher impact was observed via the CTE value and Young's modulus of the adhesive. The lower the CTE value and Young's modulus, the lower the risk of bulk fillet cracking. An increase of the adhesive CTE value by 25 %, as well as the wetting angle between underfill and substrate, increase the risk of delamination by almost 75 %.

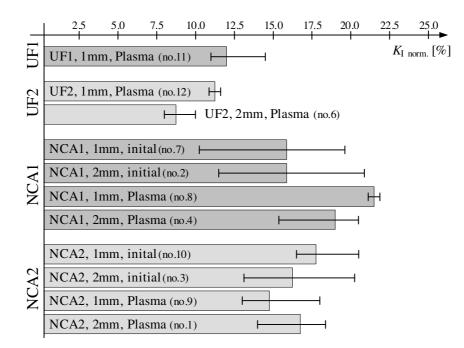

Comparing the impact of the used adhesives on the risk of fillet cracking and delamination, the unfilled adhesive NCA1 shows the highest risk for both failure mechanisms. This is due to the higher CTE value of NCA1 compared to the other utilized adhesives. Even more, the measured critical stress intensity factor  $K_{\rm Ic}$  for that adhesive is much lower. Since the fillet formation is different for every adhesive, and the formation shows a very high impact on fillet cracking, the impact of the adhesive properties can not be experimentally verified using flip chip assemblies.

Based on the results of the present work, optimization of SBB flip chip interconnections on MID boards is based on the present work already possible in the design phase. There are only two failure mechanisms for this kind of interconnection technology when exposed to thermal cycling. Failure at the bump is not a failure mechanism for the studied packaging technology. The proposed guidelines support the selection of the appropriate underfill, board material and geometry such as thickness and chip size. Additionally, the results of this work clearly indicate the use of oxygen plasma treatment on the LCP board prior to flip chip assembly.

#### Zusammenfassung

Die Stud Bump Bonding (SBB) Flip-Chip Technologie auf MID Substraten ist eine vielversprechende Lösung für die wachsende Nachfrage nach zuverlässigen Aufbau- und Verbindungstechnologien bei gleichzeitiger Miniaturisierung und Reduktion von Kosten und Komponenten.

Potentielle Fehlermechanismen und deren Einflüsse auf die Zuverlässigkeit von gelöteten Flip-Chip Verbindungen auf organischen Substraten wurden bereits in zahlreichen Studien untersucht. Hingegen waren im Vorfeld dieser Arbeit die Fehlermechanismen sowie die Einflussfaktoren auf die Zuverlässigkeit von SBB Flip-Chip Verbindungen auf thermoplastischen MID Substraten weitgehenst noch unbekannt.

Diese Arbeit zeigt, dass die SBB Flip-Chip Technologie in Kombination mit der MID Substrat-Technologie eine höchst zuverlässige Aufbau- und Verbindungstechnik (AVT) darstellt. Basierend auf Automotive Anforderungen konnte gezeigt werden, dass diese AVT Technologie Temperaturwechsel-Lagerungen zwischen 150 °C und -40 °C ohne jegliche elektrische Ausfälle widersteht. Die Untersuchungen wurden bis 3000 Zyklen durchgeführt.

Es kamen zwei unterschiedliche SBB Technologien zum Einsatz. Zum einen wurde ein isotrop leitfähiger Klebstoff (ICA) zusammen mit einem Underfiller (UF) verwendet um eine elektrische und mechanische Verbindung zwischen Silizium-Chip und MID Substrat aufzubauen. Zum anderen wurde die SBB Flip-Chip Technologie mit einem nicht elektrisch leitfähigen Klebstoff (NCA) zum Verbindungsaufbau zwischen Chip und Substrat verwendet. Für beide Technologien wurden jeweils zwei Underfiller bzw. zwei NCAs untersucht. Um experimentell noch weitere Einflussparameter auf die Zuverlässigkeit beurteilen zu können, wurden zusätzlich zwei unterschiedliche Chipgrößen und Substratdicken zur Herstellung der SBB Flip-Chip Verbindungen eingesetzt. Darüber hinaus wurde der Einfluss der Oberflächenbehandlung mit Sauerstoffplasma untersucht welche den Benetzungswinkel und Meniskusform stark beeinflusst.

Eine systematische und detaillierte Zusammenstellung von potentiellen Ausfallmechanismen für SBB Flip-Chip Anwendungen basierend auf einer Literaturübersicht wurde durchgeführt. Es konnten zwei potentielle Fehlermechanismen identifiziert werden. Eine Finite Elemente Analyse der Spannungen und Dehnungen im Klebstoff-Meniskus unterstützt diese Zusammenstellung weiter. Zum einen ist dies eine Rissentstehung im oberen Teil des Meniskus. Zum anderen wird eine Delamination-Entstehung zwischen dem Substrat und der Unterfüllung bzw. Klebstoff als Ausfall vorhergesagt.

In den Zuverlässigkeitsuntersuchungen konnten die beiden theoretisch vorhergesagten Ausfallmechanismen bei SBB Verbindungen experimentell nachgewiesen werden. Es konnte gezeigt werden, dass die beiden Mechanismen auch gleichzeitig auftreten können. Eine Ausfallinitiierung bzw. Versagen in der Nähe der Stud Bumps wurde, wie theoretisch ebenfalls vorhergesagt, nicht detektiert.

Der standardisierte Haftkegel-Test wird verwendet um einfach und kostengünstig die Haftung zwischen unterschiedlichen Substraten zu bestimmen. In dieser Arbeit wurde dieser Test erweitert um das Delaminationsrisiko zwischen dem MID Substrat und den Klebstoffen zu charakterisieren. Die Adhäsion hängt stark von dem Verhältnis aus Scher- und Zugspannung im Bereich einer Delamination ab, dem so genannten Phasenwinkel. Daher ist es entscheidend, die Haftfestigkeit bei unterschiedlichen Phasenwinkeln zu bestimmen. Mit Hilfe des in dieser Arbeit erweiterten Haftkegeltests kann eine weite Variation des Phasenwinkels mit nur einem einzigen Testaufbau realisiert werden. Hierbei wird eine Korrelation zwischen Finite-Elemente Analyse und experimentellen Schertests bei unterschiedlichen Scherhöhen verwendet. Die Abhängigkeit der Haftfestigkeit von dem Phasenwinkel ist im Einklang mit Arbeiten aus aufwendigen Tests an unterschiedlichsten Probengeometrien. Das Versagen bei der Untersuchung der Haftfestigkeit trat in der obersten, äußerst dünnen Spritzgusshaut des LCPs ein. Daher konnte mit der untersuchten Oberflächenbehandlung mit Sauerstoff-Plasma kaum eine Haftfestigkeitssteigerung erreicht werden.

Die theoretisch vorhergesagten Ausfallmechanismen dienten als Basis um einen Auslegungs-Leitfaden für die Optimierung von SBB Flip-Chip Verbindungen auf MID Substraten zu erstellen. Grundsätzlich kann ausgesagt werden, dass die beiden Ausfallmechanismen sehr stark von lokalen Geometrien und Materialeigenschaften in der Umgebung der kritischen Bereiche abhängen. Größen, die das globale Verhalten der Verbindung beeinflussen, haben einen zu vernachlässigen Einfluss auf die Ausfallmechanismen. Dies sind die Chipgröße, die Substratdicke sowie die Substrateigenschaften.

Eine große Auswirkung auf die betrachteten Vergleichsgrößen haben der thermische Ausdehnungskoeffizient (CTE) und das E-Modul des Klebstoffs. Je niedriger der Ausdehnungskoeffizient und das E-Modul, desto geringer ist das Risiko einer Rissentstehung im oberen Teil des Meniskus. Eine Erhöhung des CTE-Werts um 25% erhöht das Risiko eines Ausfalls um fast das Dreifache. Ebenso kann das Delaminationsrisiko zwischen Klebstoff und Substrat reduziert werden, wenn der Benetzungswinkel so klein wie möglich gehalten wird. Eine Erhöhung des Winkels um 25% zieht eine Erhöhung des Delaminationsrisikos um mehr als 75% nach sich.

Vergleicht man den Einfluss der eingesetzten Klebstoffe auf das Risiko für eine Riss-Initiierung im Underfill Meniskus und Delamination, zeigt NCA1 zeigt das höchste Risiko hinsichtlich beider Ausfallmechanismen. Dies kann auf den höheren Ausdehnungskoeffizienten des NCA1 im Vergleich zu den anderen eingesetzten Klebstoffen zurückgeführt werden. Darüber hinaus zeigt NCA1 auch den niedrigsten kritischen Spannungsintensitätsfaktor  $K_{\rm Ic}$ der verwendeten Klebstoffe. Da jedoch die Meniskusausbildung sehr stark vom eingesetzten Klebstoff abhängt, und die Meniskusausbildung einen sehr großen Einfluss auf die untersuchten Ausfallmechanismen besitzt, kann der Einfluss der Material-Eigenschaften des Klebstoffes nicht anhand der Ergebnisse der Zuverlässigkeitsuntersuchungen der Flip Chip-Verbindungen experimentell verifiziert werden.

Mit Hilfe der Ergebnisse der hier vorliegenden Arbeit kann eine Optimierung und daher Zuverlässigkeitssteigerung einer SBB Flip-Chip Verbindung auf MID Substraten bereits in der Auslegungsphase durchgeführt werden. Der Leitfaden hilft bei der Auswahl der geeigneten Klebstoffe, Substratmaterialien und Geometriegrößen wie Substratdicke und Chipgröße. Als Ergebnis dieser Arbeit ist zudem festzuhalten, dass die Oberflächenbehandlung mit Sauerstoffplasma einen unabdingbaren Prozessschritt darstellt um die Zuverlässigkeit von SBB Flip-Chip Verbindungen auf MID Substraten zu erhöhen.

#### Danksagung

Die vorliegende Arbeit entstand während meiner Tätigkeit als Doktorand bei der Robert Bosch GmbH, Forschung und Vorausentwicklung, Bereich Kunststoffe in Waiblingen und dem Fraunhofer Institut für Zuverlässigkeit und Mikrointegration in Berlin.

Mein Dank gilt Prof. Dr. Dr. Herbert Reichl für die Betreuung dieser Arbeit und für seine wertvollen fachlichen Anregungen.

Ganz besonders möchte ich Prof. Dr. Bernhard Wunderle für seine intensiven fachlichen Diskussionen, sein permanentes Engagement und Interesse an der Arbeit danken, und auch für die Übernahme des zweiten Gutachtens.

Herrn Karl-Friedrich Becker vom IZM in Berlin möchte ich für seine fachliche Betreuung, ständige Hilfsbereitschaft und wertvollen Diskussionsbeiträge, besonders was Messmethodiken und Zuverlässigkeitsuntersuchungen anbelangt, danken.

Danke sagen möchte ich auch an Dr. Hans Walter, Dr. Olaf Wittler und Dr. Jürgen Auersperg vom Fraunhofer Institut für die Diskussionen und Hinweise zum Gelingen der Arbeit.

Herrn Hartmut Rohde danke ich für die Initiierung des Promotionsthemas, fachliche Betreuung und die Einführung in die Bosch- und MID-Welt, und nicht zu vergessen in die Welt der effektiven Geschäftsreisen. Die Einbindung in die Gruppe CR/APP4 bei Bosch unter der Leitung von Herrn Dr. Gerhard Liebing trug zum Gelingen der Arbeit bei. Ein ganz besonderer Dank möchte ich auch an Herrn Frieder Sundermeier für die zum Ende hin finanzielle Unterbringung der Arbeit in seinem Projekt richten, sowie den Herren Ulrich Schaaf, Andreas Kugler, Dr. Patrick Stihler und Kai von Garnier für die Unterstützung bei den experimentellen Arbeiten.

Ein herzliches Dankeschön geht an meine damaligen Mitdoktoranden Frau Dr. Tanja Alxneit, Herrn Dr. Richard Löw und Herrn Jan Göhler für die angenehme und motivierende Arbeitsatmosphäre.

Meiner Frau Sarah möchte ich für die Geduld während der Phase des Verfassens der Arbeit von ganzem Herzen danken, sowie für die gründliche und geduldige Korrektur dieser Arbeit.

# Contents

| $\mathbf{S}$ | um   | mary                                                                         | Ι    |

|--------------|------|------------------------------------------------------------------------------|------|

| $\mathbf{Z}$ | usa  | mmenfassung                                                                  | III  |

| D            | anl  | ksagung                                                                      | VI   |

| Ι            | In   | ntroduction                                                                  | 1    |

| 1            | Intr | roduction                                                                    | 2    |

| 2            | Tec  | chnological Description of SBB Process and MID                               | 5    |

| IJ           | [ ]  | Theoretical Assessments, Models and Assemblies                               | 12   |

| 3            | Ide  | ntification of Potential Failure Mechanism of SBB Flip Chip Interconnections | 13   |

| 4            | The  | eory of Bulk and Interfacial Fracture Mechanics                              | 20   |

|              | 4.1  | Linear Elastic Fracture Mechanics (LEFM)                                     | . 20 |

|              | 4.2  | Stress Field at Crack Tip                                                    | . 22 |

|              |      | 4.2.1 Bulk Crack                                                             | . 22 |

|              |      | 4.2.2 Interfacial Crack                                                      | . 24 |

|              | 4.3  | Energy Release Rate                                                          | . 27 |

|              |      | 4.3.1 Concept                                                                | . 27 |

|              |      | 4.3.2 EBB for Interfacial Fracture Mechanics                                 | 29   |

| 5 | Ma  | terial ( | Characterization                                           | 30 |

|---|-----|----------|------------------------------------------------------------|----|

|   | 5.1 | Releva   | ant Material Properties                                    | 30 |

|   | 5.2 | Used     | Materials                                                  | 31 |

|   |     | 5.2.1    | Underfills and NCAs                                        | 31 |

|   |     | 5.2.2    | Liquid Crystal Polymer (LCP)                               | 32 |

|   | 5.3 | Mode     | ing of Visco-Elastic Material Behavior                     | 34 |

|   | 5.4 | Coeffi   | cient of Thermal Expansion (CTE)                           | 41 |

|   | 5.5 | Calcu    | lation of Properties for Interface Adhesive/LCP            | 43 |

| 6 | Cri | tical B  | ulk and Interfacial Fracture Toughness                     | 44 |

|   | 6.1 | Crack    | Initiation and Propagation in Homogenous Media             | 44 |

|   | 6.2 | Fractu   | re Toughness of Interfacial Cracks                         | 47 |

|   |     | 6.2.1    | Overview of Interfacial Fracture Toughness                 | 47 |

|   |     | 6.2.2    | Work Flow of the Button Shear Test                         | 49 |

|   |     | 6.2.3    | Experimental Setup and Testing                             | 50 |

|   |     | 6.2.4    | Measurements of Adhesive Strength NCA on LCP               | 52 |

|   |     | 6.2.5    | FE-Analysis to Calculate ERR and Mode-Mixity               | 55 |

|   |     | 6.2.6    | Correlation to Obtain Interfacial Fracture Toughness       | 57 |

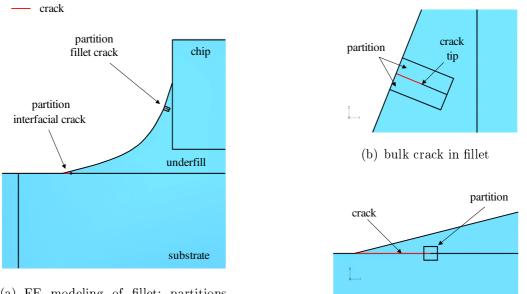

| 7 | FE- | Mode     | ling, Stress Analysis and Establishing Failure Criteria    | 59 |

|   | 7.1 | FE-m     | odeling of Flip Chip Interconnection                       | 59 |

|   |     | 7.1.1    | Parameterized FE-Modeling                                  | 59 |

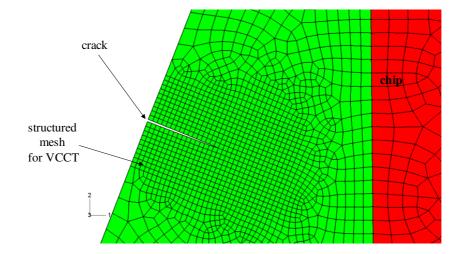

|   |     | 7.1.2    | VCCT Implementation and Calculation of Energy Release Rate | 61 |

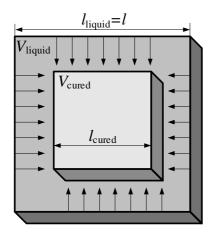

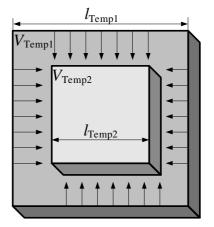

|   |     | 7.1.3    | Assessment of Curing Shrinkage                             | 63 |

|   |     | 7.1.4    | Material Models and Applied Load                           | 66 |

|   | 7.2 | Stress   | Analysis of SBB Flip Chip Interconnection                  | 68 |

|   |     | 7.2.1    | Stress Analysis Without Crack                              | 68 |

|   |     | 7.2.2    | Assessment of Stress Concentration at Upper Part of Fillet | 70 |

|   |     | 7.2.3    | Assessment of Delamination Adhesive/Board                  | 74 |

| 8                                          | Cha | aracter | ization of Flip Chip Assemblies                              | 76  |

|--------------------------------------------|-----|---------|--------------------------------------------------------------|-----|

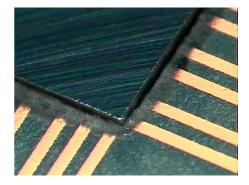

|                                            | 8.1 | Layou   | t and Characterization of MID substrates                     | 76  |

|                                            |     | 8.1.1   | Layout of the MID substrates                                 | 76  |

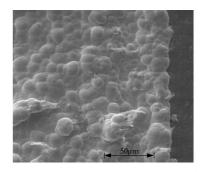

|                                            |     | 8.1.2   | Metallization Process and Characterization of MID Substrates | 77  |

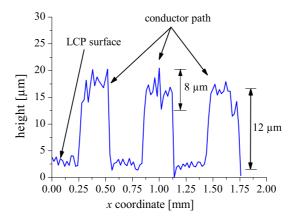

|                                            |     | 8.1.3   | Surface Properties of LCP Substrate                          | 78  |

|                                            | 8.2 | Flip (  | Thip and Stud Bump Bonding Process                           | 79  |

|                                            |     | 8.2.1   | Process Description of Stud Bumping                          | 79  |

|                                            |     | 8.2.2   | Stud Bump Bonding Process                                    | 81  |

|                                            |     | 8.2.3   | Studied Flip Chip Assemblies                                 | 83  |

| 8.3 Characterization of Flip Chip Assembly |     |         |                                                              | 84  |

|                                            |     | 8.3.1   | Warpage Measurements                                         | 84  |

|                                            |     | 8.3.2   | Fillet Formation                                             | 88  |

| I                                          | I   | Reli    | ability Studies                                              | 90  |

| 9                                          | Des | sign-St | udy by Application of Theoretical Failure Criteria           | 91  |

|                                            | 9.1 | Consi   | derations Concerning Impact of Parameters                    | 91  |

|                                            |     | 9.1.1   | Failure Criteria Used for Design-Studies                     | 91  |

|                                            |     | 9.1.2   | Investigated Design Parameters                               | 94  |

|                                            | 9.2 | Impac   | t of Specific Geometric Parameters and Material Properties   | 95  |

|                                            |     | 9.2.1   | Size of Flip Chip                                            | 95  |

|                                            |     | 9.2.2   | Board Thickness                                              | 96  |

|                                            |     | 9.2.3   | Board Material Properties                                    | 98  |

|                                            |     | 9.2.4   |                                                              | 101 |

|                                            |     | 0.2.1   | Orientation of Orthotropic Board Material                    | 101 |

|                                            |     | 9.2.5   | Orientation of Orthotropic Board Material                    |     |

|                                            |     |         |                                                              | 102 |

| 10 Experimental Verification                                                | 116 |

|-----------------------------------------------------------------------------|-----|

| 10.1 Objective of Experimental Reliability Testing                          |     |

| 10.2 Procedure of Reliability Testing and Failure Definition                |     |

| 10.2.1 Thermal Cycling                                                      |     |

| 10.2.2 Failure Definition                                                   |     |

| 10.3 Experimental Verification of Failure Modes                             |     |

| 10.3.1 Experimentally Observed Failure Mechanism                            |     |

| 10.3.2 Bulk Cracking, Initiating at Corner fillet                           |     |

| 10.3.3 Bulk Cracking, Initiating at Center Fillet                           |     |

| 10.3.4 Delamination Between Board and Adhesive                              |     |

| 10.4 Correlation of Predicted and Experimentally Detected Failure Mechanism |     |

| 10.5 Conclusion                                                             |     |

| 10.6 Outlook                                                                | 130 |

| Appendix                  | 130 |

|---------------------------|-----|

| 11 Abbreviations          | 131 |

| 12 Mathematical Notations | 132 |

| List of References        | 133 |

| Lebenslauf                | 146 |

# Part I

# Introduction

# Chapter 1

## Introduction

The Moore's law has been the proven dictum in semiconductor development for many years now and this will continue to be for the foreseeable future. However, the progress in the semiconductor industry alone will not be able to meet the performance, functionality, miniaturization and cost efficiency requirements of today's microelectronic systems [90]. The packaging technology plays a key role to meet the required miniaturization, increased functionality and reducing costs [89]. In order to achieve these goals, new technologies and materials have to be developed. *Reichl et al.* adds that a rapid market introduction of such new concepts is to be achieved by using state-of-the-art technologies and existing infrastructure, as well as the integration of latest technologies [90].

This is especially true for the development of new packaging concepts for automotive applications, while a rapid introduction of new technologies is important in order to guarantee market leadership, the combination of state-of-the-art technologies with the latest invention reduces the risk when introducing new concepts. One example of such an automotive application is a rotational sensor, Fig. 1.1, which combines the widely-used flip chip technology with the latest substrate technology Molded Interconnect Devices (MID).

MID is capable of realization of new functions which the planar Printed Circuit Board (PCB) technology cannot yet fulfill [17]. The MID technology allows the combination of conductor parts and the housing into a single piece. Thus, it is possible to use three-dimensional injected molded thermoplastic parts as conductor paths, a screening layer and an antenna function. Moreover, the MID parts can be utilized as a carrier for electronic components, as well as for the integration of mechanical elements.

Besides the challenges of the manufacturing and assembly processes, the identification of the failure mechanisms and reliability affecting parameters play a key role in the acceptance of a new packaging concept, particulary for automotive applications.

(a) MID substrate

(b) Flip chip assembled

Fig. 1.1: Example of a sensor for automotive application; using the MID technology as a three dimensional PCB and the flip chip technology to interconnect the chip with the PCB [8, 40]

The packaging concept Stud Bump Bonding (SBB) flip chip on MID is already used for consumer products such as hearing aids [106, 129] and lens holders for cameras [39]. The reliability studies are limited to prove feasibility, rather than identification of failure mechanisms and understanding the impact of certain parameters on reliability. Until now, the packaging technology has not found an entry in automotive applications, particularly because of the exposure occurring to these applications such as thermal cycling and humidity storage.

Failure mechanisms can, among others, be distinguished in overstress and wearout failure mechanisms [114]. Overstress failure mechanisms are defined as an exceeding of the strength or capacity of a component or material within a single event. On the other hand, wearout failure mechanisms take place, when a component is loaded at a much lower level but continuously. Failure mechanisms are fatigue damage, creep, wear, stress-driven voiding and interfacial delamination, etc. Fatigue mechanisms are either fully or partially responsible for 90 % of all structural and electrical failure [114]. In order to ensure that electronic components do not fail by these wearout mechanisms within their required lifetime, different standardized test conditions are set up. For electronic components and systems for Automotive applications, the Automotive Electronics Counsils (AEC) defined qualification tests which are shown in Tab. 1.1. These qualification tests are similar to the MIL standards [1, 2, 3, 124].

Flip chip interconnections are widely studied under the testing conditions listed in Tab. 1.1. Among these conditions, the temperature cycling and humidity biasing are considered to be the tests which are most challenging. In this work, the focus lies on the thermal cycling of SBB flip chip interconnection on LCP substrates. Compared to standard PCB material, like FR4, the substrate material LCP has a different Young's modulus and Coefficient of thermal expansion. This leads primarily to a different CTE mismatches between chip and substrate compared to flip chip interconnections with FR4. Therefore, the focus lies on the reliability performance when exposed to thermal cycling. Moreover, LCP shows a very low humidity Tab. 1.1: Stress test qualification according to AEC Q100 in order to approve a principal suitability of devices; Electrical, environmental, and mechanical tests similar to MIL STD750, MIL STD202, etc. [1, 2, 3, 124]

| Test                      | Conditions                          | Failure allowed                |

|---------------------------|-------------------------------------|--------------------------------|

| Temperature Storage       | 1000 hours at $T_{\rm max}$         | $0 \text{ from } 77 \dots 120$ |

| Temperature Humidity Bias | 1000 hours 85 °C / 85 $\%~\rm RH$   | 0 from 120 231                 |

|                           | $V_{ m max}$                        |                                |

| Temperature Cycling       | 1000 cycles -40 °C to $T_{\rm max}$ | 0 from 120                     |

| Power Temperature Cycling | -40 °C to 125 °C for 1000           | 0 from 231                     |

|                           | cycles                              |                                |

| Vibration                 | 4 minutes at 40 g and 20 Hz $$      | 0 from 231                     |

|                           | to 2000 Hz                          |                                |

absorption in contrast to FR4 or PCB made of flex materials<sup>1</sup>.

The scope of the present work is in the identification of the failure mechanisms of the SBB flip chip interconnection on MID boards. Two different kinds of SBB flip chip technologies are used: the ICA (isotropic-conductive adhesive, plus capillary underfill) and NCA (non-conductive adhesive) technology. The Laser-Direct-Structuring (LDS) is utilized as MID technology. The assembled interconnections are tested under automotive thermal cycling conditions (+150 °C/-40 °C). In order to extend the lifetime of the SBB flip chip interconnections on MID boards, the failure mechanisms are used to create a design guideline. The guideline contains the influence of the chip size, board thickness and surface treatment, utilized SBB technology, as well as the fillet shape.

$<sup>^1\</sup>mathrm{FR4}$  has an absorption of humidity of about 0.9 % [77], where LCP shows an absorption between 0.005 and 0.03% [110]

## Chapter 2

# Technological Description of SBB Process and MID

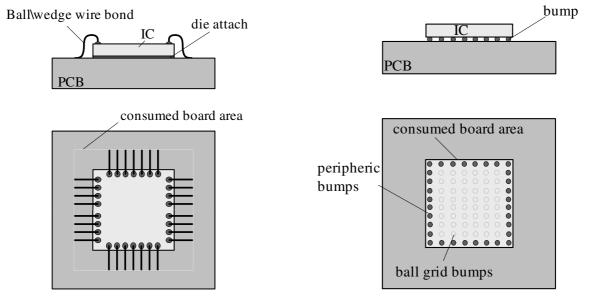

A Stud Bump Bonding (SBB) flip chip interconnection belongs to the class of chip scale packages (CSP). A CSP is defined as an IC package which occupies a footprint area of no more than 50 % greater than the area of the chip it packages [114]. Several varieties of CSP designs are in use today. The main types of CSP are the wirebonding and the flip chip technology, either on flexible or rigid PCB boards [43, 78, 81, 114]. The two technologies are displayed in Fig. 2.1.

In wirebonding, the chip is mounted face up and it's rear surface is directly bonded to the substrate. The interconnection consumes the chip area plus the area needed for the wirebonds. On the contrary, the flip chip assembly requires the lowest footprint area on the substrate and allows additional significant reduction in package height [81]. The mechanical and electrical connections between IC and substrates are established by bumps, mainly made of metals. The flip chip process was first introduced for ceramic substrates by IBM in 1962 as the so-called C4 technology - Controlled Collapse Chip Connection [114].

The flip chip technology can basically be categorized into two different kinds: flip chip assemblies using solder bump technology and flip chip assemblies using adhesives, conductive or non-conductive [80]. For solder bumped flip chip interconnections, the bumps are deposited on solder wettable metal terminals on the active surface of the IC. The pads on the IC matches wettable pads on the PCB [114]. The solder bumps are aligned to the PCB and then reflowed at high temperatures to form simultaneously electrical and mechanical connections. The advantages of the solder bump flip chip technology definitely lies in the high ampacity and the parallel formation of the bumps and the inexpensive bump material. The high reflow temperatures, especially when it comes to leadfree solder materials, play a limiting factor concerning the use of polymer-based PCB material. Moreover, the necessity

(a) Wire bonded chip interconnection

(b) Flip chip interconnection

Fig. 2.1: Overview of the chip scale packages (CSP) wire bonding and flip chip technology; (a): Chip placement on the board using die attach material (solder, adhesives) to establish mechanical and thermal connection; wire bonds using ball/wedge bonding for electrical interconnection; (b): balls made of solder, by gold stud bumping or electroless procedures are used to give mechanical, electrical and thermal connection between IC and substrate; the wire bond assembly consumes board area of the size of the die plus the wire bond loops, whereas the flip chip interconnection does not need more area than the chip itself; comparing the number of I/Os, the flip chip technology is capable of having bumps not only located peripherally along the chip edges but distributed over the whole chip [43, 81, 112, 114]

of applying flux during assembly process limits the reliability of solder joint flip chip interconnections. The flux is used to clean the pads, prevent re-oxidation and increase the heat flow during solder process [32]. The failure mechanisms of solder bumped flip chips assembly and their relevance for SBB flip chip interconnections are discussed below. Alternatively, flip chip assemblies using adhesive bonding are available. The bumps on the pads of the IC are formed mainly by electroplating, electroless plating, or manufacturing of gold stud bumps by using a modified wire bonder [81]. After bump formation, the connection between the IC and the substrate is established using conductive or non-conductive adhesives. The adhesives are cured at elevated temperatures. The main advantages of this kind of flip chip technology are the lower process temperatures during flip chip assembly, as well as that no flux is needed.

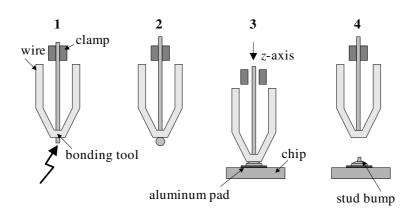

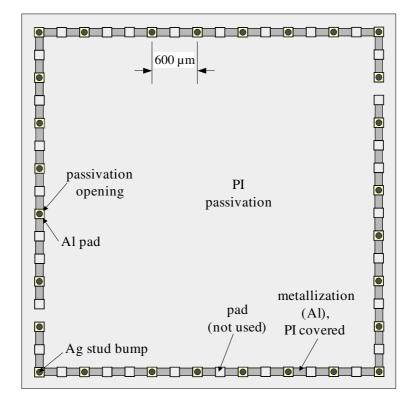

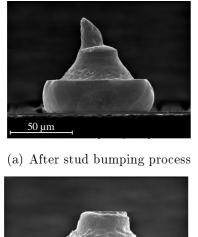

In the present work, the Stud Bumping technology is invoked to form the bumps on the aluminum pads on the IC. It is similar to the ball/wedge wire bonding process. But after creating the ball and placing it on the chip pad, the wire is broken off [81]. This controlled breaking off above the heel is forced by doping the gold wire with 1 to 2 percent palladium [66]. The process is sketched in Fig. 2.2.

Fig. 2.2: Schematic flowchart of gold stud bumping; in the first step: (1) Passing the gold wire through the capillary tube like for conventional wire bonding process, (2) formation of a ball by applying an electrical discharge, (3) placing the ball on the die pad and building up an interconnection of ball and pad by thermocompression and ultrasonic energy, (4) the capillary tube clamping the wire is withdrawn and the wire is cut [39, 66, 81, 112, 129].

Modern wire bonders are capable of placing up to fifteen bumps per second [66, 129].

The flip chip technology Stud Bump Bonding (SBB) Process is a relatively rarely used technology compared to solder bump flip chip technology. Nevertheless, consumer applications such as hearing aids [106, 129], lens holders for cameras and ASIC packaging on flexible printed wiring board [39] are already realized using the SBB process.

There are different kinds of SBB flip chip technologies. The main difference between the methods lays in the way the chip and the substrate are electrically connected [33, 66]. In that study, two methods are used: (1) Using an isotropic-conductive adhesive (ICA) for the electrical connection, together with a capillary underfill (UF) which establishes a stable mechanical connection; (2) the electrical connection of the chip and the substrate is realized via a direct contact of the stud bump to the metallization of the substrate; through its cure shrinkage, a non-conductive adhesive (NCA) secures constant mechanical and therefore electrical contact between the bump and the substrate [127].

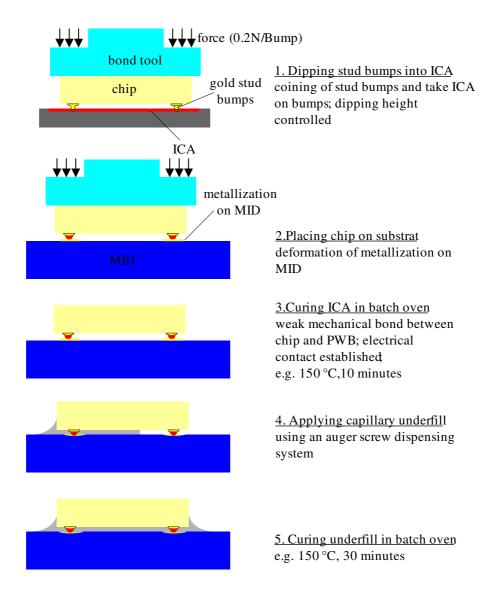

The process flow of the ICA SBB technology is displayed in Fig. 2.4.

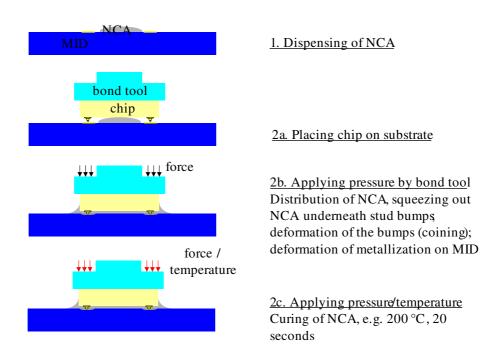

The Stud Bump Bonding Process, which utilizes a non-conductive adhesive, requires less process steps than the ICA SBB process, Fig. 2.3.

The process steps can also be combined or performed in a slightly different sequence. The advantages of the SBB process compared to solder flip chip technology are [66, 91]

• the SBB process is suitable for MEMS and ICs without passivation on the electrical structures

Fig. 2.3: Process Flow: Stud Bump Bonding (SBB) Process using non conductive adhesive (NCA) [66, 87, 127]

- Bumping can be performed on the already diced chip, which makes it especially interesting for small volume applications or prototypes

- It is based on the well-controlled thermosonic wire bonding

- It has the following advantages over the solder bump technology

- no use of lead based materials as well as flux

- lower curing temperatures of the isotropic-conductive adhesive and underfills; very short curing time for the NCA SBB technology

- higher resistance concerning high temperature storage

where the disadvantages are

- Concerning the ICA technology, the handling of the adhesive bonded but yet not underfilled chips can be critical due to the low adhesive bonding of the bumps and the pad on the IC

- Risk of short circuits caused by broken wire tails during coining process

- $\bullet\,$  Stud Bumping is a sequential process which is therefore not cost efficient for high I/O counts.

Fig. 2.4: Process Flow: Stud Bump Bonding (SBB) Process using isotropic conductive adhesive (ICA) together with capillary underfill (UF) [66, 87]

As already mentioned, comparing the manufacturing time of the bumps on the silicon wafer, the solder ball technology shows a significant advantages in contrast to the Stud Bump technology when it comes to high I/O counts. An example of a commercial solder bumping process for deposition on evaporation and plating can be found in [77, 79, 114]. The process can consist of about seven steps on the wafer level: (1) Evaporation of Under Bump Metallization (UBM) and the solder dam, (2) pattern plating and template resist, (3) etching of solder dam, (4) electroplating of the solder, (5) stripping of the photoresist, (6) reflow process to build solder balls and finally (7) etching of the solder dam and UBM. The masks created, especially for a certain chip design, can be used several times for deposition and edging. Performing also the bump creation on the wafer level by the Stud bump technology, the needed time is much higher for high I/O counts. Nevertheless, the creation of the mask is not needed for the Stud bumping process. The assembly of solder ball flip chips consists of dipping of the diced chips with the solder balls in a flux film to transfer flux to the balls. The flux is needed to clean the balls and pads on the substrate from oxides and contaminations. After placing the chip on the substrate, the solder balls are again melted in the reflow process to produce a mechanical and electrical contact between the chip and the substrate through the balls. These steps are performed sequentially for each flip chip and therefore quite similar to the SBB ICA assembly process. The following underfill process is for both technologies, solder ball and SBB ICA flip chip technology, the same, Fig. 2.4.

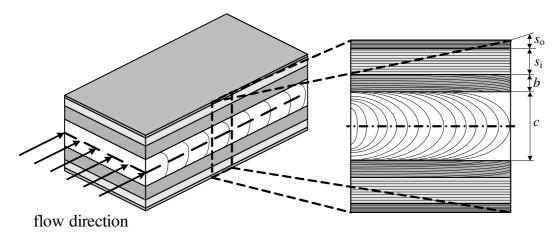

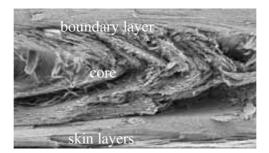

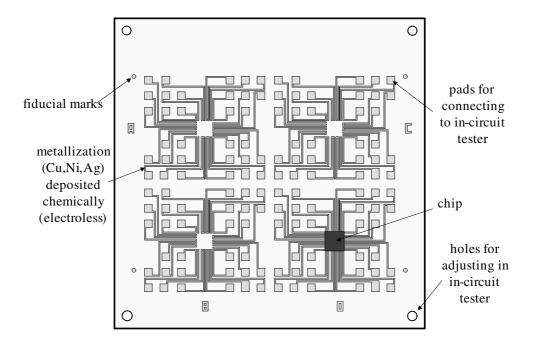

The Stud Bump Bonding flip chip technology obeying the NCA process reduces the number of process step significantly since only the placing of the chip and curing of the NCA is required, Fig. 2.3. The curing has to be performed directly in the chip placer, which lowers the throughput of the chip placer compared to the solder bump and SBB ICA technology where the melting or curing are performed in a reflow or batch oven, respectively. The idea of creating electric interconnections based on thermoplastic materials, produced by injection molding, goes back to the 1960s [18]. The MID technology has the advantage through combining electrical and mechanical functionality. The biggest advantage of the MID technology lies in the realization of three dimensional conductor paths whereas boards based on ceramic or fiber reinforced thermoset materials (e.g. FR4) are mainly limited to two dimensions. An overview of the different MID-technologies can be found in [18, 20, 36, 41, 74]. In the presented work, the MID substrates are fabricated using the Laser Direct Structuring (LDS) technology [50, 61, 62, 97]. The process steps are shown in Fig. 2.5.

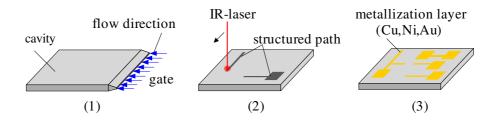

Fig. 2.5: Process flow of LPKF-Direct Laser Structuring (LDS) of a thermoplastic substrate [50, 61, 62];

(1) injection molding of a Liquid Crystal Polymer (LCP); it is modified to be capable of laser activation; the gate is designed as a film gate; (2) LPKF laser structuring of the LCP by an IR laser; (3) deposition of Cu,Ni,Au-layers by chemical deposition

# Part II

# Theoretical Assessments, Models and Assemblies

## Chapter 3

# Identification of Potential Failure Mechanism of SBB Flip Chip Interconnections

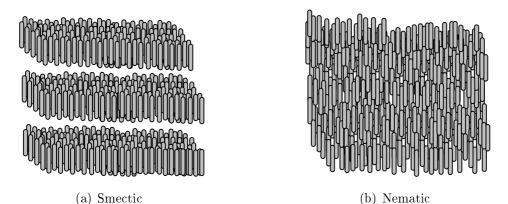

The SBB process is, in comparison to solder bumped flip chip interconnections, a rarely studied technology. The published studies concentrate on the feasibility of the assembly process. No reports are available concerning reliability for SBB flip chip interconnections. As mentioned, the solder bumped flip chip interconnections are the focus of many studies. Therefore, the concepts and failure mechanism used to study the reliability of solder bumped flip chip interconnections with relevance for SBB assemblies are shown and discussed.

Many mechanical and thermo-mechanical systems are described by simple analytical models. Many attempts to cover the behavior of a flip chip interconnection by a simplified system can be found in literature. Flip chip interconnections are simplified by tri- or bi-material-layered system where the fillet and the bumps are neglected: for two-layered systems in [93, 103, 128] and for three-layered systems by [9, 104, 121].

The thermo-mechanical behavior is described by differential equations based on the theory of elasticity. The equations are solved by applying boundary condition, as well as transition conditions between the two or three layers [120]. The solutions are the tensile  $\sigma_{yy}$  and peel stress  $\tau_{xy}$  between the layers as function of the coordinate x. Additionally, the warpage  $\delta(x)$ can be determined.

The advantage of the analytical solutions lies in the simple representation of dependencies of the stresses and warpage on the load and material properties [93, 103]

$$\sigma_{yy}, \tau_{xy} \sim \Delta \alpha \Delta T, E \tag{3.1}$$

$$\delta \sim \Delta \alpha \Delta T, \frac{1}{E}.$$

(3.2)

The warpage  $\delta$  increases with the distance x from the center and reaches its maximum at x = L. The shear stresses  $\tau_{xy}$  between the layers are zero at x = L. This is due to the fact that no lateral forces are present at that position [103]. The peeling stress  $\sigma_{yy}$  decays rapidly when x approaches the center of the composite  $x \to 0$ .

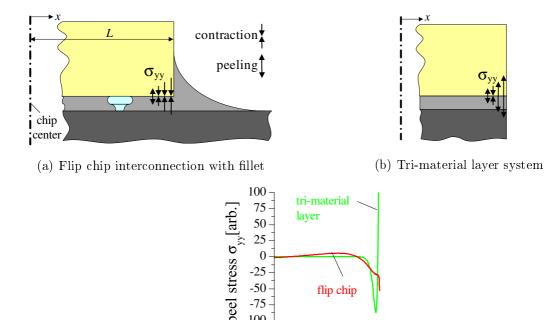

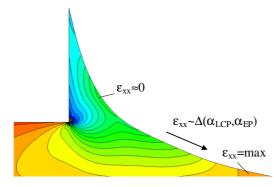

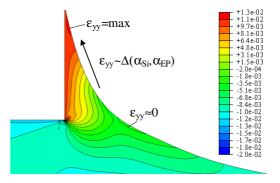

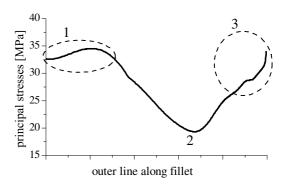

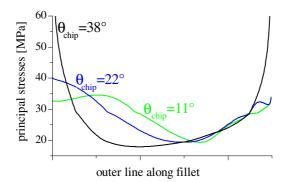

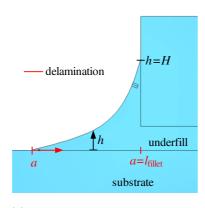

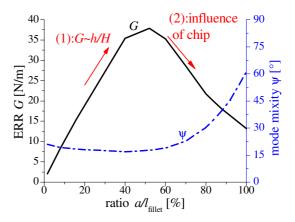

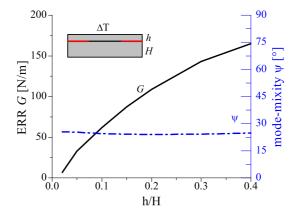

Fig. 3.1 reveals that an approximation of a flip chip interconnection by a tri-material layer does not correctly represent the stresses at x = L. Parameters and geometries which mostly act locally cannot be represented by these solutions.

-75 100

0 0.25L 0.5L 0.75L

flip chip

Fig. 3.1: Comparison of tensile stresses in the interface of a flip chip interconnection and a tri-material layer; (a) due to the fillet, the interface chip/underfill experiences a contraction for  $x \to L$ ; (b) for a trimaterial layer, due to the singularity at x = L, the tensile stresses are showing a peeling character; analytical solutions are available [9, 104, 120, 121, 128]; (c) it reveals that a tri-material layer approximation of a flip chip interconnections is not capable of displaying the stresses correctly

Therefore, the analytical representation cannot be used to study the reliability of a flip chip interconnection. The Finite Element Analysis can overcome that problem. Therefore, the interconnection is studied using Finite Element Analysis because it is capable of truly representing the geometry of the interconnection, as well as accounting for complex material behavior as visco-elasticity and plasticity.

In order to study the reliability of the flip chip interconnection, it is essential to know the mechanisms which lead to failure. This approach is generally known as the physics-of-failure approach and has been used for many years now. Physics of failure analysis is a term for identifying and understanding the physical processes and mechanisms of failure. It led to

improvements concerning the reliability of systems, even as the complexity of the systems increased. Due to more powerful computers, numerical simulations of the failure mechanisms which are mainly based on physical and chemical principles are used more and more. The feasibility of computer-based physics-of-failure analysis grew even more due to the availability of complex material models. Using computer-based physics-of-failure, it is even possible to combine different failure mechanisms in the reliability study [115].

The flip chip technology is a widely-studied application in which the physics-of-failure approach is applied. Fig. 3.2 gives an overview of the reported failure locations and mechanisms. The failure mechanism are mainly detected for solder bumped flip chip interconnections. The reported mechanisms are now described and their applicability to stud bump bonding flip chip interconnections discussed.

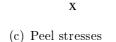

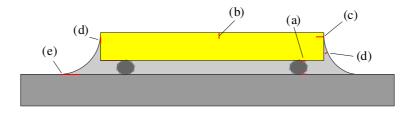

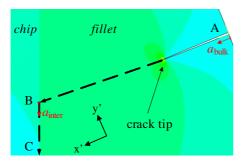

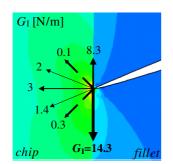

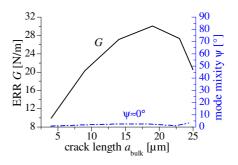

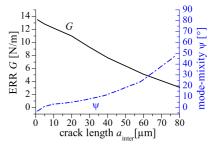

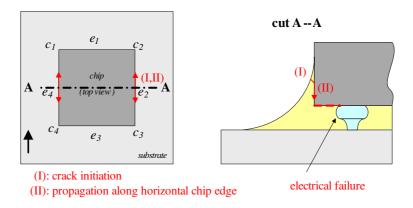

Fig. 3.2: Reported location of failure of solder bumped flip chip interconnections: (a) solder fatigue followed by delamination of passivation and underfill or visversa; (b) horizontal chip cracking [116]; (c) vertical chip cracking [30, 58, 59]; (d) bulk and interfacial cracking in the upper part of the fillet [6, 23, 63, 64]; (e) interfacial cracking between underfill and substrate [5, 27, 46, 64, 70, 71, 73, 108]

The lifetime of solder bumped flip chip interconnections is limited by the solder fatigue of the bumps when exposed to thermal cycling storage. Cyclical plastic deformation change the structure, weaken the solder and can lead to fatigue. A frequently relation to estimate the number of cycles until fatigue fracture occurs is based on the Coffin-Manson relation

$$N_{\rm f} = C \, \varepsilon_{\rm creep}^{-n}, \tag{3.3}$$

with the creep strain per cycle  $\varepsilon_{\text{creep}}$  [45, 77, 114, 125]. *C* and *n* are material constants. An important technology to dramatically increase the fatigue lifetime is to underfill the chip. The filled epoxy encapsulant matches the CTE of the bumps, minimizes the stresses on the solder joints and increases the fatigue life [82]. It could be shown that significant improvements in fatigue life can be achieved [21]. Depending on the size of the flip chip and bump, the use of underfills yields an increase of lifetime by 8 up to 80 times compared to flip chip interconnections without underfill. However, restraining the movement of the chip relative to the substrate can produce a significant shear stress as well as tensile stress of the underfill layer giving rise to a new failure mode: underfill delamination and rupture. Especially in presence of flux contamination originating from the assembly process, delamination between the chip passivation and underfill can occur and again reduce the lifetime [25, 45, 83, 84, 85,

125]. The delamination leads to much higher creep strain  $\varepsilon_{\text{creep}}$  in the bump and therefore to a shorter lifetime, even with underfill [32]. To summarize, creep strain in the bump made of solder leads to failure in the bump region of solder bumped flip chip interconnections. Using underfill, the creep strain can be significantly reduced. Whereas contamination from the flip chip process may lead to delamination of the bump/underfill respectively underfill/chip and again to higher creep strain in the bump.

In the present work, the gold stud bump technology is used to form the bumps. Therefore, no plastic creep strain is expected to occur in the bump. Since underfill material is used, the stresses and strains in the bump can be decreased compared to flip chip assemblies without underfill [21, 83, 84]. Nevertheless, the stress and strain level within the gold bump depends also on the chosen underfill or NCA. The SBB process does not require the use of flux, therefore, no contamination around the bumps is expected [66]. This supports the assumption that bump failure is not a potential failure mode for SBB flip chip interconnections. Nevertheless, scanning acoustic microscopy (SAM) and the measurement of the electrical resistance are performed during and after reliability testing to experimentally verify the assumption of no risk of bump failure.

Another reported failure mechanism of flip chip interconnections is bulk cracking of the silicon die. For integrated circuits dies, defects are caused by etching, sawing, device processing and handling. Hereby, two different kinds of cracking are reported: in Fig. 3.2b vertical die cracking on the top surface of the chip due to scratches [116]; and in Fig. 3.2c cracking on the vertical chip edge caused by flaws produced by dicing process [30, 58, 59].

For brittle materials, the maximum tensile stress is not a unique material property, because it is dependent on the specimen preparation. A more definite criterion is available in fracture mechanics, where the critical stress  $\sigma_c$  is given as a function of the initial defect [116]. For surface flaws with a size of 2*a*, the critical tensile stress is a function of the critical stress intensity factor  $K_{\rm Ic}$

$$\sigma_{\rm c} = m \frac{K_{\rm Ic}}{\sqrt{\pi a}} \tag{3.4}$$

where *m* represents a form factor of the defect which equals m = 1.2 for a semielliptical shape [59, 116]. The critical stress intensity factor of silicon lies between 0.82 and  $1.1 \text{ MPa}\sqrt{m}$  [15, 58, 59, 101, 116].

Vertical chip cracking can be avoided by polishing the flip chip surface. Since the backside of the chips in the present work are polished, and the chip bending is expected to be low <sup>1</sup>, vertical die cracking is not a concern but is experimentally monitored. Defect on the vertical edge of the die is mainly caused by the sawing process. In some studies, the die cracking

$<sup>^{1}</sup>$ The chip warpage and therefore the vertical chip cracking is strongly influenced by the CTE-mismatch and the ratio of the inertia of bending of the substrate and chip

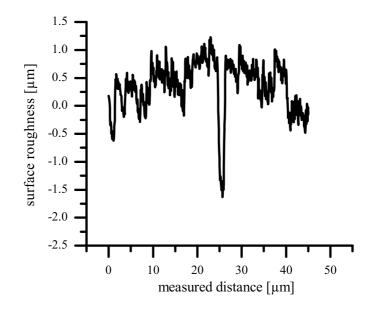

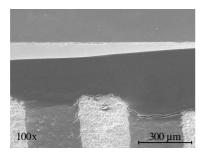

is investigated due to possible catastrophical failure already at cool down after underfill process [59]. Other publications concentrate on die cracking due to thermal cycling [58]. For the present work, the flaw size of the flip chips after dicing process are in the range of 1 to 2  $\mu$ m, Fig. 3.3.

Fig. 3.3: Surface roughness of used flip chip along the sawing edge measured by a profilometer; the maximum flaw size is around  $2\mu m$

Using Eq. (3.4), the critical stress equates to 526 MPa. The stress along the vertical chip edge of the flip chip for the studied assemblies lies around 30MPa for cooling down from 150 °C to -40 °C. Therefore, die cracking is not taken into account as failure criteria for the studied SBB flip chip interconnections.

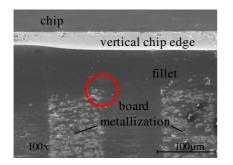

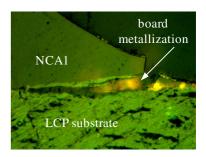

The underfill fillet plays a key role in horizontal chip/underfill delamination. This is due the fact that the fillet converts tensile stresses at the chip edge to compressive stress [6]. Nevertheless, as seen in Fig. 3.1, maximum stresses are present in the fillet. The stresses in the fillet can lead to crack initiation at different locations of the fillet [6, 23, 63, 64]. In [6], the influence of crack initiation and propagation of solder bump flip chip is studied. The focus lies on the experimental observation of fillet cracking due to thermal cycling and moisture. The fillet cracks start in the chip corners and lead to delamination between vertical chip edge and underfill. Consequently, the delamination reaches the lower chip corner and is followed by chip passivation/underfill interfacial cracking. [64, 70] studies additional crack initiation at the chip edges. The fillet is analyzed applying a two dimensional fracture mechanics approach. Despite this, crack initiation starts in the bulk material; additional, [64, 70] models a delamination between the vertical chip edge and the underfill.

Additional to fillet cracking, delamination between the substrate and the underfill at the

lower part of the fillet is reported [5, 27, 46, 64, 70, 71, 73, 108]. The delamination initiation is due to singular stresses in that region. This kind of failure can lead to bump failure once the delamination has reached the bump [70].

It can be assumed that fillet cracking - at vertical chip edge or between substrate and underfill - is independent of the bumping technology used. Therefore, it is considered as a possible failure mechanism for SBB flip chip interconnections.

Cracking in bulk material is caused by fatigue of the material due to cyclic loading, e.g. thermal cycling. Fatigue is described by the domain of micro mechanics or damage mechanics [117, 123]. Once a micro crack extended to a macro crack, the method of fracture mechanics can be applied. Since damage concepts are not well established respectively not very practical to apply on whole structures, the numerical modeling for a more complicated structure like a flip chip interconnection is not well established. Damage models are available for test specimens and RVEs (representative volume element) [13, 29]. However, no damage models are commercially available for interfaces. The concept of fracture mechanics is well studied for bulk and interfacial cracks. Due to the fracture mechanics approach of the crack tip field, the critical values of test specimens can be compared with more complicated structures. Widely-used test specimen for obtained critical bulk properties are the CT-test (Mode-I) and CTS-probe (mixture of Mode-I,-II). Investigations in using smaller test specimens are available. Therefore, the fracture mechanics approach is used to study the SBB flip chip interconnection.

Crack propagation can be distinguished in subcritical and critical crack propagation. Fig. 3.4 shows the crack propagation per cycle as function of the stress intensity factor.

The stress intensity factor K is a quantity used in fracture mechanics and related to the stress at the crack. Cyclic loading is assumed as well as pure tensile loading. The crack propagation depends on the existing stress intensity factor. In region I, the applied load is below a threshold value  $K_{\rm th.}$ , where no crack propagation is detected. Increasing the load, the crack propagation speed is linear proportional to the applied load. Increasing the load further, the crack propagation is instable followed by a complete failure. This value of the stress intensity factor is defined as the fracture toughness  $K_c$  of the material. For most engineering problems, crack propagation occurs in region II. This also applies for the studied flip chip interconnections, where thermal cycling leads to failure after a certain number of cycles.

Characterization of bulk material in region II is time-consuming and involves extensive testing. Moreover, only few publications exist in which the constant crack propagation due to thermal loading is studied. The focus of the present work lies in developing a method, which allows a quick design of and material choice for SBB flip chip interconnections. Therefore,

Fig. 3.4: The crack growth rate  $\log(da/dN)$  depends on the applied external load; the higher the load, the faster the crack propagation; the different crack growth regions depend on the applied stress intensity factor  $\Delta K$ ; in region I, no crack propagation can detected due to the fact that the external load is too small; where as at region II and III crack propagation occurs; in region II, crack growth occurs, the crack propagation rate is linear dependent on the external load  $\Delta K$ ; supercritical crack characterizes region III, the crack propagates with a high velocity

the underfills and NCAs used are characterized by their mechanical properties, as well as by their fracture toughness  $K_c$ . For cracking of substrate/underfill interface, no test is available which is fast and has small consumption of material. Therefore, a method has to be developed which includes these requirements.

## Chapter 4

# Theory of Bulk and Interfacial Fracture Mechanics

#### 4.1 Linear Elastic Fracture Mechanics (LEFM)

The fracture mechanics approach is used to describe the proposed failure mechanism - bulk cracking in the fillet as well as interfacial cracking between the substrate and the underfill.

Cyclic loading causes fatigue cracking in bulk material. Fatigue is described by methods like micro or damage mechanics [117, 123]. Fatigue damage concepts are widely studied. The most studies are performed on cyclic fatigue of metals [10, 11, 49, 57], while only few studies are focused on damage of polymers. The mechanisms are strongly influenced by the matrix and filler particles [13, 117, 123]. These damage concepts have not yet reached a level where they are verified. Moreover these concepts are time- and cost-effective. Another reason why damage concepts are beyond the focus of the present work lies in the lack of damage concepts for interfaces.

The fracture mechanics approach is formulated for bulk and interfacial cracks. Due to the nature of the approach using a crack tip field method, the critical values of test specimens can be compared with more complex structures. Widely-used test specimens for critical bulk properties are the CT-test (Mode-I) and CTS-probe (mixture of Mode-I,II). For interfacial cracking, several different types of test specimens are available. Therefore, the fracture mechanics approach is used to study the SBB flip chip interconnection.

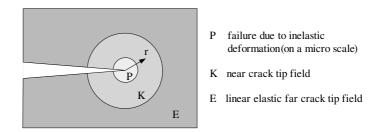

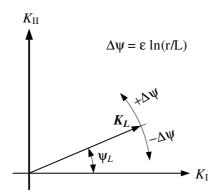

For the description of a crack, it is assumed that the zone, where microscopic affects are the dominating regime, is limited to a certain area P, which is defined in Fig. 4.1. Around that area, the behavior of the cracked body can be described by the linear elastic field. This field is divided into the near field K and far field E. In the near field, the singular stress

Fig. 4.1: Process zone of linear elastic fracture mechanics (LEFM); the plastic zone P describes the area where microcracking takes place which are mostly inelastic; the cracking occurs in the matrix or for filled materials between the filler particles and the surrounding matrix material; around that lies the near crack tip field K in which the stress intensity factor concept is valid: it is assumed that the stresses are a linear function of the stress intensity factor K, Eq.(4.6); around the K-field, the linear dependence of the stresses and stress intensity factor are no longer valid anymore).

field dominates and higher order terms can be neglected. The singularity leads to an infinite increase of the stresses for  $r \to 0$ . The type of singularity at the crack tip depends on the boundary conditions at the crack flanks. For linear-elastic materials, the singularity is of the type  $r^{-1/2}$ , whereas for perfect linear-plastic materials, the singularity shows a  $r^{-1}$  shape [24]. Moreover, the singularity of an interfacial crack is even more complex. The singularity shows an oscillating behavior very close to the crack tip.

The size of the different zones is strongly dependent on the plastic deformation of the body before new crack surface is built. Crack propagation in brittle material is rarely accompanied by plastic deformation. Epoxy resins show for temperatures below glass transition a brittle behavior [48, 122]. Therefore, the theory of linear-elastic fracture mechanics (LEFM) is sufficient to describe cracks within epoxy based polymers.

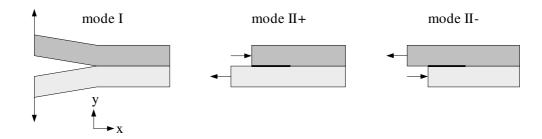

Cracks in two-dimensional load cases can be divided into different kinds of crack modes depending on the stress distribution  $\sigma_{yy}, \sigma_{xy}$ . Mode-I associates to a symmetric opening referring to the *x*-axis, Fig. 4.2. The antisymmetric displacement of the crack flanks in xdirection symbolizes the shearing mode (Mode-II).

Different concepts are available for LEFM and described in detail in [24]. In the presented work, the concept of the energy release rate (ERR) is used to describe the load on an existing crack. This method is capable of quantifying cracks in homogeneous materials, as well as cracks lying in the interface of a material combination [102]. Moreover, the method has the advantage that a regular Finite Element mesh is sufficient for numerical calculation of ERR [37, 38, 94]. Therefore, the method stands out in comparison to concepts which require a mesh with collapsed elements. These kinds of elements are required for obtaining accurate results in case of K-concept and J-integral [38, 102].

For LEFM, the energy release rate is related to the K-concept. It describes the singular stress field around a crack. The understanding of the concept is an essential requirement for

Fig. 4.2: Depending on the external load and geometry, cracks can be divided in different modes; Mode-I is opening mode ( $\Delta y > 0$ ) where no sliding of the flanks is present ; Mode-II represents the sliding of the flanks along the x-axis; hereby, two different cases can be distinguished: Mode-II+: shearing mode ( $\Delta x > 0$ ) and Mode-II-: shearing mode with ( $\Delta x < 0$ ); in the most cases, both modes occur simultaneously;

the application of ERR to interfacial LEFM. Specifically, the definition of the singularity of an interfacial crack is a prerequisite.

#### 4.2 Stress Field at Crack Tip

#### 4.2.1 Bulk Crack

The stress and displacement field in an elastic, homogeneous body can be described by using complex stress functions [24]. For plane stress and strain conditions, the stress field is completely described by two complex functions  $\Psi(z), \Phi(z)$  with the complex variable  $z = r^{i\phi}$ , with its respective conjugated variable  $\bar{z} = r^{-i\phi}$ . This approach originates from Muskhelishvili [60]. The solution for the stress and displacement field in terms of the complex functions are the formulas by Kolosov

$$\sigma_{\rm x} + \sigma_{\rm y} = 2 \left[ \Phi'(z) + \overline{\Phi'}(z) \right] \tag{4.1}$$

$$\sigma_{\mathbf{y}} - \sigma_{\mathbf{x}} + 2i\tau_{xy} = 2\left[\overline{z}\Phi''(z) + \Psi'(z)\right] \tag{4.2}$$

$$2G(u+iv) = \kappa \Phi(z) - z\overline{\Phi'}(z) - \overline{\Psi}(z)$$

(4.3)

with  $\kappa = 3 - 4\nu$  for plane strain.

To describe the crack tip field, it is assumed that the complex functions are of the form of

$$\Phi(z) = A z^{\lambda} \quad \Psi(z) = B z^{\lambda} \tag{4.4}$$

where  $\lambda$  is restricted to be real and positive. A and B are constants which are determined from boundary conditions. Using Eq.(4.4), a linear system of equations is obtained. Assuming that the crack flanks are traction free – zero tensile and shear stress at the crack faces ( $\psi = \pi$ ) – the equation of the eigenvalues of the linear system of equations is obtained. For  $r \to 0$  (K region in Fig. 4.1), the eigenvalue  $\lambda = 1/2$  dominates and higher order eigenvalues can be neglected

$$\lambda = 1/2 \quad \text{for} \quad r \to 0. \tag{4.5}$$

It is convenient to split the solution into symmetric and asymmetric parts with respect to the *x*-axis. The symmetric stress and displacement fields are defined as the crack Mode-I

$$\sigma_{ij} = \left[\frac{1}{\sqrt{2\pi r}}\right] K_{\rm I} f_{1,ij}(\varphi) \tag{4.6}$$

$$u, v = \left[\sqrt{\frac{r}{2\pi}}\right] \frac{K_{\rm I}}{\sqrt{2G}} f_{u,v}(\varphi) \tag{4.7}$$

with the functions f, which depend only on the angle  $\varphi$  [24, 48, 123]. Crack Mode-II is represented by the asymmetric part of the solution. The expressions for Mode-II stress and displacement field can be found in [24, 48].  $K_{\rm I}$  and  $K_{\rm II}$  are stress intensity factors and are a quantity to describe strength of the crack tip field.

The ratio of shear to tensile stress in a crack tip is defined as mode-mix, often also referred to as mode-mixity. For a crack in a homogeneous body,  $K_{\rm I}$  accounts independently from the distance r to the crack tip for the tensile stress. So does  $K_{\rm II}$  for the shear stress. Therefore, the mode-mixity can be expressed as

$$\psi = \arctan\left(\frac{\tau_{xy}(r,0)}{\sigma_{yy}(r,0)}\right) = \arctan\left(\frac{K_{\text{II}}}{K_{\text{I}}}\right) \neq f(r)$$

(4.8)

with  $\psi$  as the phase angle.

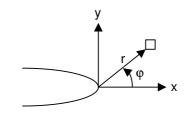

Recalling Eq.(4.6), the stress field shows a  $r^{-1/2}$  singularity. This is characteristic for a crack in a linear elastic material with traction-free crack flanks. The displacement field shows a  $r^{1/2}$  singularity, Eq.(4.7). Therefore, the displacement of the crack surfaces  $\varphi = \pm \pi$  has a parabolic shape, Fig. 4.3,

$$\Delta v = v^{+} - v^{-} = \frac{K_{\rm I}}{\sqrt{2G}} \left(\kappa + 1\right) \left[\sqrt{\frac{r}{2\pi}}\right].$$

(4.9)

Fig. 4.3: Used coordinate system of crack tip field; due to the eigenvalue  $\lambda = 1/2$ , the displacement field at the crack tip shows a parabolic shape, Eq. (4.9)

The type of the singularity changes depending on the geometry of the crack tip (i.e. a v-notch), linear-elastic plastic crack tips, as well as other boundary conditions other than traction-free crack flanks (e.g. contact of the crack flanks).

$K_i$  is obtained by calculating the stresses or displacements for  $r \to 0$  from Eq. (4.6). For frequently-used geometries and loads (i.e. compact tension (CT) test), analytical solutions of the stress fields are listed in [24, 48]. For a CT specimen, K as function of the force P, the geometry parameters B,W and the crack length a are given by

$$K = \frac{P}{B\sqrt{W}}f(t) \quad \text{with} \quad f = \frac{2+t}{(1-t)^{3/2}} \sum_{i=0}^{4} C_i t_i$$

(4.10)

with t = a/W and the constants  $C_i$ . For more complex geometries and loads, the stress field has to be solved numerically. Finite Element packages mostly utilize the displacements at the crack flanks to calculate the stress intensity factors, compare Eq.(4.9) [4].

#### 4.2.2 Interfacial Crack

The stress field of an interfacial crack can also be described by the equations of Kolosov Eq.(4.3). Because the crack lies between materials with different elastic properties, Fig. 4.4, the complex functions Eq.(4.4) are applied to each layer separately

$$\Phi_1(z) = A_1 z^{\lambda} \quad \Psi_1(z) = B_1 z^{\lambda} \quad \Phi_2(z) = A_2 z^{\lambda} \quad \Psi_2(z) = B_2 z^{\lambda}$$

(4.11)

where the subscript 1 and 2 denote the layer 1 and 2, respectively [14, 24].

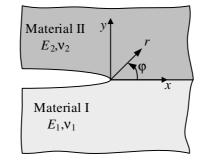

Fig. 4.4: A crack between two dissimilar materials

Applying the boundary conditions, (1) stress free crack surfaces at  $\varphi = \pm \pi$  and (2) transition conditions between the two materials at  $\varphi = 0$ , lead to a system of linear equations<sup>1</sup>. The

<sup>&</sup>lt;sup>1</sup> For different boundary conditions other than traction-free crack flanks, the eigenvalue and therefore the kind of singularity changes. The eigenvalue of flanks which are in contact leads to a solely real eigenvalue which is dependent on the coefficient of friction [14, 102].

solution of the system (higher order terms are neglected) is an eigenvalue which is similar to the one for the homogeneous case Eq.(4.5)

$$\lambda = 1/2 + i\varepsilon. \tag{4.12}$$

$\varepsilon$  is the bimaterial constant and describes the influence of the ratio of the two materials. In plane strain condition,  $\varepsilon$  is obtained by

$$\varepsilon = \frac{1}{2\pi} \ln\left(\frac{\mu_2 \kappa_1 + \mu_1}{\mu_1 \kappa_2 + \mu_2}\right) = \frac{1}{2\pi} \ln\left(\frac{1+\beta}{1-\beta}\right)$$

(4.13)

with  $\kappa_i = 3 - 4\nu_i$  and  $\mu_i$  as the bulk shear modulus for materials 1 and 2.

A more frequently used interpretation of the mismatch of the elastic properties are the Dundurs' parameters  $\alpha$  and  $\beta$  [29]. They separate the influences of the plane tensile and shear modulus across the interface.  $\alpha$  gives a relation of the Young's modulus of the both materials. Whereas  $\beta$  reveals the mismatch due to the difference of the in-plane bulk modulus. For plane strain with  $E^* = \frac{E}{1-\nu^2}$ , they are given as

$$\alpha = \frac{E_1^* - E_2^*}{E_1^* + E_2^*} \qquad \beta = \frac{1}{2} \frac{\mu_1 \left(1 - 2\nu_2\right) - \mu_2 \left(1 - 2\nu_1\right)}{\mu_1 \left(1 - \nu_2\right) + \mu_2 \left(1 - \nu_1\right)}.$$

(4.14)

For the homogeneous case  $E_1 = E_2$  and  $\nu_1 = \nu_2$  where the material mismatch vanishes, the Dundurs' parameters  $\alpha, \beta$ , as well as the bimaterial constant  $\varepsilon$ , are zero.

The solution of the stress field  $\sigma(r, \varphi)$  is obtained applying the eigenvalue to Eq.(4.11). The solution can be found in [14, 29]. The stress field in the ligament between the two materials,  $\varphi = 0$ , is given by

$$\sigma_{yy}(r,\varphi=0) + i\sigma_{xy}(r,\varphi=0) = \left[\frac{r^{i\varepsilon}}{\sqrt{2\pi r}}\right] K.$$

(4.15)

K represents the complex interface stress intensity factor

$$K = K_1 + iK_2 = |K| r^{i\varepsilon}.$$

(4.16)

Because of the asymmetry of the material properties,  $K_1$  and  $K_2$  do not represent the crack opening mode (Mode-I) and shearing mode (Mode-II), respectively [24].

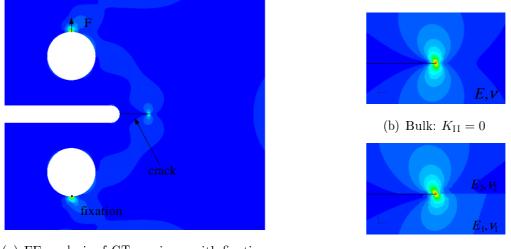

The asymmetry of the stress field due to the difference in material properties can be seen in Fig. 4.5. A compact tension (CT) specimen is symmetrically loaded by a force F, Fig. 4.5a. The symmetric test configuration for a crack in a bulk material  $(E, \nu)$  leads to a symmetric stress field, shown in Fig. 4.5b. Therefore, Mode-II equals  $K_{\rm II} = 0$ . For a bimaterial specimen with a pre-crack lying between two different materials  $((E_1, \nu_1), (E_2, \nu_2))$ , the stress field is asymmetric, Fig. 4.5c, which leads to  $K_{\rm II} \neq 0$ .

(a) FE analysis of CT specimen with fixation and symmetric loading by force F

Fig. 4.5: Comparison stress field  $(\sigma_{yy})$  for a bulk and interfacial crack at symmetric loading; (b) symmetric stress field hence homogeneous material; (c) asymmetric stress field hence bimaterial crack

In order to calculate the stress intensity factors which represent the real Mode-I and Mode-II of the interface, *Hutchinson* suggests using the formula  $\psi$  [29]

$$\psi = \arctan\left[\frac{\Delta u}{c\Delta v}\right] + \arctan(2\varepsilon) + \varepsilon \ln(r/L)$$

(4.17)

with

$$c = \sqrt{\frac{2(\mu_1 + \mu_2)}{\mu_1 \frac{1 - 2\nu_2}{1 - \nu_2} + \mu_2 \frac{1 - 2\nu_1}{1 - \nu_1}}},$$

(4.18)

where L as a characteristic length is introduced.

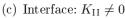

The first term in Eq.(4.17) gives the ratio of sliding and opening of the crack flanks, modified by the factor c which counts for the difference in elastic properties of both layers. In the case of a crack in a homogenous material, c becomes zero - so do the other two terms - and the phase angle is solely calculated by the relative displacements of the flanks. The second and third term are due to the difference of the elastic properties. The influence of the characteristic length can also be understood as a rotation around the angle consisting of the first and second term in Eq.(4.17). The rotation depends on the selection of the characteristic length L as well as on the bimaterial constant  $\varepsilon$ . This is shown in Fig. 4.6.

Fig. 4.6:  $K_{\rm I}, K_{\rm II}$ -space; complex stress intensity factor  $K_L$  at r = L; rotation of K by  $\Delta \psi = \varepsilon \ln(r/L)$ caused by oscillating singularity;  $|\Delta \psi| \le 4^\circ$  for epoxy/LCP interface ( $\varepsilon_{\rm epoxy/LCP} \approx 0.03$ )

The tension and shear stresses in the ligament are obtained at r = L. In the presented work, the element size of the Finite Element mesh L is used as the characteristic length. A element size of about 0.5  $\mu$ m is chosen. This leads to a simplification of Eq.(4.17)

$$\psi = \arctan\left[\frac{\Delta u}{c\Delta v}\right] + \arctan(2\varepsilon).$$

(4.19)

The influence of the third term can be estimated when  $r = \Delta r + L$  is chosen, with  $\Delta r = 0.1L$ . The rotation contributed by the third is around  $0.16^{\circ}$ , which can therefore be neglected.

With  $\varepsilon_{\rm epoxy/LCP} \approx 0.03$ , the rotation due to the oscillating singularity is  $|\Delta \psi_{\rm max}| = 4^{\circ}$ .

### 4.3 Energy Release Rate

#### 4.3.1 Concept

The energy release rate (ERR) is based on the theorem of energy conservation. Once a crack propagates from a to  $a + \Delta a$ , the internal energy of the body degrades. This energy can be related to the energy needed to produce new crack surface. This leads to the definition of the energy release rate which simplifies for plane strain to

$$G = -\frac{\mathrm{d}\Pi}{\mathrm{d}a}.\tag{4.20}$$

G is of the unit [force/length]. A more figurative definition of the ERR is the contention by Irwin [31]. It is proposed that if the crack extends by a small amount  $\Delta a$ , the energy absorbed in the process is equal to the work required to close the crack to its original length. Applying this statement, the ERR can also be used to characterize the crack Mode-I, -II by

$$G_{\rm I} = \lim_{\Delta a \to 0} \int_{0}^{\Delta a} \sigma_{yy}(\Delta a - r, 0) \,\Delta v(\Delta a - r, \pm \pi) \,\mathrm{d}r \tag{4.21}$$

$$G_{\rm II} = \lim_{\Delta a \to 0} \int_0^{\Delta a} \tau_{xy} (\Delta a - r, 0) \,\Delta u (\Delta a - r, \pm \pi) \,\mathrm{d}r \tag{4.22}$$

with the stresses at the near crack tip  $\sigma_{yy}(r,\varphi)$ , and  $\tau_{xy}(r,\varphi)$ ,  $\Delta v(r,\varphi)$  the crack opening displacement and  $\Delta u(r,\varphi)$  the sliding of the crack flanks [38, 76, 94, 123]. Moreover, the components  $G_{\rm I}$  and  $G_{\rm II}$  are linearly added to the complete energy release rate<sup>2</sup>

$$G = G_{\rm I} + G_{\rm II}. \tag{4.23}$$

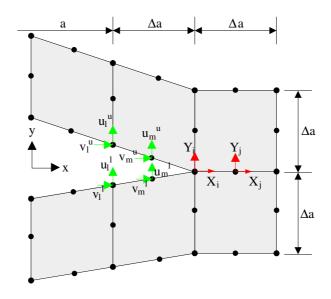

This interpretation of the ERR is utilized by the Virtual Crack Closure Technique (VCCT) which is used to numerically obtain G. VCCT was first introduced by *Rybicki* and *Kanninen* [94]. A detailed adaption to Finite Element formulation can be found in [38]. This implementation into FE analysis utilizes the displacements u, v and the forces X, Y at the nodes to calculate G. The forces represent the cohesion of the corresponding nodes against separation. Therefore, the Eqs.(4.21),(4.22) are translated for a plane strain to

$$G_{\rm I} = -\frac{1}{2\Delta a} \left[ Y_{\rm i} \left( u_{\rm l}^u - u_{\rm l}^{\rm l} \right) + Y_{\rm j} \left( u_{\rm m}^u - u_{\rm m}^{\rm l} \right) \right]$$

(4.24)

$$G_{\rm II} = -\frac{1}{2\Delta a} \left[ X_{\rm i} \left( v_{\rm l}^u - v_{\rm l}^{\rm l} \right) + X_{\rm j} \left( v_{\rm m}^u - v_{\rm m}^{\rm l} \right) \right]$$

(4.25)

where the notation for the displacements and forces are shown in Fig. 4.7.

A requirement for adapting VCCT to Finite Element analysis is the accessibility to the forces X, Y at the nodes i, j. For the used Finite Element package ABAQUS, these forces are not directly available. Therefore, the forces are obtained by a work-around, by adding connector elements in the crack tip [86].

For a crack in a homogeneous body, ERR can be expressed in terms of the stress intensity factors [24]. Because ERR describes the energy change caused by crack propagation in an elastic body, it refers to both crack modes

$$G = \frac{1}{E^*} \left( K_{\rm I}^2 + K_{\rm II}^2 \right) \tag{4.26}$$

with  $E^* = \frac{E}{1-\nu^2}$  for plane strain. Invoking Eqs.(4.21),(4.22), the stress intensity factors belonging to the single modes can be calculated by [94]

$$K_{\rm I} = \sqrt{E^* G_{\rm I}} \quad K_{\rm II} = \sqrt{E^* G_{\rm II}}.$$

(4.27)

<sup>&</sup>lt;sup>2</sup>Where the stress intensity factor K symbolizes a vectorized value, ERR is scalar and can be added as performed in Eq. (4.23)

Fig. 4.7: Virtual Crack Closure Technique (VCCT) for implementation of ERR into Finite Element analysis; using displacements and forces at nodes; adaption into FE package ABAQUS by using connector elements [86]

#### 4.3.2 ERR for Interfacial Fracture Mechanics

The ERR accounts for the energy set free during tensile as well as shear loading of a crack Eq.(4.27). This relation is also valid for an interfacial crack and modifies to

$$G = \frac{1}{\overline{E}\cosh^2(\pi\varepsilon)} \left(K_1^2 + K_2^2\right) = \frac{1}{\overline{E}\cosh^2(\pi\varepsilon)} |K|, \qquad (4.28)$$

because of the change of the elastic properties of the material combination, with  $\overline{E}$

$$\frac{1}{\overline{E}} = \frac{1}{2} \left( \frac{1}{E_1} + \frac{1}{E_2} \right).$$

(4.29)

The overall energy release rate for an interfacial crack, gathered from VCCT Eqs.(4.21),(4.22), is an adaption of Eq.(4.23)

$$G = G_1 + G_2. (4.30)$$

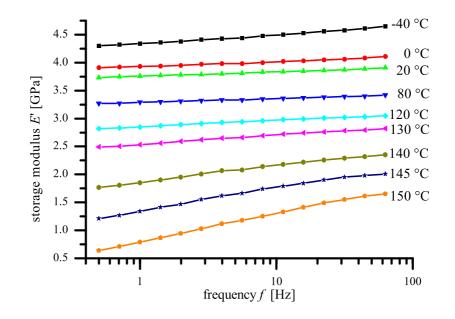

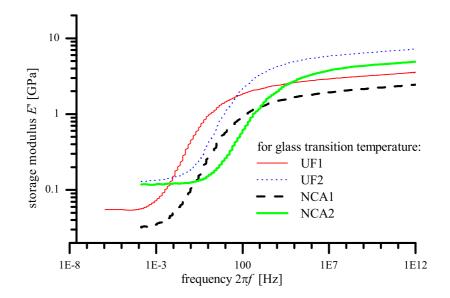

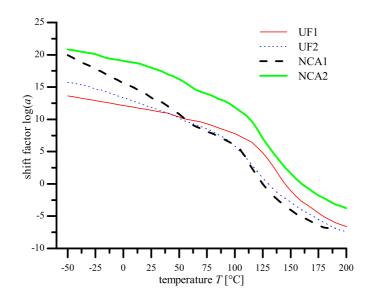

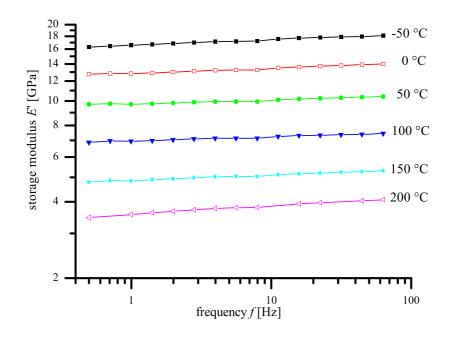

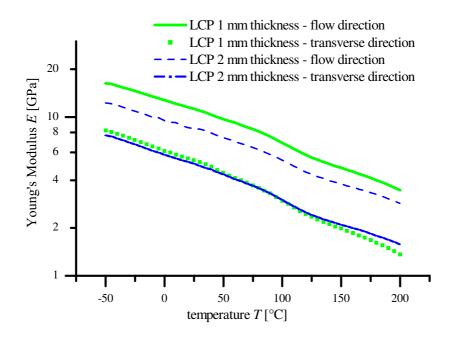

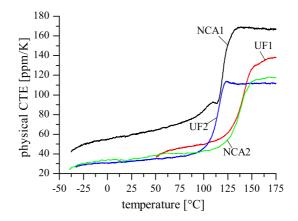

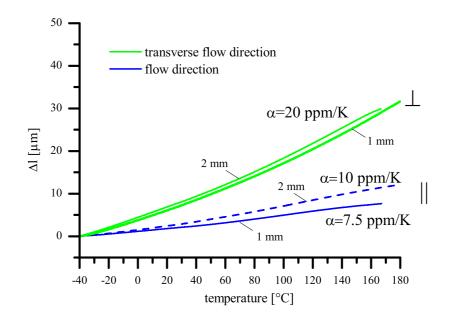

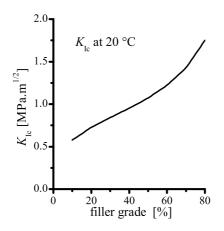

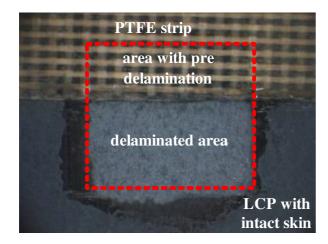

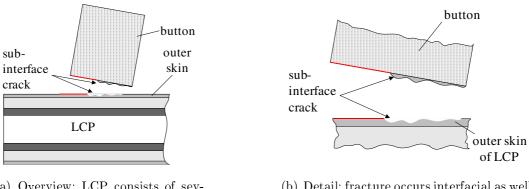

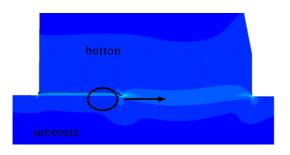

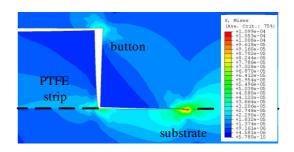

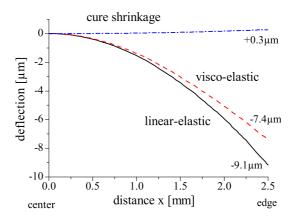

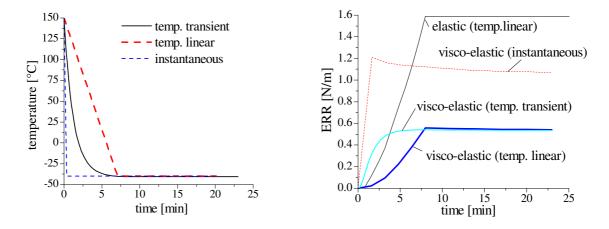

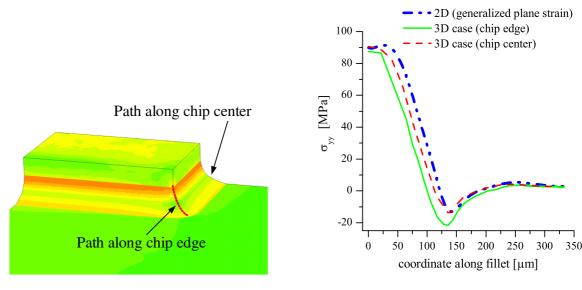

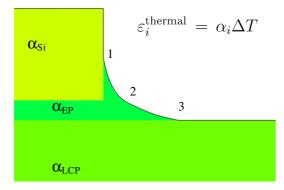

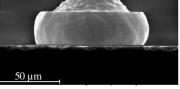

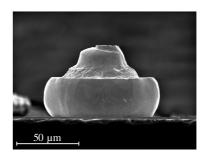

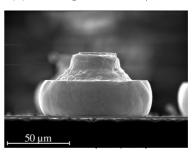

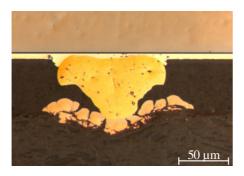

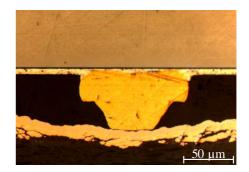

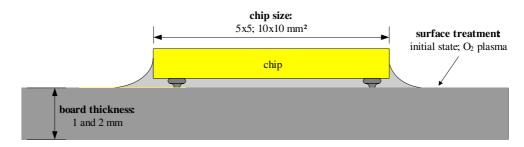

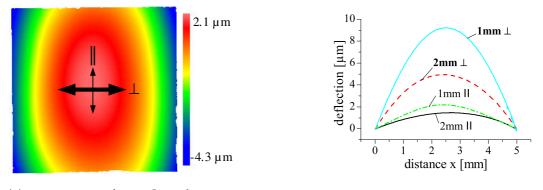

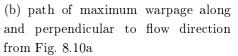

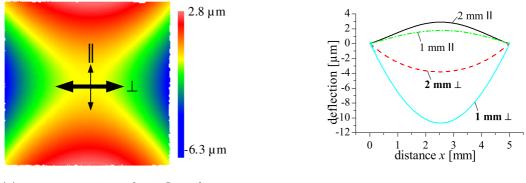

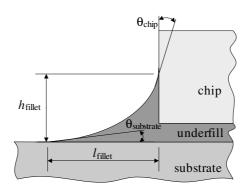

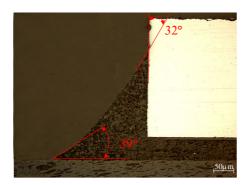

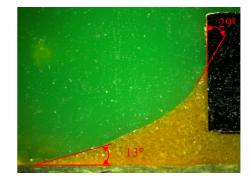

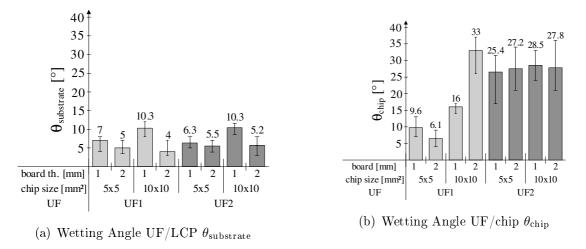

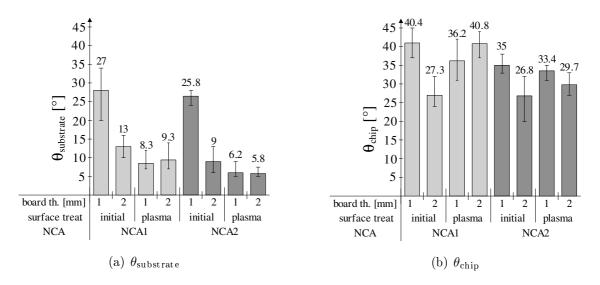

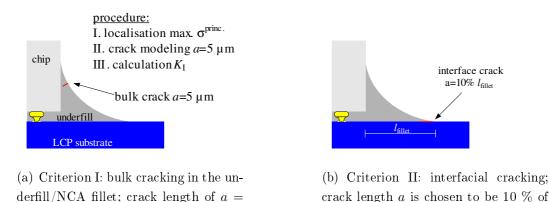

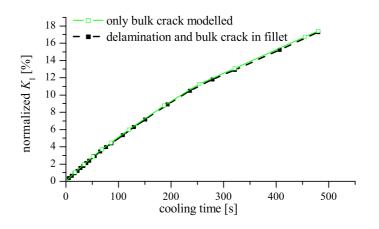

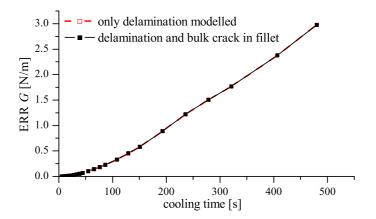

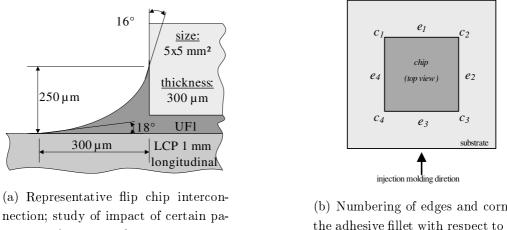

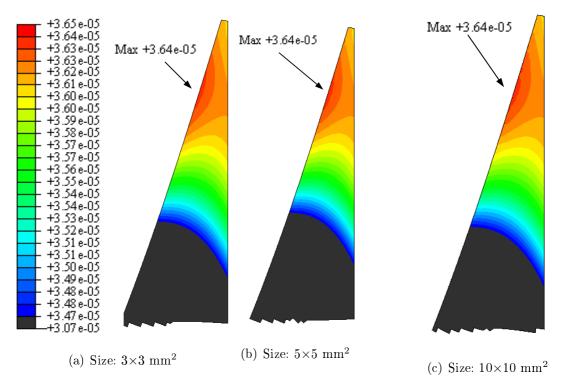

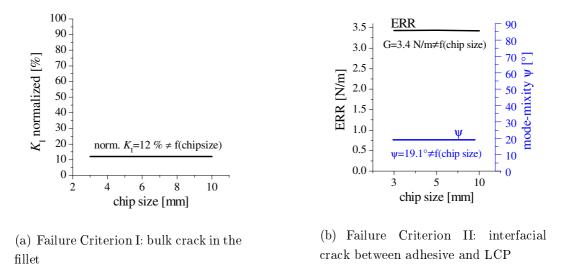

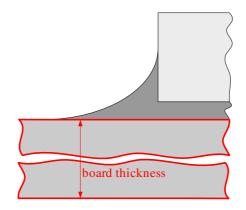

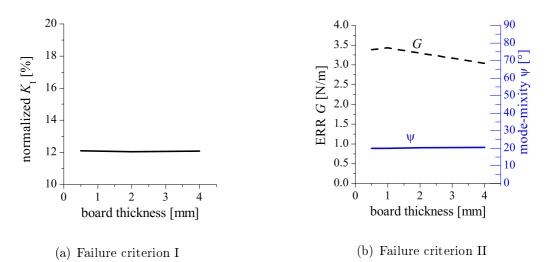

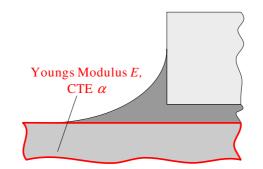

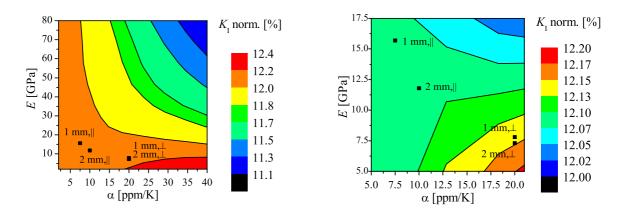

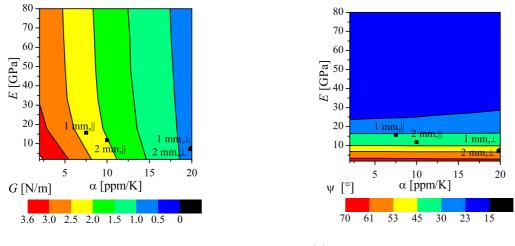

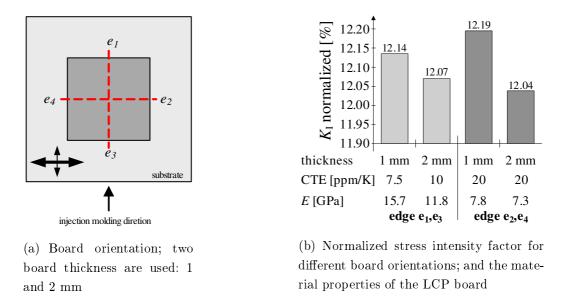

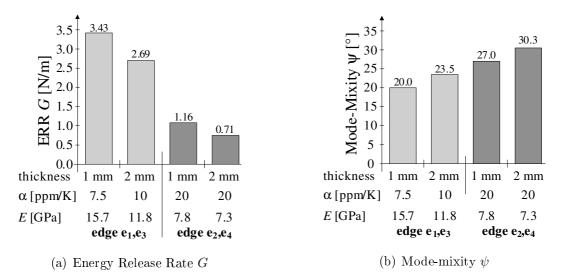

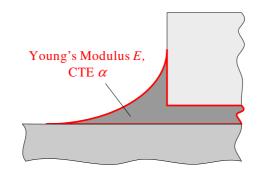

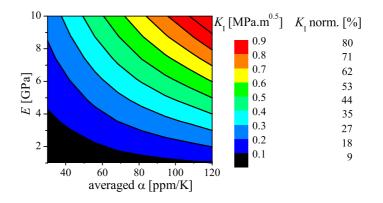

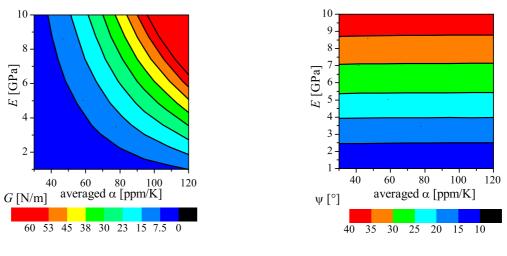

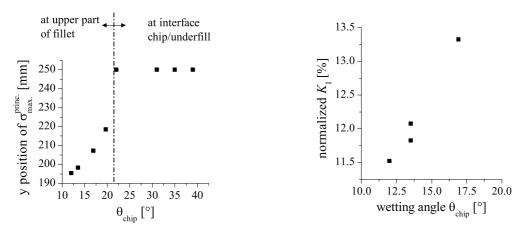

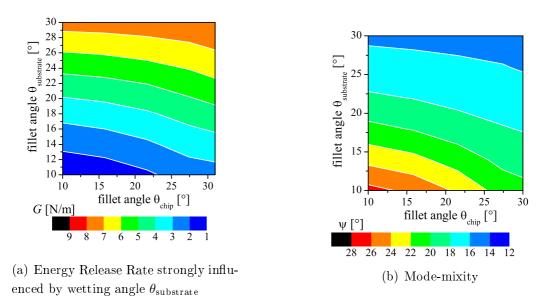

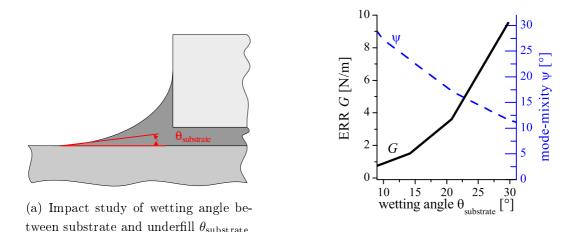

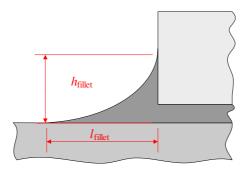

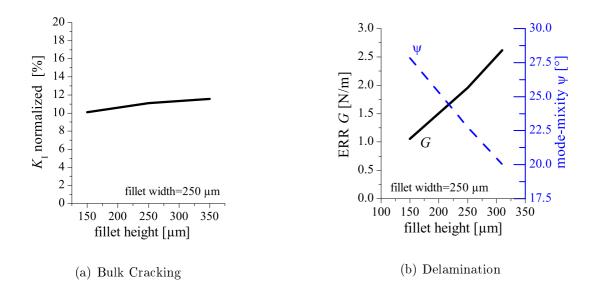

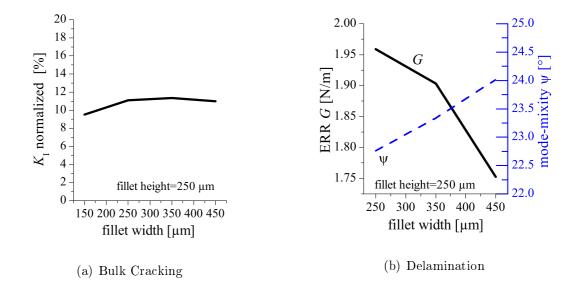

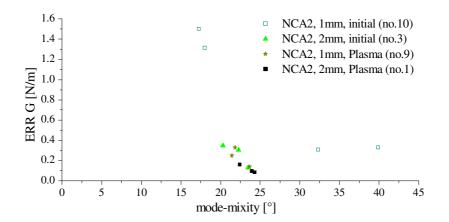

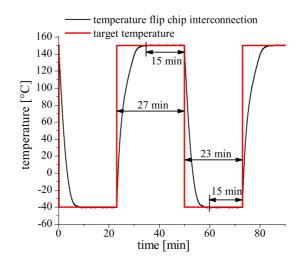

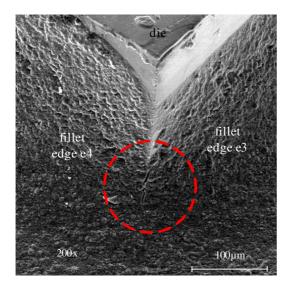

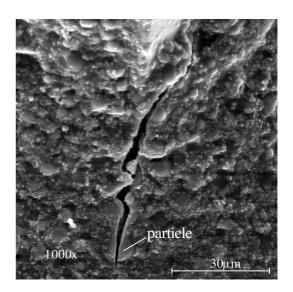

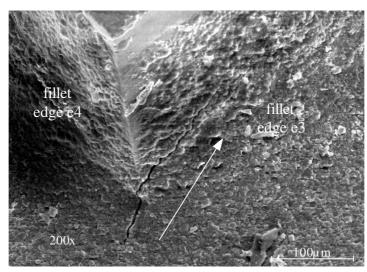

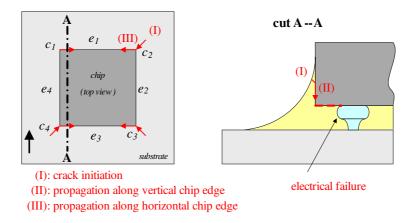

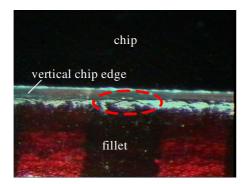

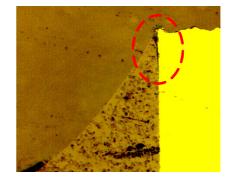

$G_1$  and  $G_2$  do not represent the Mode-I and -II of the interfacial crack. In order to perform mode separation, the mode-mixity angle  $\psi$  from Eq.(4.17) and the total ERR G are used.