# Wideband GaN Microwave Power Amplifiers with Class-G Supply Modulation

vorgelegt von

M.Sc.

Nikolai Wolff

geboren in Berlin

von der Fakultät IV – Elektrotechnik und Informatik

der Technischen Universität Berlin

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

Dr.-Ing.

genehmigte Dissertation

### Promotionsausschuss:

Vorsitzender: Prof. Dr.-Ing. habil. Dietmar Kissinger

Gutachter: Prof. Dr.-Ing. habil. Wolfgang Heinrich

Prof. Dr.-Ing. Dr.-Ing. habil. Robert Weigel

Prof. Dr. Christian Fager

Tag der wissenschaftlichen Aussprache: 21. August 2018

Berlin 2018

# Acknowledgment

This work was conducted at the Ferdinand-Braun-Institut, Leibniz-Institut für Höchstfrequenztechnik in the III-V Electronics department in the time between August 2014 and February 2018.

I would like to express my deepest gratitude to my supervisors Prof. Dr.-Ing. habil. Wolfgang Heinrich and Dr. Olof Bengtsson. You introduced me into the wonderful world of science and guided my work to ensure good scientific practice.

I also want to thank Sebastian Preis and Sophie Paul, my Ph.D. student colleagues in the RF power lab. You were always there for discussions and with inspiring ideas. Furthermore, I would like to thank my colleagues at the III-V Electronics department for the good working atmosphere and the many social activities outside work.

#### **Abstract**

The continuous and rapidly growing demand for mobile communication access led worldwide to a major increase in the number of base stations to provide the sufficient coverage and quality of service. As a consequence, mobile communication networks have become a significant contributor to the worldwide energy consumption. The necessity to save operational cost and the increased energy awareness fueled research on the efficiency optimization of base station transceivers. A close view at the transceiver shows that the RF power amplifiers in the transmitter are dominating the power consumption of today's base stations, with a share between 50% and 80%. In order to cope with the rapidly increasing access bandwidth, broadband operation with multicarrier modulation formats that provide high spectral efficiency is required. Thus, the RF power amplifier must operate energyefficient as well as highly linear over a wide dynamic range, due to the large peak-to-average power ratio of the modulated signals. Classical RF power amplifiers cannot fulfil these requirements. Several advanced topologies for efficiency improvement of RF power amplifiers have been developed. Modulating the amplifiers supply voltage according to the variation of the envelope signal is one of the most promising concepts. This topology is investigated in this thesis, with an architecture that switches the supply voltage of the power amplifier in discrete levels with a class-G supply modulator.

The thesis addresses comprehensively all aspects of class-G supply modulation. First, the behavior of linear RF power amplifiers and those with reduced conduction angle when operated with supply modulation is analyzed theoretically. Based on the results several prototype designs were realized, to validate the theory and to gain experience on the influence of the various parameters, such as the discrete supply voltage levels, the switching thresholds, and the interface between the RF PA and the class-G supply modulator. This comprised efforts both on improving the RF power amplifiers and developing several class-G supply modulators.

The measurement system for the dynamic characterization of class-G modulated RF amplifiers and the linearization with baseband digital predistortion plays a key role in this work. Accordingly, the system setup, the dynamic range, and the bandwidth requirements for the measurements with digital predistortion are addressed and different dynamic range enhancement techniques are evaluated and implemented. Class-G supply modulated RF power amplifiers based on gallium nitride technology exhibit a strong nonlinear behavior, therefore linearization is required. For this purpose, the linearization with digital predistortion

based on behavioral models is optimized for the class-G topology and a novel predistorter model is developed and analyzed.

Finally, the milestone class-G systems developed during this work are presented and discussed. This begins with the design and analysis of the first dynamically operated class-G supply-modulated RF power amplifier system that provides a modulation bandwidth up to 20 MHz. It covers the progress up to a PA module that provides an instantaneous modulation bandwidth of 120 MHz and achieves better performance than state-of-the art continuous supply modulation systems.

## Kurzfassung

kontinuierlich und rapide steigende Bedarf an mobilem Der Kommunikationsnetzen führte weltweit zu einem deutlichen Anstieg von installierten Mobilfunk-Basisstationen, um eine flächendeckende Versorgung mit der nötigen Qualität sicherzustellen. Dies hat dazu geführt, dass die mobilen Kommunikationsnetze signifikant zum weltweiten Energieverbrauch beitragen. Die Notwendigkeit zur Einsparung von Betriebskosten und das steigende Bewusstsein im Umgang mit dem Verbrauch von Energie hat dabei Forschungen zur Effizienzsteigerung dieser Systeme in den Mittelpunkt gerückt. Bei einer Analyse des Energieverbrauchs in einer heutigen Mobilfunk-Basisstation wird schnell ersichtlich, dass der HF-Leistungsverstärker dabei den bedeutendsten Anteil beiträgt und zwischen 50% und 80% der Energie verbraucht. Durch die rasch wachsenden Datenraten werden breitbandige Mehrträger-Modulationsformate mit hoher spektraler Effizienz benötigt. Der HF Leistungsverstärker muss dadurch über einen weiten Dynamikbereich sowohl sehr linear als auch effizient arbeiten, da die modulierten Signale ein hohes Verhältnis von Spitzen- zu Mittelwertleistung haben. Klassische HF Leistungsverstärker erfüllen diese Anforderungen nur ungenügend. Aus dieser Problematik heraus wurden verschiedene Verstärkertopologien mit verbesserter power back-off Effizienz entwickelt. Ein vielversprechendes Konzept in diesem Zusammenhang ist die Modulation der Versorgungsspannung des HF Leistungsverstärkers mit der Einhüllenden des modulierten Signals. Ein Sonderfall dieser Topologie mit diskreten Versorgungsspannungsstufen (Klasse-G Modulation der Versorgungsspannung) wird in dieser Arbeit untersucht.

Die Arbeit behandelt alle Aspekte eines Klasse-G-modulierten HF-Leistungsverstärkers. Zu Beginn werden die Eigenschaften von linearen Verstärkern und solchen mit reduziertem Stromleitwinkel für den Betrieb mit variabler Versorgungsspannung theoretisch untersucht. Auf Basis dieser Voruntersuchungen werden dann Prototypen realisiert. Mit Hilfe von Messungen wird so die Validität der Theorie überprüft und der Einfluss der vielzähligen Parameter, wie z.B. die Wahl der diskreten Versorgungsspannungen, die Schwellen für das Umschalten der Versorgungsspannung und die elektrische Verbindung zwischen Klasse-G Modulator und HF Verstärker untersucht. Parallel zur Weiterentwicklung der HF Leistungsverstärker werden Klasse-G-Versorgungsspannungsmodulatoren entwickelt und an die Anforderungen angepasst.

Ein weiterer wichtiger Teil dieser Arbeit befasst sich mit dem Aufbau eines Messplatzes für die dynamische Charakterisierung der Klasse-G-modulierten HF-Leistungsverstärker und

der Linearisierung mittels digitaler Vorverzerrung im Basisband. Des Weiteren werden der erforderliche Dynamikumfang für die Linearisierung mittels digitaler Vorverzerrung und verschiedene Konzepte zur Erhöhung des Dynamikumfangs mittels Signalverarbeitung untersucht und implementiert. Auf Galliumnitrid-Technologie basierende Klasse-Gmodulierte HF-Leistungsverstärker zeigen im Betrieb ein stark nichtlineares Verhalten. Die Kompensation der Nichtlinearitäten wird mittels einer digitalen Vorverzerrung, die auf Verhaltensmodellen beruht, implementiert und ein neues für Klasse-G-Betrieb optimiertes Modell eingeführt.

Abschließend werden die Meilensteine der in dieser Arbeit entwickelten Klasse-G Systeme zusammengefasst und vorgestellt. Dies beginnt mit dem ersten rudimentären der den dynamischen Klasse-G Betrieb mit Signalen bis Prototyp, Modulationsbandbreite ermöglicht, und endet bei einem System mit einer Modulationsbandbreite von 120 MHz, das den aktuellen Stand der Technik der kontinuierlich versorgungsspannungsmodulierten Systeme erreicht und hinsichtlich der Bandbreite deutlich übertrifft.

# Contents

| A | cknowled  | lgment                                                                    | l    |

|---|-----------|---------------------------------------------------------------------------|------|

| A | bstract   |                                                                           | II]  |

| K | urzfassun | ıg                                                                        | V    |

| C | ontents   |                                                                           | .VII |

| 1 | Introd    | luction                                                                   | 1    |

| 2 | Theo      | ry of Class-G Supply Modulation                                           | 5    |

|   | 2.1 S     | Supply modulation of linear and reduced conduction angle power amplifiers | 6    |

|   | 2.1.1     | Power back-off efficiency with continuously reduced supply voltage        | 7    |

|   | 2.1.2     | Power back-off efficiency for discretized supply voltage modulation       | 13   |

|   | 2.1.3     | Quasistatic GaN-HEMT model based simulations with knee I-V effects        | 15   |

|   | 2.2       | Class-G modulator switching speed requirements                            | 20   |

|   | 2.3 E     | Efficiency enhancement limits of class-G supply modulation                | 30   |

|   | 2.4 P     | Power amplifier linearity under class-G supply modulation                 | 35   |

|   | 2.4.1     | Baseband signal distortions caused by gain and phase variations           | 36   |

|   | 2.4.2     | Impact of class-G supply modulation on the transducer gain                | 36   |

|   | 2.4.3     | Quantification of nonlinear distortions in class-G supply modulated PAs   | 38   |

|   | 2.5       | Conclusions                                                               | 43   |

| 3 | RF Po     | ower Amplifiers for Supply Modulation                                     | 45   |

|   | 3.1       | The RF power GaN-HEMT                                                     | 45   |

|   | 3.1.1     | The Gallium-Nitride III-V semiconductor properties                        | 45   |

|   | 3.1.2     | Epitaxial and device structure of a GaN-HEMT                              | 46   |

|   | 3.1.3     | Electrical characteristics of the FBH GaN-HEMTs                           | 47   |

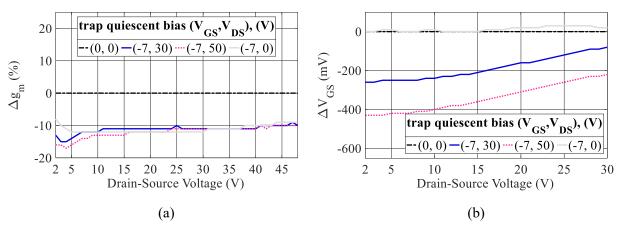

|   | 3.2 I     | mpact of charge-trapping in GaN-HEMTs on RF performance                   | 51   |

|   | 3.2.1     | Dynamic I-V measurements                                                  | 52   |

|   | 3.2.2     | Slow compressive gain and its relation to gate-lag                        | 55   |

|   | 3.2.3     | Drain current degradation in relation to the drain-lag                    | 56   |

|   | 3.2.4 | Conclusions                                                                 | 60   |

|---|-------|-----------------------------------------------------------------------------|------|

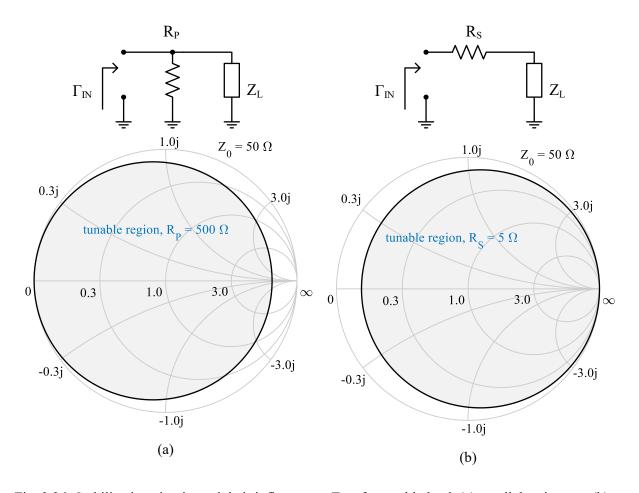

|   | 3.3   | Design considerations for supply modulation                                 | 60   |

|   | 3.3.1 | Supply voltage dependent output impedance matching                          | 61   |

|   | 3.3.2 | Probability distribution optimized design for class-G supply modulation     | 62   |

|   | 3.3.3 | Bias circuitry design for class-G operation                                 | 65   |

|   | 3.3.4 | Stability analysis                                                          | 68   |

| 4 | Clas  | s-G Supply Modulators                                                       | 73   |

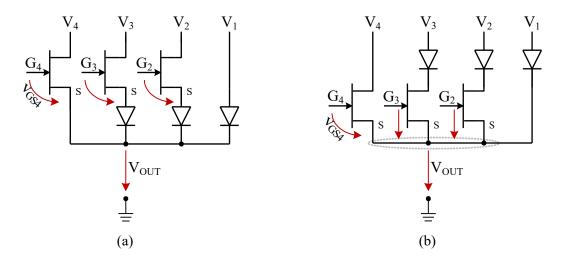

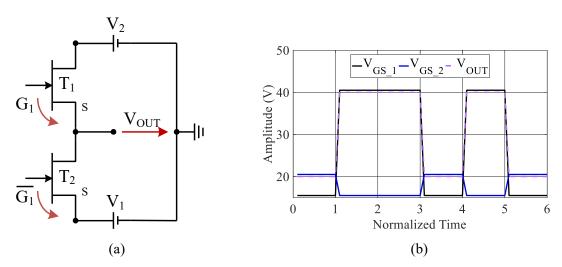

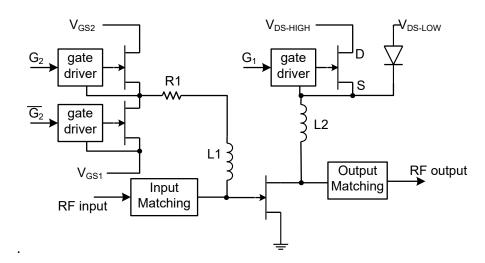

|   | 4.1   | GaN-HEMT switching stages                                                   | 73   |

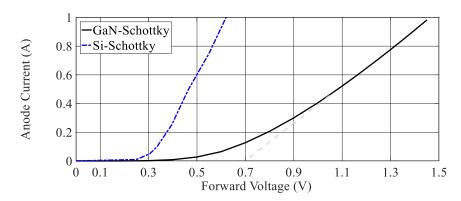

|   | 4.1.1 | GaN-based Schottky diodes                                                   | 75   |

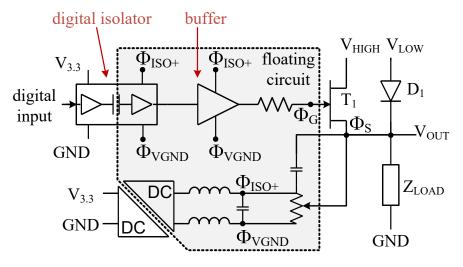

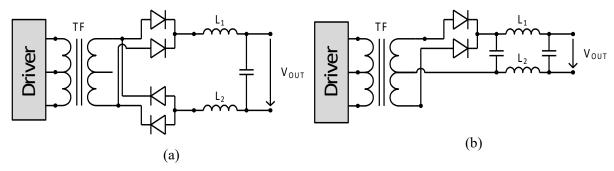

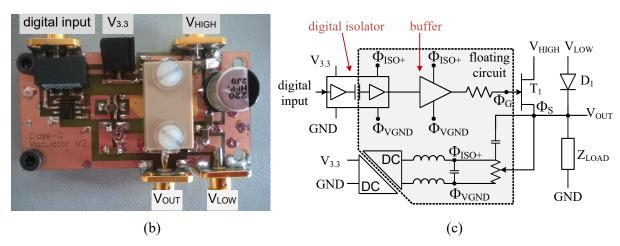

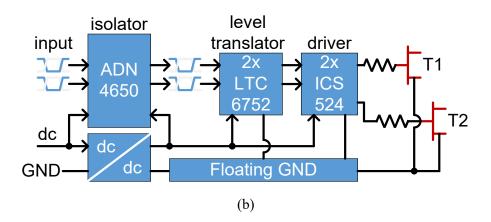

|   | 4.2   | Galvanically isolated gate drivers                                          | 76   |

|   | 4.2.1 | Digital Isolators                                                           | 78   |

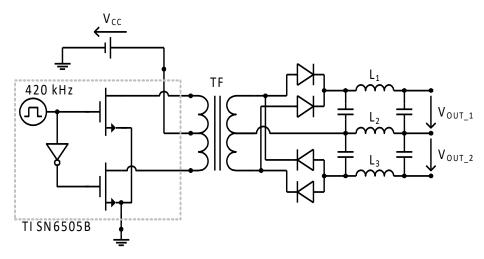

|   | 4.2.2 | Isolated DC/DC converters                                                   | 79   |

|   | 4.2.3 | Common-mode suppression.                                                    | 81   |

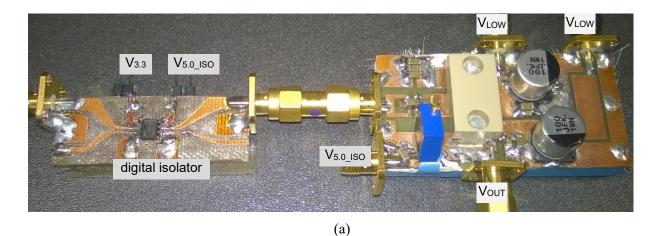

|   | 4.3   | Class-G supply modulator designs                                            | 82   |

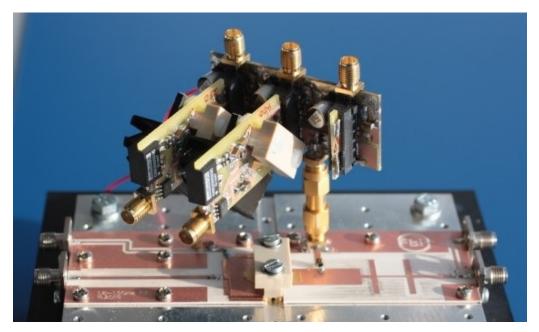

|   | 4.3.1 | The first generation                                                        | 82   |

|   | 4.3.2 | The second generation                                                       | 85   |

|   | 4.3.3 | The third generation                                                        | 86   |

| 5 | Mea   | surement Setup and Optimization                                             | 89   |

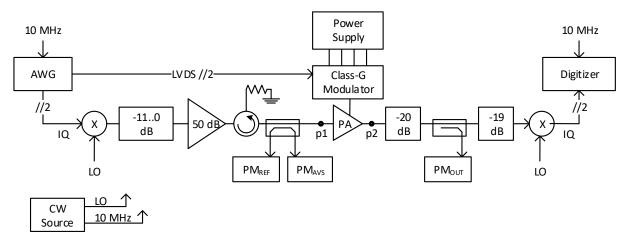

|   | 5.1   | Multiple-input single-output setup for wideband modulated measurements      | 89   |

|   | 5.2   | Synchronization                                                             | 90   |

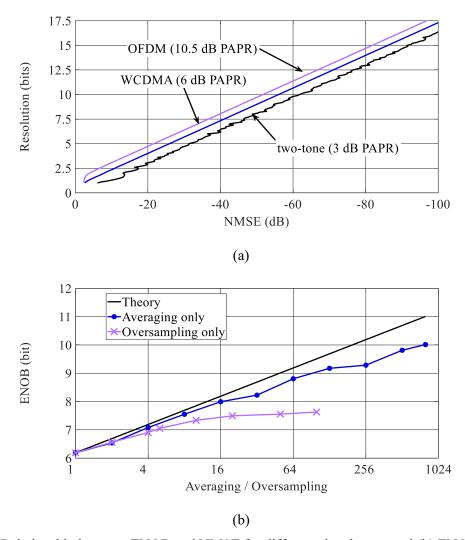

|   | 5.3   | Dynamic range enhancement                                                   | 91   |

| 6 | Digi  | tal Predistortion and Signal Processing for Class-G Power Amplifier Systems | s.95 |

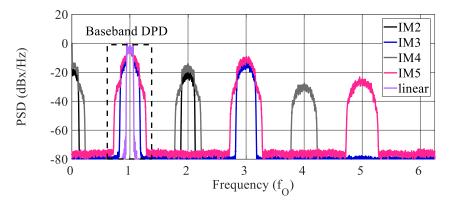

|   | 6.1   | Baseband digital predistortion                                              | 95   |

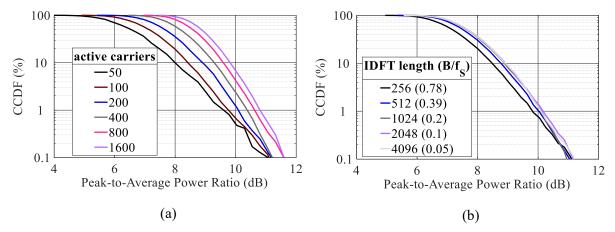

|   | 6.2   | Peak-to-average power reduction                                             | 97   |

|   | 6.3   | Iterative learning control                                                  | 101  |

|   | 6.4   | Behavioral model based digital predistortion                                | 102  |

|   | 6.4.1 | Volterra-based models                                                       | 102  |

|   | 6.4.2 | Model optimization for class-G operation                                    | 104  |

|    | 6.4.3  | Bandwidth requirements                                         | .106 |

|----|--------|----------------------------------------------------------------|------|

| 6  | .5 P   | Predistorter model training and coefficient extraction         | .107 |

|    | 6.5.1  | Model coefficient extraction                                   | .107 |

|    | 6.5.2  | Predistorter training based on iterative learning architecture | .108 |

|    | 6.5.3  | Predistorter training based on iterative learning control      | .109 |

| 7  | Class  | -G RF Power Amplifier System Optimization                      | .111 |

| 7  | .1 S   | State-of-the-art                                               | .111 |

| 7  | .2 N   | Milestone Class-G Systems                                      | .112 |

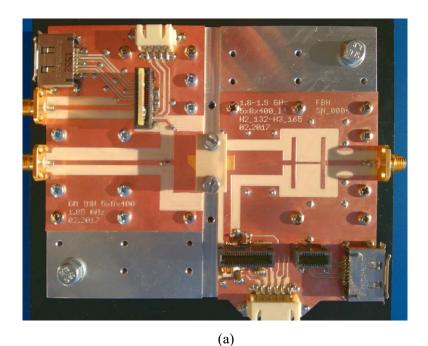

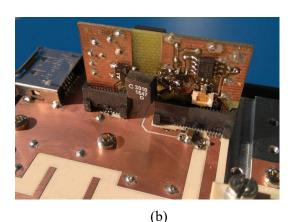

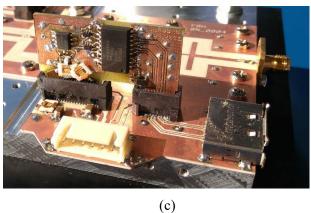

|    | 7.2.1  | 40 W RF power amplifier based system operating at 2.65 GHz     | .112 |

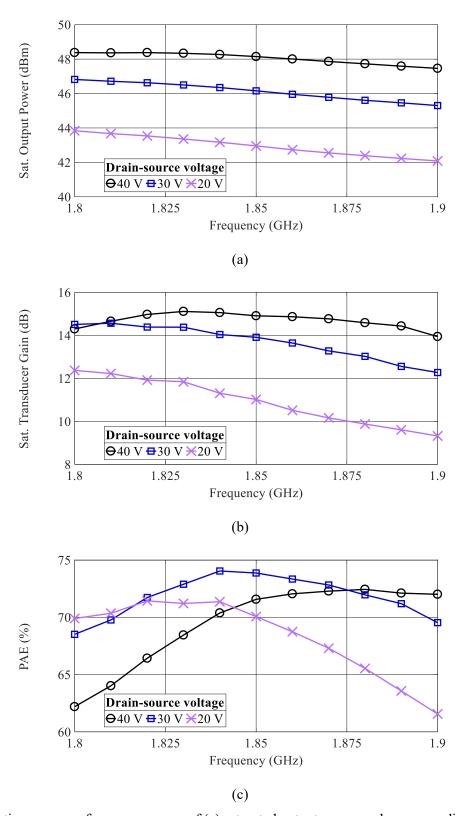

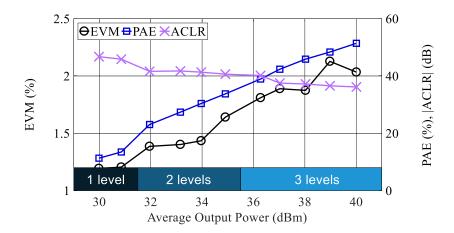

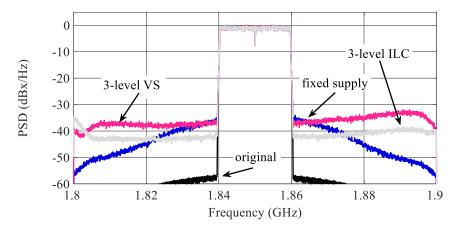

|    | 7.2.2  | 65 W three-level class-G systems with over 50% PAE at 1.85 GHz | and  |

| 20 | MHz i  | nstantaneous modulation bandwidth                              | .117 |

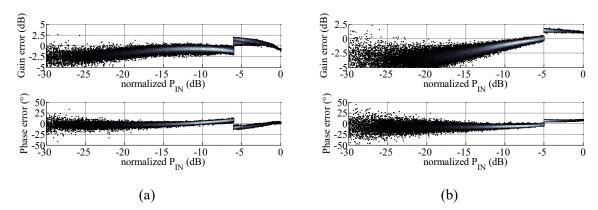

|    | 7.2.3  | Discrete-level gate bias and supply modulated PA               | .121 |

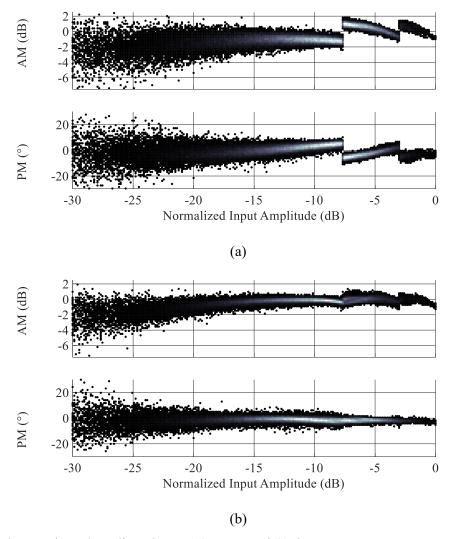

|    | 7.2.4  | 79 W three-level class-G systems with over 38% PAE at 1.8 GHz  | and  |

| 12 | 0 MHz  | instantaneous modulation bandwidth                             | .124 |

| 8  | Sumn   | nary and Outlook                                               | .129 |

| 9  | Appe   | ndix                                                           | .131 |

| 9  | .1     | Conduction angles, quiescent and ac current                    | .131 |

| 9  | .2 I   | ntermodulation distortion                                      | .132 |

| 10 | Symb   | ools and abbreviations                                         | .135 |

| 11 | Refer  | rences                                                         | .137 |

| 12 | Public | cations                                                        | .145 |

## 1 Introduction

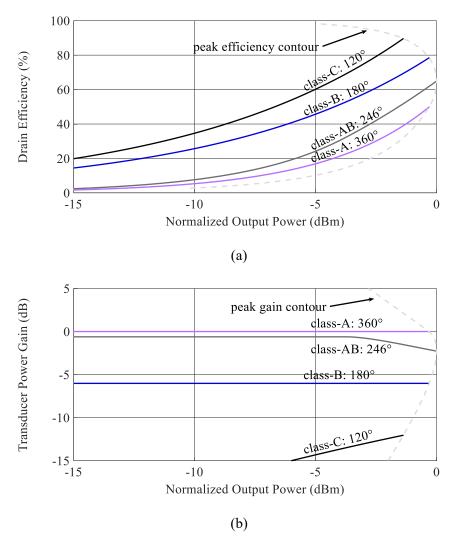

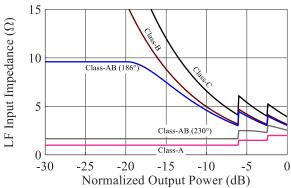

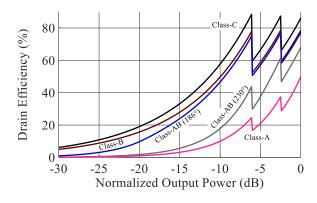

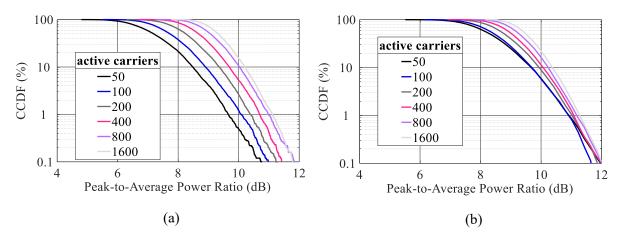

The worldwide power consumption of telecommunication networks is rapidly growing due to the steadily increasing demand on broadband internet access. With an estimated annual growth rate of over 10% and an estimated total power consumption of 257 TWh in 2012 [1], telecommunication networks contribute significantly to the worldwide power consumption. In line with this, broadband wireless data access is rapidly developing towards higher bandwidth, with a continuously growing amount of mobile subscriptions and mobile traffic [2]. For the required wireless transmission of data, a modulated radio frequency (RF) signal must be generated and amplified by an RF power amplifier (PA) to provide the output power that is high enough to compensate for the immense path-losses in a wireless transmission link, in which the attenuation scales with the square of the distance [3] - even for optimum freespace conditions. Therefore, an RF PA is needed in each base station transmitter and it is a key component when it comes to system efficiency: The RF PA consumes 50-80% of the total energy and is therefore the most power-hungry part in a base station [4]. The PA must fulfill the linearity requirements to avoid emission outside the specified RF band, since the frequency spectrum is densely utilized, and to allow transmission with low bit-error rates. This suggests operating the PA in a linear regime where it is guaranteed that also the highest power peaks are amplified without driving the PA into compression. The need for high data throughput and a high number of users demands for a structured and efficient utilization of the RF spectrum with modulation schemes that provide high spectral efficiency. In communication standards like long-term-evolution (LTE), which belongs to the 4<sup>th</sup> generation (4G) wireless networks, and the future 5G technology, orthogonal frequency-divisionmultiplexing (OFDM) is used for modulating the downlink channel, i.e., the transmission link from the base station to the mobile handset. For OFDM modulated signals the peak-toaverage power ratio (PAPR), i.e., the ratio between peak power and average transmitted power, is usually very high [5]. The PAPR increases with the number of modulated subcarriers [6], which makes the design of broadband systems even more challenging. High PAPR requires the operation of the PA in power back-off to maintain linearity. PA architectures like class-A and class-AB [7] are significantly losing efficiency when operated at power back-off. For a class-A this is caused by the fact that the drain-source current is constant while the output power (Pout) is reduced. Simulations of the drain efficiency vs. power back-off for ideal PAs of different operation classes are shown in Fig. 1.1 (a). The

efficiency drops rapidly for all PA classes with conduction angles above 180°, i.e., class-A to -B. For conduction angles above 180° the efficiency increases, but the gain decreases rapidly under power back-off, which is plotted in Fig. 1.1 (b). A good trade-off between gain and back-off efficiency is found in the class-AB range.

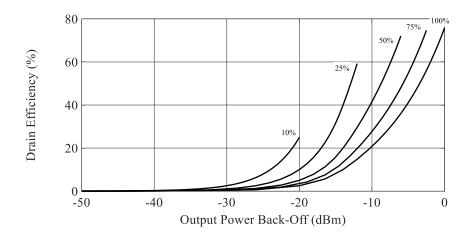

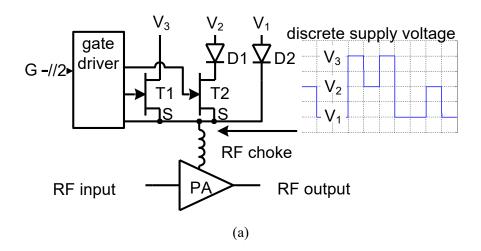

Fig. 1.2 shows the simulated drain efficiency at power back-off for different supply voltages and a class-AB PA. The efficiency can be improved in output power back-off by reducing the supply voltage of the PA. This is the key point which most supply modulation techniques are based on: Whenever the PA is operated at an output power below its maximum level, the supply voltage is decreased to achieve an increase in efficiency. In envelope tracking (ET) topologies the supply voltage is modulated with the envelope of the modulated RF signal. In contrast to the Kahn envelope elimination and restoration (EER) approach, the RF input of the PA is still driven with the modulated signal and contains phase- and amplitude information. The supply modulation can be implemented either analog with continuous supply-voltage modulation or with discrete supply voltage levels. In this work, the discrete level supply modulation is referred to as class-G supply modulation. The class-G modulator is in principle a multilevel switch which selects between two or more fixed supply voltages. This thesis investigates theory, design, and operation of such systems.

Fig. 1.1: Theoretical (a) drain efficiency and (b) transducer power gain for different conduction angles/amplifier classes vs. output power normalized to the peak output power. The transducer gain is normalized to the gain of a class-A PA.

Fig. 1.2: Simulated drain efficiency vs. power back-off of a class-AB PA, when adjusting supply voltage (curve parameter denotes % of maximum supply voltage).

## 2 Theory of Class-G Supply Modulation

Class-G supply modulation is a discrete-level supply voltage modulation technique, in which the supply voltage of a PA is switched between discrete levels. If the PA is operated with a modulated RF signal, the supply voltage is switched according to the envelope of the modulated signal. Class-G supply modulation is a relatively young concept that was first introduced for low frequency audio applications in 1976 [8]. The adoption of the class-G supply modulation for RF applications was first proposed in [9] and the first RF PA systems with class-G modulation where published in 1995 [10]. It was shown that class-G modulation works well in the RF domain, and that a high efficiency improvement can be achieved. In the initial work on class-G the linearity degradation was not the main focus, since most systems were based on integrated silicon circuits. In general, there were not many publications available on the topic at the beginning of this thesis work in 2014, especially for PA architectures based on gallium nitride (GaN) semiconductors. This has been changed by the achievements presented in this thesis. Nowadays, class-G modulation is a competitive solution which shows performance that compares well with other state-of-the-art efficiency-enhancement techniques.

In the following the concept of class-G supply modulation is discussed in detail. First, the efficiency and transducer gain of a linear PA is analyzed under the conditions of variable power back-off and supply voltage levels, but with a fixed load (R<sub>L</sub>). The behavior of the RF PA in relation to these parameters is crucial for the design of highly efficient supply modulated systems and, which is shown in this work, has proven to be a very complex issue. This first design step is usually done based on continuous wave (CW) load-pull measurements or simulations. It is important to know that, due to memory and thermal effects, the CW-based analysis does not exactly fit the behavior of the class-G PA system under dynamic operation, as it was shown in [11]. Nevertheless, the information obtained is useful to understand the effects of the various parameters of the system. Furthermore, the data can be used for simulations to investigate system performance and limitations while considering the effects of the bandwidth and amplitude distribution of the IQ modulated signal. This chapter is divided into three thematic parts. First the efficiency and linearity of a PA at power back-off is evaluated to investigate which amplifier class is best suited for class-G modulation. In the second part the dynamic requirements for the class-G supply modulator are investigated to find out how many supply voltage levels to use and which maximum switching frequency is required for a specific IQ modulation bandwidth and targeted efficiency enhancement. The

last part discusses the limitations in efficiency enhancement for the class-G modulation topology.

# 2.1 Supply modulation of linear and reduced conduction angle power amplifiers

The efficiency of linear and reduced conduction angle PAs, particularly class-A to class-C, depends on the instantaneous output power of the PA. It decreases with lower output power levels, as shown in Fig. 1.2. When a modulated signal with dynamic envelope amplitude is applied to a PA, the average efficiency is degraded since the average output power must be decreased to avoid overdriving the PA at the peak power levels. Therefore, the PAPR of the amplified signal is a very important property from a PA point of view. For a complex-valued signal vector  $\underline{x}$ , the PAPR (in dB) is defined by:

$$PAPR = 10 \cdot \log_{10} \left( \max \left( \left| \underline{x} \right|^2 \right) \right) - 10 \cdot \log_{10} \left( \min \left( \left| \underline{x} \right|^2 \right) \right) \tag{1}$$

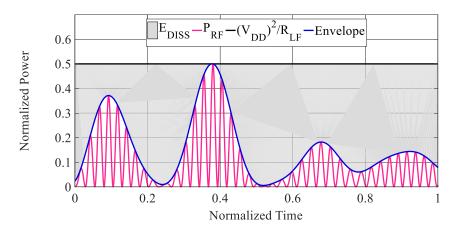

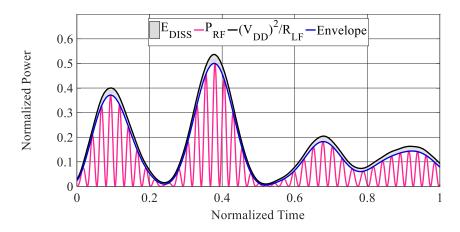

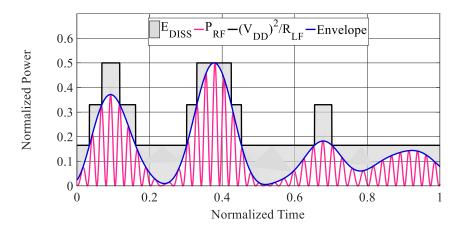

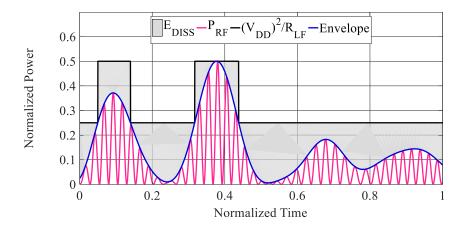

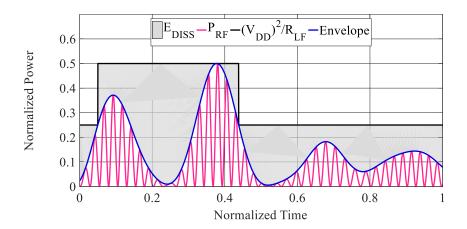

The PAPR determines the average power back-off that is required to drive the PA in a linear range, without clipping the maximum signal amplitudes. This is visualized by Fig. 2.1, which shows the time domain envelope- and RF power signals of a class-A PA. The gray shaded area represents the total dissipated energy. It can be concluded, that low envelope power levels significantly contribute to the total dissipated energy.

Fig. 2.1: Time domain signals of envelope- and RF power for a constant supply voltage. The dissipated energy is equivalent to the gray shaded area (simplified illustration).

In the following study, the possible performance enhancement of supply modulation and its impact on the PA characteristics are investigated. Therefore, the power back-off behavior of linear power amplifiers is analyzed for reduced supply voltages. Thereby it is considered

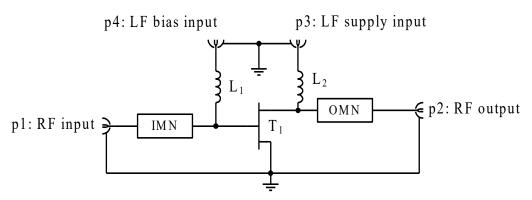

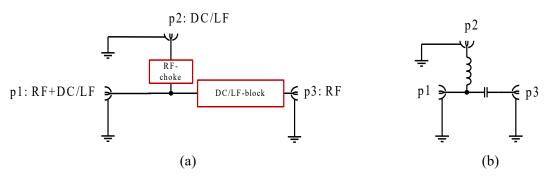

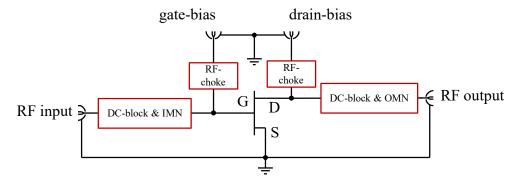

that R<sub>L</sub> is constant (no simultaneous load modulation is applied). The variation of the supply voltage causes a mismatch regarding optimum PAE or P<sub>OUT</sub>. To investigate this effect, the theory of the reduced conduction angle power amplifier classes [7] is expanded to investigate the power back-off behavior as function of the DC supply voltage levels. For this purpose, the PA is evaluated as a four-port device, two RF ports (p1, p2) and two low frequency (LF) ports (p3, p4), as shown in Fig. 2.2. The RF signal is fed into p1 and the amplified signal is obtained at p2. The supply modulator is connected at the port p3 and provides the DC to LF modulated supply voltage and current. In the first analysis, the LF port p4 is set to a constant bias level, resulting in a simplified three port representation of the PA which is also used in the literature [18]. Later in this chapter the port p4 is also modulated which allows dynamically controlling the quiescent bias point synchronously with the DC supply voltage which can be beneficial for some PA classes.

Fig. 2.2: Schematic of the supply modulated PA ports. L<sub>1</sub> and L<sub>2</sub> are RF-chokes, IMN and OMN the input- and output matching networks.

The following part is divided into four subsections: First the reduced conduction angle theory is introduced for supply modulated PAs, based on idealized conditions. Thereby the behavior of the different amplifier classes at power back-off with reduced supply voltage is investigated and the suitability for supply modulation is discussed. In the second part, the influence of discretized supply voltage levels, which represents the case of class-G supply modulation, is investigated. The third part addresses the knee I-V effects based on a quasi-static GaN-HEMT model and compares the result to the theoretically derived values. In the last part the linearity is considered, and the influence of supply modulation is discussed for continuous- and class-G supply modulation.

#### 2.1.1 Power back-off efficiency with continuously reduced supply voltage

In continuous supply modulation the supply voltage of the PA (LF port p3) is adjusted with the envelope amplitude as shown in Fig. 2.3. The comparison to the constant supply

voltage case shown in Fig. 2.1 reveals that the area of dissipated energy is reduced significantly.

Fig. 2.3: Time domain signals of envelope- and RF power for a continuously modulated supply voltage (simplified illustration).

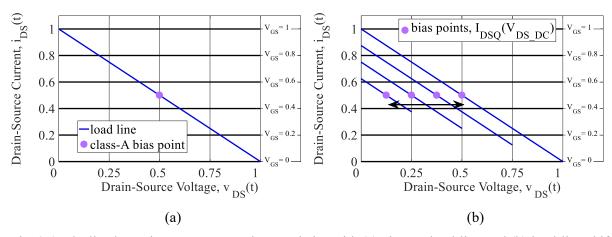

The analysis is based on an idealized model, where the saturated drain-source current is linearly dependent on the gate-source voltage. The load impedances are all set to be resistive. The drain-source current and -voltage are normalized to their maximum value ( $I_{DS\_MAX}$ ) and  $V_{DS\_MAX}$ , respectively. In Fig. 2.4 (a) the load-line for a class-A PA is shown for operation with a resistive load and a normalized DC supply voltage ( $V_{DS\_DC}$ ) of 0.5. The conduction angle ( $\alpha$ ) of the drain-source current is 360°, which makes the drain-source voltage  $v_{DS}(t)$  linearly dependent on the drain-source current  $i_{DS}(t)$ . In this case the PA operates linearly and the load line slope  $R_{LL}$  is constant (2) and identical to the load resistance  $R_L$  (3):

$$\frac{dR_{LL}}{dt} = \frac{d}{dt} \frac{v_{DS}(t)}{i_{DS}(t)} = 0 , \alpha \ge 360$$

(2)

$$R_L = R_{LL}$$

,  $\alpha \ge 360$  (3)

For lower conduction angles, the drain-source current is clipped at a level of zero to avoid negative current values. This causes the generation of harmonics. In the reduced conduction angle theory, the fundamental is terminated by a fixed resistance ( $R_{L1}$ ) and all other harmonics are terminated by a short [7]. Therefore, the amplitude of the AC output voltage ( $\hat{v}_{DS\_AC}$ ) depends only on the amplitude of the fundamental drain-source current ( $\hat{i}_{DS\_AC1}$ ) and  $R_{L1}$  (4). This causes the load-line slope to differ from  $R_{L1}$  if other harmonics are present (5).

$$\widehat{\mathbf{v}}_{\mathrm{DS}\ \mathrm{AC}} = \widehat{\mathbf{i}}_{\mathrm{DS}\ \mathrm{AC1}} \cdot \mathbf{R}_{\mathrm{L1}} \tag{4}$$

$$R_{L} \neq R_{LL} \quad , \quad \alpha < 360 \tag{5}$$

When supply modulation is applied, the load-line is shifted horizontally, since R<sub>L</sub> is constant and the quiescent drain-source current (I<sub>DSQ</sub>) is independent of V<sub>DS\_DC</sub>. The shift of the load-line and the quiescent bias points with supply voltage is shown in Fig. 2.4 (b) for the class-A case.

Fig. 2.4: Idealized transistor DC output characteristics with (a) class-A load-line and (b) load-line shift with DC supply voltage reduction.

For the class-A condition shown it is observed that the drain-source current is not excited over its full range and the current AC/DC ratio is reduced. This is caused by the fixed load impedance and the reduced supply voltage and is also valid for other PA classes. With the definition of  $v_{DS}(t)$  in (6) the maximum value  $\hat{1}_{DS\_AC1}$  can be calculated, based on two conditions. First (7) must be true to avoid negative values of  $v_{DS}(t)$  and second (8) must be fulfilled to ensure that  $v_{DS}(t)$  does not exceed  $V_{DS\_MAX}$ . For maximum output power,  $V_{DS\_DC}$  must be operated in the range from 0 to 0.5, therefore, (8) is not a limitation during operation with reduced  $V_{DS\_DC}$ .

$$v_{DS}(t) = V_{DS\_DC} - \hat{i}_{DS\_AC1} \cdot \cos(\omega_1 t) \cdot R_{L1}$$

(6)

$$\widehat{\mathbf{i}}_{DS\_AC1} \left( \mathbf{V}_{DS\_DC} \right) \leq \frac{\mathbf{V}_{DS\_DC}}{\mathbf{R}_{L1}} , \frac{1}{2} \geq \mathbf{V}_{DS\_DC}$$

(7)

$$\widehat{i}_{DS\_AC1}(V_{DS\_DC}) \leq \frac{1 - V_{DS\_DC}}{R_{L1}} , \frac{1}{2} \leq V_{DS\_DC}$$

(8)

The limitation of î<sub>DS AC1</sub> causes several effects in the supply modulated PA: The maximum output power (Pout MAX) becomes dependent on the supply voltage as defined in (9). It scales quadratically with the supply voltage, resulting in a V<sub>DS DC</sub> dependent reduction of the maximum output power (P<sub>OUT BO</sub>) with a decay of -20 dB/dec (10). Additionally, the efficiency of the PA classes with positive quiescent current (I<sub>DSQ</sub> > 0 A; class-AB to class-A) reduces, since the DC supply current (I<sub>DS DC</sub>) does not scale linearly with î<sub>DS AC1</sub> (derivation of I<sub>DS DC</sub> and î<sub>DS AC1</sub> in appendix 9.1). This results in a V<sub>DS DC</sub> dependent drop of the DC power consumption at an output power back-off level (P<sub>DC BO</sub>) (11) of less than -20 dB/dec. The worst case is a class-A PA, where P<sub>DC BO</sub> decreases with only -10 dB/dec, since I<sub>DS DC</sub> is constant, independent of V<sub>DS</sub> <sub>DC</sub> (I<sub>DS</sub> <sub>DC</sub> = I<sub>DSO</sub>). A possible solution for the class-A case is the modulation of the gate-source bias port (p4) to reduce I<sub>DSQ</sub> simultaneously with V<sub>DS DC</sub>, which is discussed in Chapter 2.1.3. By combining (10) and (11) the drain efficiency at power back-off ( $\eta_D$  BO) in dependency of the peak drain efficiency ( $\eta_D$  MAX), i.e.,  $\eta_D$  at maximum supply voltage and output power, is derived in (12). The DC to LF impedance at power backoff (Z<sub>LF BO</sub>), seen at port p3, is seen by the supply modulator and, therefore, an important parameter for the design of modulators. The impedance is defined by the fraction of V<sub>DS DC</sub> and the current I<sub>DS DC</sub> (13). Due to the dependency between V<sub>DS DC</sub> and P<sub>OUT BO</sub> in (10),  $Z_{LF\ BO}$  is linearly dependent on the back-off drain efficiency  $\eta_{D\ BO}$ .

$$P_{OUT\_MAX}(V_{DS\_DC}) = \frac{\hat{i}_{DS\_AC1}(V_{DS\_DC})^2 \cdot R_{L1}}{2}$$

$$= \frac{V_{DS\_DC}^2}{2 \cdot Z_{L1}}$$

(9)

$$P_{\text{OUT\_BO}}(V_{\text{DS\_DC}}) = 10 \cdot \log_{10} \left( \frac{P_{\text{OUT\_MAX}}(V_{\text{DS\_DC}})}{P_{\text{OUT\_MAX}}(1)} \right)$$

$$= 20 \cdot \log_{10} (V_{\text{DS\_DC}}) \text{ (dB)}$$

(10)

$$P_{DC\_BO}(V_{DS\_DC}) = 10 \cdot \log_{10} \left( \frac{I_{DS\_DC}(V_{DS\_DC})}{I_{DS\_DC}(1)} \right) + \log_{10} (V_{DS\_DC}) \quad (dB) \quad (11)$$

$$\eta_{D_{BO}}(V_{DS_{DC}}) = \eta_{D_{MAX}} \cdot 10^{\left(\frac{P_{OUT_{BO}}(V_{DS_{DC}}) - P_{DC_{BO}}(V_{DS_{DC}})}{10}\right)}$$

$$= \eta_{D_{MAX}} \cdot \frac{V_{DS_{DC}} \cdot I_{DS_{DC}}(1)}{I_{DS_{DC}}(V_{DS_{DC}})}$$

(12)

$$Z_{LF\_BO}(V_{DS\_DC}) = \frac{V_{DS\_DC}}{I_{DS\_DC}(V_{DS\_DC})}$$

$$= k \cdot n_{D\_BO}(V_{DS\_DC})$$

(13)

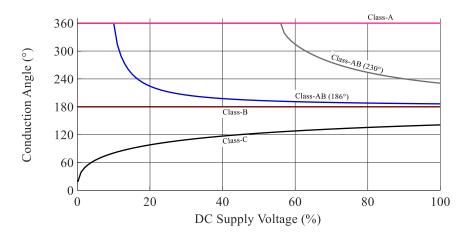

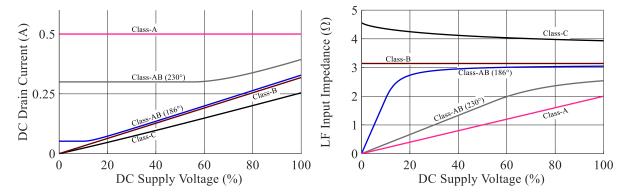

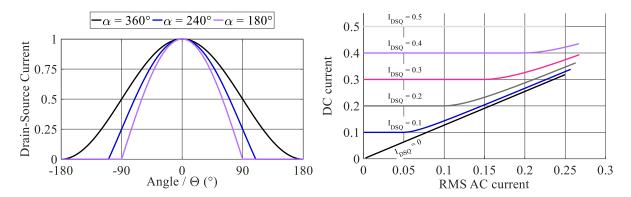

Fig. 2.5 shows the I<sub>DS</sub> conduction angle as function of the V<sub>DS\_DC</sub> for selected PA classes. The conduction angle for class-A and class-B is constant over the full supply voltage range. For class-C the conduction angle is reduced with the supply voltage, having the effect that the PA is driven deeper into class-C. The conduction angle of the class-AB region drifts towards class-A, depending on the conduction angle at full supply voltage.

Fig. 2.5: Influence of the supply voltage reduction on the I<sub>DS</sub> conduction angle for different PA classes.

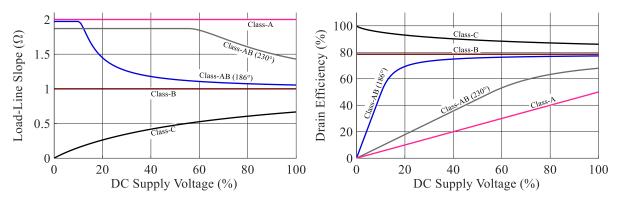

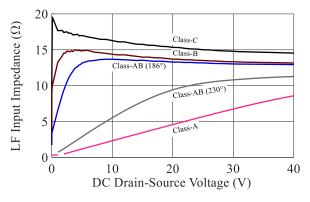

The horizontal load-line shift shown in Fig. 2.4 (b) is valid in case of a constant conduction angle, i.e., class-A and class-B. For class-AB and class-C the load-line is shifted and additionally the slope changes. This is caused by the fundamental of the drain-source current,  $\hat{\imath}_{DS\_AC1}$ , which does not scale linearly with the supply voltage. The load-line slope vs. the supply voltage is shown in Fig. 2.6 for different PA classes. For the class-AB condition the load-line slope is converging towards the resistance of the fundamental load, when  $V_{DS\_DC}$  is reduced. The calculated drain efficiency as function of the supply-voltage is shown in Fig. 2.7. For class-A, a linear decrease of efficiency with supply-voltage back-off is seen. The class-B case holds a constant efficiency level. For the supply modulator the impedance of the LF supply port of the PA (p3) is very important for the design of filters if used. If the

impedance varies with the supply voltage, the filter characteristics will change as well. To evaluate the impedance at p3, I<sub>DS DC</sub> (shown in Fig. 2.8) and the supply voltage are used to calculate the impedance is as shown in Fig. 2.9. For class-B the impedance seen by the supply modulator is constant over the supply voltage. For class-A the strongest variation is observed, since the DC current is constant due to the high quiescent current. Therefore, class-B to deep class-AB seem to be viable candidates as bias conditions for supply modulated power amplifiers. Comparing Fig. 2.9 to Fig. 2.7 shows that the drain efficiency and the LF input impedance are linearly dependent, as defined by (13).

Fig. 2.6: Load-line slope for different conduction Fig. 2.7: Drain efficiency for different PA classes angles as function of the DC supply voltage.

vs. DC supply voltage.

Fig. 2.8: DC value of the drain-source current as function of the DC supply voltage.

Fig. 2.9: Input impedance seen at the LF drain supply port (p3) as function of the DC supply voltage.

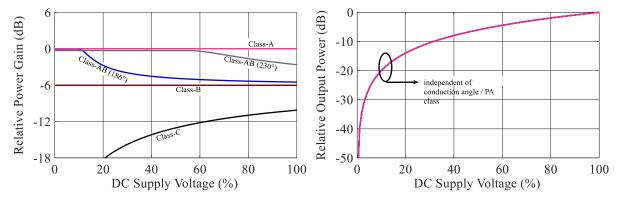

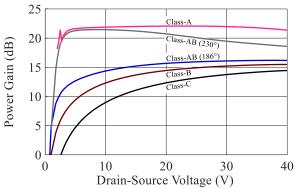

In Fig. 2.10 the normalized power gain (referenced to the gain of class-A) is shown. In class-C the gain decreases rapidly with reduced supply voltage, which makes it impracticable for supply modulation. Class-B shows a constant gain 6 dB below the class-A case. This is a significant drawback, since every dB in gain is important in a PA system. The lower gain may not affect the PAE of the main PA significantly, but it requires a preamplifier or a multistage design, depending on the requirements and the technology used. The relationship between P<sub>OUT\_MAX</sub> and the V<sub>DS</sub> is shown in Fig. 2.11, according to the definition in (9). The PA class is not influencing the maximum output power at supply voltage back-up. Finally, the definition of the optimum PA class will be based on the statistics of the amplified modulated signal, especially the PAPR. Factors like voltage dependent output capacitances of the transistor [22], charge trapping, knee I-V effects and thermal heating will cause the design to diverge from the ideal theory presented and must be accounted for individually in a PA design.

Fig. 2.10: Relative power gain for different PA classes at maximum output power as function of the DC supply voltage.

Fig. 2.11: Maximum output power normalized to the power at 100% drain-source voltage for different power amplifier classes / conduction angles.

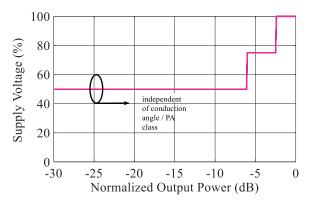

## 2.1.2 Power back-off efficiency for discretized supply voltage modulation

The back-off behavior derived in the previous subsection shows the PA behavior for different PA classes when operated at supply voltage back-off. Thereby, the input signal power is adjusted to achieve the maximum output power for the specific supply voltage, resulting in an output power dependent function for the supply voltage setup shown in Fig. 2.11. In class-G operation, only discrete supply voltage levels are available. Fig. 2.12 shows the time domain signals of the envelope- and RF power and the corresponding supply voltage for a three-level class-G modulation.

Fig. 2.12: Time domain signals of envelope- and RF power for class-G supply voltage modulation (simplified illustration).

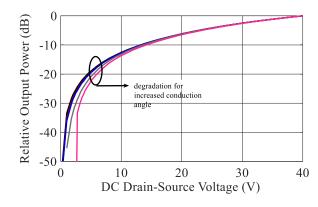

The switching of the supply voltage between the discrete levels causes discontinuities in all supply voltage dependent figures, i.e., the efficiency, DC power consumption, and LF impedance. For the following analysis the supply voltage is modulated with three levels located at 50%, 75% and 100% of the normalized supply voltage as shown in Fig. 2.13. The LF input impedance as function of the normalized output power is plotted in Fig. 2.14. The comparison to Fig. 2.9 shows that the behavior under power back-off significantly changed due to the discretization of the supply voltage. This is on one hand caused by the abrupt changes of the supply voltage and on the other hand by the constant supply voltage levels. Since the LF impedance in combination with a RF-choke represents the load connected to the supply modulator, its behavior is of high importance and needs to be considered carefully in the design of the RF-choke and the dimensioning of the modulator switching stage. This topic is addressed in Chapter 3.3.3. The drain efficiency shown in Fig. 2.15 and the corresponding DC power consumption in Fig. 2.16 are both affected by the discretization of the supply voltage. The back-off efficiency improvement is reduced in the intervals with constant supply voltage, resulting in a supply voltage level dependent efficiency improvement for class-G supply modulation.

Fig. 2.13: Supply voltage level vs. normalized output power.

Fig. 2.14: LF input impedance seen at the drain bias interface vs. normalized output power for different conduction angles.

Fig. 2.15: Drain efficiency vs. normalized output power for different conduction angles.

Fig. 2.16: DC power consumption vs. normalized output power for different conduction angles.

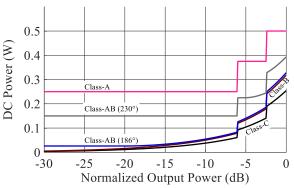

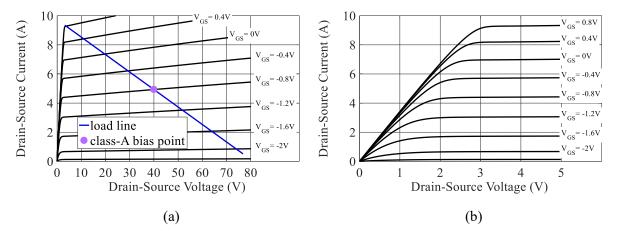

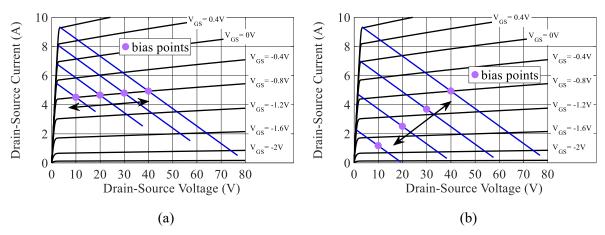

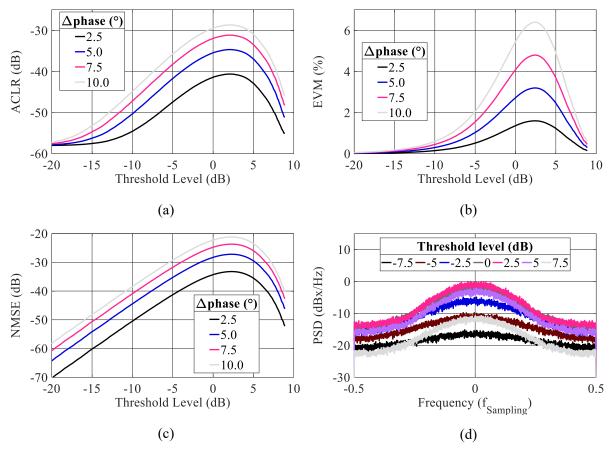

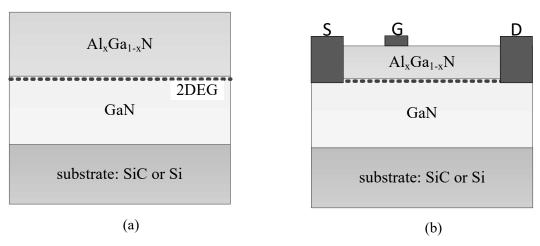

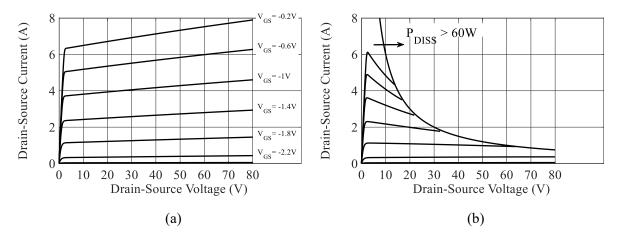

#### 2.1.3 Quasistatic GaN-HEMT model based simulations with knee I-V effects

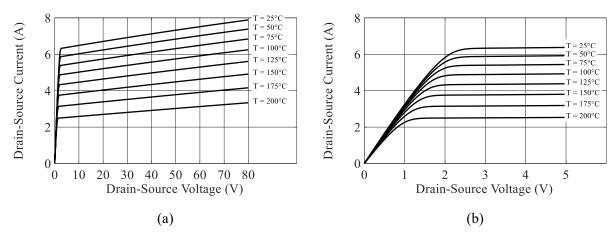

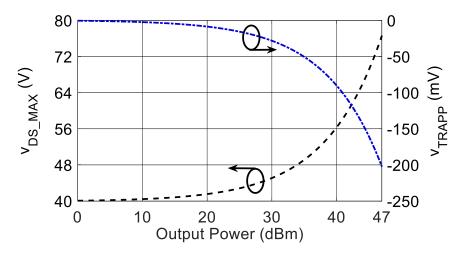

For the analysis of the multiport PA in a realistic environment, a transistor model is used. The model is based on a packaged GaN-HEMT fabricated at the FBH. The transistor has 0.5 µm gate length and a total gate width of 16 mm. It delivers a maximum RF output power of ~80 W at 2 GHz at 40 V supply voltage. This transistor is used in most of the implemented systems presented in Chapter 7 and proved to be very robust and efficient. More details on the technology and the device are presented in Chapter 3.1. The dataset used for the following analysis is based on simulations using the Chalmers model proposed by Angelov et al. [19]. The DC- and thermal characteristics are extracted and applied to the reduced conduction angle power amplifier theory, including the effect of the knee I-V region. The focus is on the qualitative behavior, since details are related to a specific device only and may not have a general importance. The DC characteristics are presented in Fig. 2.17 (a) for the full I-V characteristics and in (b) for the knee I-V region. For supply modulated PAs, the knee I-V

region becomes more significant, since its influence on efficiency is increased with reduced  $V_{DS}$ . As seen in (b),  $V_{DS}$  must be larger than zero for a positive  $I_{DS}$ , which limits the maximum efficiency.

Fig. 2.17: Full DC characteristics with an idealized class-A load-line (a) and knee I-V region (b) of an exemplary RF GaN-HEMT used for class-G supply modulated PAs. Thermal self-heating is not simulated.

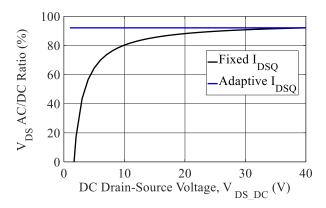

The shift of the load line with supply modulation is shown in Fig. 2.18 (a) for a fixed gate-source bias voltage and in (b) for an adaptive bias voltage (applied at port p4, Fig. 2.2). A comparison of Fig. 2.18 (a) with the idealized case Fig. 2.4 (b) shows that the load line is shifted horizontally, but  $I_{DSQ}$  exhibits only a weak dependence on  $V_{DS\_DC}$ . Besides that, the knee I-V voltage is limiting the AC output voltage swing. The modulation of the fourth port shown in Fig. 2.18 (b) reveals some advantages over the three-port implementation shown in (a): First, the reduction of  $I_{DSQ}$  reduces the dissipated DC power and second, the impact of the knee I-V region on the possible output voltage swing is reduced. This is verified by the analysis of the amplitude ratio of AC- and the DC drain-source supply voltage ( $V_{DS\_AC\_REL}$ ) shown in Fig. 2.19. With the adaptive biasing, the ratio is kept constant over the full DC supply voltage range.

Fig. 2.18: Horizontal shift of the idealized class-A load-line for reduced supply voltages with fixed I<sub>DSO</sub> (a) and with combined gate-bias modulation at p4 (b).

Fig. 2.19: Impact of the knee I-V region on the ratio of AC amplitude and DC supply voltage with fixed quiescent drain-source current and adaptive biasing

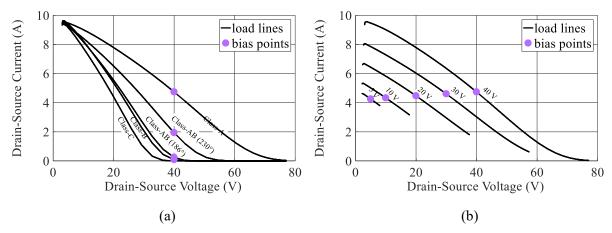

The class-A load lines shown in Fig. 2.18 are idealized load lines with constant slope and the PA is not driven into the knee I-V region. The load lines extracted from simulations are shown in Fig. 2.20 (a) for different bias conditions at  $V_{DS\_DC} = 40$  V and for a class-A biasing and different  $V_{DS\_DC}$  in (b). The input power drive is adjusted to achieve  $V_{AC\_REL} = 90\%$  to avoid driving the PA into the knee I-V region. Comparing the idealized load line shown in Fig. 2.18 (a) to the simulations in Fig. 2.20 (b) reveals that harmonics are generated since the load line slope is not constant. For reduced supply voltages, an increased impact of the knee I-V region on the possible output voltage swing is observed.

Fig. 2.20: Simulated load-lines for (a) different bias points and fixed  $V_{DS}$  and (b) for a class-A condition at different  $V_{DS}$ .  $V_{AC}$  REL = 90%.

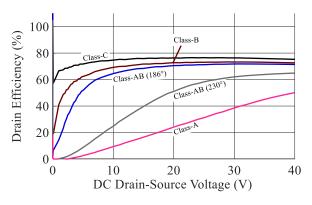

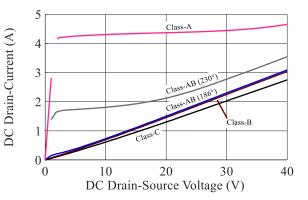

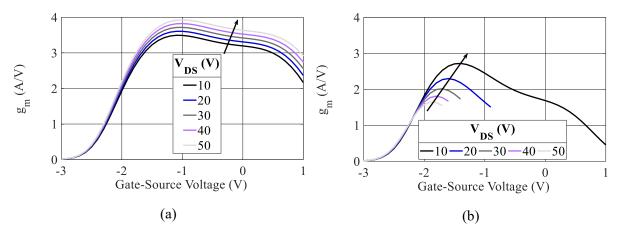

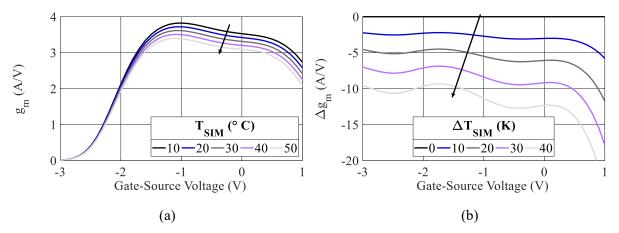

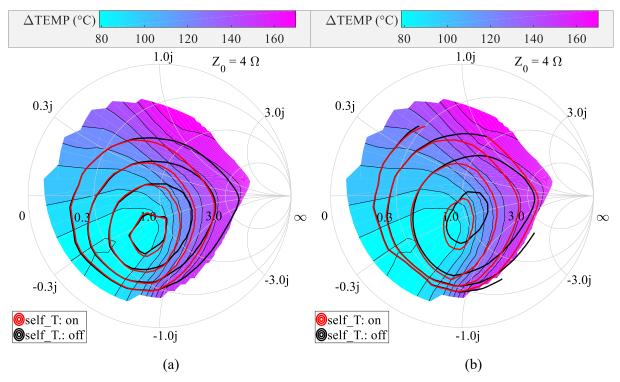

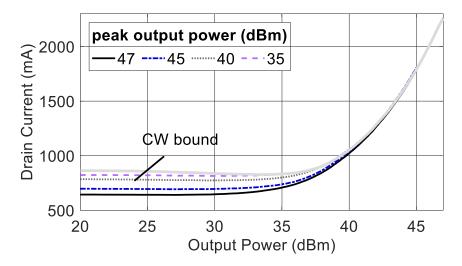

The simulation results based on the GaN-HEMT model for the different amplifier classes are shown in the following. The maximum supply voltage level is set to  $V_{DS} = 40 \text{ V}$ . Fig. 2.21 shows the drain efficiency as function of V<sub>DS</sub>. The comparison to the theoretical PA classes (Fig. 2.7) shows a large deviation for low conduction angles (class-C and class-B) for low V<sub>DS</sub>. The efficiency at the maximum supply voltage shows a slight degradation for the reduced conduction angle classes. For class-A to class-AB the deviation is less significant due to the inherently low efficiency of these PA classes. I<sub>DS</sub> is shown in Fig. 2.22 and provides more information on the behavior at low supply voltages. The impact of the knee I-V for supply voltages below 5 V is clearly seen in the class-A and class-AB condition, where the current is drastically reduced due to the on resistance (R<sub>ON</sub>) of the GaN-HEMT. The LF input impedance and the power gain are plotted in Fig. 2.23 and Fig. 2.24, respectively. They are also affected by the knee I-V characteristics. Besides the influence of the knee I-V region, a larger power gain deviation is observed for deep class-AB and class-B biasing. The V<sub>DS</sub> dependent maximum output power is shown in Fig. 2.25. For the drain efficiency and the LF input impedance an interesting behavior is seen: For the idealized case with continuous supply modulation it was seen that both curves are linearly dependent and scaled by a fixed factor. For the simulations based on the GaN-HEMT model this behavior disappears. The explanation for this behavior is found in the back-off behavior of the maximum output power as function of V<sub>DS</sub>, which is not constantly decreasing with -20 dB/dec as derived theoretically. This can be verified in the semi-logarithmic representation of the V<sub>DS</sub> dependent maximum output power for the theoretical- and simulation-based results shown in Fig. 2.26. For levels below 20 V the deviation increases rapidly.

Fig. 2.21: Simulated drain efficiency for different Fig. 2.22: Simulated DC drain current (I<sub>DS</sub>) as amplifier classes as function of the DC supply voltage.

function of the DC supply voltage.

Fig. 2.23: Simulated LF input impedance seen at p3 as function of the DC supply voltage.

Fig. 2.24: Simulated power gain for different amplifier classes as function of the DC supply voltage.

Fig. 2.25: Simulated maximum relative output power as function of the DC supply voltage.

Fig. 2.26: Comparison of theoretical and simulated maximum relative output power as function of the DC supply voltage.

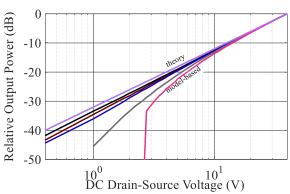

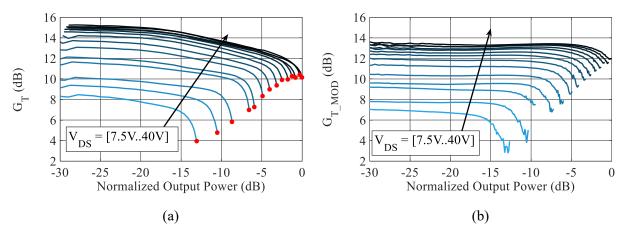

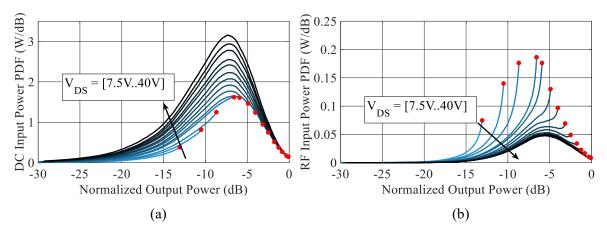

The power-added efficiency (PAE) and G<sub>T</sub> are calculated for several fixed supply voltage levels and a fixed quiescent bias current of 600 mA. The simulation results are shown in Fig. 2.27. Self-heating effects are not included in the simulations. For low supply voltages a strong impact of the knee I-V region is visible. For supply modulated systems this is a limiting boundary condition for the lower supply voltage level.

Fig. 2.27: Simulated of (a) PAE and (b)  $G_T$  vs. output power for different supply voltages in a class-AB bias point (600 mA quiescent drain current). Harmonics are shorted and fundamental matched to  $R_{L1} = 8 \ \Omega$ .

### 2.2 Class-G modulator switching speed requirements

The previous chapter investigated the PA characteristics at reduced supply voltages. In modulated operation the signal amplitudes are distributed depending on the modulation format. Therefore, the calculation of the performance under modulated operation requires the specification of a modulated signal. In wireless communication the baseband information is modulated on an RF carrier. The spectral efficiency of a modulation format is defined as the ratio of data rate to modulation bandwidth. For optimum utilization of the usable RF spectrum, the spectral efficiency must be as high as possible. Therefore, complex-valued baseband signals, i.e., IQ-signals, are used to fully utilize the lower and upper sideband. A widespread modulation scheme that allows high spectral efficiency and the possibility to handle frequency selective distortions is the orthogonal frequency division multiplexing (OFDM). It allows the modulation of multiple carriers in the frequency domain with arbitrary IQ modulation formats, e.g., QAM. In mobile communication systems OFDM is widely used in downlink channels [23], [24] and is therefore used in this work to generate the reference test signals.

In supply modulated PA systems, the modulator must track the envelope amplitude of the modulated signal. The required envelope signal is independent of the RF carrier and directly available from the baseband IQ signal. The instantaneous envelope  $\underline{v}_{ENV}(t)$  of a complex-valued baseband signal  $\underline{x}_{BB}(t)$  is defined as:

$$v_{ENV}(t) = \left| \underline{x_{BB}}(t) \right|$$

$$= \sqrt{x_{I}(t)^{2} + x_{Q}(t)^{2}}$$

(14)

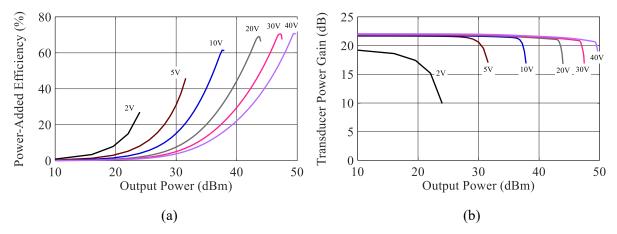

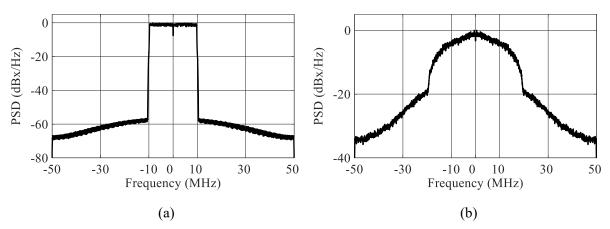

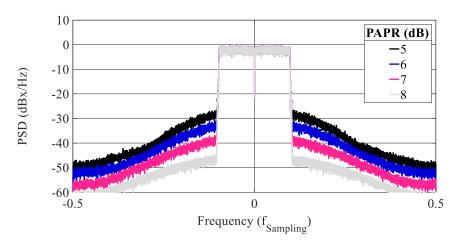

A comparison of the IQ modulation bandwidth and the envelope bandwidth is presented in Fig. 2.28 for an OFDM-modulated signal with 20 MHz modulation bandwidth. Due to the non-linear function of the square root and the power of two in (14), the bandwidth of the envelope signal is expanded to infinity if both signals, in-phase  $x_I(t)$  and quadrature  $x_O(t)$ , are modulated. This makes it impossible for supply modulators to perfectly track the envelope amplitude in continuous supply modulated systems, but it is sufficient for a continuous supply modulated system to track a bandwidth three to seven times higher than the IQ modulation bandwidth [25], [26]. The efficiency improvement decreases if the bandwidth is further reduced, since a DC offset voltage must be applied to the low-pass filtered envelope signal to ensure that the amplitude does not drop below the original envelope amplitude. Values below the targeted level cause saturation of the PA and degrade the linearity. Furthermore, the lowpass filtering causes an overshoot of the supply voltage and thus may cause temporary operation outside the PA safe operating area. The impact of low-pass filtering on the signal v<sub>ENV</sub>(t) is shown in Fig. 2.29, where the unfiltered envelope is compared to an ideal low-pass filtered version of (a) 20 MHz and (b) 60 MHz. With the narrow filter bandwidth (a) the amplitude cannot follow the targeted envelope voltage accurately, which requires a higher DC offset. With the wider filter bandwidth in (b) the required DC offset is much lower, and the envelope is tracked more accurately. As a result, the possible efficiency enhancement is higher than in case (a).

Fig. 2.28: Amplitude power spectral density of (a) an IQ modulated multicarrier baseband signal and (b) its envelope. (An averaging filter is applied in the frequency domain.)

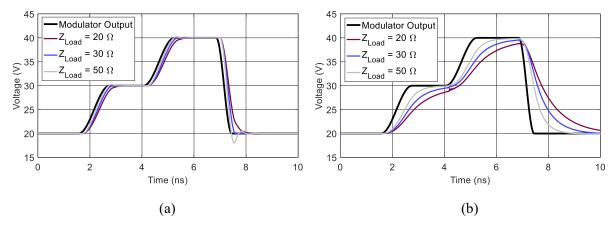

Fig. 2.29: Time domain representation of the low-pass filtered envelope of a 20 MHz OFDM signal, for an ideal filter of (a) 20 MHz and (b) 60 MHz cut-off frequency. A DC offset is applied to the low-pass signal to ensure that the amplitude is always equal or higher than the unfiltered signal. Also, the overall peak amplitude of the entire signal is plotted (denoted by P<sub>MAX\_LP</sub> for the low-pass filtered signal and by P<sub>MAX</sub> for the original signal, respectively).

Due to the supply voltage discretization in class-G supply modulation, the modulator cannot track the envelope signal accurately. It is therefore accepted that the modulator output signal differs from the envelope. For PAs based on GaN-HEMT technology, nonlinearities are introduced by the supply-modulation since the gain of the PA depends on the supply voltage. With the high computational power available nowadays it is possible to correct the nonlinearities using digital predistortion techniques (DPD), which is discussed in Chapter 6. DPD linearization is only possible, if it is ensured that the supply voltage of the PA is always high enough to avoid overdrive. Compared to continuous supply modulation class-G supply modulation has the advantage that if the envelope dynamics would require the modulator to switch faster than its hardware limits, the control software can skip short pulses and keep a higher supply voltage level instead. Therefore, one does not need a low-pass filter that may cause a supply voltage overshoot. An example for a two-level class-G system is given by

Fig. 2.30 for a fast class-G modulator that tracks all envelope peaks and in Fig. 2.31 for a modulator with an increased minimum pulse width that results in a pulse-skip operation. In both cases the supply voltage is always high enough to avoid driving the PA into saturation. It is obvious that the pulse-skip modulation achieves less efficiency improvement since the area of dissipated energy, E<sub>DISS</sub>, is increased.

Fig. 2.30: Supply waveform, envelope and RF signal against time for fast two-level class-G modulation.

Fig. 2.31: Supply waveform, envelope and RF signal against time for a two-level class-G modulation with increased minimum pulse width, maintaining signal integrity.

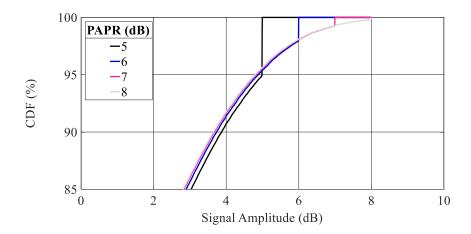

The relationship between the IQ modulation bandwidth and the switching speed limitations of the modulator is investigated in the following in detail. The subject turns out to be very complex, especially when the class-G system has more than two supply voltage levels. The results are based on the study in [27]. The following analysis assumes that the linearity is restored using DPD. This assumption is required to ensure that the amplitude probability density function (PDF) of the normalized output signal is equal to the test signal PDF. An important specification of a class-G modulator is the duration of the shortest supply

voltage pulses  $t_{P\_MIN}$  it can deliver to the PA. Based on the definition of  $t_{P\_MIN}$  the maximum toggle frequency  $f_{SW~MAX}$  is derived:

$$f_{SW\_MAX} = \frac{1}{2 \cdot t_{P MIN}}$$

(15)

It defines the maximum frequency at which the modulator can switch for a 50% duty-cycle signal. It is used in the following to define the switching speed of a class-G modulator and to define a relation between the IQ modulation bandwidth and the modulator switching speed. It must be noted, that the power spectrum of the modulator output signal has a much higher bandwidth than  $f_{SW\_MAX}$ , since the modulator generates almost rectangular pulses which contain higher-order harmonics. For the analysis of the relationship between IQ modulation bandwidth and modulator performance, we define the relative switching frequency

$$f_{REL\_G} = \frac{B_{IQ}}{f_{SW MAX}}$$

(16)

where  $B_{IQ}$  is the IQ modulation bandwidth. With the definition of  $f_{REL\_G}$  the analysis of the modulator switching speed will be independent of the IQ modulation bandwidth.

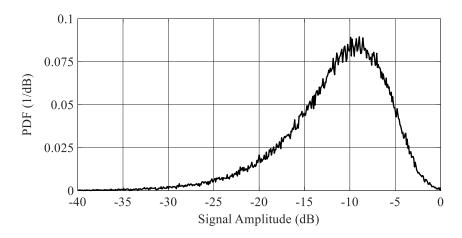

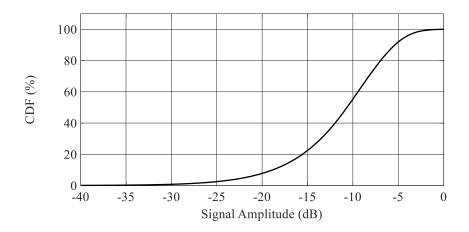

Since each modulation format has its own characteristic PDF of the signal power (which also defines the signal PAPR) the following analysis represents only modulation formats based on OFDM accurately. For this analysis an OFDM modulated signal with 9 dB PAPR is used. The modulation bandwidth is 20% of the sampling rate, i.e., 100 MHz IQ modulation bandwidth requires a sampling rate of 500 MS/s. The PDF and the cumulative distribution function (CDF) of the test signal are shown in Fig. 2.32 and Fig. 2.33, respectively.

Fig. 2.32: Amplitude probability density function of the OFDM-modulated test signal.

Fig. 2.33: Cumulative amplitude density function of the OFDM-modulated test signal.

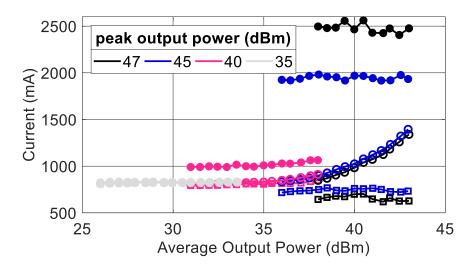

The modulator minimum pulse width t<sub>P\_MIN</sub> is calculated based on (15). The modulator control signal is preprocessed to ensure that all pulses have a minimum duration of t<sub>P\_MIN</sub>, and that the supply voltage of the PA is always high enough to avoid overdrive. For a two-level system this removes short pulses of low supply voltage levels and expands short pulses of high supply voltage levels. For a multilevel system the calculation of the optimum sequence becomes more sophisticated, since each manipulated pulse can affect other levels as well. For the generation of the modulator control signal the threshold level (P<sub>TH</sub>) for each switching level must be defined. In a two-level system there is only a single threshold level which defines whether the lower supply voltage or the higher supply voltage will be switched on. P<sub>TH</sub> must be chosen according to the maximum allowed output power of the PA for the chosen supply voltage, as derived in Chapter 2.1. P<sub>TH</sub> represents the power level in dB above the average power of the test signal. The average power level is chosen as reference, since this is intuitively related to the PA which input power will be adjusted to achieve a specified average output power. When class-G modulation with N supply voltage levels is applied, it is

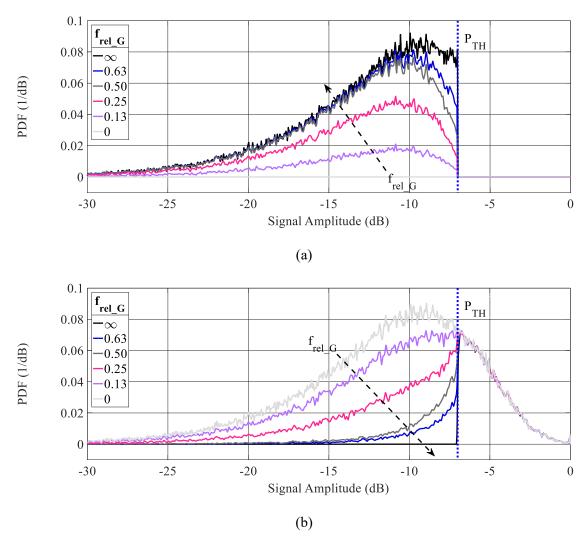

possible to split the test signal PDF into N parts. Therefore, for each power supply a PDF for the amplitudes can be derived. The sum of all PDFs equals the original test signal PDF. This is shown in Fig. 2.34 for a two-level class-G system using the test-signal shown in Fig. 2.32 and Fig. 2.33 and a threshold level  $P_{TH} = 2$  dB. In (a) the PDF of the amplitudes supplied by the lower voltage supply are shown, in (b) the amplitudes for the higher supply voltage. The PDFs are parametrized with the relative switching frequency  $f_{REL\_G}$ . For  $f_{REL\_G} = 0$  the PDF in (b) equals the test signal PDF, while the probability in (a) is zero for all normalized power levels. This represents the case of fixed supply voltage operation, since the class-G modulator is switched constantly to the high supply voltage. For an infinite  $f_{REL\_G}$  the PDF is split vertically at the threshold level  $P_{TH}$ . This represents the ideal case, where the modulator switches without limitation in minimum pulse length. All values in between show the realistic case, where the modulator switching frequency is limited. With decreasing values, it is seen that more and more power levels below the threshold level are handled at the higher supply voltage, resulting in efficiency degradation. In (a) the PDFs for amplitudes above  $P_{TH}$  are all zero since they would cause PA overdrive.

Fig. 2.34: Amplitude probability distribution for a two-level class-G system with different relative modulator switching frequency (f<sub>REL\_G</sub>) constraints for an OFDM modulated signal with 9 dB PAPR. (a) lower supply voltage and (b) higher supply voltage.

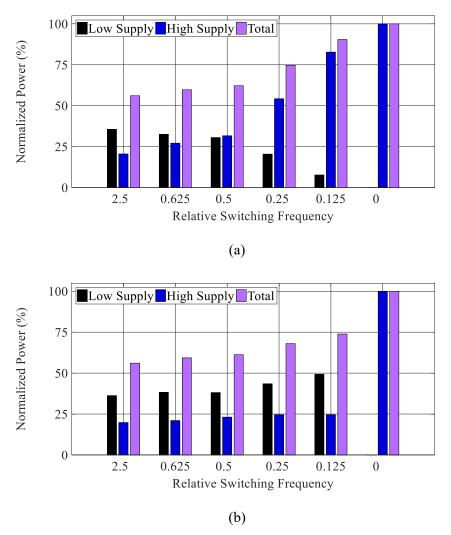

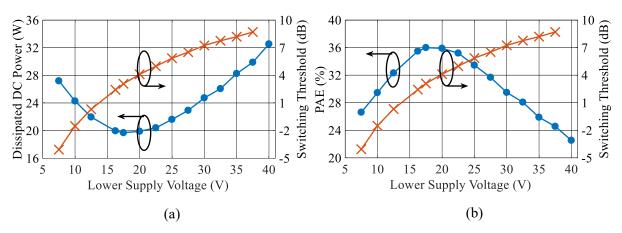

The distribution of the signal amplitudes on the different power supplies has a direct impact on the efficiency of the system. In class-G it is targeted to always use the lowest possible supply voltage level. If the switching speed is constrained, then it occurs that a higher supply voltage level will be active for signal power levels below P<sub>TH</sub>. The distribution of the average power delivered by the power supplies in a two-level system is shown in Fig. 2.35 for the exemplary OFDM test signal. In (a) P<sub>TH</sub> is fixed at 2 dB, while (b) uses an adaptive P<sub>TH</sub> that is adjusted with f<sub>REL\_G</sub>. The power is normalized to the power consumed in the static supply voltage case. The calculation is based on a constant DC current multiplied by the supply voltage level for each power supply which according to the characteristics of the DC current shown in Fig. 2.8, is valid for the class-A biased PA:

$$P_{DC} = I_{DC} \cdot \sum_{n=1}^{N} V_{DC}(n) \cdot p_{on}(n)$$

(17)

The amount of supply voltage levels is defined by N and each level is weighted by the probability that the power supply is active ( $\mathbf{p_{on}}$ ). For class-AB biasing the DC current becomes a function of the supply voltage and must be calculated for each level separately. As already pointed out by the PDF in Fig. 2.34 (b), for  $f_{REL\_G} = 0$  the whole energy is provided by the higher supply level. For  $f_{REL\_G} < 0.625$  the almost optimum case is reached. The influence of  $P_{TH}$  can be seen by the comparison of (a) and (b) in Fig. 2.35. In (a)  $P_{TH}$  is kept constant at 2 dB, which is the optimum value for  $f_{REL\_G} > 1$ . In (b)  $P_{TH}$  is adjusted for each value of  $f_{REL\_G}$  in a range from 2 to 5.3 dB. Especially for low values,  $P_{TH}$  must be increased to achieve optimum efficiency improvement under the constrained  $f_{REL\_G}$  condition. It can be seen, that for low values of  $f_{REL\_G} < 0.5$  the adjustment of  $P_{TH}$  is important. One should note here that an adjustment of  $P_{TH}$  directly involves a change in the discrete supply voltage level, since  $P_{TH}$  sets the required peak power for each supply voltage level. Furthermore, the case (b) shows more constant power consumption for each power supply, dependent on  $f_{REL\_G}$ .

Fig. 2.35: Distribution of the normalized power delivered by the low-voltage and high-voltage supply vs. relative modulator switching frequency for an ideal class-A PA and an OFDM signal. (a)  $P_{TH} = 2 \text{ dB}$ , (b)  $P_{TH}$  optimized for each  $f_{REL G}$  in a range from 2 dB to 5.3 dB.

The distribution of the power consumption shows, that the maximum switching frequency of the class-G modulator can be lower than the IQ modulation bandwidth of the test signal, while the efficiency improvement is still high. For systems with more than two supply voltage levels the analysis becomes more complex since multiple threshold levels must be defined for optimum efficiency. As shown in Table 1 the use of more than two supply voltage levels allows reducing  $f_{REL_G}$  by maintaining constant total power consumption. This constitutes an important advantage for class-G modulation when it comes to extremely broadband modulated systems, where the IQ modulation bandwidth is much higher than the possible supply switching frequency. The simulation results show that, in case of a five-level system, still 50% less dissipated power can be achieved with a maximum switching frequency of only 45% of the IQ modulation bandwidth.

Table 1: Maximum switching frequency requirement as function of the number of supply voltage levels and the associated reduction of dissipated power. The calculations are based on an ideal class-A PA. The OFDM modulated test signal has 9 dB PAPR.

| P <sub>DC_G</sub> /P <sub>DC</sub> | 2-level | 3-level | 4-level | 5-level | 6-level |  |

|------------------------------------|---------|---------|---------|---------|---------|--|

|                                    | frel_g  | frel_G  | frel_G  | frel_G  | frel_g  |  |

| 40%                                |         |         |         | 2.4     | 1.95    |  |

| 45%                                |         |         | 1.20    | 1.00    | 0.95    |  |

| 50%                                |         | 0.95    | 0.55    | 0.45    | 0.45    |  |

| 60%                                | 0.60    | 0.30    | 0.25    | 0.20    | 0.20    |  |

| 70%                                | 0.25    | 0.15    | 0.15    | 0.15    | 0.10    |  |

| : condition not achievable         |         |         |         |         |         |  |

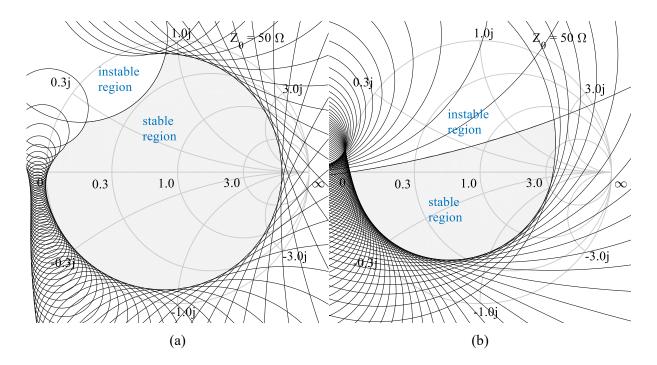

## 2.3 Efficiency enhancement limits of class-G supply modulation

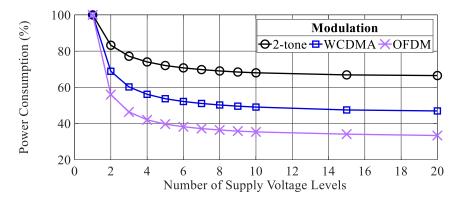

The maximum efficiency enhancement of class-G supply modulation depends on the number of voltage levels used, the maximum switching frequency of the class-G modulator (discussed in Chapter 2.2), and the PA class of operation. For an ideal supply modulator, i.e., a modulator without switching losses and limitations in switching frequency, the best efficiency is achieved when the number of supply voltage levels is going towards infinity. In this case the class-G system converges to a linear envelope tracking system, which is not implementable in practice. Besides that, the higher number of supply voltage levels lowers the modulator efficiency since there are more transistors to be driven and the higher complexity of the modulator increases its power dissipation. At the same time, the efficiency improvement with increasing number of supply voltage levels saturates. Together, this leads to a maximum in efficiency improvement for a certain number of supply voltage levels. This is investigated in the following for different modulation schemes. The analysis considers the amplitude PDF of the test signal, which significantly influences the efficiency improvement, as well as the efficiency of the modulator and the power amplifier. The goal is to analytically find the number of supply voltage levels for a given setup in terms of maximum efficiency. The following analysis uses the supply voltage and power back-off level dependent PA characteristics discussed in Chapter 2.1 for an idealized PA.

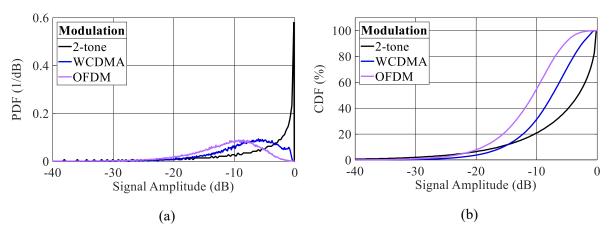

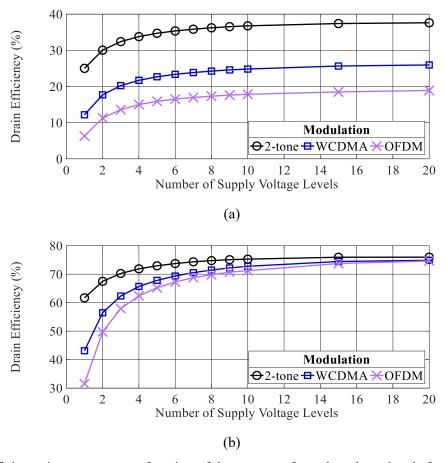

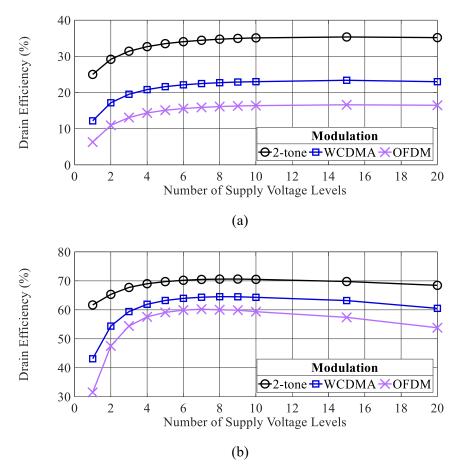

The efficiency improvement as function of the number of supply voltage levels is analyzed for three different signal types: An OFDM modulated signal with 9 dB PAPR, a WCDMA signal with 6 dB PAPR and a two-tone signal with 3 dB PAPR. Fig. 2.36 shows the

signal amplitude (a) PDFs and (b) CDFs. The PDF and CDF functions differ significantly for the analyzed test signals and the comparison of the CDFs reveals that the amplitudes are distributed on a wider range for the OFDM signal than for the WCDMA or the two-tone signal. This effect is cause by the higher PAPR of the OFDM signal. For class-G modulation this has a significant impact on the efficiency improvement that can be achieved.

Fig. 2.36: Amplitude (a) probability distribution function and (b) cumulative distribution function of a two-tone signal with 3 dB PAPR, a WCDMA signal with 6 dB PAPR and an OFDM signal with 9 dB PAPR.

The efficiency improvement in class-G systems is based on the reduction of the dissipated power. With the assumption of a constant DC current consumed by the RF PA, e.g., a class-A PA, the power delivered by the power supply is calculated based on (17). The reduction of the power consumption is plotted in Fig. 2.37 for the three test signals, with supply switching threshold levels optimized for efficiency.

Fig. 2.37: Reduction of power consumption of an ideal class-A PA as a function of the number of discrete supply voltage levels for signals with different PAPR.

It shows that for the signals with higher PAPR the possible power consumption reduction is higher. Besides that, the relative improvements with more supply voltage levels are higher compared to signals with low PAPR. This effect is caused by the fact, that for the case

without supply modulation the PA efficiency is higher for the signal with lower PAPR, since the required power back-off level is lower. Translating the results from Fig. 2.37 into the drain efficiency η<sub>D</sub> clarifies the situation, which is shown in Fig. 2.38 for the ideal class-A (a) and class-B (b) PA. For the class-A PA the efficiency improvement measured in percentage-points is not related to the PAPR of the signal, since the maximum efficiency achieved with supply modulation decreases linearly with the average output power (Fig. 2.7). For the class-B biased PA it can be stated, that signals with higher PAPR allow more efficiency improvement than signals with lower PAPR, since the efficiency without supply modulation is lower for a signal with higher PAPR and the maximum efficiency achieved with supply modulation is independent of the average output power. More precisely, the higher PAPR requires an increased number of supply voltage levels. This can be verified by the comparison of the efficiency improvement shown in Fig. 2.38.

Fig. 2.38: Efficiency improvement as function of the amount of supply voltage levels for different modulation formats with different PAPR, for (a) a class-A biased and (b) a class-B biased PA.

In Fig. 2.38 the modulator is assumed to be 100% efficient. In practice, the efficiency of a class-G modulator is very high but not ideal. Depending on the topology, static and dynamic losses reduce the efficiency of a modulator [28]. The losses can be separated into losses in the

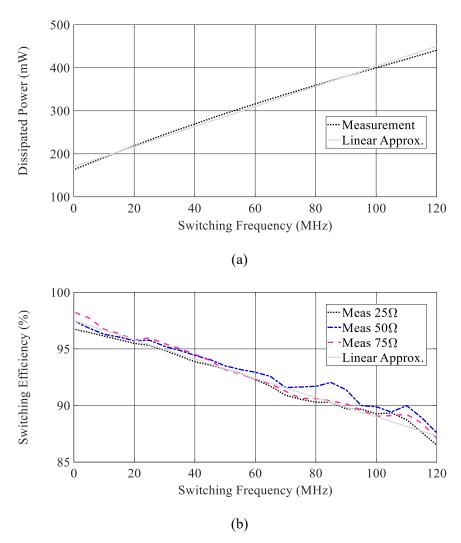

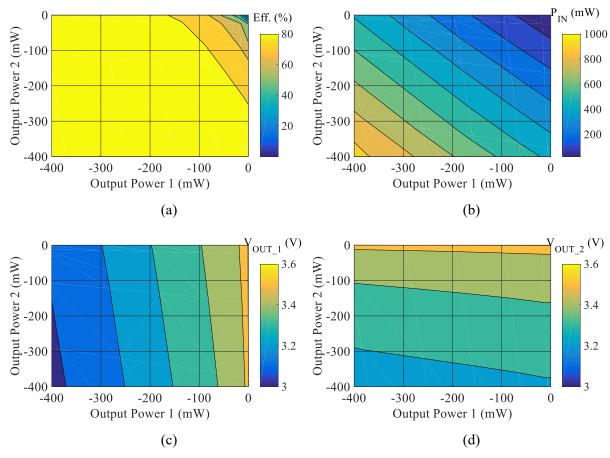

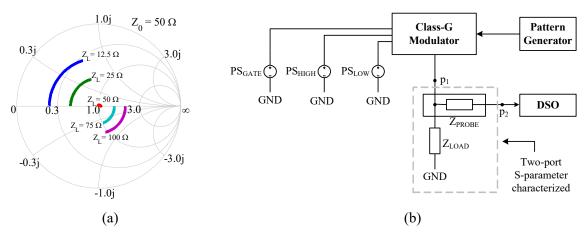

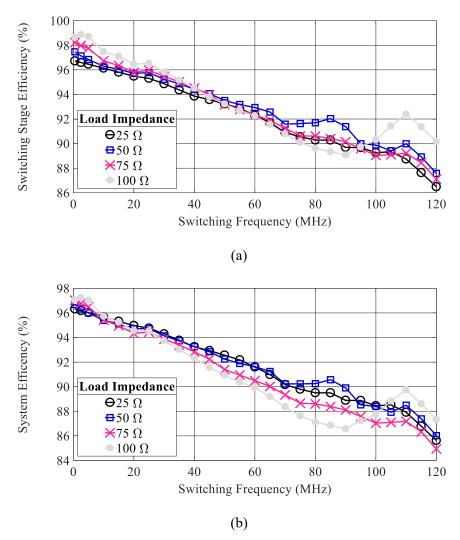

transistor gate driver circuit, which in [28] are independent of the switched supply voltages and load impedances, i.e., the output power of the modulator, and the switching stage losses which scale with output power. For low output power levels, it is important to minimize the losses in the gate driver circuit. Chapter 4.1.1 gives more information on the gate drivers and different implementations. For the following analysis the modulator losses are set to depend on the switching frequency and the number of supply voltage levels. The number of supply voltage levels influences the static driver losses in the modulator. The switching stage losses are counted only once and are calculated based on the average switching frequency of the class-G modulator control signal. The following analysis is only a simplified description of the losses that occur in a real system. It would become significantly more complex when taking into account all factors, e.g., the changing load impedance and the impact on the switching stage efficiency. Besides the reduction in complexity the results are more general and less hardware-specific. The dataset used for extraction of the modulator losses is shown in Fig. 2.39 for (a) the gate driver losses and (b) the switching stage losses which are based on measurements of a class-G supply modulator. The gate driver losses show an almost linear increase with the switching frequency. Linearly approximated they consist of a static dissipated power of (N-1)·170 mW, i.e., 170 mW for each transistor switch in the modulator, and dynamic losses of 2.3 mW/MHz. The switching stage efficiency is shown for different load impedances. It also decreases almost linearly with the switching frequency. For the linear approximation a static efficiency of 97.5 % and a decrease of -8.5 percentage-points per 100 MHz are assumed.

Fig. 2.39: Power dissipation in (a) the gate driver and (b) efficiency of the switching stage as function of the supply switching frequency for a two-level class-G modulator [28]. The supply voltage is switched with 50% duty-cycle between 20 V and 40 V and different load impedances.

The modulation bandwidth does not influence the efficiency of the system in the analysis with an ideal supply modulator. With the realistic modulator model, the modulation bandwidth must be considered as well, since the average supply switching frequency increases linear with the modulation bandwidth. The IQ modulation bandwidth of the three test signals is set to 5 MHz. The efficiency enhancement including modulator losses is shown in Fig. 2.40 for an ideal PA with a peak output power of 60 W. The average output power depends on the signal PAPR, e.g., 30 W for the 2-tone, 15 W for the WCDMA and 7.5 W for the OFDM signal. Comparing the results for the simulations with and without modulator losses one finds that (a) the class-A PA does not show efficiency improvement for N > 10 and (b) that for the class-B PA the efficiency is decreased significantly for N > 7. This is mainly

caused by the static losses of the class-G modulator, which become more dominant if the overall power consumption of the PA is low. As a result, the drain efficiency decreases for the high PAPR OFDM signal already for configurations with more than seven supply voltage levels, peaking at only 60%. In this case the class-G modulator should be optimized to consume the least possible quiescent power.

Fig. 2.40: Efficiency improvement as function of the amount of supply voltage levels for different modulation formats with different PAPR including modulator losses, for (a) a class-A biased and (b) a class-B biased PA with 60 W peak output power.

## 2.4 Power amplifier linearity under class-G supply modulation

For linear amplification, the PA must provide a constant magnitude and phase of the complex valued gain/transmission coefficient (G) over the full modulation band and output power range. Any variation results in a distorted PA output signal. In the previous chapter it is observed that the magnitude of the gain depends on the PA class and power back-off, as shown in Fig. 2.10. Based on the theory of linear and reduced conduction angle PAs, the supply voltage modulation does not further influence the gain of the PA. This emphasizes the choice of the PA operating point in class class-A, class-B or deep class-AB only.

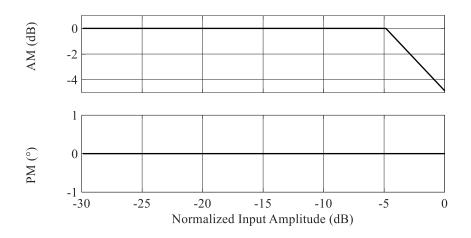

In a practical PA implementation based on GaN technology, it is observed that  $\underline{G}$  diverges from the ideal theory and shows a supply voltage dependency for its magnitude and phase [20], [21]. Furthermore, if the PA is driven into saturation, the magnitude of the transducer power gain compresses and a phase shift between input and output signal is observed. With class-G supply modulation, as with any other supply modulation, both mechanisms introduce distortions to the output signal and will be addressed in the following.

#### 2.4.1 Baseband signal distortions caused by gain and phase variations

For the evaluation of the linearity  $\underline{x}_{BB}(t)$  is defined as the IQ-modulated baseband signal, consisting of the in-phase component  $x_{I}(t)$  and the quadrature component  $x_{Q}(t)$ :

$$x_{BB}(t) = x_{I}(t) + j \cdot x_{Q}(t)$$

(18)

The measured baseband signal at the PA output is defined as  $\underline{y}_{BB}(t)$ . Like the input signal it consists of an in-phase and a quadrature component,  $y_I(t)$  and  $y_Q(t)$ , respectively. For a system without memory, the signal  $\underline{y}_{BB}(t)$  is derived according to (19) with  $\underline{G}(|\underline{x}_{BB}(t)|)$  as nonlinear function.

$$\underline{y_{BB}}(t) = y_{I}(t) + j \cdot y_{Q}(t)$$

$$= \underline{G}(|\underline{x_{BB}}(t)|) \cdot \underline{x_{BB}}(t), \quad \underline{G} : \mathbb{R} \to \mathbb{C}, \quad x \mapsto y$$

(19)

The magnitude of  $\underline{G}$  affects the in-phase and quadrature component equally, but the phase variation causes IQ impairments which can be interpreted as an input power dependent rotation of the constellation diagram.

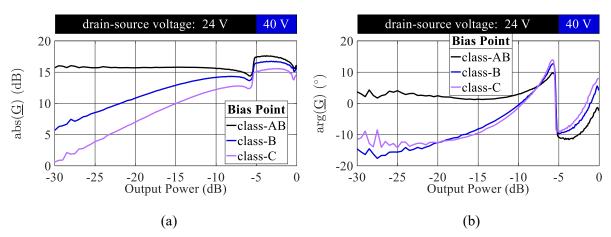

#### 2.4.2 Impact of class-G supply modulation on the transducer gain

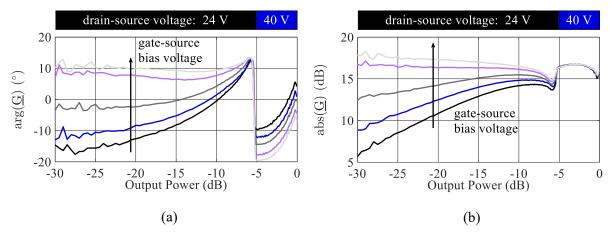

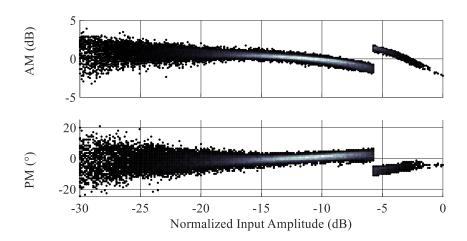

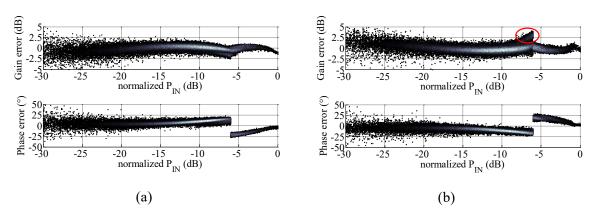

For the simplified quasistatic model used in the previous chapter, the phase variation of the gain factor is not addressed, since it depends on reactive components which are not modelled. Dynamic measurements show that also the phase is changing with the supply voltage and output power. Therefore, it has a significant contribution to the overall nonlinear behavior of the PA. In Fig. 2.41  $\underline{G}$  extracted from modulated measurements of a GaN-based PA under dynamic class-G supply modulated operation is shown vs. normalized output power for three different bias points. Memory effects have been removed by averaging. For the magnitude and phase of  $\underline{G}$  a sharp discontinuity is observed at a level of -6 dB output power,

where the threshold level for switching of the supply voltage between the lower level of 24 V and the higher level of 40 V is located.

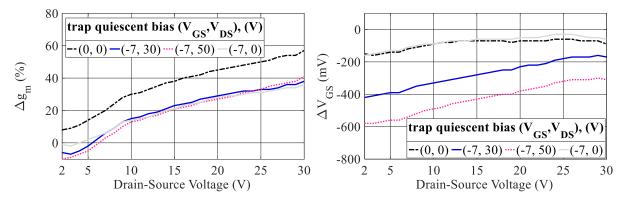

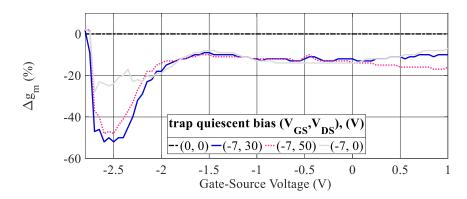

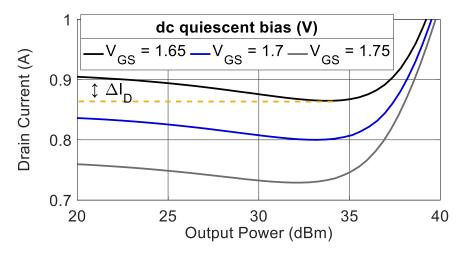

Furthermore, it is observed in Fig. 2.41 (a) that the magnitude of  $\underline{G}$  diverges from the theoretically derived value in the power back-off region. The behavior is equivalent to a reduction of the conduction angle, i.e., the magnitude of the gain factor for the class-B bias point decreases with reduced output power and matches the expected gain for class-C. Thereby, the magnitude of  $\underline{G}$  for the lower supply voltage level is reduced in general. The quasi-static simulations (Chapter 2.1.3), where the I-V knee region is considered, show only a minor reduction of the gain with the supply voltage in the range from 5 V to 40 V. Therefore, the static I-V knee cannot be the root cause of this phenomenon. An explanation for the observed reduced conduction angle is found by taking the existence of trapping effects in the GaN-HEMT into account. The trapping effects are discussed later in Chapter 3.2.

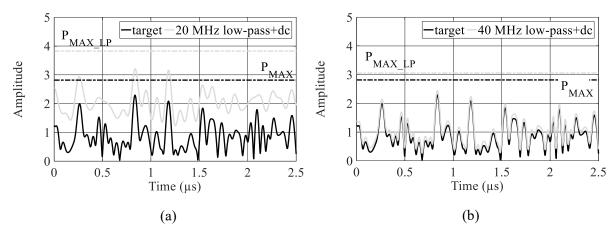

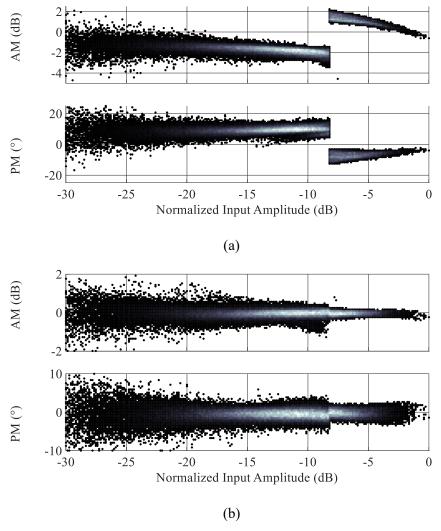

Fig. 2.41: (a) gain and (b) phase variation as function of the output power for different bias points and two-level class-G supply modulation.

For further investigation of the conduction angle the bias point is swept for the lower supply voltage level and output powers below -6 dB as shown in Fig. 2.42. A dynamic gate-bias modulation is applied synchronously with the class-G supply modulation. The gate-bias at the supply voltage level of 40 V is kept constant at the class-B condition. With increased gate-source bias voltage it is seen that the flatness of  $\underline{G}$  is improved for magnitude and phase in the power back-off region below -6 dB. The estimated behavior for the magnitude of  $\underline{G}$  of a class-B biased PA can be achieved by increasing the gate-bias voltage for the 24 V region. The discontinuity of  $\underline{G}$  at the switching threshold is reduced for the magnitude, but the phase increases with the gate-source bias voltage from 20° to 30°.

Fig. 2.42: (a) gain and (b) phase variation as a function of output power for different bias points and two-level class-G supply modulation with additional gate-bias modulation for the lower supply voltage level.

## 2.4.3 Quantification of nonlinear distortions in class-G supply modulated PAs

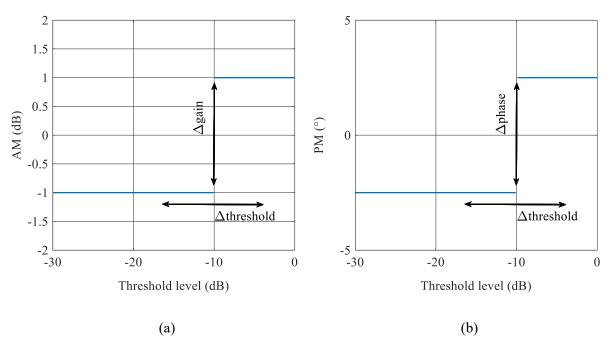

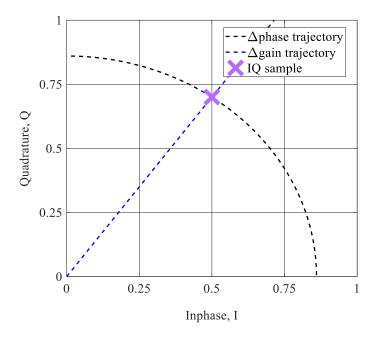

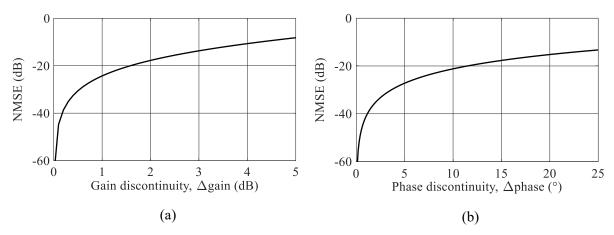

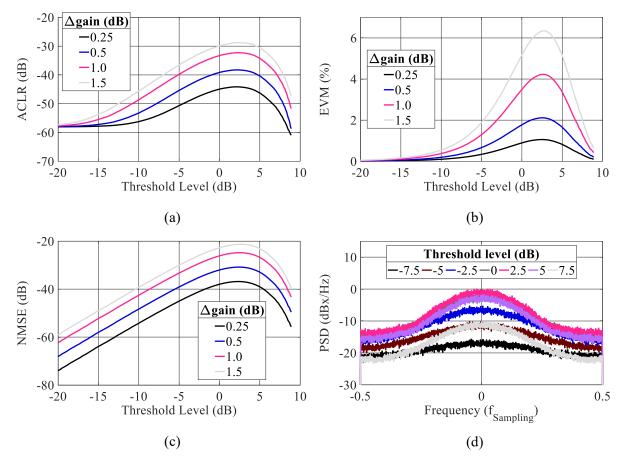

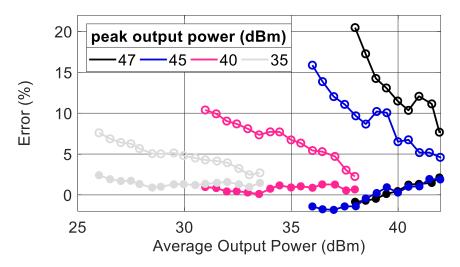

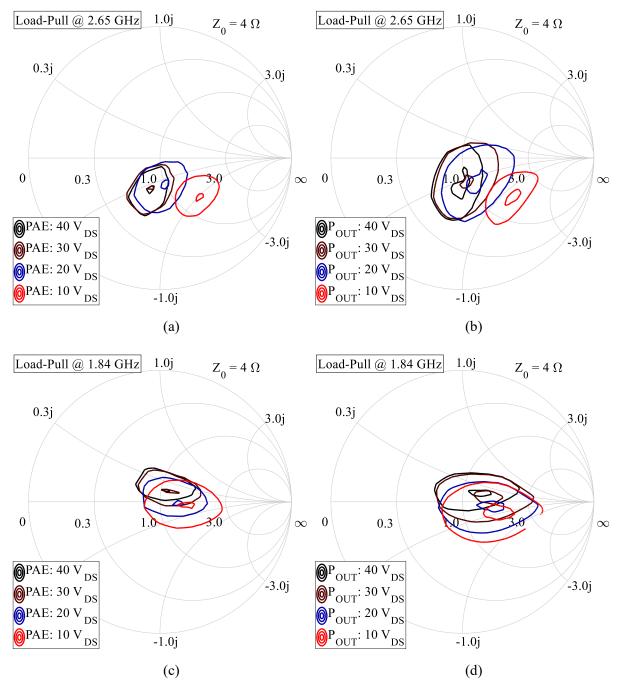

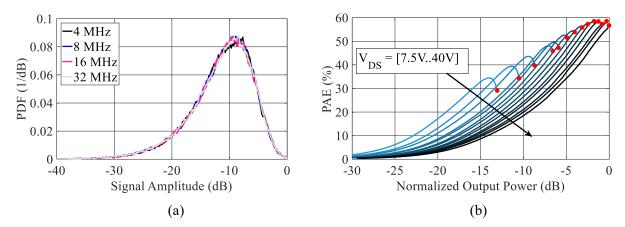

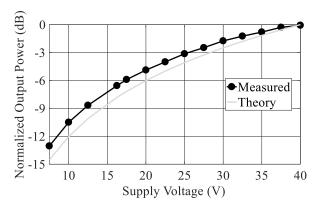

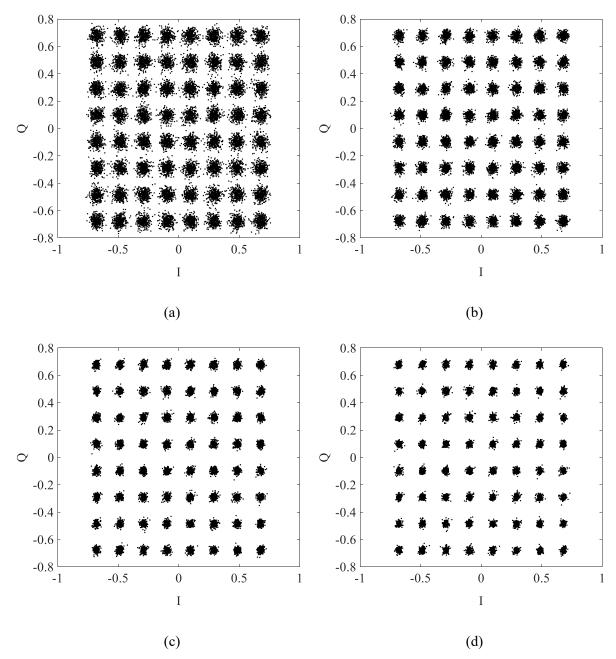

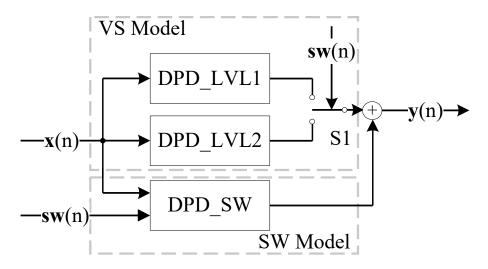

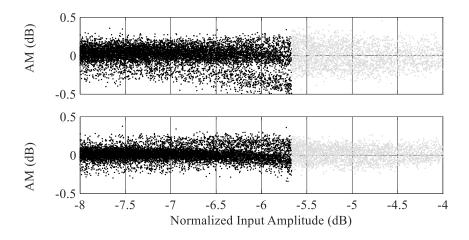

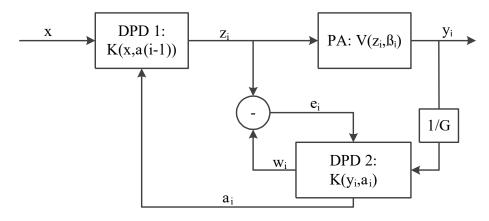

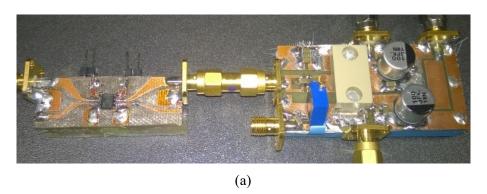

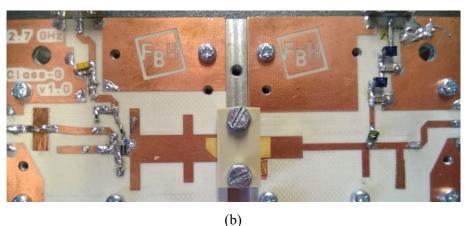

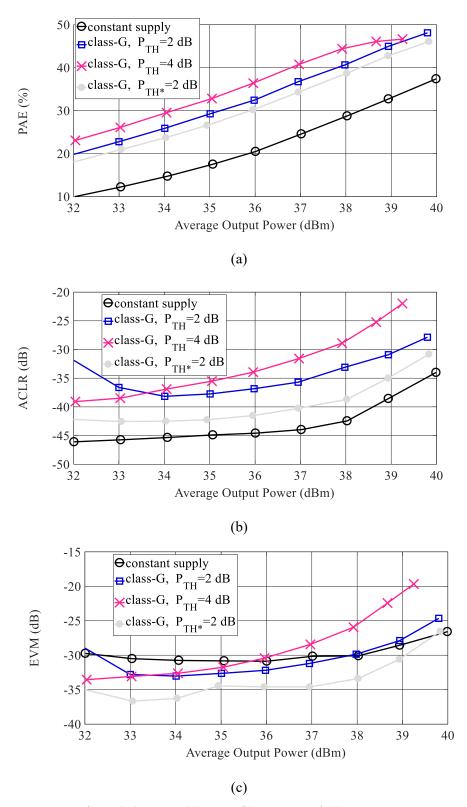

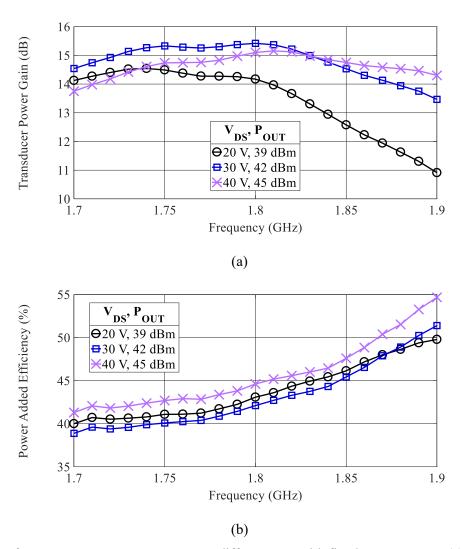

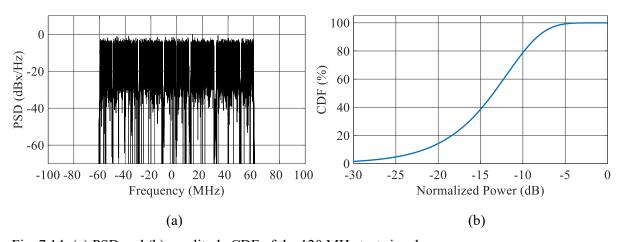

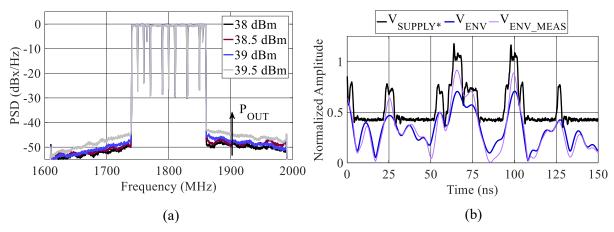

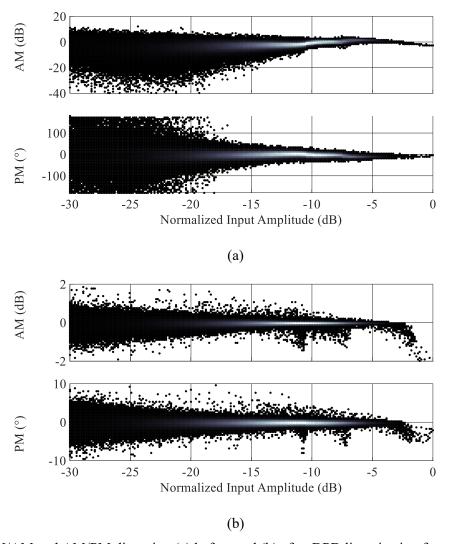

In the previous subsection it was shown that the magnitude and phase of the transducer power gain varies with the supply voltage levels and the output power. The impact of the magnitude and phase variations at the discontinuity and at different supply voltage levels will be investigated in the following for systems with fixed gate-bias level and for the case of synchronous gate-bias modulation.