## Intermodulation Distortion in GaN HEMT

vorgelegt von M.Sc. Eng. Ibrahim Khalil aus Barisal, Bangladesch

von der Fakultät IV-Elektrotechnik und Informatik der Technischen Universität Berlin zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften Dr.-Ing.

genehmigte Dissertation

#### Promotionsausschuss:

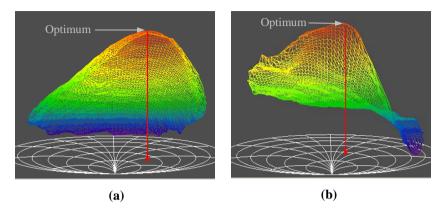

Vorsitzender: Prof. Dr.-Ing. Klaus Petermann Berichter: Prof. Dr.-Ing. habil. W. Heinrich

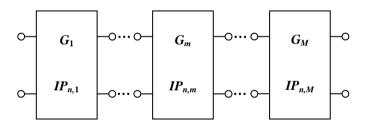

Berichter: Prof. Dr.-Ing. Dr.-Ing habil. R. Weigel

Tag der wissenschaftlichen Aussprache: 17.07.2009

Berlin 2009

D 83

# Acknowledgments

This work has been done during my scientific activities at Ferdinand-Braun-Institut für Höchstfrequenztechnik (FBH) in Berlin, Germany. I had a wonderful time during my stay in Berlin not only in professional life but also private. I would like to take this opportunity to acknowledge and express my heartfelt gratitude to some who have made it possible for me to complete this thesis.

My supervisor and mentor Prof. Dr.-Ing. Wolfgang Heinrich, for giving me the opportunity to work in his group and supervising this thesis. His incessant support with sound knowledge and beautiful mind brought this work to a success.

Prof. Dr. Günther Tränkle, our institute director, for his valuable suggestions and organization support.

Dr. Hans-Joachim Würfl, Head of Business Area GaN-Electronics, for his constant support and ideas in process and technology.

Especial thanks goes to Prof. Dr. Robert Weigel for his kind decision to review this thesis in his busy schedule.

I must also thank Mr. Erhan Ersoy for helping me developing control software for IM3 measurement setup during his internship at FBH, Mr. Bahat-Treidel Eldad who is not just a colleague, but his cooperation and his extravagant job regarding physical simulations had been a great source of useful data. Also Nidhi Chaturvedi, who helped explaining the process technology and most of the information regarding process are cited from her PhD thesis.

VI Acknowledgments

Ralf Doerner, Jens Schmidt and Steffen Schulz had been always helpful in measurement lab. Dr. Bernd Janke helped me doing layouts even in his busy schedule. Dr. Frank Schnieder helped regarding large signal model. I must also thank Dr. Franz-Josef Schmückle, Dr. Matthias Rudolph and Dr. Chafik Meliani for their valuable suggestions and help. Armin Liero, Mark Neumann and Hai Bang Nguyen helped regarding transistor mounting. Head of the microwave measurement group Dr. Roland Gesche was always a source of new ideas. I would like to give special thanks to the former head of microwave measurement group, Dr. Peter Heymann who had been always an endless source of knowledge in the field of microwave measurement technique.

I am thankful to all my colleagues at FBH from the departments of microwave technique, process technology and material technology who have directly or indirectly contributed to the development of this work.

Dr. Olof Bengtsson, for his enthusiasm to proof read my work, I thank him.

I would like to acknowledge all project partners and funding agencies especially German ministry of science and technology (BMBF), European space agency (ESA) and TESAT Spacecom. I specially thank Prof. Dr. Michael Uren and his group from QinetiQ, UK, for providing data of IP3 simulation.

I am thankful to my family, especially to my parents, whose constant encouragement keeps me always motivated during my difficulties, without them I could not be me. Finally, I am thanking to all my relatives and friends for constant supports and advices.

## Abstract

This work treats intermodulation distortion performance GaN-HEMT high-power transistors. A detailed study on the physical parameters influencing third-order intermodulation distortions is carried out, based on the large-signal model and on physical device simulation. Devices are characterized in terms of linearity by setting up a sophisticated measurement system. Among others, an electronic fuse is used at the drain side to avoid catastrophic failure during measurement. The bias-dependent transconductance characteristic is identified as the dominating source for intermodulation distortion in GaN HEMTs, while drain-source capacitance and access resistances have only minor influence. The corresponding physical parameters transconductance behavior governing the are determined optimized structures for high linearity are proposed. Besides characterization and analysis of conventional designs, a novel device architecture for very high linearity is presented. Finally, performance of GaN HEMTs within a hybrid amplifier configuration is shown and the combination of high power, high linearity, and low-noise characteristics is highlighted.

VIII Kurzfassung

# Kurzfassung

Diese Arbeit behandelt Verhalten das von GaN-HEMT-Hochleistungs-Transistoren in bezug auf Intermodulationsverzerrungen. Die Grundlage bildet eine detaillierte Untersuchung des Einflusses der verschiedenen physikalischen Parameter auf die Intermodulationsprodukte 3. Ordnung, die auf dem Großsignalmodell Bauelementesimulationen und physikalischen beruht Zur Charakterisierung der Linearität der Transistoren wurde ein komplexes aufgebaut, bei dem der drainseitigen Messsystem u.a. an Versorgungsquelle eine elektronische Sicherung implementiert ist, die die Zerstörung des Messobjekts bei kritischen Betriebszuständen Als Ursache verhindert. dominierende der Intermodulationsverzerrungen in GaN-HEMTs wurde die arbeitspunktabhängige Charakteristik der Steilheit identifiziert, währenddessen Drain-Source-Kapazität und Kontaktwiderstände nur geringen Einfluss haben. Die physikalischen Parameter, die das Steilheitsverhalten bestimmen, werden ermittelt und optimierte Strukturen for hohe Linearität vorgeschlagen. Neben der Charakterisierung und der Analyse von konventionellen Designs wird eine neuartige Baulelementearchitektur für sehr hohe Linearität vorgestellt. Abschließend wird das Potential von GaN-HEMTs in einer hybriden Verstärkerstruktur gezeigt und die resultierende Kombination aus hoher Leistung, hoher Linearität und niedriger Rauschzahl demonstriert.

<u>Contents</u> <u>IX</u>

# **Contents**

| Acknowledgments<br>Abstract                                                                                                                                                                                                  | v<br>vii                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| CHAPTER 1                                                                                                                                                                                                                    | 1                                |

| Introduction                                                                                                                                                                                                                 |                                  |

| <ul><li>1.1 Overview</li><li>1.2 Organization of the thesis</li></ul>                                                                                                                                                        | 1<br>5                           |

| CHAPTER 2                                                                                                                                                                                                                    | 9                                |

| Nonlinear distortions in active devices                                                                                                                                                                                      | 9                                |

| <ul><li>2.1 Linearity figure of merit for active devices</li><li>2.2 Distortion in active devices</li><li>2.3 IMD characterization of devices</li><li>2.4 Comparison of devices in terms of linearity</li></ul>              | 9<br>10<br>15<br>20              |

| CHAPTER 3                                                                                                                                                                                                                    | 23                               |

| GaN HEMT                                                                                                                                                                                                                     | 23                               |

| <ul> <li>3.1 Basic HEMT operation</li> <li>3.2 GaN material properties</li> <li>3.3 GaN HEMTdevice fabrication</li> <li>3.3.1 Substrate</li> <li>3.3.2 Basic GaN process technology at FBH</li> <li>3.4 Packaging</li> </ul> | 15<br>23<br>24<br>24<br>25<br>28 |

<u>Contents</u> X

| CHAPTER 4                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 31                                                       |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| Measurement and characterization                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                          |

| 4.1 Intermodulation test setup 4.1.1 The input amplifier 4.1.2 Bias-T                                                                                                                                                                                                                                                                                                                                                                                           | 31<br>35                                                 |

| 4.1.2 Dias-1 4.2 Power calibration 4.3 Fixture 4.4 Measurements 4.5 Measurement safety 4.5.1 Drain safety using e-fuse 4.5.2 Self pinching bias-T to avoid gate turn-on and spurious oscillation                                                                                                                                                                                                                                                                | 37<br>37<br>39<br>41<br>42<br>47                         |

| CHAPTER 5                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57                                                       |

| IMD sources in GaN HEMT                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                          |

| <ul> <li>5.1 Sensitivity analysis based on large signal model</li> <li>5.2 Measurement based analysis</li> <li>5.2.1 SiN undoped cap</li> <li>5.2.2 GaN cap doped with silicon</li> <li>5.3.3 AlGaN barrier height</li> <li>5.3.4 T-Gate and embedded gate</li> <li>5.3.5 Field plate variation</li> <li>5.3.6 Drain source capacitance variation</li> <li>5.3 Access resistance related nonlinearity</li> <li>5.31 Influence of gate source spacing</li> </ul> | 57<br>69<br>69<br>71<br>73<br>73<br>75<br>77<br>79<br>84 |

| CHAPTER 6                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 92                                                       |

| Device Level Linearity of GaN HEMT                                                                                                                                                                                                                                                                                                                                                                                                                              | 87                                                       |

| 6.1 Linking systematic and sensitivity analyses to physical simulation                                                                                                                                                                                                                                                                                                                                                                                          | 87                                                       |

| <ul><li>6.2 Influence of barrier thickness</li><li>6.3.1 Theory and simulation</li><li>6.3.2 Fabrication, measurements &amp; discussion</li><li>6.3 Enhancing overall linearity of a large device</li></ul>                                                                                                                                                                                                                                                     | 92<br>92<br>95<br>99                                     |

| 6.4 Enhancing linearity at low back-off regime 6.4.1 Simulation and analysis                                                                                                                                                                                                                                                                                                                                                                                    | 103<br>104                                               |

<u>Contents</u> XI

| CHAPTER 7                                                                                                                                                                                                                          | 109                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| GaN HEMT as Linear Amplifier                                                                                                                                                                                                       |                                        |

| <ul> <li>7.1 Class-A, B and AB</li> <li>7.2 GaN HEMT based linear PA design</li> <li>7.3 Performance of GaN HEMT</li> <li>7.3.1 Power performance</li> <li>7.3.2 Noise performance</li> <li>7.3.3 Linearity performance</li> </ul> | 109<br>110<br>112<br>113<br>114<br>117 |

| CONCLUSIONS                                                                                                                                                                                                                        | 119                                    |

| References List of acronyms Appendix-I Appendix-II Publication and patent                                                                                                                                                          | 125<br>131<br>133<br>135<br>137        |

## 1 Introduction

Modern wireless communication systems are improving day-by-day and offering new services such as video telephony, internet access, high quality audio, video transfer etc. All these applications require high-speed data transfer. To provide services to the increasing numbers of customers and to meet the demand of high-speed transmission, mobile industry keeps on migrating one generation to other. Transferring high data rate means high frequency carrier, higher transmission bandwidth, and complex modulation techniques.

This increasing service quality demands low cost, compact, wideband, and efficient and linear power amplifiers. In addition to mobile phone services there are many other applications where a linear amplifier is required. Some of these applications are satellite communication, navigation system, anti-collision radar, wi-fi and many other wireless data communication modules.

In table 1, frequency allocation and approximated power range of commonly used wireless devices are shown.

In first-generation cellular standards such as advanced mobile phone system (AMPS), an analogue modulation scheme was used. As this modulation had constant envelope, no significant linearity requirements were necessary for handset PA. The efficiency of the system was very low as well. However, for base-station, still there were some linearity requirements. In second-generation systems i.e, the global system for mobile communications (GSM), cell capacity was increased to a great extent by using digital modulation technique and sophisticated digital signal processing (DSP). There were two types of

2 1 Introduction

multiple access techniques implemented namely time division multiple access (TDMA) and code division multiple access (CDMA). The TDMA-based system has become the most widely used mobile system. A constant envelope signal was still used, but, some linearity requirements were needed due to power ramping for a transmitter time slot. This reduced the efficiency slightly, but since the PA is on for only 1/8 of the time, the importance of PA efficiency over the total operating time was reduced to a significant degree and very good operating times were achieved in GSM handsets. However, this does not hold for base stations.

In third-generation systems such as wideband code-division multiple access (WCDMA) or universal mobile telephone

TABLE 1.1

STANDARDS & ALLOCATED RF FREQUENCY BANDS

| Standard          | Freq. Band<br>(GHz)            | Average<br>Transmitted Power |  |

|-------------------|--------------------------------|------------------------------|--|

| GSM-900/1800 (DL) | 0.935 - 0.960<br>1.805 - 1.880 | 10-20 Watts                  |  |

| UMTS (DL)         | 2.110 - 2.170                  | 5-10 Watts                   |  |

| WLAN 802.11a      | 5.725 - 5.850                  | 50-250 mW                    |  |

| Wi-Fi             | 2.400 - 2.484                  | 1 Watt                       |  |

| Bluetooth         | 2.40 - 2.484                   | 0-20 dBm                     |  |

| UWB               | 3.10 - 10.60                   | -40dBm/MHz                   |  |

| Satellite         | 8 - 10                         | -                            |  |

| Automotive Radar  | 76-77                          | 6-20 dBm                     |  |

Transmitted power are typical values, which may differ from application to application.

system (UMTS), operating times comparable to those available in second-generation systems present a serious challenge, and current applications are not capable of achieving these. From a PA point of view, the difficulties in modern telecommunications systems arise from spectral efficiency.

With rapidly increasing numbers of users and their demand of higher data transmission rate, the available frequency spectrum is heavily crowded. To cut the cost in expensive frequency spectrum, one must transmit the maximum amount of data using the minimum bandwidth. This can be achieved using complex and sophisticated modulation techniques. For example, UMTS utilizes a bandwidthefficient modulation, usually Quadrature Phase Shift Keying (QPSK), and therefore is capable of providing higher bit rates per unit bandwidth. Typically UMTS systems are expected to deliver peak data rates of up to 2.4 Mbps with average data rates of 300 kbps. Unfortunately these kind of modulation schemes lead to wide, dynamic signals that require highly linear amplification. As a result, signal distortion must be minimized in order not to interfere neighboring channels and to use the frequency spectrum efficiently. Therefore, linearity of RF power amplifiers becomes one of the most and probably the most important parameter to be considered for modern communication.

PA linearity is normally achieved with high back-off or external linearizer circuits. High back-off means less efficiency and oversized amplifiers, which results in high production cost and environmental disaster in long run due to lower efficiency. External linearizer means extra effort and complex circuits, which are costly and cumbersome. Moreover, increasing the modulation scheme complexity and

4 1 Introduction

bandwidth to enable fast data transfer often renders linearization schemes ineffective.

On the other hand, increasing demand from wireless industry made the semiconductor industry to improve the technology and find new materials. The first amplifying transistor based on semiconductor was invented by the team of William B. Schockley in 1947 at Bell Lab and later shared his Nobel Prize with his team members John Bardeen and Walter H. Brattain [1][2]. The invention of the first transistor based on germanium became the basis for the electronic age. Since then, semiconductor industry kept on growing. Silicon based devices were very successful and mostly used in past decades. Silicon has low electron mobility therefore it was not easy to make high frequency devices with this technology. GaAs (Gallium Arsenide) came with a great hope for high frequency application as it has high electron mobility. InP (Indium Phosphide) technology was also introduced for very high frequency applications. These materials are often called compound (III-V) semiconductor as they are compound of two material from 3<sup>rd</sup> and 5<sup>th</sup> column of periodic table. GaN (Gallium Nitride) is a new material in this III-V community. It has potential to become the most important semiconductor material since silicon. Although GaN was first introduced as a material for blue laser, recently high frequency and high power RF applications found GaN to be a very promising material. It has large band-gap, very high sheet carrier density and high mobility. Taking advantage of these combinations GaN offers high breakdown voltage, high current density and robustness. Besides its problems with defects and traps it has been proven by this time one of the best material capable of delivering highest density of power up to mm-wave [3][4]. This technology has a growing interest in RF community.

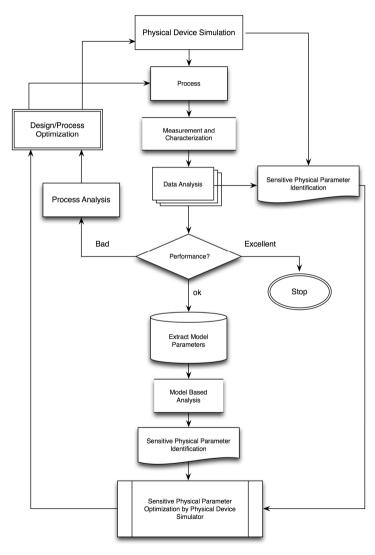

At the Ferdinand-Braun-Institut, power HEMTs and MMICs are developed based on GaN technology. As a new material, this technology is undergoing its evolution era. The technology is not yet commercialized in mass scale. As modern broadband communication concerned, it is very important to characterize the linearity of these amplifying devices. The purpose of this thesis was to characterize these devices in terms of linearity, specifically intermodulation distortion. In more detail, it covers the following aspects.

- Development of a reliable measurement system to characterize high power GaN HEMTs in terms of linearity.

- A thorough investigation to identify the causes of intermodulation distortions in GaN HEMTs. This includes simulation, systematic comparison and analysis of measurement data.

- To propose methods for linearity improvement at the device level.

- Linear amplifier design with GaN HEMT technology.

### 1.1 Organization of the thesis

This thesis consists of seven chapters and conclusions. It is comprised of three main parts. The first part is the introductory part that includes general understanding of distortion phenomenon and characterization methods. It also includes a general description of GaN HEMT technology. The second and core part is about the systematic analysis of devices and improvement of device architecture in terms of linearity. The concluding part presents performance of GaN HEMT device within an amplifier. In the following the organization of the chapters is given.

6 1 Introduction

Chapter 1 – Introduction, starts with the motivation and the goal of this thesis along with some general information to understand the necessity of this thesis. General information includes different wireless standards and an introductory overview on different semiconductor technologies to realize wireless communication circuitry. A comprehensive guideline and understanding the organization of the thesis is the main focus of this chapter.

**Chapter 2,** Nonlinear Distortions, revises the basics of distortion mechanism in active amplifying devices. Nonlinear characterization methods and commonly used figure of merits in terms of linearity are presented here.

In **Chapter 3**, *GaN HEMT*, we have briefly introduced the AlGaN/GaN HEMT technology. This technology is a relatively new technology in semiconductor industry. Ferdinand-Braun-Institut (FBH) has its own process line to fabricate GaN HEMTs and MMIC based on this technology.

**Chapter 4**, Measurement and Characterization, presents the measurement system for GaN HEMT characterization used for this work. As the characterized GaN devices are high power devices, it was necessary to develop a reliable measurement system which is capable of handling such high power and perform accurate measurements.

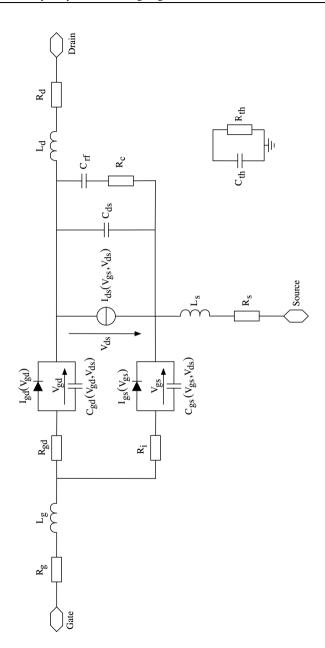

In **Chapter 5**, IMD *Sources in GaN HEMT*, we examine device level distortion sources in GaN HEMTs. Analysis based on large-signal model and measurement data are presented in this chapter. A model-based analysis captures the mechanism of nonlinear distortions in GaN HEMT. This chapter also includes a measurement based analysis where a number of devices with changed physical parameters were compared.

Chapter 6 – Enhancing Device Level Linearity addresses the physical parameter optimization and innovative methods to improve GaN HEMT linearity at the device level. It was shown that optimized physical parameter and operating condition is the key of linearity enhancement. This chapter also presents an innovative device architecture for highly linear devices.

Performance of GaN HEMTs within an amplifier is presented in **Chapter 7** – *GaN HEMT as Linear Amplifier*. This chapter also includes some concepts and considerations for designing practical linear amplifiers based on GaN HEMT.

Finally, - Conclusion, concludes the thesis with a comprehensive summary and outlook.

## 2 Nonlinear distortions

In a perfect world, communication would be transfer of information across a given medium without any loss or interference to other users. In reality, the communication channels add unwanted signals to the desired information. These signals include random noise and distortion. Random noise is not correlated with the information, whereas distortion generation is a strong function of the information carrying signal [5]. Distortion can be generated from any part of the communication subsystem e.g., circuit components or from the medium. These subsystems include antennas, amplifiers, mixers, digital-to-analog and analog-to-digital converters. The amplifying device is the heart of electrical communication system. These active devices or amplifiers are usually quasi nonlinear to strongly nonlinear. Distortion generated as a result of the nonlinear characteristics of active devices is the scope of this chapter.

This chapter reviews the relevant results and theories related to the distortions in amplifying devices, especially HEMTs, which were important in the development of this thesis.

## 2.1 Linearity figure of merit for active devices

Usually the following terms are commonly used as figure of merit for linearity of amplifiers or amplifying devices.

- Gain compression/ $P_{\mbox{\tiny -1}}$  dB point

- Harmonic distortion

- Phase distortion

- Intermodulation distortion

- IP3 /TOI (Third Order Intercept Point).

- ACPR (Adjacent Channel Power Ratio)/ Spectral regrowth.

- EVM (Error Vector Magnitude).

Actually, they are related to each other and will be clarified in the following sections.

### 2.2 Distortions in amplifying devices

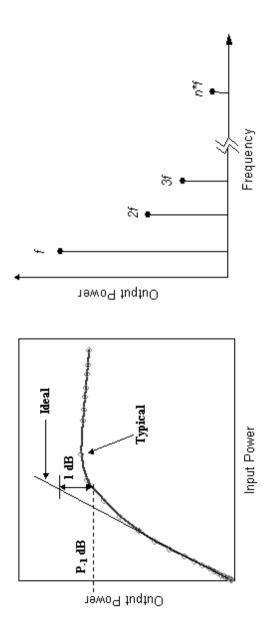

Active devices such as transistors are usually used to amplify electrical signal. In a perfect linear system these devices would amplify the signal with a constant gain up to infinite input power. In reality these devices have a transfer characteristic as shown in fig. 2.1 in comparison to perfect linear amplifier.

As pointed in the figure, gain drops after a certain input or output power. When the gain is 1 dB less than the linear gain the corresponding output power is called P<sub>-1dB</sub>. In ideal case the output power is considered only at one frequency which is the input signal frequency. Due to the nonlinearity, the amplifier generates additional frequency components at the multiples of this signal frequency are called harmonic distortion.

The input vs. output curve can be expressed by Taylor series as shown in eq. 2.1.

$$V_{out} = a_0 + a_1 \cdot V_{in} + a_2 \cdot V_{in}^2 + a_3 \cdot V_{in}^3 + \dots + a_n \cdot V_{in}^n + \dots$$

(2.1)

Let us consider an RF amplifier amplifying a pure sine wave  $(x = A \sin \omega_l t)$ . The output signal consists of the amplified signal and higher harmonics. The nearest harmonic product occurs at the double of the signal frequency and thus can be filtered out easily.

Figure 2.1 Input vs. output curve of a typical non-linear device and corresponding frequency spectrum for monochromatic input signal.

mixed products i.e.,  $n \le 3$ ).

TABLE 2.1

LIST OF THE OUTPUT FREQUENCY COMPONENTS OF A NONLINEAR SYSTEM EXCITED BY A TWO-TONE SIGNAL (N≤3)

| Frequency Components                           | Magnitude                       | Phase                                               |

|------------------------------------------------|---------------------------------|-----------------------------------------------------|

| dc                                             | $a_0 + a_1 . A^2$               |                                                     |

| $\omega_{I}$ , $\omega_{2}$                    | $a_1 A + \frac{9}{4} a_3 . A^3$ | Sin                                                 |

| $2\omega_1, 2\omega_2$                         | $\frac{1}{2}a_2 . A^2$          | -Cos                                                |

| $3\omega_1, 3\omega_2$                         | $\frac{1}{4}a_3 .A^3$           | -Sin                                                |

| $(\omega_1 + \omega_2), (\omega_2 - \omega_1)$ | $a_2 . A^2$                     | -Cos, Cos                                           |

| $(2\omega_1+\omega_2),(2\omega_2+\omega_1)$    | $\frac{3}{4}a_3.A^3$            | -Sin                                                |

| $(2\omega_1-\omega_2)$                         | $\frac{3}{4}a_3 .A^3$           | "Sin" if , $\omega_l > \omega_2$ Otherwise "-Sin"   |

| $(\omega_1+2\omega_2), (\omega_1-2\omega_2)$   | $\frac{3}{4}a_3 .A^3$           | "Sin" if, $\omega_2 > \omega_1$<br>Otherwise "-Sin" |

<sup>\*</sup> The phase of a term is defined by its behavior at t=0.

For a modulated signal, however, this does not work anymore because mixing products are generated which fall in the signal band and it is impossible to filter them out. These mixing products are called intermodulation distortion products. The simplest modulated signal is a two-tone signal  $(x = A_I \sin \omega_I t + A_2 \sin \omega_2 t)$ , where  $\omega_I$  and  $\omega_2$  correspond to two closely spaced frequency components, which is similar to an amplitude-modulated signal.

A two-tone signal consists of two closely spaced sine waves. A simple two-tone signal having the same amplitude A can be written as:  $x = A(\sin \omega_1 t + \sin \omega_2 t)$

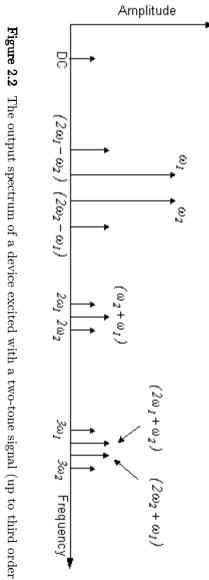

The next step is to replace  $V_{\rm in}$  in eq. (2.1) by the two-tone signal and to do some mathematical calculations to have a spectral representation. Fig. 2.2 shows the resulting frequency components considering the terms up to third order in eq. (2.1), table 2.1 adds details on the respective spectral lines.

However, as distortion products are concerned, power devices have more than one nonlinearity mechanism and the components generated from different mechanism interact [6]. The third order distortion components at  $(2\omega_1 - \omega_2)$ ,  $(2\omega_2 - \omega_1)$  are of special interest because they fall inside the signal band. They are commonly referred to as third-order intermodulation products (IM3).  $(2\omega_1 - \omega_2)$  is called "IM3L" and  $(2\omega_2 - \omega_1)$  is called "IM3U" where "L" and "U" stand for Lower and Upper sideband. If the input signal is increased by a factor x then IM3 products would increase by  $x^3$ . That means in a flat gain operation, if the input and output fundamental signal amplitude is increased by 1 dB, the third-order components grow by 3 dB. If we imagine that we could increase the input signal amplitude further and further while maintaining this slope, at some point the IM3 will meet the Pout curve. This point is defined as third-order intercept point, often abbreviated as IP3 or TOI. This point is a point derived by extrapolation. A real amplifier will reach saturation far below this power level. The IP3 has been the most widely used measure for defining device linearity. Intercept points of any order can be calculated by a single RF measurement when applying the following formulas:

$$IP_n [dBm] = Pout_{(fund.)} [dBm] + \frac{(Suppression)_n}{(n-1)} [dB]$$

where,

$(Suppression)_n [dB] = Pout_{(fund.)} [dBm] - Pout_{(IM_n)} [dBm]$

For IP3, one obtains the specific result

$$IP_{3} [dBm] = Pout_{(fund.)} [dBm] + \frac{Pout_{(fund.)} - Pout_{(IM3)}}{2} [dB]$$

(2.3)

This calculation is valid only if the measurement is performed carefully within the linear operation regime ensuring that the distortion products are well above the noise level. However, the amplifiers or devices do not behave the same for each input power level and therefore IP3 is often debated to be the linearity figure of merit. If one measures the output powers and the IM3 powers of the tones for the complete operating power range of a device then the real nonlinear behavior of the device of full operating range can be estimated. The real difference between the output power of the fundamental tone and IM3 tone is called carrier to intermodulation (C/I) ratio. Thus the IP3 for a single power level is usually redefined as TOI (Third order intercept) by the following relation derived from eq 2.4.

$$TOI [dBm] = Pout_{(fundamental)} [dBm] + \frac{1}{2} \cdot \left(\frac{C}{I}\right) [dB]$$

$$where, \left(\frac{C}{I}\right) [dB] = Pout_{(fundamental)} [dBm] - Pout_{(IM 3)} [dBm]$$

(2.4)

### 2.3 IMD characterization of the devices

There are various ways of intermodulation distortion characterization. The most common and classical one is to measure

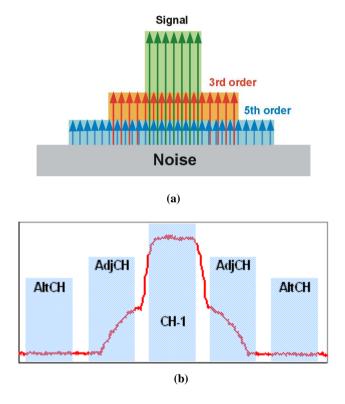

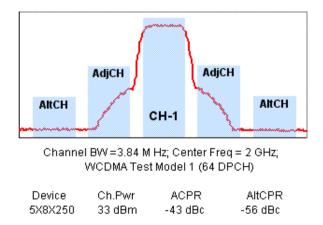

the intermodulation distortion products by exciting the device with a two-tone signal as explained in section 2.1. Two-tone signal is amplitude modulated like signal with suppressed carrier. As mentioned earlier, today's mobile communication usually use a wideband digitally modulated signal. Such a signal can be imagined as densely spaced multiple tones. If the device is excited with a multitone signal then a broad spectrum of the distortion product can be seen. This gives a more clear idea how a device would behave under wide-band excitation. However, a more realistic test can be done if a real world wide-band signal. The amplifier can be excited according to users wish (i.e. the modulation scheme, number of channel etc.) and the output spectrum can be observed. Fig. 2.3(b), shows a typical output spectrum of an amplifier, amplifying wideband modulated signal and fig. 2.3(a) shows the mechanism of growing sidebands from multitone point of view. If the channels are defined, then one can measure the ratio of total power in the signal and the power in the side band. This measurement is called adjacent channel power ratio (ACPR).

### 2.3.1 Demodulated signal characterization

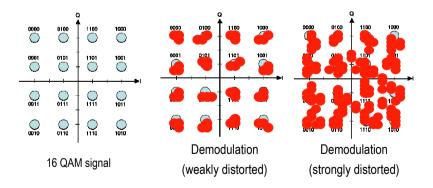

If the analyzer is equipped with a digital demodulator and synchronized with the signal generator, then one can demodulate the signal at the output of the amplifier and analyze the amplified signal quality. Constellation diagram, error vector magnitude (EVM), Bit Error Ratio (BER), code domain analysis etc. are some examples of more advanced and signal specific figures of merit. A constellation diagram is a representation of a signal modulated by a digital modulation scheme such as quadrature amplitude modulation or phase-shift keying. It displays the signal as a two-dimensional scatter diagram in the complex plane at symbol sampling instants. In a more abstract sense, it represents the possible symbols that may be selected

by a given modulation scheme as points in the complex plane. Measured constellation diagrams can be used to recognize the type of interference and distortion in a signal.

**Figure 2.3:** The output spectrum of a device excited with (a) multitone signal (b) wide band signal where the abscissa and ordinate correspond to frequency and power accordingly.

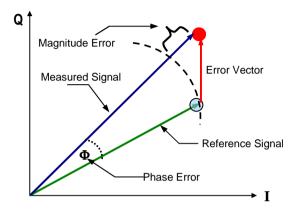

A signal sent by an ideal transmitter or received by a receiver would have all constellation points precisely at the ideal locations. Due to distortion of the signal, the actual constellation points deviate from the ideal location. An error vector is a vector in the I-Q plane between the ideal constellation point and the point received by the receiver. Its average length (or magnitude), defined as the Euclidean distance between the two points, is the EVM.

The error vector magnitude is equal to the ratio of the power of the error vector to the root mean square (RMS) power of the reference. It is defined in dB as:

$$EVM(dB) = 10\log_{10}\left(\frac{P_{error}}{P_{reference}}\right)$$

(2.5)

where  $P_{error}$  is the RMS power of the error vector, and Preference is the RMS power of ideal transmitted signal.

EVM is defined as a percentage in a compatible way with the same definitions:

$$EVM(\%) = \sqrt{\frac{P_{error}}{P_{reference}}} \times 100\%$$

(2.6)

**Figure 2.4:** Constellation diagram ( Defined and received signal shown in I-Q plane)

Figure 2.5: Vector components defining error vector magnitude (EVM)

Bit error ratio is the ratio of the number of bits incorrectly received to the total number of bits sent during a specified time interval.

## 2.4 Comparison of devices in terms of linearity

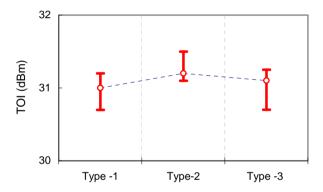

As one of the main goal of this work is to minimize the intermodulation distortion at the device level, it is very important to compare the intermodulation distortion of devices in a reliable way. The absolute linearity of a device is very difficult to determine and hence to compare. This is because the linearity of device depends on many factors such as bias, termination impedance etc. One of the most simple and classic figures of merit is to compare IP3. However IP3 is not able to show the complete picture as most of the practical

application consider large signal operation of active device. A complete power sweep of two-tone measurement can show the linearity behavior over whole power spectrum. In this case it is enough to compare only C/I ratio. Some publication compare C/I ratio over the input power which does not show a real comparison if the devices have difference in gain. Therefore C/I must be compared as a function absolute output power.

Devices with different architecture may have different pinch-off voltage and transconductance profile. Therefore, it is important to fix the bias point properly. Sometimes the comparisons are done at constant  $V_{\rm g}$  and  $V_{\rm d}$  which is valid if both the transistor have similar pinch-off condition and transconductance profile. This is not usually the case for different epitaxial design. A better way is to compare them at the same drain current.

Termination impedance is another factor to consider. As long as the transistors have the same periphery and technology we assume similar mismatch at 50  $\Omega$ . It is safe to measure the devices in the well defined 50  $\Omega$  environment. To be consistent, in this work we have compared linearity of the devices with equal periphery at defined drain bias (voltage and current) in a 50  $\Omega$  environment.

## 3 GaN HEMT

GaN is the youngest and one of the most promising materials in III-V semiconductor industry. GaN was introduced as the first material to produce blue laser. Later it was also successfully adapted to produce devices for RF applications. As a III-V material system the GaN and AlGaN pair has the same advantage as other III-V materials to create a heterojunction. The GaN/AlGaN system is often referred to have similarity with GaAs/AlGaAs. However, recent findings show that the 2 DEG (two dimensional electron gas) formation process is quite different in these two technologies.

Therefore, it is important to understand the mechanism of GaN HEMT operation, in particular, the 2DEG formation in AlGaN/GaN heterostructures. In this chapter, the basic HEMT and specially GaN HEMT operation are sketched, together with a short description on the FBH process. This is important to understand the mechanism of intermodulation distortion in GaN HEMTs.

### 3.1 Basic HEMT operation

The HEMT operation relies on using high mobility electrons generated from the hetero junction of with a highly doped n-type AlGaAs layer and an undoped GaAs layer. The electrons generated in the n-type AlGaAs drop completely into the neighboring GaAs, because the hetero-junction created by different band-gap material forms a steep canyon in the GaAs side where the electrons can move quickly without colliding with their donor atoms.

22 3 GaN HEMT

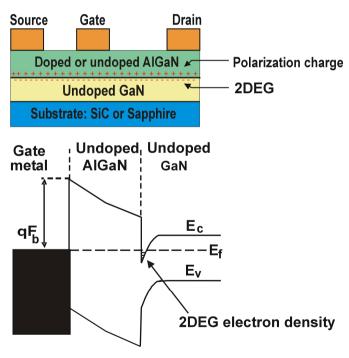

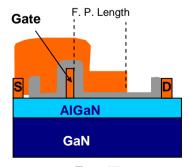

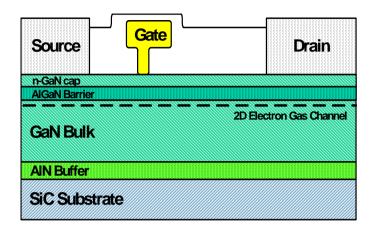

However, the GaN HEMT 2DEG formation is different from that in GaAs. Due to the presence of a strong polarization field across the AlGaN/GaN heterojunction, a 2DEG with sheet carrier density up to 10<sup>13</sup> per square centimeter is achieved without any doping [7]. Ibbetson et al. [8] found that surface states act as a source of electrons in 2DEG. The built-in static electric field in the AlGaN layer induced by spontaneous and piezoelectric polarization leads to an altered band diagram and the electron distribution of the AlGaN/GaN heterostructure. Basic GaN HEMT structure and band diagrams are shown in fig. 3.1.

Figure 3.1: Basic structure and its band diagram AlGaN/ GaN HEMT.

### 3.2 GaN material properties

The material properties of GaN, makes it a very attractive material to produce high power microwave devices in comparison to other available semiconductor materials.

Wide band-gap and high breakdown electric field allows high terminal voltage operation of the transistor based on GaN technology. High electron mobility ( $\mu=1200$  to 1500 cm<sup>2</sup>/Vs in 2DEG) and saturation velocity determine its high frequency characteristics. The high sheet carrier density (ns  $\approx 1 \text{x} 10^{13}$  cm<sup>-2</sup>) of two-dimensional electron gas (2DEG) in AlGaN/GaN HEMT maintains high current densities. The high voltage operation with high current density makes GaN devices the best high power devices so far. GaN grown on SiC has a very good thermal conductivity which is very important for

TABLE 3.1

SEMICONDUCTOR MATERIAL PROPERTIES

| Material properties                                     | Si       | GaAs   | 6H-SiC   | 4H-SiC   | GaN    |

|---------------------------------------------------------|----------|--------|----------|----------|--------|

| Band gap (eV)                                           | Indirect | Direct | Indirect | Indirect | Direct |

|                                                         | 1.1      | 1.4    | 3.0      | 3.2      | 3.4    |

| Electron mobility (cm²/V-s)                             | 1500     | 8500   | 250      | 700      | 800    |

| Breakdown voltage (MV/cm)                               | 0.3      | 0.4    | 2.4      | 2.0      | 3.3    |

| Saturation velocity (x10 <sup>7</sup> cm /s)            | 1.0      | 2.0    | 2.0      | 2.0      | 2.7    |

| Thermal conductivity (W/cm-K)                           | 1.5      | 0.5    | 4.5      | 4.5      | 1.3    |

| Operating temperature ( ${\mathfrak C}$ )               | 300      | 300    | > 500    | > 500    | 750    |

| Melting temperature (K)                                 | 1690     | 1510   | > 2100   | > 2100   | >1700  |

| Johnson figure of merit $(\alpha V_{br}^2 x V_{sat}^2)$ | 1        | 11     | 260      | 180      | 760    |

24 3 GaN HEMT

power transistors to be reliable and durable due to increased channel temperature at high power operation. Experiments showed that a GaN transistor can work at high ambient temperature such as 300°C while silicon transistors stop working at about 140°C [19].

#### 3.3 GaN Device fabrication

At FBH, a complete GaN HEMTs process line is available covering the entire spectrum from epitaxy to packaging. GaN layers are grown on SiC wafers. A detailed discussion on the fabrication process is out of the scope of this thesis. However, a brief review is given in the following based on [10], which clarifies the basics of the devices investigate during this work.

#### 3.3.1 Substrate

The choice of the suitable substrate is a key issue for GaN HEMTs. GaN is so far not commercially available as substrate crystal. The first successful epitaxial layers of GaN were grown on Sapphire. Sapphire is cost effective but has low thermal conductivity. Therefore, SiC gained recently more popularity with improved technology to grow defect free GaN layer. SiC has very good thermal properties, which is nearly 10 times more than that of the sapphire. Also, the reduced lattice mismatch between SiC substrate and GaN improves the epitaxial quality and reduces dislocations densities. As SiC is still expensive, other thermal management techniques such as flip-chip mounting technology have been used to make AlGaN/GaN HEMTs on sapphire competitive. GaN HEMTs have also been produced using freestanding GaN substrates [9]. However, this is very expensive, have lower thermal conductivity and till now limited to laboratory. Recently, GaN on Si substrate has also been commercialized. Si wafer is 100 time cheaper than SiC and allows to use larger wafer size.

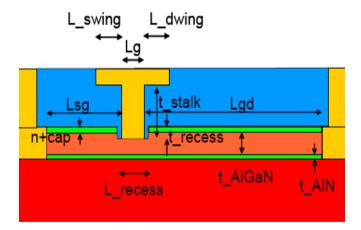

#### 3.3.2 Basic GaN Process technology at FBH

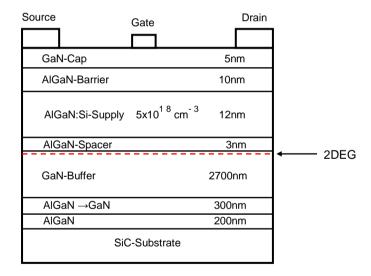

The  $Al_{0.25}Ga_{0.75}N/GaN$  HFET structures used for this work were grown by MOCVD on 2" SiC wafers. The epitaxy growth sequence started with the deposition of a 500 nm thick AlGaN layer followed by a 2.7  $\mu$ m thick highly insulating GaN buffer layer, 3 nm  $Al_{0.25}Ga_{0.75}N$  spacer, 12 nm Si-doped  $Al_{0.25}Ga_{0.75}N$  supply layer, 10 nm  $Al_{0.25}Ga_{0.75}N$  barrier. A 25 nm thick AlGaN layer on the top of the GaN buffer forms a two-dimensional electron gas (2 DEG) at the AlGaN/GaN interface.

Figure 3.2: Basic FBH epitaxial layer structure for GaN HEMT

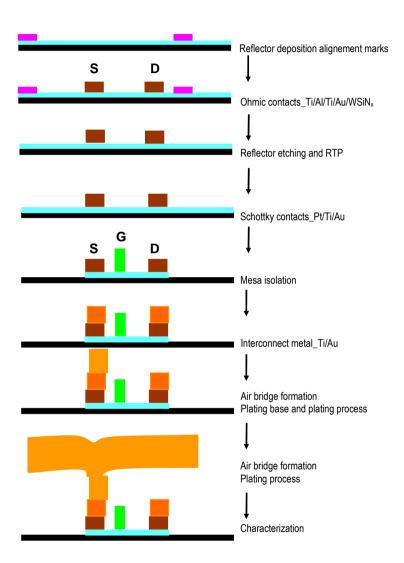

The  $Al_{0.25}Ga_{0.75}N/GaN$  HEMT device fabrication was accomplished in eight lithography steps shown in fig. 3.3. It starts with the deposition of backside and front side Ti reflector layers (Z-layer) on

26 3 GaN HEMT

transparent wafers for ease of handling, recognition and exposure using wafer stepper layer and a 5 nm thick GaN cap layer.

The front side Ti layer is structured and alignment marks are defined by stepper lithography. A sophisticated  ${\rm Ti/Al/Ti/Au/WSiN_x}$  metallization scheme is employed for the fabrication of ohmic contacts (B-layer). The reflector is then removed (Y-layer) and wafers are annealed in  ${\rm N_2}$  ambient to achieve low contact resistance. Gate contacts (C-layer) are made in using Pt/Ti/Au metallization. A gate length of 0.5  $\mu$ m is defined with stepper lithography.

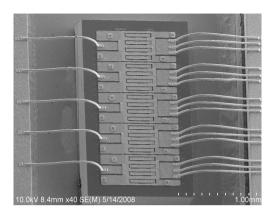

The mesa isolation is done (A-layer) by reactive ion etching RIE (BCl<sub>3</sub>/Cl<sub>2</sub>/Ar). Gate fingers and drain fingers are interconnected (D-layer) using Ti/Au. Source pads are connected using Au air bridges in two steps. First the plating base (F1-layer) is defined using Ti/Au/Ti metal and then the air bridges are realized using Au galvanic electroplating (F2-layer).

To improve the device performance, several modification have been introduced in FBH process technology in the last years. Some important modifications are the implementation of  $\mathrm{SiN}_{x}$  passivation layer, to protect the device surface from surface contamination and possible damage during device processing, an improved metallization system and implementation of fieldplate etc. Besides this, many other special modifications have been taken place for application specific devices such as low noise, high linearity, high frequency applications etc. [10].

Figure 3.3: The AlGaN/GaN HEMT device fabrication steps [10].

28 3 GaN HEMT

## 3.4 Packaging

After fabrication and characterization on wafer, the transistors are diced and packaged in convenient metal packages. Usually the base plate (often called flange) of the package is made of gold plated copper-tungsten-alloy which shows high thermal and electric conductivity. Above the flange a rectangular Aluminium oxide  $(Al_2O_3)$  frame is placed. On the top of this layer, T-shaped metal fins are placed at the input and output side which serve as leads and as bonding area.

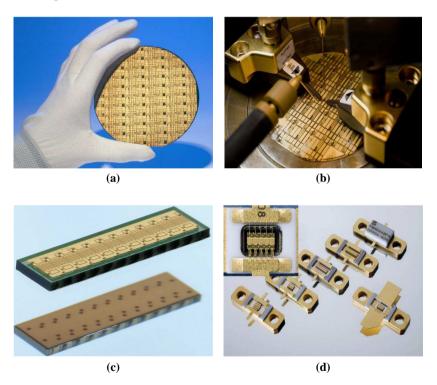

**Figure 3.4** GaN HEMT packaging steps: (a) A Processed wafer , (b) Onwafer test (c) Diced device, (d) Device bonded in package

3.4 Packaging 29

The diced chip is normally soldered at the middle of the package and bonded at the gate and drain side of the device. Source connected to the flange either by via holes or by bonding. After bonding the device into a package, it is sealed by a ceramic lid. In fig. 3.4, different steps from wafer till packaging is shown.

## 4 Measurement and characterization

Measurement and characterization of devices is the most fundamental part of this work. Although nonlinear measurements, in particular two-tone measurements were the most important characterizations in terms of linearity, other standard measurements like s-parameter, load-pull and noise figure measurements have been performed as well. Devices were characterized on-wafer and in packaged form. Packaged devices were characterized in special test fixtures. As high power devices are concerned, the commercial nonlinear measurement systems were not capable of handling the required measurements. Therefore, a customized and dedicated measurement system had to be built for nonlinear characterization using commercial equipment. The measurement system was completely automated, The control software was realized using LabView<sup>1</sup>.

In this chapter, we will mainly present the non-linear measurement system of FBH along with the difficulties and innovative solutions for reliable characterization of high power GaN devices. In addition to that, some critical failures during measurements and the corresponding counter actions are described.

## 4.1 Intermodulation test setup

Usually, a two-tone test signal is generated combining the output signals of two signal-generators. This method has a few drawbacks and difficulties:

-

<sup>&</sup>lt;sup>1</sup> LabView is a trade mark of National Instruments.

- It is very difficult to maintain equal amplitude of both tones due to the individual control of each tone. Especially, if the signals are amplified using individual external amplifiers to obtain higher driving power, problems arise due to gain differences in these amplifiers. Moreover, there might be isolation problem.

- In order to achieve stable and reproducible results, the phases of the two signals must be controlled, which is maintained only if phase-locking of the two generators is realized.

- If the signal is first combined and then amplified by a single amplifier this amplifier itself generates distortion products, which result in an incorrect measurement. In this case, the amplifier must be operated at a large power backoff, which leads often to a very expensive solution and sometimes may be even impossible.

To avoid these difficulties, modern multi-tone generators have a built-in wide-band I-Q modulator. Controlling quadrature I-Q signals at the base-band, it is possible to generate arbitrary multi-tone signals. If the two-tone signal is generated with this kind of generator, the signal is available from a single channel, which eliminates the first two problems mentioned above. However, the output power of the generator is not very high and therefore we encounter the same problem as before in amplifying the signal without distortion. As we can control the base-band I-Q signal there is a possibility to compensate the distortion of the amplifier by a proper pre-distortion of the I-Q modulation. This, of course, requires an option at the generator to control the I-Q signal externally.

Therefore, it is necessary to set up a combined system with a connection between the analyzer and the generator. One first has to measure the distortion products of the amplifier and, then based on this information, generate a pre-distorted base-band signal at the input of this amplifier so that the resulting distortion components at the output vanish. This process can be called linearization. In our case, we use an Agilent PSG (Performance Signal Generator) and PSA (Performance Spectrum Analyzer)<sup>2</sup> connected by GPIB to a computer.

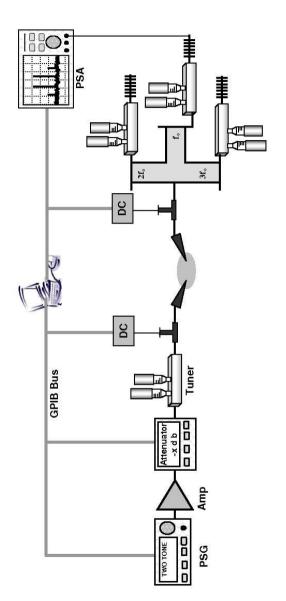

Concept diagram of the measurement system using a multi-tone generator is shown in fig. 4.1. A two-tone signal is generated using a PSG. Next to the generator, there is an amplifier followed by an automatic attenuator. Such an automatic attenuator, also remotely controlled by the computer, is required to realize the power sweep. This is necessary because the distortion of the input amplifier is suppressed by pre-distortion as stated earlier. But this linearization holds only at a particular power level. If the power level is swept at the generator, the linearization does not remain valid for the entire sweep and it would have been necessary to perform linearization for each power value, which is impractical because of several reasons: First, linearization is very sensitive and not well reproducible. Thus, when using predetermined I-Q data from a look-up table, this may not yield the desired low distortion levels at the amplifier output. This is because the linearization depends on many factors like amplifier gain, phase, temperature etc. Second, the correction is achieved by an adaptive optimization algorithm and therefore time consuming. Moreover, the DUT (Device Under Test) must be replaced by a through at the time of new calibration.

<sup>&</sup>lt;sup>2</sup> PSA (Performance Signal Analyzer) and PSG (Performance Signal Generator) are the trademarks of Agilent Technologies.

Figure 4.1 Measurement setup for intermodulation distortion characterizations.

Figure 4.2 Test signal before and after linearization. Signal tone spacing 5 MHz and linearization done on 25 MHz bandwidth

Therefore, the best idea is to perform the correction of the input amplifier at the highest possible output power and realizing the power sweep by using a step attenuator.

In fig 4.2, the test signal is shown before and after linearization. As can be seen, linearization is very effective. To do the linearization a computer algorithm is used. The software gets the distortion data from the PSA and calculates an approximate distortion parameter according to the gain of the path (PSG output to PSA input) and rotates the I-Q offset at the generator. Then the output is measured again, compared to the previous setting and an error factor is calculated. In this way, a continuous iteration is done to find the optimum pre-distortion parameters. However, one must take care of selecting the appropriate amplifier and bias-Ts.

#### 4.1.1 The input driving amplifier

If the amplifier produces too much distortion then the software may not find a solution to linearize (and it might even be impossible on principle because the linearization concepts are limited in terms of the distortion level they can compensate). One should use an amplifier having high dynamic range with suitable output power, reasonably low-noise properties, high-IP3 and broadband characteristics. If the amplifier is narrow-band (as, e.g., LDMOS amplifiers) it may be very difficult or even impossible to linearize them according to the aforementioned technique. In our case, we use GaAs-HBT and GaN-HEMT amplifiers. We tried Si LDMOS and TWT amplifiers as well but were not able to achieve satisfactory linearization even after a number of iterations.

Also, it is always better to have a single amplifier with sufficiently high output power and gain margin. If more than one amplifier are connected in series to achieve higher gain and power, it becomes difficult to linearize them due to interstage distortions.

The test signals before and after linearization are shown in fig. 4.2 for a commercial amplifier. Here the tones have 5 MHz spacing and a linearization is done on a bandwidth of 25 MHz to suppress  $3^{\rm rd}$  and  $5^{\rm th}$  order distortion components.

#### 4.1.2 Bias-T

It is very important to select proper bias-Ts for an IP3 measurement. The bias-T must cover also the frequency range of the envelope, i.e. the tone spacing  $\Delta f$ . If the bias T does not pass this frequency component properly the envelope will be distorted and the measurement can be incorrect. This shows up as asymmetry between the lower (IM3L) and upper (IM3U) distortion products, which may be misinterpreted as memory effect of the device.

We have also added tuners at the input and output for device characterization at different source and load impedances. A very high quality triplexer is used at the output to separate higher harmonics and tune them independently so that higher harmonic effects on linearity can be studied.

#### 4.2 Power calibration

A power calibration is necessary to perform accurate measurements. Loss at the output network must be determined using a network analyzer or a power meter. For this purpose, output and input are connected by a thru and a power sweep is done using the attenuator. For each position of the attenuator, the power is measured taking into account the losses in the output network i.e., in the probes, the connectors, and the cable, and, if applicable, any attenuator at the input of the spectrum analyzer. The measured power is later used as the input power at the DUT for different attenuator positions.

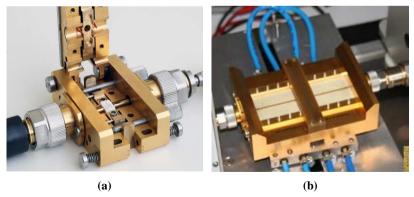

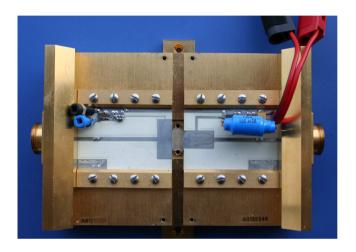

#### 4.3 Fixture

GaN devices fabricated on wafer are usually diced and packaged in industry standard packages. As this package adds parasitics, it is important to characterize these devices in packaged form. We have used two kind of commercial fixtures as shown in fig. 4.3 (a) and (b) for small signal and large signal characterization accordingly. We will call them *Robotron* and *ICM* fixture according to their manufacturer name. The *Robotron* fixture can be calibrated precisely at the device reference plane for small signal measurement. The device is clamped directly at the coaxial interface. The drawback of this fixture is that it cannot handle very high power. In the ICM fixture the transistor is connected to a microstrip interface and the fixture is mounted on a water cooled heat sink. This fixture is very robust and can handle more than 100 Watt CW power. Another advantage of this fixture is

that the 50  $\Omega$  microstrip lines can be replaced by arbitrary boards. It is important to measure power accurately. The low impedance presents a tuning problem for the load and source-pull measurement due to the fact that the impedances are either outside the range of the tuner, or where the tuner accuracy degrades [11]. The tuner losses increase with the increasing reflection coefficient seen from the input and output of the transistor towards the tuners. As a result, it is difficult to estimate the accurate power delivered from the device. It was observed that after measuring the whole packaged device in a standard commercial test fixture, expected power was not available. To estimate the impedance, s-parameter of the device was measured in a 50  $\Omega$  environment. Quarter wavelength transformers were designed as pre-matching networks. This means that a lower impedance transmission line directly at the device which matches input or output impedance of the transistor to 50  $\Omega$ . Having a transmission line which is much closer to the impedance level of the transistor, the amount of loss decreases and the tuner is relaxed considerably to tune the device further more accurately.

Fig 4.3 (a) "Robotron" fixture and (b) "ICM" fixture.

4.4 Measurements 39

#### 4.4 Measurements

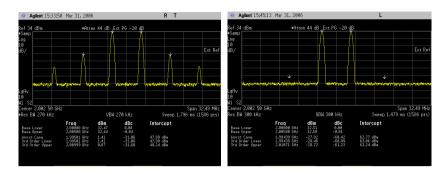

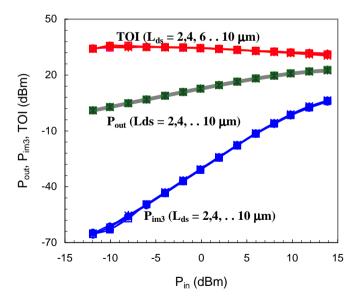

The PSA provides a third order intercept point (TOI) measurement option, which is based on the suppression formula stated earlier in eq. 2.3. This measurement has the following disadvantages:

- The whole bandwidth from  $(2\omega_1 \omega_2)$  to  $(2\omega_2 \omega_1)$  must be selected at once. Therefore, the noise level of the analyzer increases and dynamic range is decreased.

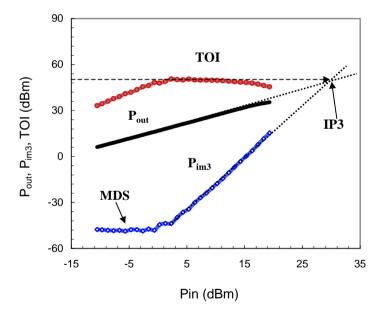

- Without performing a power sweep, one does not know whether the measurements are reliable. If the device is operated at low input power, the distortion components may not be high enough compared to system noise (i.e., close to or lower than MDS, the Minimum Detectable Signal). In this case, the analyzer takes the noise level as distortion component amplitude, which provides a totally wrong result. On the other hand, if the device is driven to the saturation region, there will be huge distortions and the single-point measurement would not satisfy the IP3 definition. In fig. 4.4, these two phenomenon can be observed at low and high input levels.

- Under some special conditions, i.e., at some particular biaspoint and RF level, the device may operate in an extremely linear way, which is called sweet spot. One may take advantage of such conditions but they cannot be used as the IP3 of the device. These points are very sensitive to all parameters and sometimes even not reproducible. Therefore, performing a single-point measurement one may incidentally meet this condition, which leads to a drastically overestimation of the device linearity.

In our case, the measurement system is completely automated and computer controlled by in-house software developed using LabView. The frequency components of interest are measured individually with a very narrow bandwidth. Therefore, it is possible to detect also very low amplitudes. There is the possibility of hardware averaging and peak search to avoid possible uncertainties. DC-Sweep, RF-sweep and security measures are implemented in the program as well.

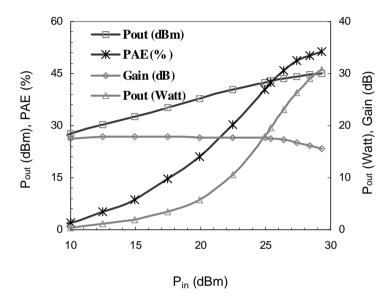

In the following we show an example of a measurement (see fig. 4.4). The DUT is a packaged high-power GaN transistor.

**Figure 4.4** Output power, 3<sup>rd</sup>-order intermodulation power and the corresponding 3<sup>rd</sup>-order intercept point as a function of input power. The device is a packaged GaN-HEMT.

This device reaches an IP3 of about 50 dBm. To achieve good accuracy, one needs an adequate amount of linear input power. Therefore, an external amplifier was used to amplify the test signal and its distortion was suppressed as described above in order to obtain a distortion-free two-tone signal. Please notice that up to an input power of about 4 dBm the distortion components are below the MDS (Minimum Detectable Signal). This illustrates that accurate measurement of such big devices needs enough driving power. If the power of third-order distortion components does not grow according to a 3<sup>rd</sup> order rule, either there is no distortion by transfer mechanisms (this is the case for ideal linear devices such as a passive component, for instance) or the distortion components are out of measurement sensitivity. If the 3<sup>rd</sup> order distortion components show a 1<sup>st</sup> order characteristics, i.e., the curve is parallel to the fundamental power, this can be interpreted as input distortion, which might origin from the input amplifier or attenuator and is only amplified by the DUT.

## 4.5 Measurement safety

As very high power devices concerned, critical failure during measurements results in a catastrophic penalty. Common problems during measurements are:

- Maximum electric field within the device exceeds the breakdown field and the drain is burnt or explodes.

- Forward turn-on of the gate diode exceeds the burnout limit [58].

- Unwanted oscillation due to bad tuning or impedance matching.

Using following safety measures these critical failures can be avoided in many cases.

#### 4.5.1 Drain safety using e-fuse

GaN Power devices are operated at very high drain voltage and they deliver high current. During large power device measurement typical DC voltage at the drain exceeds 50 V and current goes up to 10 A. Huge DC power supplies are required, with a high amount of stored energy. Therefore, quite often the current limits adjusted by the bias compliance settings reacts too slow. As a consequence, the transistors are destroyed during critical measurements and, even worse, destroys neighboring devices and other parts of the system, e.g. the probe tips. Using an e-fuse the damage can be minimized in such situations, thus protecting wafer probes, bias tees, connectors, and, as far as possible, the transistors themselves.

The DUT (device under test) is usually on-wafer device and contacted by suitable probe tips. In the following, the device is assumed to be of HEMT type.

During the measurements, current or voltage may exceed their maximum values or a failure in the transistor or at its periphery may occur due to RF and thermal stress. This will usually result in an excessive DC current into the drain which heats up the devices, burning the drain or even causing explosion in the worst cases. The proposed drain current e-fuse can avoid these types of accidents in many cases. This inexpensive solution may save a great deal of time and money and avoid loss of invaluable measurement data. DUTs and probe tips are safe from the transient DC peaks of the power supplies usually generated due to the high-energy emission of output capacitors of the power supply. Moreover, in cases of device failure, the fast

switch-off process of the e-fuse restricts the damage to its origin. Hence, the defective part can be located, which helps in detecting the sources of failure and is very important for device development.

#### A. E-fuse working principle:

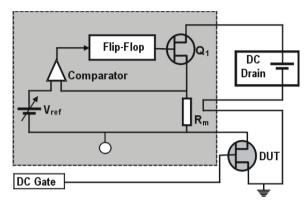

As discussed above, the main reason of damage is a high drain current. Thus, if the drain bias is switched off very fast, the damage can be avoided in many cases. For this purpose, we need to do two things, firstly to follow the instantaneous drain current continuously and, second, to switch it off very fast and efficiently, i.e., without any parasitic DC pulse or overshooting. Fig. 4.5 presents a schematic diagram of the circuit realizing these functions. The e-fuse circuit works as follows:

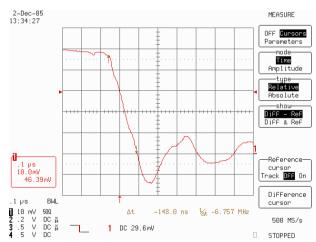

The voltage across the resistor  $R_{\rm m}$  is proportional to the drain current. This voltage is monitored and compared with a variable reference voltage  $V_{\rm ref}$ . If the voltage drops at  $R_{\rm m}$  is higher than  $V_{\rm ref}$ , the flip-flop will be turned off. Then, the transistor  $Q_{\rm l}$  driven by the flip-flop will cut the drain supply of the DUT very fast. The flip-flop can be turned on or off via the front panel. After a break action, the flip-flop must be reset or switched on for further measurements. The essential feature of the e-fuse is its switching characteristic that should be fast and free from parasitic pulses and peaks. Fig. 4.6 presents the respective data, a screenshot from the oscilloscope. The current is drawn as a function of time. Switching off 10 A of continuous current takes about 150 ns. One observes that the switching is very clean in terms of unwanted pulses or peaks.

## B. Measurement Examples with and without e-fuse:

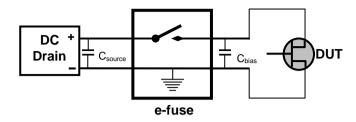

In this section we will present some measurements performed with and without the e-fuse connected to the drain. The output capacitance of common laboratory power supplies which is shown as  $C_{\rm source}$  in fig. 4.7, is in the range of 1.000  $\mu F$  to 10.000  $\mu F$ . If we assume a drain voltage of 28 V, the stored energy in the power supplies reaches 0.4 to 4 W. If an e-fuse is connected,  $C_{\rm source}$  is isolated from the DUT. Therefore, only the stored energy in the bias Tee, i.e., the energy in  $C_{\rm bias}$  and an additional contribution generated due to the switching action are effective and can damage the DUT. A typical bias Tee has a capacitance of 10 nF to 100 nF, hence the energy stored is about 40  $\mu$ W to 400  $\mu$ W.

Assuming a total short resistance of 1  $\Omega$  and a total switching time of 1  $\mu$ s, there is an additional switch-off energy of about 400  $\mu$ Ws. Therefore, depending on the actual conditions of the devices used, applying an e-fuse drastically reduces the stored energy, in the example above by a factor of 500 to 10,000.

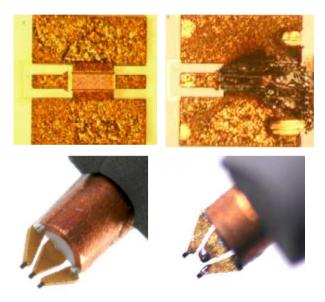

Fig. 4.8 presents photos of a GaN HEMT measured without e-fuse before and after a catastrophic failure, which led to excessive drain current causing explosion of the transistor. As can be seen the drain side is completely burnt. Even worse, this damaged the probe tips as well. The center finger of the probe tip was simply melted and partially evaporated. This can be avoided by using the e-fuse. In the following, we will show an example.

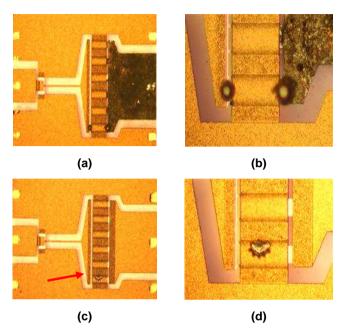

Figs. 4.9 (a) and (b) refer to the case without e-fuse. It can be seen that the drain side of the multi-finger device is burnt completely and the damage extends till the probes causing a tip damage. In contrast, figs. 4.9 (c) and (d) present the results for a similar kind of problem when using the e-fuse. Only a minimum burn-out has taken place where only a single finger is damaged and the drain contact remains intact leaving the tip unaffected. This is important not only in order to save cost on measurement equipment but also due to the

fact that it allows better localization of the origin of the failure in within the transistor. Overall, the benefits of the quick drain fusing are obvious.

Figure 4.5 Schematic diagram of the e-fuse circuit (shaded part is the e-fuse)

**Figure 4.6** Screen shot of a switching action. Abscissa corresponds to time and ordinate corresponds to current, 50 ns and 2 A per div. respectively.

Figure 4.7 A typical RF measurement system connected with an e-fuse.

Figure 4.8  $\,$  A GaN HEMT and probe tip damaged during measurement without e-fuse (right).

Figure 4.9 Transistor after failure during RF power measurements: without e-fuse (a) and (b); using e-fuse (c) and (d).

# 4.5.2 Self pinching bias-T to avoid gate turn-on and spurious oscillation<sup>3</sup>

This section deals with the forward turn-on and unwanted oscillation problems. We propose a simple gate bias-T for GaN HEMT measurement and circuits based on this kind of devices. This bias includes a simple series diode in the DC path that blocks any positive current from gate, in other words it restricts the gate diode of the device to operate in forward bias which is often called as forward turn-on. The new bias circuit assures a safe operating condition of

<sup>&</sup>lt;sup>3</sup> Patent pending: Nr.- 08164363.7-1233

FET/HEMT transistor during forward turn-on and do not hamper or degrade normal operating performance.

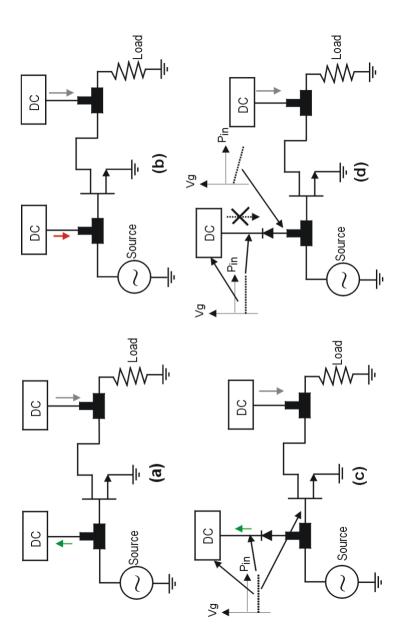

The presented bias T includes a normal p-n diode in the DC path of the gate bias. This diode does not have any effect during normal operation but pinches off the device automatically during forward turn-on. We have presented different RF measurements where this gate turn-on and gate-burn occurs. Measurements with the proposed bias-T clearly show that these condition can be easily avoided and thus the device survivability can be increased.

It is important to notice that, "gate-diode" refers to the schottky diode at the gate of the device which is the internal diode of the device or the part of the device itself. The "bias T-diode" refers to the external p-n diode that is introduced at the gate DC path which is not a part of the device rather a part of bias circuitry.

## A. Principle of operation:

The proposed DC bias circuit is similar to a commercial bias T that includes a simple diode restricting forward bias current at GaN FET/HEMT gate. AtNormal operating conditions gate of FET/HEMT (Normally on) devices is kept at a negative voltage at a desired bias condition. At this condition a very small negative current flow towards the gate that means the gate-diode is in reverse bias. The DC source at gate which is kept at negative voltage delivers a negative current. We have observed during measurement that, with increasing RF drive at the gate, the device enters into a self biasing condition and this negative current starts increasing towards zero. When the RF drive at the gate becomes very high then the gate current tries to shift towards positive. In this operating condition the gate-diode operates in forward bias. The device cannot stand this condition and can be easily damaged.

Figure 4.10 HEMT Operation in (a) and (c) normal operating condition with commercial bias and with new bias scheme; (b) and (d) under overdrive with commercial and new bias respectively.

A statistical study of our measurements shows that the most of the device damaged during RF measurement had a positive gate current. To avoid this situation we have added a simple p-n diode in the gate path. A series diode as shown in fig. 4.10 can restrict this positive current. Restricting this positive current the FET/HEMT device can be operated in a safe mode. If the diode is deployed at the gate DC path then maximum current which is allowed to flow from the DC source is zero. To fulfill this condition the voltage at gate automatically shifts towards negative (pinch-off) voltage. The principle of operation is shown in fig 4.10.

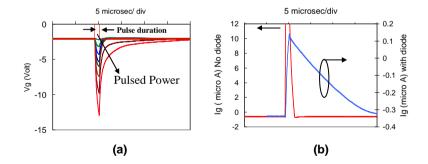

To investigate further we have tested the effectiveness of this bias scheme under very high pulsed input drive. As can be seen in fig. 4.11 (a), the voltage at the gate of the device drops according to input power and hence protect the device.

Figure 4.11 (a) Voltage at the gate of a  $2x125~\mu m$  device under pulsed overdrive (Pulsed RF power applied up-to 16 Watts. (b) Gate current measured at 16 Watt with diode and at 5 Watt without diode at gate path. The device did not survive in the second case.

The voltage at the gate dropped upto  $-13\mathrm{V}$  for an 1  $\mu\mathrm{s}$  long RF pulse of 16 Watts at the input of a small  $2x125~\mu\mathrm{m}$  device. The negative gate voltage at gate is not critical at GaN device. It is shown in [12], that GaN device survives more than  $-50~\mathrm{Volt}$ .

#### B. Load Pull Measurement:

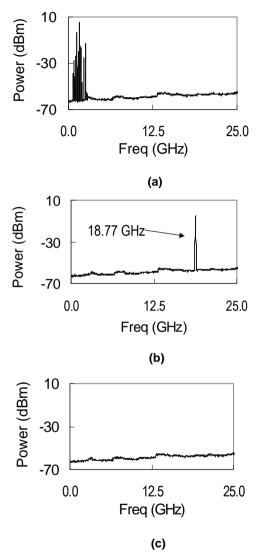

During characterization, it is necessary to operate these devices at many variations, sometimes extreme conditions (i.e. at different bias conditions and input/output impedance terminations). An inappropriate operating condition oftenruins these unexpectedly during characterization. Specially during load/source pull measurement where load and source impedance is varied to get the optimum RF operating condition (i.e., maximum power, highest linearity, high PAE etc.), tuners scan through different complex impedances over the smith chart. Some of the tuner positions may present a critical complex impedance to the device and lead to unwanted oscillation, usually but not restricted, at very low frequency where the device has very high gain. This can be observed by a spectrum analyzer but in many cases it is too late to save the device. The proposed bias circuit can automatically pinch off the device and thus saves it.

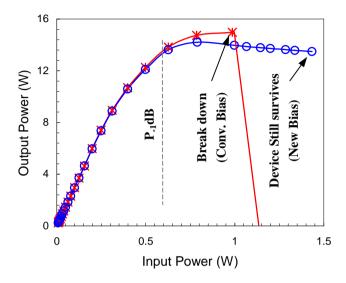

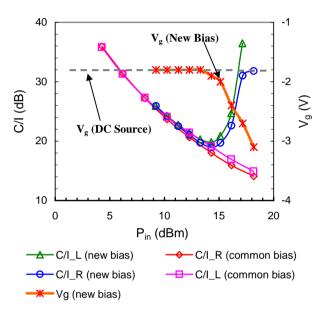

We have compared the load pull measurement of high power GaN HEMT devices with and without diode configuration. The implementation of the diode does not degrade the performance or measurement quality in terms of power and efficiency below normal driving condition (i.e. below  $P_{-1}$  dB). However, it does affect the measurement results at saturated power. In fig. 4.11, a comparison of load-pull power sweep is shown. As stated earlier, another major problem during load-pull measurement is to meet oscillating condition which can kill the device.

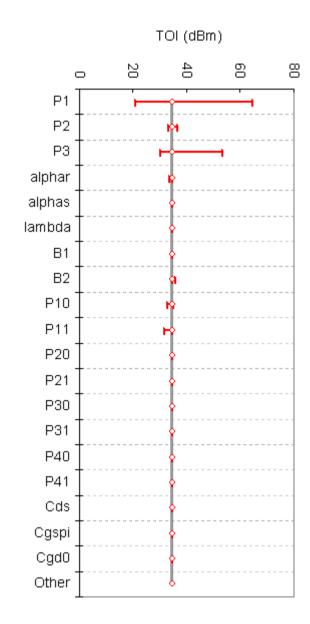

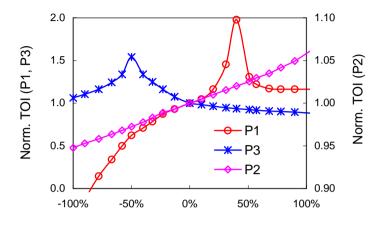

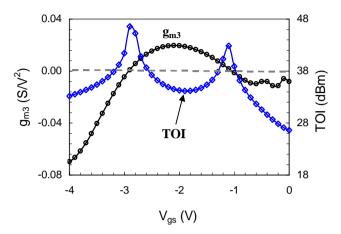

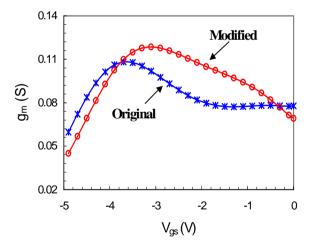

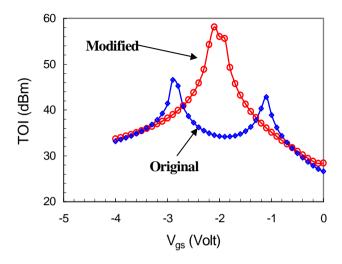

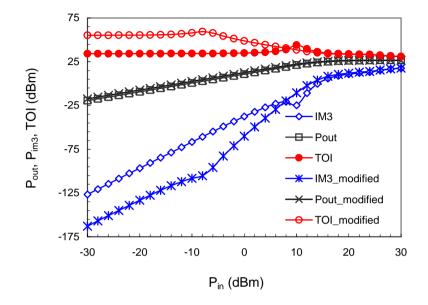

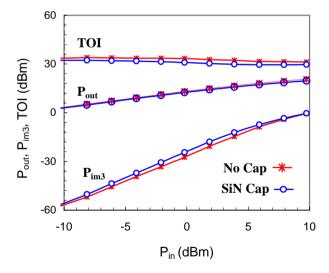

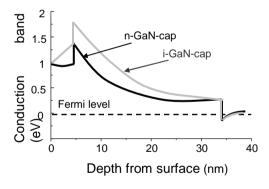

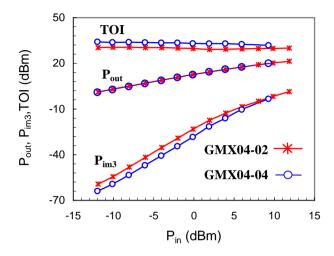

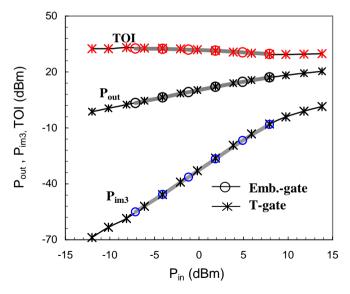

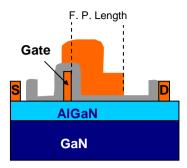

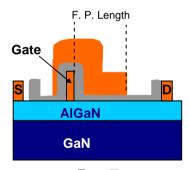

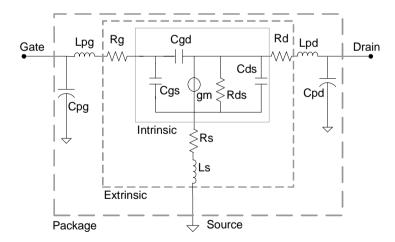

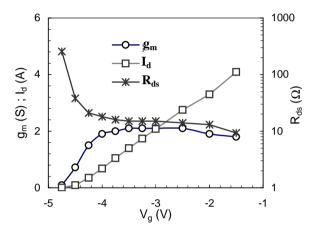

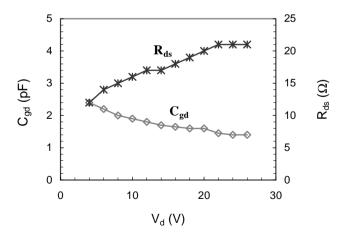

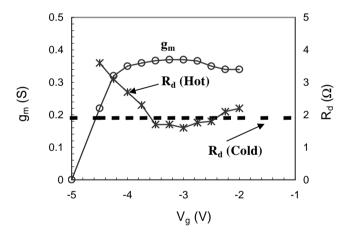

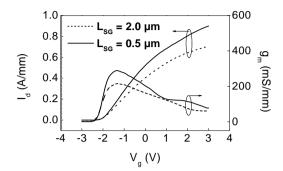

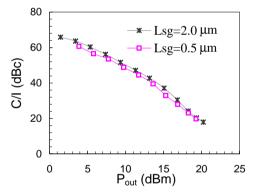

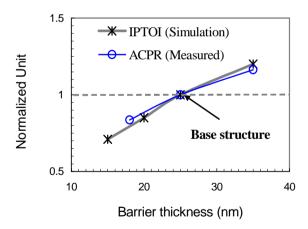

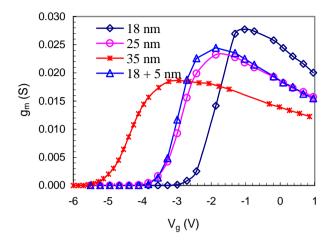

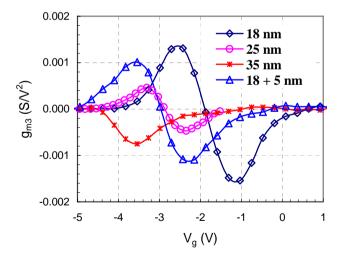

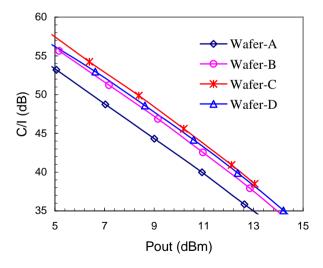

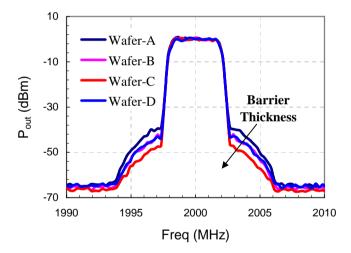

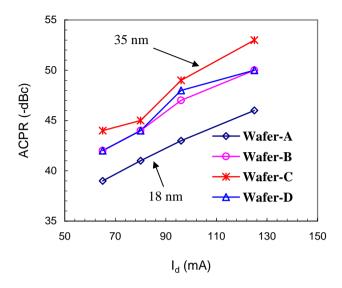

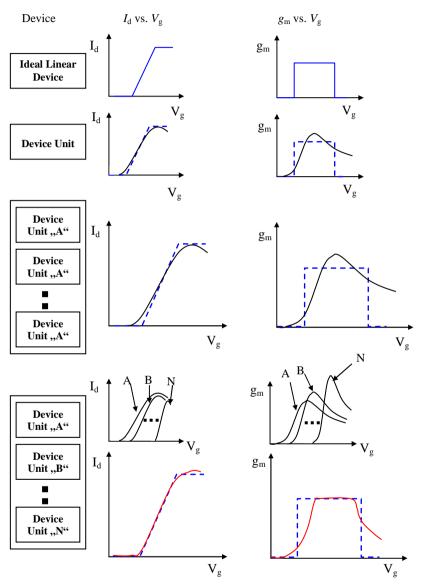

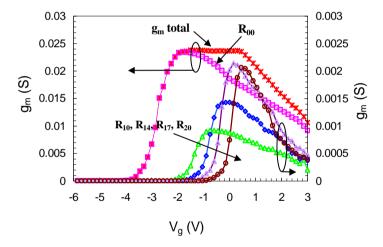

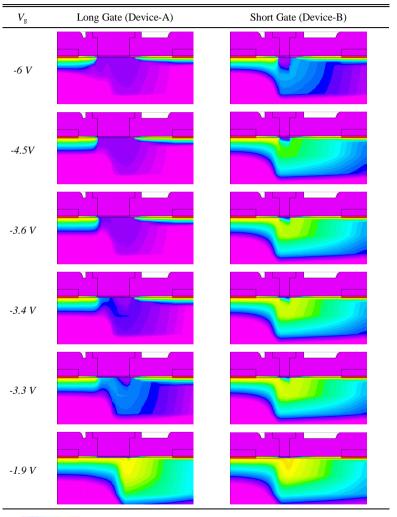

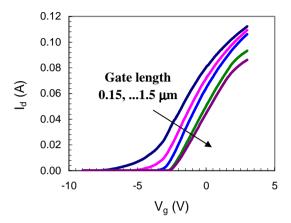

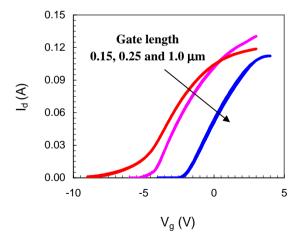

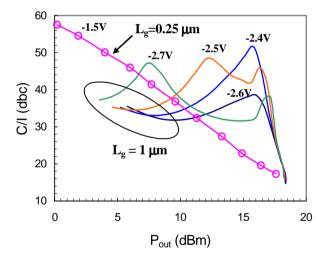

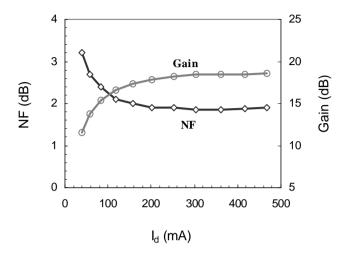

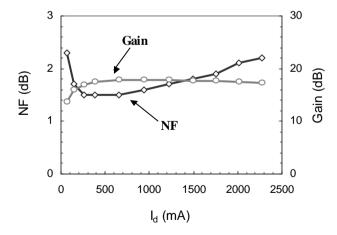

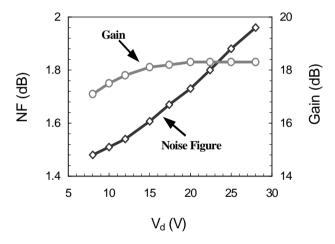

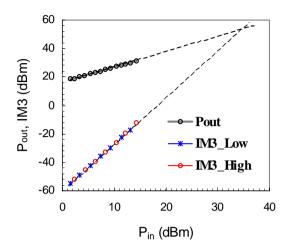

Figure 4.11 A 5x8x250 device measured at 2 GHz;  $V_d$ =24 Volt and  $I_d$ =1A.